## POLITECNICO DI TORINO

SCUOLA DI DOTTORATO Dottorato in Dispositivi elettronici – XXVIII

Tesi di Dottorato

# Behavioral modeling and FPGA implementation of digital predistortion for RF and microwave power amplifiers

Jiang Tao

Tutore Prof. Marco Pirola Prof. Vittorio Camarchia Coordinatore

Prof. Giovanni Ghione

March 2016

## Abstract

With the high interest in digital modulation techniques which are very sensitive to the PA nonlinearity, modern wireless communication systems require the usage of linearization techniques to improve the linear behavior of the RF power amplifier. The powerful and cheap digital processing technology makes the digital predistortion (DPD) a competitive candidate for the linearization of the PA. This thesis introduces the basic principle of DPD, its implementation on FPGA and the adaptive DPD system.

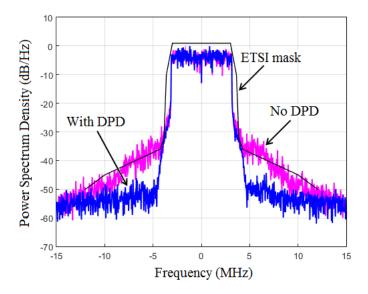

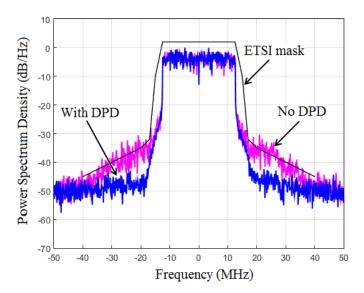

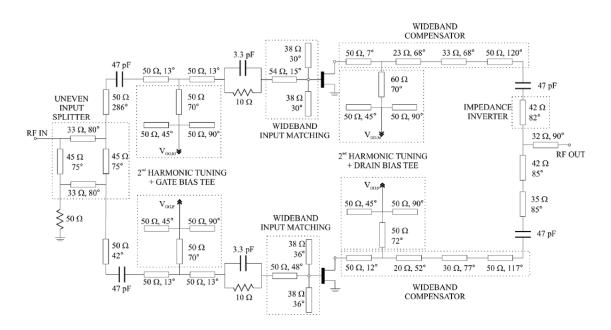

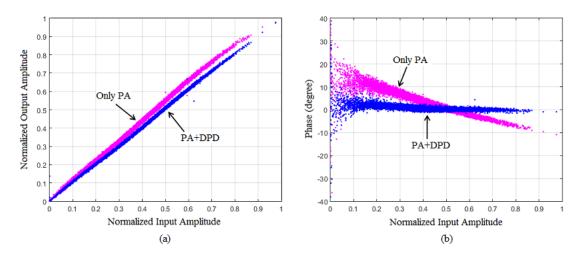

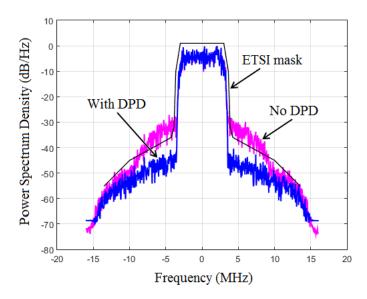

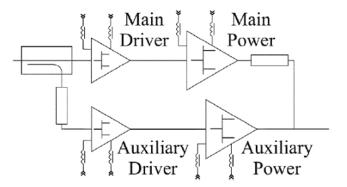

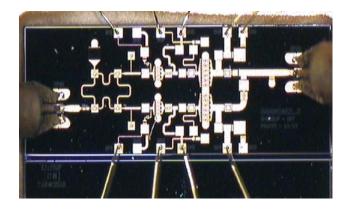

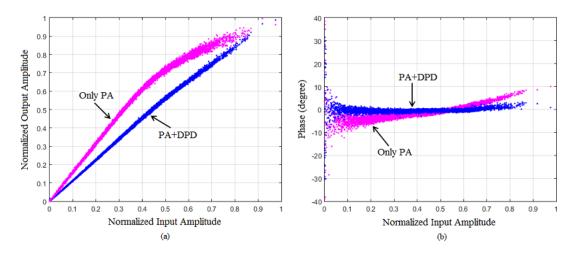

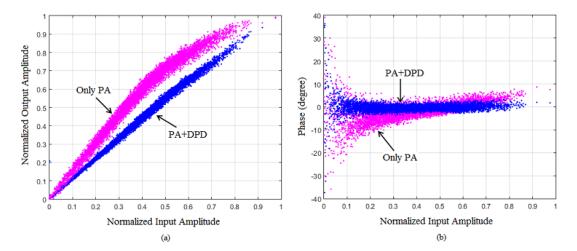

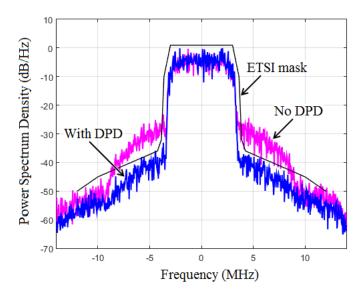

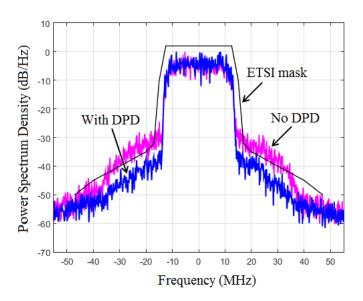

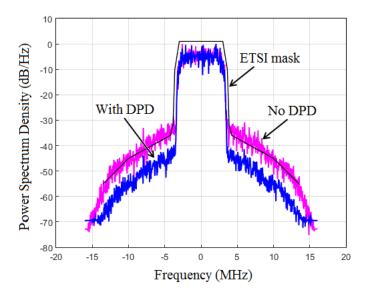

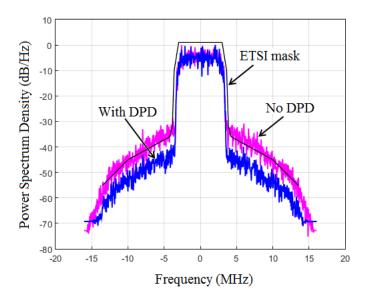

The linearization of 4 PAs with DPD technique has been introduced: for the hybrid class AB PA operating at 2.6 GHz with a WiMAX testing signal, 33.7 dBm average power, 29.6 % drain efficiency, 13 dB ACPR and 9 dB NMSE improvement have been obtained; for the hybrid Doherty PA operating at 3.4 GHz with an I/Q testing signal, 35.0 dBm average power, 36.8 % drain efficiency, 12 dB ACPR and 13 dB NMSE improvement have been obtained; for the MMIC class AB PA operating at 7 GHz with an I/Q testing signal, 29.4 dBm average power, 25.7 % drain efficiency, 12 dB ACPR and 12 dB NMSE improvement have been obtained; for the two-stage PA operating at 24 GHz with an I/Q testing signal, 23.5 dBm average power, more than 14.0 % drain efficiency, 11 dB ACPR and 11 dB NMSE improvement have been obtained.

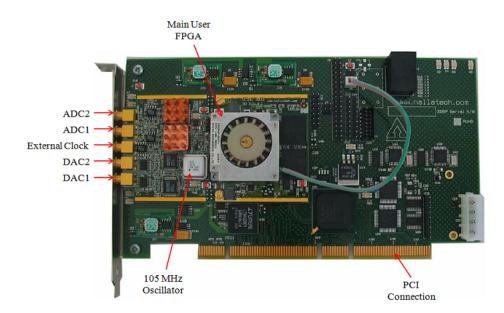

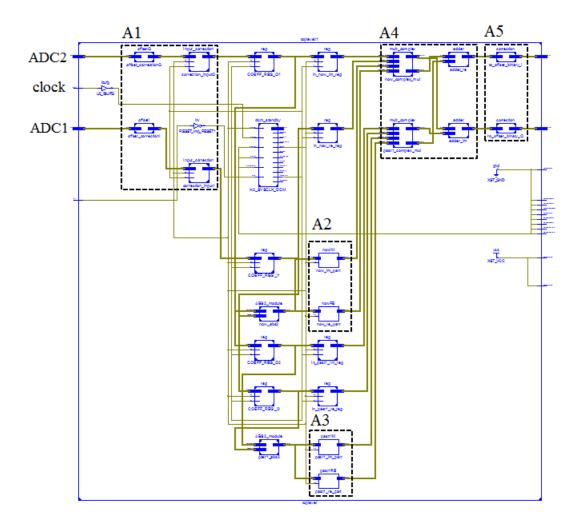

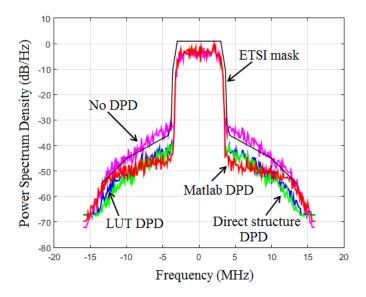

The DPD algorithm has been implemented on FPGA with two methods based on LUT and a direct structure with only adders and multipliers. The block RAM on the FPGA board is chosen as the table in the LUT methods. The linearization performance for these three methods is similar. The test PA is the hybrid Doherty PA mentioned above and the test signal is the I/Q signal with 7.4 dB PAPR. 35.1 dBm average power, 36.8 % efficiency, 11 dB ACPR and 11 dB NMSE improvement have been obtained. The cost of logic resources for the direct structure method is the largest with 1,172 flip-flops, while the number of flip-flops for the two LUT methods is 263 and 583.

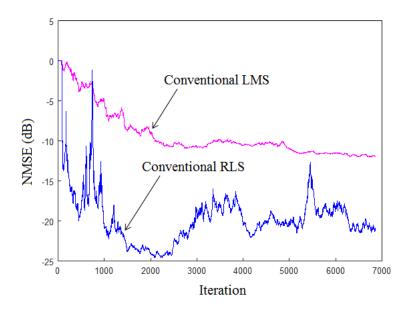

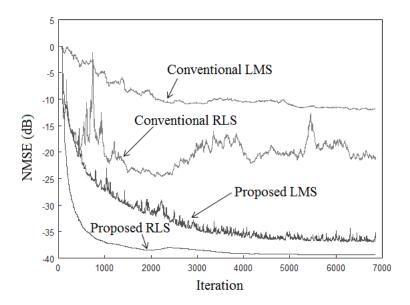

A new adaptive algorithm has been proposed in this thesis for the adaptive DPD

system. This new algorithm improves the performance in extracting the model parameters in complex number domain. With the experimental data from a combined class AB PA, the final accuracy of the model extracted by the new algorithm has been improved from -20 dB to about -40 dB and the converge speed is faster.

## Acknowledgments

I want to thank Prof. Marco Pirola and Prof. Vittorio Camarchia, my tutors, for all their help and guidance throughout my PhD carrier. It is a great pleasure working with such knowledgeable and experienced professors. I am grateful to have an opportunity to learn from them.

Roberto Quaglia, a research assistant in this lab group, provided me huge assistance during my work. I am very grateful for his willingness to always give me a help whenever I need.

To all my friends at Politecnico di Torino, thanks for making here a great place to study.

I would like to thank my parents for their love and support. Without you I would not be where I am today.

# Abbreviation

| ACPR                 | Adjancent Channel Power Ratio                   |

|----------------------|-------------------------------------------------|

| ADC                  | Analog to Digital                               |

| CLB                  | Configurable Logic Block                        |

| DAC                  | Digital to Analog                               |

| DSP                  | Digital Signal Processing                       |

| $\mathbf{DUT}$       | Device Under Test                               |

| ETSI                 | European Telecommunications Standards Institute |

| FPGA                 | Field Programmable Gate Array                   |

| $\operatorname{GaN}$ | Gallium Nitride                                 |

| GPIB                 | General Purpose Interface Bus                   |

| HEMT                 | High Electron Mobility Transistor               |

| IMD                  | Intermodulation Distortion                      |

| $\mathbf{LMS}$       | Least Mean Square                               |

| $\mathbf{LUT}$       | Look Up Table                                   |

| $\mathbf{LS}$        | Least Square                                    |

| MMIC                 | Monolithic Microwave Integrated Circuit         |

| NMSE                 | Normalized Mean Square Error                    |

| OFDM                 | Orthogonal Frequency Division Multiplexing      |

| PA                   | Power Amplifier                                 |

| PAE                  | Power Added Efficiency                          |

| PAPR                 | Peak to Average Power Ratio                     |

| PCI                  | Peripheral Component Interconnect               |

| $\mathbf{QAM}$       | Quadrature Amplitude Modulation                 |

| RFPA                 | Radio Frequency Power Amplifier                 |

| RLS                  | Recursive Least Square                          |

| RTL                  | Register Transfer Level                         |

|                      |                                                 |

# Table of contents

| A        | Abstract        |                                        |    |  |  |

|----------|-----------------|----------------------------------------|----|--|--|

| A        | Acknowledgments |                                        |    |  |  |

| 1        | Pov             | ver Amplifier Overview                 | 1  |  |  |

|          | 1.1             | Power Gain and Efficiency              | 2  |  |  |

|          | 1.2             | Power Amplifier Nonlinearity           | 3  |  |  |

|          |                 | 1.2.1 Power Amplifier Classification   | 4  |  |  |

|          |                 | 1.2.2 Distortion due to nonlinearity   | 6  |  |  |

|          | 1.3             | AM/AM and AM/PM Characteristics        | 8  |  |  |

|          | 1.4             | Memory Effects                         | 10 |  |  |

|          |                 | 1.4.1 Short-Term Memory Effects        | 10 |  |  |

|          |                 | 1.4.2 Long-Term Memory Effects         | 11 |  |  |

| <b>2</b> | Pov             | ver Amplifier Linearization Techniques | 12 |  |  |

|          | 2.1             | Power Back-off                         | 13 |  |  |

|          | 2.2             | LINC                                   | 14 |  |  |

|          | 2.3             | Feedforward                            | 15 |  |  |

|          | 2.4             | Feedback                               | 16 |  |  |

|          | 2.5             | Baseband Digital Predistortion         | 18 |  |  |

| 3        | Bas             | beband Digital Predistortion           | 20 |  |  |

|          | 3.1             | Basic Principle                        | 21 |  |  |

|          | 3.2             | DPD implementation                     | 25 |  |  |

|          | 3.3             | DPD Architecture                       | 26 |  |  |

|          |                 | 3.3.1 Direct Learning Architecture     | 26 |  |  |

|          |                 | 3.3.2 Indirect Learning Architecture   | 27 |  |  |

|          | 3.4             | DPD problems                           | 27 |  |  |

| 4        | Pov             | ver Amplifier Behavioral models        | 29 |  |  |

|          | 41              | Behavioral models                      | 30 |  |  |

|          | 4.2 | Figure of Merit                                        |     | • | 31 |

|----------|-----|--------------------------------------------------------|-----|---|----|

|          |     | 4.2.1 NMSE                                             |     |   | 32 |

|          |     | 4.2.2 ACPR                                             |     |   | 33 |

|          | 4.3 | Even-order Terms in the Polynomial                     |     |   | 34 |

|          | 4.4 | Memoryless models                                      |     |   | 35 |

|          |     | 4.4.1 Memoryless polynomial model                      |     |   | 36 |

|          |     | 4.4.2 LUT model                                        |     |   | 37 |

|          | 4.5 | Models with memory                                     |     |   | 38 |

|          |     | 4.5.1 Full Volterra model                              |     |   | 38 |

|          |     | 4.5.2 Memory polynomial model                          |     |   | 39 |

|          |     | 4.5.3 Generalized Memory Polynomial Model              |     |   | 40 |

|          |     | 4.5.4 Dynamic Deviation Reduction-based Volterra Model |     |   | 41 |

|          |     | 4.5.5 Rational function                                |     |   | 43 |

|          |     | 4.5.6 Hammerstein Model                                |     |   | 44 |

|          |     | 4.5.7 Wiener Model                                     |     |   | 45 |

|          | 4.6 | Model Parameters Identification technique              |     |   | 46 |

|          |     | 4.6.1 Least Square Method                              |     |   | 47 |

|          |     | 4.6.2 Model Identification Examples using LS method    |     |   | 48 |

|          | 4.7 | Model Comparison and Selection                         |     |   | 50 |

| _        |     |                                                        |     |   |    |

| <b>5</b> |     | ware Simulation based on Matlab                        |     |   | 53 |

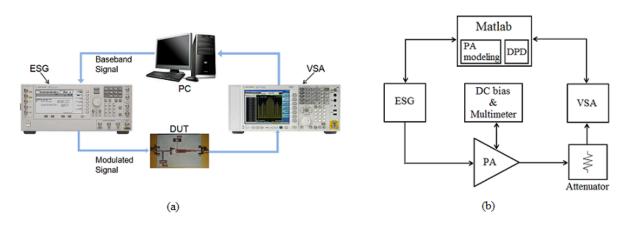

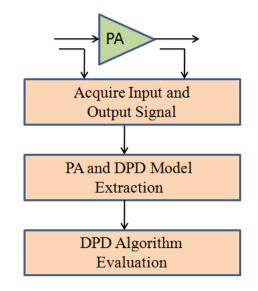

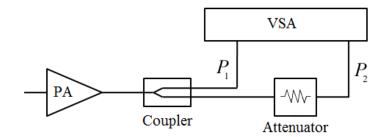

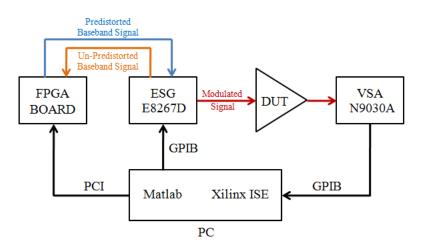

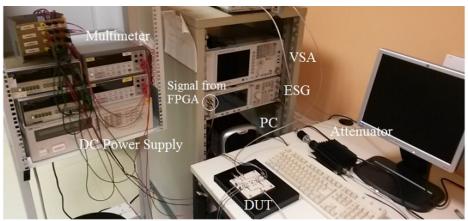

|          | 5.1 | Testbench Description                                  |     |   | 54 |

|          | 5.2 | Simulation Procedure                                   |     |   | 55 |

|          |     | 5.2.1 Attenuation Measurement                          |     |   | 56 |

|          |     | 5.2.2 Output Data Acquirement                          |     |   | 57 |

|          |     | 5.2.3 DPD Builder                                      |     |   | 58 |

|          |     | 5.2.4 DPD Performance                                  |     |   | 58 |

|          | 5.3 | Ideal DPD Simulated in Matlab                          |     |   | 59 |

|          | 5.4 | Experimental Results                                   |     | • | 61 |

|          |     | 5.4.1 Hybrid Class AB Amplifier                        |     | • | 62 |

|          |     | 5.4.2 Hybrid Doherty Amplifier                         |     |   |    |

|          |     | 5.4.3 MMIC Class AB Amplifier                          |     |   | 71 |

|          |     | 5.4.4 Two-stage Amplifier                              |     | • | 74 |

|          | 5.5 | Conclusion                                             | • • | • | 78 |

| 6        | Har | dware Implementation based on FPGA                     |     |   | 79 |

| U        | 6.1 | FPGA Introduction                                      |     |   | 80 |

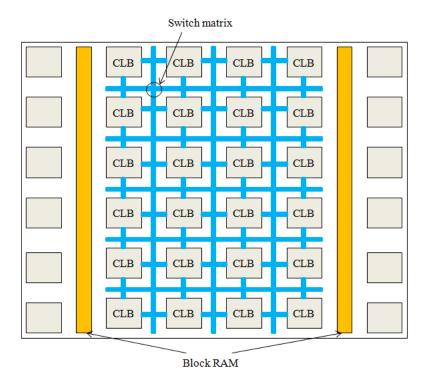

|          | 0.1 | 6.1.1 Configurable Logic Blocks                        |     |   | 81 |

|          |     | 6.1.2 ADC and DAC                                      |     |   | 82 |

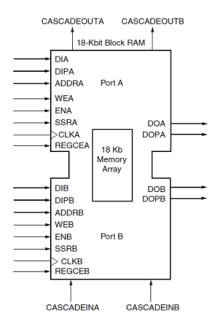

|          |     | 6.1.3 Block RAM                                        |     |   | 82 |

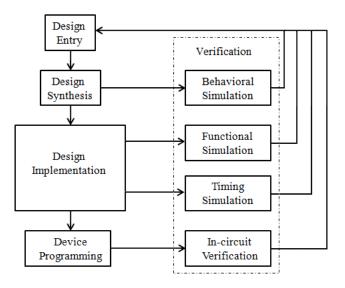

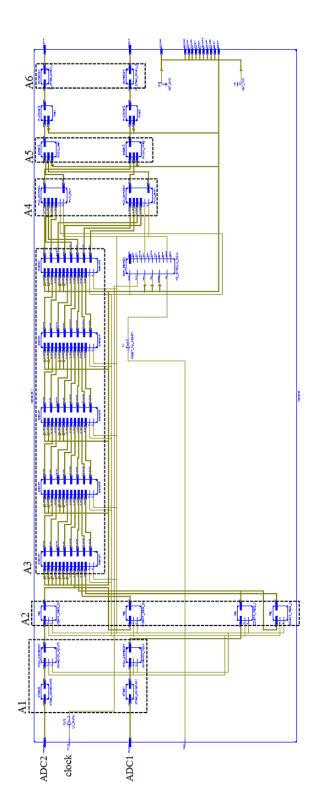

|          | 6.2 | FPGA Design Procedures                                 |     |   | 84 |

|          |     |                                                        |     |   |    |

|          | 6.3    | Implementation Methods                            | 85  |

|----------|--------|---------------------------------------------------|-----|

|          |        | 6.3.1 LUT method                                  | 85  |

|          |        | 6.3.2 Direct Multiple and Add Method              | 88  |

|          | 6.4    | Testbench Description and Experimental Procedures | 90  |

|          | 6.5    | Experimental Results                              | 91  |

|          |        | 6.5.1 Direct Multiple and Add Method              | 91  |

|          |        | 6.5.2 LUT Method                                  |     |

|          | 6.6    | Comparison and Conclusion                         |     |

|          |        |                                                   |     |

| <b>7</b> | Ada    | ptive Predistorter Design 1                       | .02 |

|          | 7.1    | Adaptive Algorithm                                | 103 |

|          |        | 7.1.1 LMS                                         | 103 |

|          |        | 7.1.2 RLS                                         | 106 |

|          | 7.2    | Adaptive Digital Predistortion Based on RLS       | 109 |

|          | 7.3    | Simulation results with RLS algorithm             | 110 |

|          |        | 7.3.1 Algorithm Modification for Complex Number   | 111 |

| 8        | Cor    | clusion and Future Work 1                         | .14 |

| Bi       | ibliog | graphy 1                                          | .17 |

## Chapter 1

## **Power Amplifier Overview**

In a typical wireless transmitter system, the radio frequency power amplifier (RF PA) is one of the most important components. A RF PA is a power device which can convert DC supply into RF power. It is used to amplify the signal to a significant power before transmitting it to the antenna. In the early days, RF power was generated by spark, arc and alternator techniques. From the late 1920s, vacuum tube transmitters were dominant for several decades. At the end of the 1960s, discrete solid state RF power devices began to appear. Since then, variety of new solid state RF power devices, such as MOSFET, HEMT, HFET, HBT, became mature and were used in industrial applications. These new devices have extended the working bandwidth and have made high output power level available.

Linearity, power efficiency and bandwidth are the three figures of merit that need to be considered when we design the PA for the modern wireless transmission applications. The original intention of PAs is to generate higher power, therefore, the output power level, as well as the power gain, are the PA's primary performance. Moreover, to limit the power consumption, efficiency is also essential to be high. Power efficiency is directly associated with the cost of the communication infrastructure.

On the other hand, high linearity is required to minimize the distortions caused by the PA. Less distortion means higher integrity of the signal during the transmission process. However, the linearity has an inherent conflict with the efficiency. PA with high linearity, like Class A PA, presents poor efficiency performance. Moreover, efficient PA architectures, such as Doherty, envelope tracking, have severe linearity problem. Therefore, linearity improvement techniques are needed for these high efficient PAs to guarantee the linearity.

### **1.1** Power Gain and Efficiency

In general, a power amplifier is defined as a device that increases the power of an arbitrary input signal. The added power is transferred to the output signal and is taken from a DC supply [2]. Ideally, all supplied power should be converted into RF power. However, it is not the case in reality and only part of the supplied power can be converted into the output power. Power efficiency is introduced to indicated how much of the supplied power is converted. The efficiency can be described in two ways: drain efficiency and power added efficiency [3]. Drain efficiency is more general and is defined as

$$\eta_d = \frac{P_{out}}{P_{DC}} \tag{1.1}$$

where  $P_{out}$  is the power delivered to the load and  $P_{DC}$  is the power taken from the supply. The drain efficiency does not take the input power into consideration. On the other hand, the power added efficiency (PAE) regards the input power as a power loss which should be subtracted from the output power. Therefor, the PAE is defined as

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{1.2}$$

where  $P_{in}$  is the input power. Power added efficiency describes the performance of the PA more accurately by including also the input power. It is also a function of the power gain as show in equation (1.3). PAE is a reasonable description of PA's performance when the power gain is high. However, it could be negative for a PA with a low power gain.

$$PAE = \frac{P_{out} - P_{out}/G}{P_{DC}} \tag{1.3}$$

where  $G = P_{out}/P_{in}$  is the power gain of the power amplifier. The power gain of a two-port device, for instance a power amplifier, is the ratio of the output power to the input power. It is usually represented in decibel as

$$G_{dB} = 10 \ \log_{10}(\frac{P_{out}}{P_{in}}) \tag{1.4}$$

In the meanwhile, the power itself can also be represented in decibel form, called dBm, which is ratio between the power and 1 mW:

$$P_{dBm} = 10 \ \log_{10}(\frac{P}{1mW}) \tag{1.5}$$

Typically, the efficiency of a PA, both drain efficicy and PAE, reaches its maximum

value at saturated power and decreases rapidly as the power decreases. However, at high power region, the PA faces a linear problem. The nonlinearity will be discussed in next section.

### **1.2** Power Amplifier Nonlinearity

In common sense, the word linearity describes a mathematical abstraction or relationship, f(x), which should satisfy the following two properties: homogeneity and superposition.

Homogeneity:

$$f(\alpha x) = \alpha f(x)$$

Superposition:  $f(\alpha x + \beta y) = \alpha f(x) + \beta f(y)$

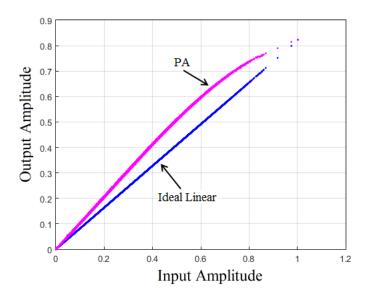

where  $\alpha$ ,  $\beta$  are two constant numbers. If two quantities have a linear relation, they will be proportional to each other, called homogeneity. Therefore, if a power amplifier is said to be linear, the output power level should have a constant gain over each input power level and the characteristic of the PA should be a straight line. However, it is not a straight line for a real PA and there is compression at high input power level, as shown in Figure 1.1(b) the solid blue line. The nonlinear distortion of a power amplifier is caused mainly due to the output power limitation. Therefore, the nonlinear behavior is more obvious when the output power tends to the saturation.

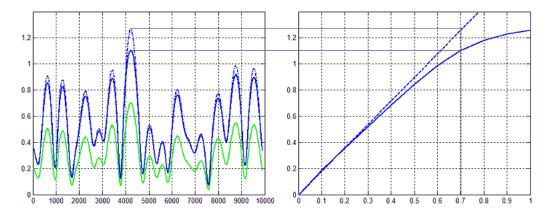

Figure 1.1. (a) Amplitude as a function of time, the green line is the input amplitude, the solid blue line is the real output amplitude and the dashed blue line is the ideal linear output amplitude. (b) AM/AM characteristic of a power amplifier, dashed line is ideal linear case and the solid line is the real case

Figure 1.1 depicts clearly the nonlinearity of a PA in time domain. In Figure 1.1(a), the green line is the input signal amplitude in time domain. If this signal passes through a linear PA with constant power gain, the output will be the dashed blue line. However, in real case, the output is the solid blue line. We can see that at lower input power level the dashed and solid blue lines coincide, meaning that the PA works with linear behavior. In the meanwhile, at some top peaks of the wave (the highest point in Figure 1.1(a) as an example), where the input power level is high, the solid line is lower than the dashed line, meaning that the PA is with compression and is not linear with high input power.

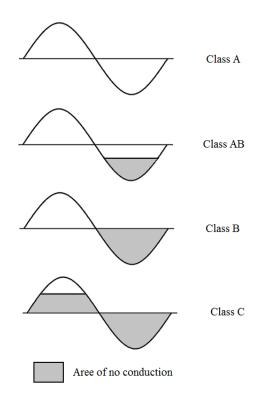

#### **1.2.1** Power Amplifier Classification

The class of operation of a PA has a significant effect on the linearity of the PA. Class A amplifiers are the most linear while Class AB amplifiers are mildly nonlinear and Class C, D , E amplifiers have highly nonlinear behavior.

A Class A PA is defined as a PA in which output current flows for the full-cycle (360°) of the input signal. In other words, the transistor remains forward biased during the whole input cycle. The class A amplifier is the most common and simplest form of PA that uses the switching transistor in the standard common emitter circuit configuration. The transistor stays always in "ON" state so that the current flows throughout one complete cycle of the input signal, producing minimum distortion and maximum amplitude to the output.

A class B amplifier has zero DC bias so that the amplifier is not in its active region when the input signal is in the range near to 0. In this way, class B amplifier has a significant advantage over class A amplifier in that no current flows through the transistor when there is no input signal at Base. Therefore, no power is dissipated in the transistor when there is no signal present while class A amplifier stage dissipates lots of heat even without input signal. However, there is a critical drawback of class B amplifiers which is that they suffer from an effect commonly known as *Crossover Distortion* [3].

The class AB amplifier is a compromise between the class A amplifier and the class B amplifier. It uses two diodes between Base and Emitter to build a voltage difference or bias voltage. The class AB amplifier attempts to solve the distortion of the crossover region that the class B amplifier exhibits at a cost of efficiency decrease. Any input signal will make the transistor to operate normally in its active region, minimizing or even eliminating the crossover distortion which is present in class B

configurations. But the efficiency of class AB amplifier is smaller than that of class B, with a value between that of class A and class B amplifiers.

In a class C amplifier configuration, the transistor being biased with negative voltage, the working point is far beyond the cut-off point. So it operates for less than half of the input cycle and the resulting output signal is strongly non-linear. The efficiency of a class C amplifier is very high, reaching ideally 100% in best cases, however it generates strong crossover distortions too.

Figure 1.2. Comparison of output signals of different amplifier classes of operation

Figure 1.2 clearly illustrate the output signals for different classes of operation. The gray area is where no signal is conducted.

Class D amplifiers [1] are switching mode amplifiers. They have at least two transistors operating as switches to create a pulse width modulation (PWM) signal at the output of the transistors. The generated signal is then low pass filtered passing the first harmonic to the load. As the current is flowing just through the switched-on active elements, the theoretical efficiency is 100% if the active devices are ideal. Nevertheless, ideal transistors are not existed and there is also power loss due to saturation, switching speed and junction capacitance. The real efficiency is less than 100%.

| Class of operation | Efficiency(%)               | Linearity                   |

|--------------------|-----------------------------|-----------------------------|

| А                  | 50                          | Good                        |

| AB                 | Between Class A and Class B | Between Class A and Class B |

| В                  | 78.5                        | Moderate                    |

| С                  | 100                         | Poor                        |

| D                  | 100                         | Poor                        |

Table 1.1.

Comparison of different class of operation in terms of efficiency and linearity

Table 1.1 summarizes the linearity situation of different classes of operation for a PA. The linearity varies with different amplifier classed.

#### 1.2.2 Distortion due to nonlinearity

#### Amplitude distortion

The nonlinear behavior of a PA can be modeled as a power series:

$$v_o = a_1 v_i + a_2 v_i^2 + a_3 v_i^3 \cdots$$

(1.6)

where  $a_1, a_2, a_3$  are coefficients and  $v_i, v_o$  are the input and output of the power amplifier, respectively. When the input signal has one single frequency,  $v_i = V \cos(\omega t)$ , the  $v_o$  will be

$$v_{o} = a_{1}V\cos(\omega t) + a_{2}V^{2}\cos^{2}(\omega t) + a_{3}V^{3}\cos^{3}(\omega t) + \cdots$$

=  $\frac{1}{2}a_{2}V^{2} + (a_{1}V + \frac{3}{4}a_{3}V^{3})\cos(\omega t)$

+  $\frac{1}{2}a_{2}V^{2}\cos(2\omega t) + \frac{1}{4}a_{3}V^{3}\cos(3\omega t) + \cdots$  (1.7)

In (7.2), the output signal consists not only of the signal with the input signal frequency but also of a DC component and the harmonic components. Even with a ideal filter that can cancel the DC and harmonic parts, the amplifier gain is no longer the linear gain  $a_1$ , but is  $a_1 + \frac{3}{4}a_3V^2$ . This new gain is no longer constant but is a function of input signal magnitude V. If  $a_3 > 0$ , the amplifier will be with gain expansion. In general, power amplifier has the feature of gain compression with  $a_3 < 0$ .

#### Intermodulation distortion

The intermodulation distortion is explained with a two-tone signal which is represented by:

$$v_i = V_1 cos(\omega_1 t) + V_2 cos(\omega_2 t) \tag{1.8}$$

where  $V_1$ ,  $V_2$  are the magnitudes of the two tones, and  $\omega_1$ ,  $\omega_2$  are their angle frequencies. The PA's nonlinearity is still modeled by a third order power series, expressed as:

$$v_o = a_1 v_i + a_2 v_i^2 + a_3 v_i^3 \cdots$$

(1.9)

Therefore, the output of the PA as a function of input signal can be obtained by substituting (1.8) in (1.9):

$$\begin{aligned} v_o &= \frac{1}{2} a_2 V_1^2 + \frac{1}{2} a_2 V_2^2 \\ &+ \left[ \left( a_1 + \frac{3}{4} a_3 V_1^2 + \frac{3}{4} a_3 V_2^2 \right) V_1 cos(\omega_1 t) + \left( a_1 + \frac{3}{4} a_3 V_2^2 + \frac{3}{4} a_3 V_1^2 \right) V_2 cos(\omega_2 t) \right] \\ &+ \left[ \frac{1}{2} a_2 V_1^2 cos(2\omega_1 t) + \frac{1}{2} a_2 V_2^2 cos(2\omega_2 t) \right] + \left[ \frac{1}{4} a_3 V_1^3 cos(3\omega_1 t) + \frac{1}{4} a_3 V_2^3 cos(3\omega_2 t) \right] \\ &+ \left[ a_2 V_1 V_2 cos((\omega_2 - \omega_1) t) + a_2 V_1 V_2 cos((\omega_2 + \omega_1) t) \right] \\ &+ \left[ \frac{3}{4} a_3 V_1^2 V_2 cos((2\omega_1 - \omega_2) t) + \frac{3}{4} a_3 V_1 V_2^2 cos((2\omega_2 - \omega_1) t) \right] \\ &+ \left[ \frac{3}{4} a_3 V_1^2 V_2 cos((2\omega_1 + \omega_2) t) + \frac{3}{4} a_3 V_1 V_2^2 cos((2\omega_2 + \omega_1) t) \right] \end{aligned}$$

(1.10)

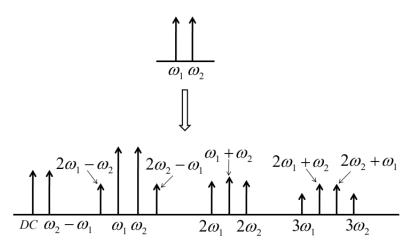

Equation (7.6) can be illustrated more clearly in Figure 1.3 which is the frequency domain representation of the output signal. The output signal consists of the useful signal, the DC component, harmonics and intermodulation products [6]. The useful signal is the signal at the fundamental frequency. The harmonics and the secondorder intermodulation components can be canceled by filters. However, there are third-order intermodulation components which are close in frequency to the fundamental frequency. These intermodulation distortions thus cannot be removed simply by filters.

Figure 1.3. Frequency domain output of a nonlinear PA driven by a two-tone signal

### **1.3** AM/AM and AM/PM Characteristics

AM/AM and AM/PM characteristics [7] are the basic curves to characterize the linearity of the PA. They get their name from the fact that amplitude modulation (AM) within the input signal results in amplitude and phase modulation (AM and PM) in the power amplifier gain. In a more general case, one PA is well described by four characteristics: amplitude to amplitude modulation (AM/AM) characteristic, the amplitude to phase modulation (AM/PM) characteristic, the phase to phase modulation (PM/PM) characteristic, and the phase to amplitude modulation (PM/AM) characteristic. Since phase modulated signals are immune to the distortions, only AM/AM and AM/PM characteristics are considered.

Let's consider a PA with a modulated signal whose baseband input and output signal x and y are

$$\begin{aligned} x &= x_I + j x_Q \\ y &= y_I + j y_Q \end{aligned}$$

(1.11)

where  $x_I$ ,  $y_I$  are the in-phase components and  $x_Q$ ,  $y_Q$  are the quadrature components. Therefore, the magnitude and phase of the instantaneous signal gain can be expressed as

$$|G| = \frac{|y|}{|x|} = \frac{\sqrt{y_I^2 + y_Q^2}}{\sqrt{x_I^2 + x_Q^2}}$$

(1.12)

$$\angle G = \tan^{-1}\left(\frac{y_Q}{y_I}\right) - \tan^{-1}\left(\frac{x_Q}{x_I}\right) \tag{1.13}$$

Figure 1.4. Sample AM/AM characteristic of a power amplifier

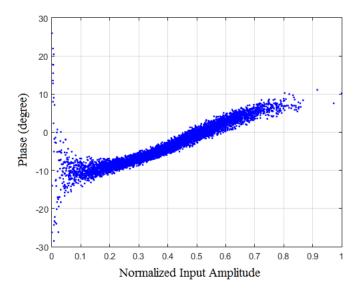

Figure 1.5. Sample AM/PM characteristic of a power amplifier

The AM/AM characteristic of PA can be obtained by plotting the amplitude of the output signal as a function of the corresponding input signal. Similarly, the AM/PM

characteristic of the PA is the phase of the power gain as a function of the instantaneous input signal. Figure 1.4 and Figure 1.5 are an example of the AM/AM and AM/PM characteristics, respectively. These two figures provide a very clear view of the linearity of the PA.

### **1.4** Memory Effects

Memory effects [8–11] in a PA can be explained as that the output of the PA at time  $t_o$  is a function not only of the input at time  $t_o$  but also of the inputs at some other previous time instants. In other words, the past input signals also contribute to the current output value. The influence of the past input signals is not infinite and the memory depth describes how long of the past input signals that contribute. The relation between the input and the output of a PA with memory can be expressed as

$$y(t_o) = f(x(t_o), x(t_o - 1), \cdots x(t_o - \tau))$$

(1.14)

where the memory depth  $\tau$  is a positive constant since every physical system is causal. From (1.14), we can see that the outputs corresponding to the same input value may be different since the past input signals may be different. Therefore, the characteristics of the output signal as a function of input signal, both in magnitude and phase, for a system with memory are not a single line as shown in Figure 1.4, Figure 1.5.

Memory effect is mainly a result of energy storage in the device. A simple example that exhibits memory is the RC circuit in which the current flowing in the circuit depends on how much charge accumulated on the capacitor. The sources of memory effects [8, 12–14] are not unique and they can be classified into two groups according to the timescale of the occurrence: short-term memory effects and long-term memory effects.

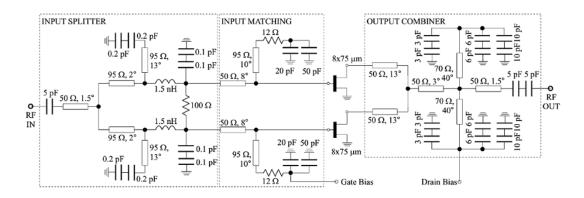

#### **1.4.1** Short-Term Memory Effects

Short-term memory effects are those that occur with a timescale same with the RF carrier frequency. The main sources of short-term memory effects are matching network and device capacitance. The matching networks at both input and output of a PA are essential to keep the maximum power transfer. However, these matching networks contain capacitors, inductors and transmission lines which present dynamic

properties. Therefore, the matching network should be carefully designed to reduce the memory impact.

The transistors themselves have parasitic capacitance and inductance which will contribute to the memory effect. These parasitic reactive components are associated with the charge transfer delay in the channel of the transistors. Therefore, the transistor is usually modeled with reactive components in the small-signal model. Generally, we should try to minimize the parasitic capacitance and inductance to reduce the delay.

### 1.4.2 Long-Term Memory Effects

Similar to the short-term memory effects definition, the long-term memory effects are those that occur with a timescale much longer. These kinds of sources include thermal effects [15] and charge trapping. The PA is not ideal 100% energy transferred and some of the energy will be wasted as heat which will change the temperature of the PA. This temperature change is relatively slow compared to the carrier frequency. However, this change can still affect some temperature dependent parameters, such as channel mobility, and the behavior of the PA will be different even with the same input signal.

Charge trapping is mainly due to the imperfect semiconductor materials and processing and these imperfections happen mainly at the interfaces of two dissimilar semiconductors. Then the local potential will be disrupted. As a result, the charge carriers may be trapped and released later, causing a change of current flow, if the potential conditions are different. This will change the behavior of the PA, contributing to the memory effects.

## Chapter 2

# Power Amplifier Linearization Techniques

RF power amplifiers are the main cause of the nonlinear behavior in the modern wireless transmission system. Nowadays, spectrum efficient modulation techniques, such as orthogonal frequency division multiplexing (OFDM), are required in modern communication systems. However, these non-constant envelope modulation are very sensitive to the nonlinearity. The signal with non-constant envelope generates intermodulation distortion (IMD) when it passes the PA. The IMD power will interfere between adjacent channels which is an unwanted phenomenon.

Moreover, these efficient modulation techniques will lead to modulated signals with high peak-to-average power ratio (PAPR). The PA should operate with power backoff which will result with a drastically decreased efficiency. To ensure the high efficient operation, many techniques have been proposed in literature. Among them, the Doherty amplifier [16] is one of the most promising techniques for high efficiency operation with non-constant envelope modulated signal. It has several advantages in terms of relative simplicity of implementations and cost effectiveness. However, the linearity and efficiency of PAs usually present opposite performances. The Doherty amplifier operates with high efficiency often at the cost of poor linearity. Therefore, linearization techniques have to be used to compensate the nonlinear distortions generated by PAs.

Various techniques are available for this purpose, such as feedforward, feedback and analog predistortion. However these solutions suffer from complex circuitry and stability problems. The digital predistortion is one of the most useful and cost-effective linearization techniques, due to the already existing digital signal processing devices.

### 2.1 Power Back-off

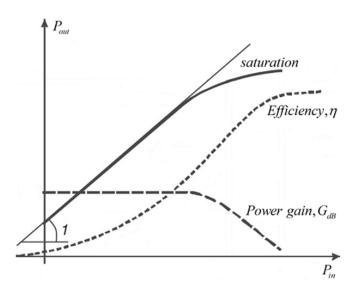

Figure 2.1 shows the typical performance of a power amplifier, including the magnitude response, the power gain and the efficiency. From the figure, we know that the PA is linear at the lower input power range while the linearity becomes worse with higher input power. Therefore, the simplest way to improve the linearity of the PA is to back-off the input power to the linear region. This is called the power back-off technique [1].

Figure 2.1. Basic AM/AM characteristic of a power amplifier

Another explanation is more quantitative with mathematical equations. Since every device with nonlinear characteristic can be expanded with Taylor series, we can model the PA with the following expression:

$$v_{out} = V_0 + a_1 v_{in} + a_2 v_{in}^2 + \cdots$$

(2.1)

where  $V_0$  is the DC part which can be blocked in RF power amplifiers,  $v_{in}$  and  $v_{out}$  are the input and output, respectively. Therefore, if the value of  $v_{in}$  reduces to a real low level, the linear term  $a_1v_{in}$  will dominate over the other power terms, leading to a more linear characteristic.

The power back-off method is still widely used for low-power, small size PAs. However, when back-off to the linear region, the efficiency of the PA is degraded, especially for signals with high peak to average power ratio (PAPR). Therefore, the power back-off solution has no effect to overcome the trade-off between linearity and efficiency. It improves the linearity by sacrificing the efficiency since the efficiency is best at saturation (as shown in Figure 2.1). To obtain both linearity and efficiency, other linearization techniques are needed.

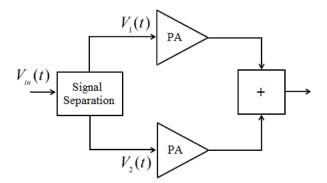

### 2.2 LINC

LINC refers to Linear amplification using Nonlinear Components [17–20], which can realize a linear amplification with high efficient nonlinear amplifiers. As illustrated in Figure 2.2, the basic idea of LINC is to separate the amplitude modulated input signal into two phase modulated signals. In this way, the non-constant envelope modulation, which are very sensitive to the PA's nonlinearity, will be replaced by the constant envelope modulation. Therefore, the resulted modulated signals can be amplified separately by two efficient PAs without any concern of distortion. These two efficient PAs should be ideally identical, with same characteristics and the delay in the two channels should also be matched. Finally, the amplified signals from the two channels should be combined to produce the amplified replica of the input signal.

Figure 2.2. The basic principle of LINC

Consider first a amplitude modulation signal:

$$V_{in}(t) = a(t)\cos(2\pi f_c t + \varphi(t)) \tag{2.2}$$

where a(t) is the envelope of the signal. When passing this signal into the signal separation component, it will be divided into two constant-amplitude signals  $V_1(t)$

and  $V_2(t)$ , expressed as:

$$V_1(t) = 0.5V\cos(2\pi f_c t + \varphi(t) + \theta(t)) \tag{2.3}$$

$$V_2(t) = 0.5V \cos(2\pi f_c t + \varphi(t) - \theta(t))$$

(2.4)

where  $\theta(t) = \cos^{-1}(a(t)/V)$ , V is the maximum amplitude of a(t).

The concept of LINC has appeared since 1930s. However, at that time, the separated signals in LINC technique were not accurate since it was difficult to generate the  $\theta(t)$  with the analog circuits. The modern digital signal processing technique can solve this problem and can make a significant improvement for the accuracy. Nevertheless, there are still problems. For instance, the two channels should be ideally matched.

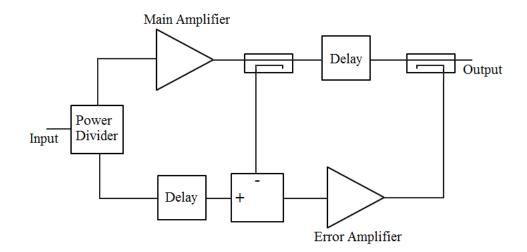

### 2.3 Feedforward

Feedforward [21–25] is an old linearization technique which applies the feedback correction at the output of the PA. It was first introduced by Howard Black in 1923 at Bell Telephone Laboratories. Figure 2.3 shows the basic principle of feedforward technique.

Figure 2.3. Basic schematic of the feedforward technique

The input signal is first divided into two signals, one being amplified by the main

amplifier as required, the other one being used as a reference with the same delay with the main amplifier. The delayed reference signal is then subtracted from the coupled signal from the main amplifier. Therefore, if there is no amplitude and phase distortion, the subtraction procedure will have a zero value. Otherwise, there will be a error signal after the subtraction. The error signal is then fed to the error amplifier to be amplified back to the original level. The amplified error signal is the compensation to the output signal from the main amplifier to get the linear and amplified signal at the output of the feedforward system.

The feedforward technique can remove both the amplitude and phase distortions of the PA and is immune to memory effects. Compared to the feedback technique, the feedforward method can provide the same benefits of feedback technique without the problem of bandwidth limitation. However, all theses come with costs. Firstly, the error amplifier in Figure 2.3 should be linear since the gain errors introduced by the error amplifier can not be compensated. Moreover, it should also be powerful enough to amplify the error signal to the same level of the main signal. Secondly, the delay lines must be carefully designed to produce the accurate delay and to match the signals in the two channels. The linearization performance is highly dependent on the precision of the signals matching in the two channels. Another aspect, the feedforward technique works with poor efficiency and has high demand on the hardware. In addition, feedforward can not linearize the PA operated at its saturation power.

### 2.4 Feedback

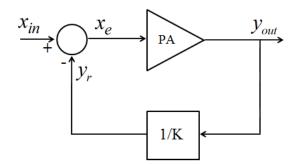

Feedback technique [1,26], which is based on the knowledge of dynamic control system, was also mentioned by Howard Black in 1927 after the failing of the feedforward idea. It has been widely used in many systems since it has been mentioned. The basic idea of feedback technique is that a part of output signal is fed back to the input with a close loop. Therefore, the difference between feedforward and feedback techniques is that the former compares the error signal at the output of the PA, whereas the latter compares at the input. A general direct feedback linearization is illustrated in Figure 2.4.

In Figure 2.4, a negative feedback loop is used to linearize the PA. The loop consists of the PA with power gain G, a divider of gain 1/K and a comparator for signal subtraction.

Figure 2.4. General direct feedback system

A part of the output signal  $y_{out}$  from the PA is fed back to the input passing through the divider. The signal after the divider is

$$y_r = \frac{1}{K} y_{out} \tag{2.5}$$

The error signal,  $x_e$ , after the comparator is defined as

$$x_e = x_{in} - y_r \tag{2.6}$$

where  $x_{in}$  is the input signal. Therefore, the output signal after the amplifier is

$$y_{out} = Gx_e \tag{2.7}$$

Finally, combining all the equations, we will get a linear gain. Therefore, this close loop can force the output signal to be a replica of the input which makes the PA linear.

$$y_{out} = \frac{KG}{K+G} x_{in} \tag{2.8}$$

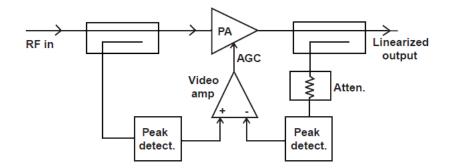

This simple technique is widely used in applications with low frequencies, in which, the time delay of the close loop is short enough and can be neglected. However, at RF, this delay will be comparable to the signal frequency and cannot ignored. In addition, at high frequencies, the phase of the PA gain varies rapidly with the frequency and usually this can lead to oscillation. Therefore, the direct feedback technique has a bandwidth limitation and works well only at low frequencies. To overcome this restriction, an indirect feedback technique [27] is applied, as shown in Figure 2.5.

In this technique, there are two peak detectors at both the input and output of the RF PA. Both the input and output signals are captured and down-converted to the IF frequency. Then the detected baseband signals are fed to a video differential amplifier where an error correction signal is generated. Then this error signal, as a

Figure 2.5. General indirect feedback system

driver, passes to a gain control of the amplifier. As a result, this loop will force the output envelope to be identical to the input envelope.

This technique still has a problem: the high order intermodulation products can not be corrected. This problem is inevitable because of the delay limitation of the feedback systems. Despite their good linearization performance, feedback techniques are still found a limited usage for the linearization of RF PAs.

### 2.5 Baseband Digital Predistortion

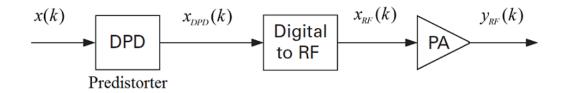

In these years, baseband digital predistortion (DPD) [28,29] becomes the preferred choice for the linearization of RF power amplifier because of its relative simplicity and good performance. Different from feedforward and feedback techniques, the DPD technique is achieved by placing a nonlinear block, called *Predistorter*, just in front of the PA as shown in Figure 2.6. The objective of this predistorter is to produce an inverse behavior of the PA.

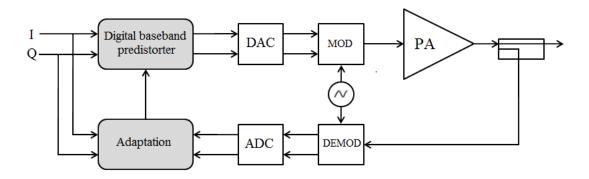

Figure 2.6. Digital transmitter with digital predistortion

Digital predistortion is now gaining worldwide popularity. It has smaller size and less cost compared to other linearization techniques. Digital predistortion can also be a standalone device which makes it more convenient in industrial applications. More details will be introduced in next chapter for digital predistortion.

## Chapter 3

# **Baseband Digital Predistortion**

The aim of studying distortions [8], caused by nonlinearity of the power amplifier, is to design a linearization architecture to minimize the distortions. There are many techniques mentioned in the previous chapter, among which the digital predistortion (DPD) is one of the most popular solution. The popularity of baseband DPD is mainly associated with its flexible implementation and good accuracy due to the implementation of digital signal processing techniques. Another attractive aspect is that the entire DPD system can be encapsulate into one standalone block. This will avoid redesigning the analog circuits when the DPD system is used.

FPGA is a good choice for implementing the DPD technique in wireless applications. It has many advantages in digital signal processing, including high speed processing, flexible implementation, high reliability and parallelism computation. Lookup Table (LUT) method is an efficient way to implement the predistorion function. The proposed DPD technique is not solely limited to FPGA and it can also be implemented based on other commercial products.

This chapter introduces the basic principle of the digital predistortion technique and the implementation issues of DPD for the RF wireless communication system. Two DPD architectures, direct and indirect learning architecture, are compared. With DPD, the PA has a significant improvement in linearity which can satisfy the highly linearity requirement of high efficient power amplifiers. However, digital predistortion also suffers from some problems, including the bandwidth expansion of the signal and additional energy consumption.

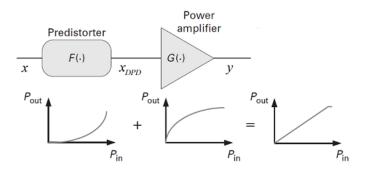

### **3.1** Basic Principle

The basic idea of digital predistortion [5, 28–31] is to introduce a nonlinear component, called *Predistorter*, just in front of the PA. The objective of this nonlinear block is to produces the nonlinear behavior which is the reverse of the PA's nonlinear behavior in both magnitude and phase. In this way, the predistorter will counteract the nonlinearity of the PA and the final behavior will be linear, as shown in Figure 3.1.

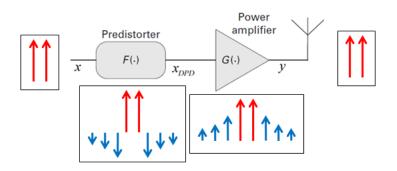

Figure 3.1. Basic principle of digital predistortion

Another interpretation of digital predistortion in frequency domain is to view the predistorter as a generator of intermodulation distortion (IMD) products. Since the PA is usually nonlinear, it will create IMD products. If the IMD products of the PA and the predistorter have the equal amplitude and 180 degree out of phase, the distortion will be cancelled, as shown in Figure 3.2 in which the downward arrow means the anti-phase.

Figure 3.2. Frequency domain interpretation of digital predistortion

In the following, the principle of DPD will be explained with mathematical equations. The predistorted signal, denoted as  $x_{DPD}$ , is

$$x_{DPD} = F(x), \tag{3.1}$$

where x is the input signal. The predistorted signal can be expressed in another form:

$$x_{DPD} = G_{DPD}(x) \cdot x, \qquad (3.2)$$

where  $G_{DPD}(x)$  can be seen as the nonlinear gain of the predistorter at point x, or it is the slope of the transfer function between  $x_{DPD}$  and x. The predistored signal will be fed to the PA and the output signal will be

$$y = G(x_{DPD}) = G(F(x)) \tag{3.3}$$

which can also be expressed as

$$y = G_{PA}(x_{DPD}) \cdot x_{DPD}, \qquad (3.4)$$

where  $G_{PA}(x_{DPD})$  is the nonlinear gain of the PA and also can be seen as the slope of the transfer function between y and  $x_{DPD}$ . Since the PA and the predistorter have the opposite nonlinear behavior, under the assumption that the output signal y is normalized by the power gain of the PA, we will have

$$G_{DPD} = \frac{1}{G_{PA}} \tag{3.5}$$

The gain of the entire system, consisting of both predistorter and PA, can be derived by

$$G = \frac{dy}{dx} = \frac{dy}{dx_{DPD}} \cdot \frac{dx_{DPD}}{dx}$$

=  $G_{PA} \cdot G_{DPD} = 1$  (3.6)

Therefore, the gain of the system is 1, a normalized constant, which means that the system is linear.

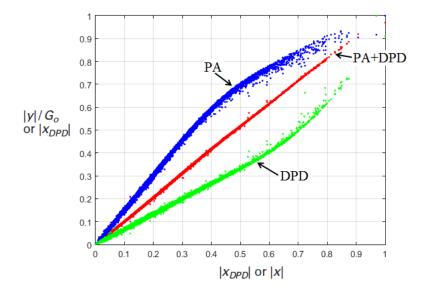

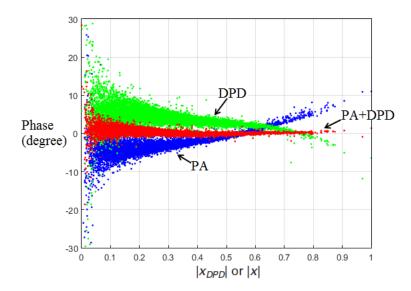

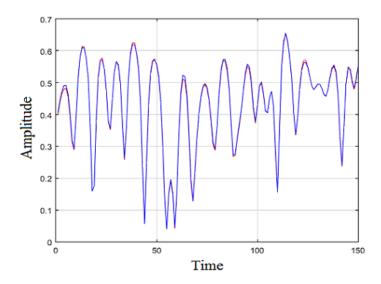

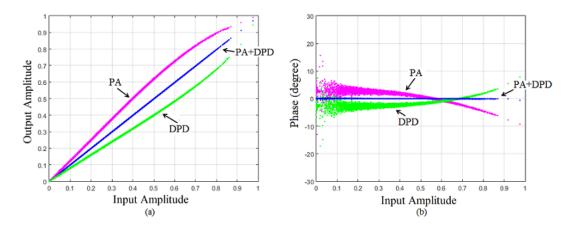

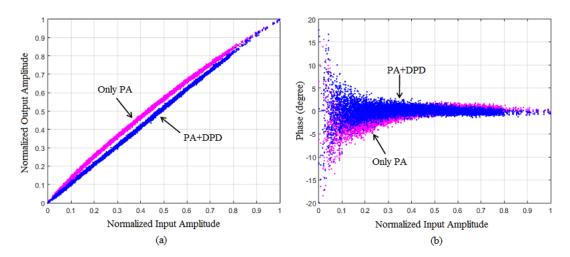

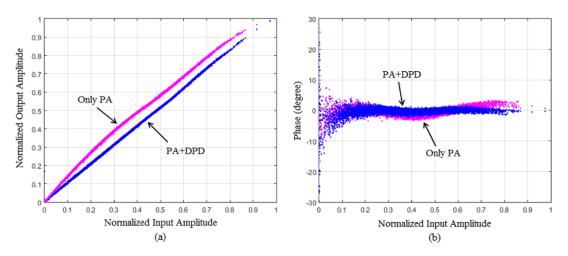

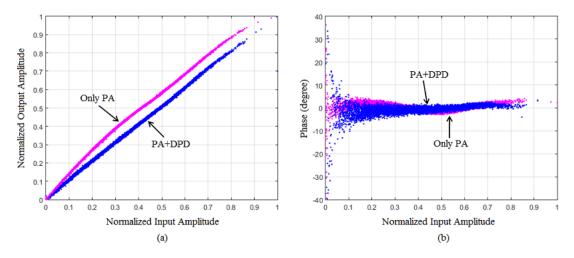

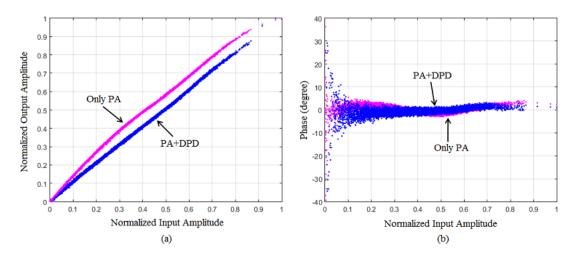

We will offer an example with data measured from a real PA to demonstrate the principle of the DPD. Figure 3.3 and Figure 3.4 illustrate the AM/AM and AM/PM characteristics for the sample PA with memory (blue), a corresponding predistorter (green) and the entire system with both PA and predistorter (red). In Figure 3.3, the horizontal axis is the magnitude of the input signal to predistorter x and the input to PA  $x_{DPD}$ , while the vertical axis is the magnitude of the output signal from predistorter  $x_{DPD}$  and the normalized output from PA  $y/G_o$ . As shown in Figure 3.3, the magnitude response of the PA is not a straight and the power gain is compressed at high power region. The predistorter, on the contrary, produces the gain expansion to compensate the compression. As a result, the resulting magnitude is

Figure 3.3. Transfer functions for a sample PA with memory (blue), predistorter suitable to obtain linear response (green), PA and predistorter(red)

Figure 3.4. Phase curves for a sample PA with memory (blue), predistorter suitable to obtain linear response (green), PA and predistorter(red)

a straight line and the gain is flat, meaning that the PA is linear.

Meanwhile, in Figure 3.3 of the AM/PM characteristics, the horizontal axis is still the magnitude of the input to predistorter x and the input to PA  $x_{DPD}$ , while the vertical axis is the phase of the PA, the predistorter and the entire system. The phase here means the phase difference between the output and input of the device. Therefore, same to the theoretical principle, the phase of the PA and the predistorter is opposite to each other. Moreover, with the DPD, the resulting phase of the whole system is nearly zero, leading to a linear response.

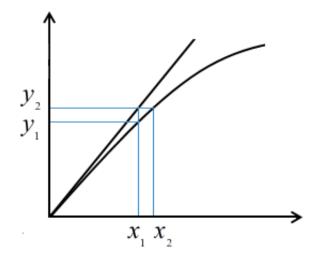

The basic principle of DPD can be explained in another more intuitive way with Figure 3.5. Suppose that at the input, there is a signal with power at point  $x_1$ . The response at the output of the PA is with power at point  $y_1$ . However, with an ideal linear behavior, the output should be at point  $y_2$ . Therefore, to obtain the power at point  $y_2$ , the input signal fed to the PA should have the power at point  $x_2$ . It is the job for the predistorter to convert the power from point  $x_1$  to the point  $x_2$  in order to get the linear result from the PA.

Figure 3.5. Power amplifier output power vs input power

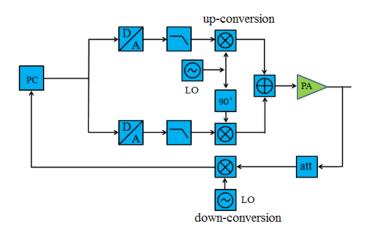

The DPD technique is implemented in digital domain, where digital signal processing technique is applied to simplify the computation. Analog-to-digital (ADC) devices are needed to convert the analog signal into digital domain. Then a model is required to describe the predistorter and to generate the predistorted signal. The detail on the modeling will be introduced in next chapter. The digital predistorted signal should pass through a digital-to-analog (DAC) to be converted back to analog signal. At last, the signal will be up-converted to the required frequency and is fed to the PA.

### 3.2 DPD implementation

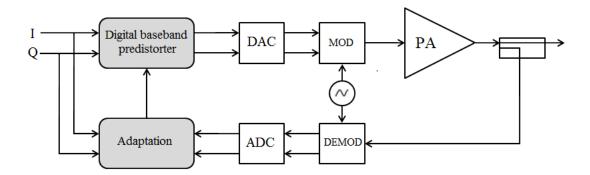

Due to the fast improvements of digital signal processing techniques, the baseband DPD has became the most adopted linearization technique. Figure 3.6 illustrates the simplified implementation of the DPD system. The signal is firstly digitized and then fed to the predistorter. The predistorter function is usually applied on a digital signal processing unit (FPGA or DSP) where the input signal is processed with a predefined algorithm. The predistorted signal is then converted back to analog signal which will be modulated to the required frequency and fed to the power amplifier.

Figure 3.6. Simplified block diagram of a DPD implementation in a transmitter

In Figure 3.6, there is a closed loop feedback which is for adaptive behavior of DPD. Since the characteristic of a PA varies in many cases, including different bias supply, changes in temperature, aging, it is essential to continuously update the predistorter function. In an adaptive DPD system, a fraction of the output signal from the PA is fed back by using a coupler. The feedback signal is demodulated to baseband and digitized for extracting the DPD function. The detail of the adaptive algorithms used in DPD will be discussed in chapter 7.

The input and output signals used to extract the predistoter function are the baseband signal to PA and the baseband signal output from PA, respectively. Therefore, the nonlinear behavior we get consists of all the nonlinear components in the chain and the DPD can minimize the nonlinearity of all these nonlinear components.

### **3.3 DPD Architecture**

The basic principle of digital predistortion technique [5, 32] is to introduce a nonlinear component which has the inverse characteristic of the PA. Therefore, it is essential to derive the inverse model with the input and output data of the PA. One method employed in the DPD system is the model inverse.

The model inverse structure is to find an inverse function to be used as the model of predistorter. There are two commonly used architectures: direct learning and indirect learning.

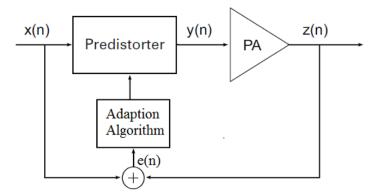

#### 3.3.1 Direct Learning Architecture

The direct learning architecture, as its name states, directly adjusts the predistorter model parameters by using the feedback error e(n) with an adaption algorithm, as shown in Figure 3.7. The error is the difference between the input signal x(n) and the normalized output signal z(n), which are time aligned. Several adaption algorithms [30–32] have been proposed for direct learning architecture. These algorithms tune the parameters of the predistorter according to the feedback error in order to minimize the feedback error. Since the error is zero for linear system, we will obtain an approximately linear behavior at last with minimum feedback error.

Figure 3.7. Block diagram of the direct learning architecture

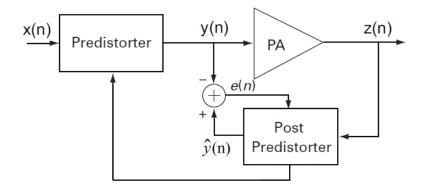

#### 3.3.2 Indirect Learning Architecture

Indirect learning architecture [5,33–36], which introduces a post predistorter, is another commonly used method in the model parameters extraction for predistorter. Its basic schematic is depicted in Figure 3.8, in which x(n) is the input to PD, y(n)is the output from PD and also the input to PA, z(n) is the normalized output from PA,  $\hat{y}(n)$  is the output from the post predistorter block, the error signal e(n) is given by  $e(n) = y(n) - \hat{y}(n)$ . The post-inverse estimation block and the predistorter have the identical nonlinear transfer function. The post-inverse estimation block generates the parameters of PD by minimizing the error signal e(n). Since that when the PA is linear, x(n) = z(n) and thus  $y(n) = \hat{y}(n)$ . Finally, the estimated parameters are copied to the predistorter.

Figure 3.8. Block diagram of the indirect learning architecture

### 3.4 DPD problems

The major problem is the bandwidth expansion of the predistorted signal  $x_{DPD}$ . The predistorted signal  $x_{DPD}$  usually has a wider bandwidth than the input signal x since the predistorter introduces the nonlinear distortion compensation. As a result, the sampling rate of  $x_{DPD}$  should be several times higher than the sample rate associated with input signal x. This throws a higher requirement on digitalto-analog converters (DACs). In return, the DAC speed limitation will restrict the maximum bandwidth of the input signal.

Another concern is focused on energy consumption of the predistorter circuitry which is usually several watt. The efficiency of a PA with DPD should also take the energy of the predistorter into consideration. Therefore, the DPD technique is suitable for PAs that exceeds 10 W. The energy consumption is related to the size of the hardware used to implement the predistorter. Therefore, the complexity of the predistorter should not be too high in order to reduce the energy consumed in predistorter.

The value of PAPR, which is defined as the ratio between the peak power and the average power, will become larger after the predistorter since the predistorter has a gain expansion. Therefore, the input power level should back-off by more than the original PAPR from the saturation level.

# Chapter 4

# Power Amplifier Behavioral models

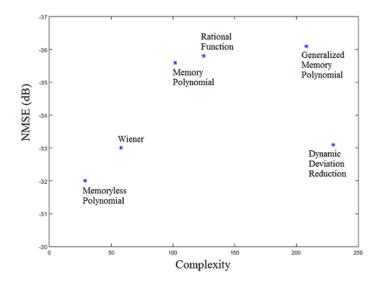

The basic principle of DPD is to add a nonlinear block just in front of the PA to compensate the PA gain compression. This block produces the exact inverse nonlinearity of the PA. Hence, a model that can predict accurately the behavior of the PA and the predistorter is required. Since RF PAs usually exhibit memory effects, the model should be able to describe not only dynamic nonlinear behavior but also memory effects. Behavioral model is the best choice, since it is built simply from the observation of the input-output behavior of the device instead of the knowledge of the device's internal constitution. There are various behavioral models proposed in the literature, such as the most comprehensive, full Volterra model and its simplified versions, like memory polynomial model or generalized memory polynomial model. Other polynomial function based models include rational function model, Hammerstein model, Wiener model and so on. We should choose one among all these models which is a tough work. The model selection is mainly based on model accuracy, model computational complexity and model extraction technique. The memory polynomial model is chosen at last due to its low complexity and satisfactory accuracy.

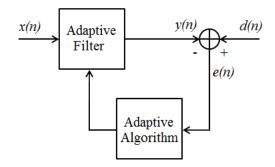

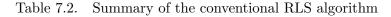

The model extraction technique is another important aspect that need to be taken into consideration. The most common solution is the least square (LS) technique which requires that the model should be linear in its parameters. The LS method can be adopted for memory polynomial model. Other extraction techniques, such as least mean square (LMS), recursive least square (RLS), are also popular for DPD systems. Different from LS method, the LMS and RLS techniques generate the model parameters sample by sample with the input and output data.

## 4.1 Behavioral models

One prerequisite to apply digital predistortion is to model the PA and predistorter accurately which is determined by the model selected. There are mainly three basic and different strategies for the device modeling: physical modeling, circuit modeling and behavioral modeling. Each of them has its advantage and drawback and is applied in different fields.

Physical model is based on the device physics. Using a microwave metal-semiconductor field-effect transistor (MESFET) as an example, the physical properties including oxide thickness, doping density, carrier mobility and so on, are the basic knowledge to build the physical model. They should solve the transport and Poisson equations at a microscopic level. These kind of models are complex to extract that make them inadequate in the real simulation.

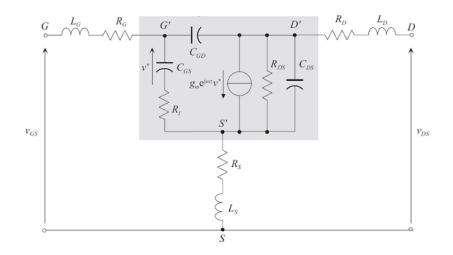

Figure 4.1. A sample FET small-signal equivalent circuit model

Circuit modeling uses active passive components to model the behavior of the transistors or diodes. Figure 4.1 shows a typical small-signal equivalent circuit model of a FET which consists both the intrinsic and extrinsic parts. These models can be constructed from S-parameter or I-V characteristics. Circuit model can be used to predict the time domain current or voltage of a PA, although they are never directly measured.

On the contrary, behavioral modeling [37, 38], also called black-box modeling (Figure 4.2), does not require the knowledge of the internal constitution of the PA and

Figure 4.2. Black-box modeling

relies only on the observation of input and output signal of the PA. The procedure is to build and tune a mathematical expression in order to make the output of the model coincided with the measured output of the PA with the same input signal. Therefore, behavioral modeling is a more computationally efficient solution and it is easier to implement the model with computational devices. Only the input and output signals of the PA are required, instead of looking deep inside the PA's internal structure. The selection of a behavioral model is mainly based on the criteria of the model accuracy, the computational complexity and the model extraction technique. It is the ideal tool for the system level simulation and it can find a widespread use in wireless communication systems.

Behavioral models can generally be divided into two groups according to the memory effects: memoryless models and models with memory. Each group has a variant number of models with different complexity and performance which will be discussed in the following sections.

## 4.2 Figure of Merit

One of the most critical requirements in DPD technique is to model the predistorter accurately. It is essential to clearly evaluate the performance of the model. Therefore, model performance evaluation criteria should be adopted to choose the proper model. The most commonly used criteria are NMSE in time domain and ACPR in frequency domain.

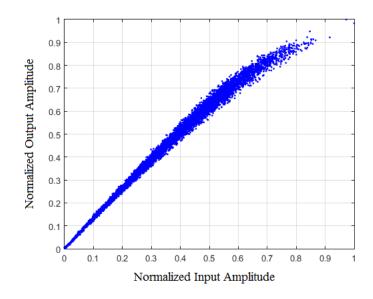

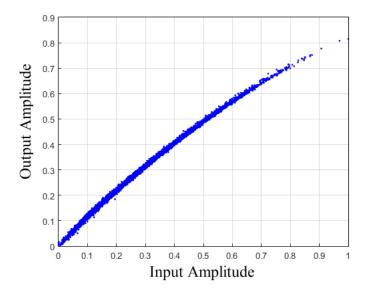

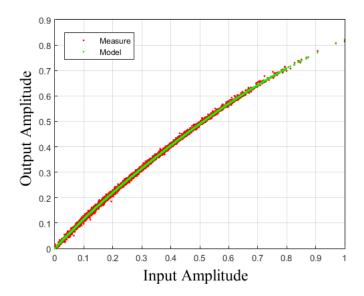

In the following sections, the test signal for the models is the LTE signal with 9.8 dB PAPR and a channel of 28 MHz. The device under test (DUT) is a wideband class AB amplifier whose characteristic is shown in Figure 4.3. It can be seen clearly that this DUT exhibits memory effects since the characteristic behavior is not a single line.

Figure 4.3. AM/AM characteristic of the sample DUT.

#### 4.2.1 NMSE

NMSE refers to Normalized Mean Square Error, which is an estimator of the overall deviations between the predicted and measured values in time domain. Therefore, it is the most straightforward approach and it is often expressed in decibels as following.

NMSE = 10

$$log_{10}\left(\frac{\sum_{k}|y_{k} - x_{k}|^{2}}{\sum_{k}|x_{k}|^{2}}\right)$$

(4.1)

where  $x_k$  is the experimental output instant of the DUT and  $y_k$  is the output instant obtained from the model. Therefore, the accuracy of the model is inversely proportional to NMSE. In other words, the lower the NMSE is, the higher the model accuracy is.

The NMSE can also represent the linearity of a PA with  $x_k$ ,  $y_k$  being the input instant and normalized output instant of the PA, respectively. In this case, -35 dB of NMSE will mean that the PA has a very good linear behavior.

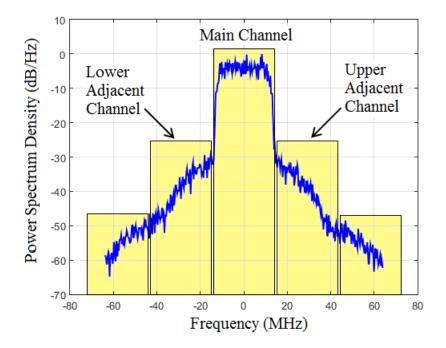

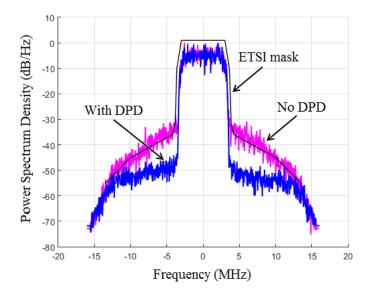

#### 4.2.2 ACPR

The adjacent channel power ratio (ACPR) is a frequency domain evaluation criterion, which is defined as the power ratio between the total power of adjacent channels and main channel. The main objective is to check the power distribution between in in-band channel and adjacent channels. It is possible to quantify the error in different frequency domain ranges. Its expression is given as

$$ACPR = 10 \ \log_{10}\left(\frac{\int_{f_1}^{f_2} |E(f)|^2 \ df + \int_{f_3}^{f_4} |E(f)|^2 \ df}{\int_{f_2}^{f_3} |E_{desired}(f)|^2 \ df}\right)$$

(4.2)

where  $|E(f)|^2$  is the power at one frequency f and frequency range  $(f_1 f_2)$  is the lower adjacent channel and  $(f_3 f_4)$  is the upper adjacent channel and  $(f_2 f_3)$  is the in-band channel. Therefore, the first and the second integral in numerator calculate the lower and upper adjacent channel power, respectively while the denominator is the in-band channel power. Figure 4.4 is an example of ACPR figure of an output signal where the in-band frequency range is -14 MHz to 14 MHz.

Figure 4.4. ACPR figure of a sample PA output

# 4.3 Even-order Terms in the Polynomial

In this chapter, all the models with power polynomials include only the odd-order terms. Although, in [77], it is proved that it is beneficial to include both the odd- and even-order terms for the models. However, most other published papers (e.g. [55,78]) consider only the odd-order terms. In this section, we will explain why only the odd-order terms are considered for the modeling in our DPD with one example of a real test power amplifier.

It would seem that all the terms in the polynomial should be used to deliver the best representation of the PA magnitude and phase responses. However, when we acquire the output signal from a PA in a real measurement, the signal is limited to the frequency band of interest. Only the carrier and odd-order intermodulation signals can be detected, while the even-order intermodulation signals will be filtered. For this reason, the even-order terms would appear to be redundant.

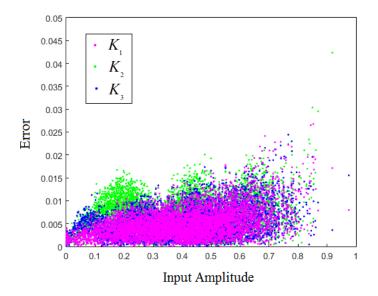

We do the same test which has been done in [77] with the memory polynomial model and our test PA data. We use the same three sets of polynomial orders for comparison:  $K_1 = \{1, 3, 5, 7, 9\}, K_2 = \{1, 3, 5\}$  and  $K_3 = \{1, 2, 3, 4, 5\}$ . The three sets are compared quantitatively with the NMSE between the output signal of the experimental data and the model which are shown in Table 4.1.  $K_2$  and  $K_3$ have the same largest polynomial order, 5. Therefore, the performance of the model is better with both even- and odd-order terms if the largest polynomial order is the same. However, if the number of the terms in a polynomial model is the same,  $K_1$ contains only the odd-order terms and has a better fit to the experimental data.

|           | $K_1$ | $K_2$ | $K_3$ |

|-----------|-------|-------|-------|

| NMSE (dB) | -37.6 | -35.2 | -36.9 |

Table 4.1. Comparison of NMSE between 3 sets of polynomial orders

The same result can be seen in Figure 4.5. The x-axis is the input amplitude and the y-axis is the output amplitude error between the experimental data and the model. The magenta points stands for polynomial order of  $K_1 = \{1, 3, 5, 7, 9\}$ , green for  $K_2 = \{1, 3, 5\}$  and blue for  $K_3 = \{1, 2, 3, 4, 5\}$ .  $K_1$  yields the best result with slightly smaller error than  $K_3$  while  $K_2$  shows the worst fit to the experimental data. We can conclude that the odd-order terms are enough for the modeling with polynomial terms. Therefore, we only consider the odd-order terms in the memory polynomial model and other models with power terms.

Figure 4.5. Comparison between 3 sets of polynomial orders. The x-axis is the input amplitude and the y-axis is the output amplitude error between the experimental data and the model.  $K_1 = \{1, 3, 5, 7, 9\}, K_2 = \{1, 3, 5\}$  and  $K_3 = \{1, 2, 3, 4, 5\}.$

## 4.4 Memoryless models

Memoryless behavioural modelling has many advantages, including easier computational implementation, relative efficiency in system simulations and its acceptable level of accuracy in many situations. Therefore, it has been used for many years in system level simulation.

Memoryless means that the output is only dependent on the current input and the previous samples have on effect on the output. There is a one-to-one mapping between present input and output signals. Therefore, if the PA is strictly memoryless, it will only introduce amplitude distortion.

The most used memoryless model is polynomial function [39]. Others, including Rapp model [42] and Ghorbani model [41] which are similar of the Saleh model [10], are also introduced in the literatures. Look-up table (LUT) method is another structure to model the memoryless systems, where the data are stored in a table in advance.

#### 4.4.1 Memoryless polynomial model

The most natural and used memoryless model is the polynomial function [39], whose equation is

$$y = \sum_{p=0}^{P} a_p x^p \tag{4.3}$$

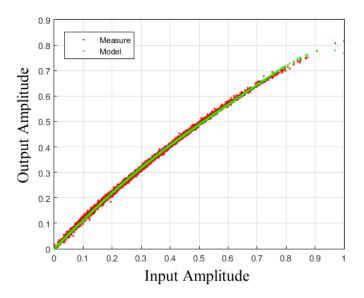

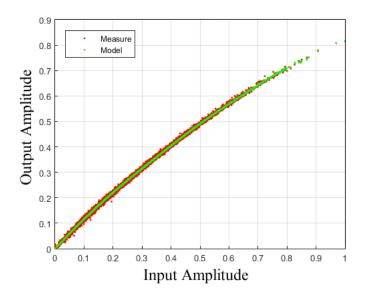

where x and y are the input and output signals, respectively, P is the polynomial order and  $a_p$  is the corresponding coefficients. The comparison between the experimental data and the model is shown in Figure 4.6. The polynomial order is 4 with only even order. As a result, the NMSE for this memoryless polynomial model is -32.2 dB.

Figure 4.6. Measured and modeled AM-AM characteristics comparison for memoryless polynomial model. The red represents the measured data and the green is for the model.

There are other memoryless or quasi-memoryless models including Rapp model [42] and Ghorbani model [41] which are similar of the Saleh model [10]. There are also several other similar models based on power series, including Bessel Function Based Model [43], Gegenbauer Polynomials Based Model [44] and Zernike Polynomials Based Model [45].

#### 4.4.2 LUT model

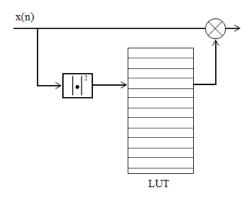

The LUT model [28] is another basic behavioral model with momoryless nonlinearity, which is relatively simple and easily implement. Different from the analytical function-based model, the LUT model stores all possible values in a table in advance and retrieve them later. It is a memory-cost model and the memory is used as the table. In other words, the LUT model saves the computational complexity with memory storage.

The simplest solution for LUT model is the one-to-one mapping, saving each possible output signal in the table indexed by its corresponding input signal. This solution is able to compensate any memoryless distortion. However, since every possible signal has to be stored, the memory size required is huge. Another propose is to store only the complex gain indexed by the magnitude of the input signal. There is a direct relation between the input and output, expressed as:

$$y(n) = G(|x(n)|) \cdot x(n),$$

(4.4)

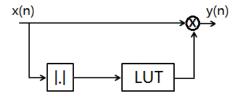

where G(|x(n)|) is the instantaneous complex gain, x(n) and y(n) are the input and output signals, respectively. The complex gain G(|x(n)|) is calculate and stored in a table. Figure 4.7 illustrates the operation of the LUT model based on complex gain method, where |.| means the magnitude. Each input corresponds to a unique complex gain and the output is the multiplication of the input and the corresponding gain. Therefore, this model is suitable for real-time applications.

Figure 4.7. Look-up-table model

However, in the meantime, LUT model also suffers some problems. For instance, extra memory resource is required to be as the tables, to store the complex gain. And only a limit number of LUT entries can be implemented which will lead to the quantization error.

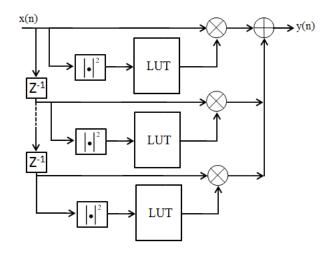

LUT model can also used for PAs with memory effects. In memory LUT model [40],

the complex gain is a function of the present and several preceding inputs instead of just present input. Therefore, the LUT size is  $K^{M+1}$ , where K is the size of memoryless LUT and M is the memory depth. It faces a more severe problem in memory size.

# 4.5 Models with memory

On the contrary, a model with memory is not only dependent on the current input but also on a certain depth of previous samples, which makes the system dynamic. Moreover, to accurately model the PA, some models with memory also depend on previous output values. Most of the RF power amplifiers used in the modern wireless communication systems exhibit the memory effects. Therefore, behavioral models with memory are more and more important.

The most comprehensive memory model is the full Volterra model. Volterra model is a polynomial expansion which can represent nonlinear systems with memory. It is typically truncated to simplified structures, giving rise to several other memory models with less complexity. Among them, the memory polynomial model is widely used in the behavioral modeling.

#### 4.5.1 Full Volterra model

The Volterra model [46,47] provides a general way to model a nonlinear system with memory which is a combination of linear convolution and nonlinear power series. It is considered as an extension of the Taylor series. In this model, the relationship between the input and output signals is:

$$y(n) = \sum_{p=1}^{P} \sum_{i_1=0}^{M} \cdots \sum_{i_p=0}^{M} h_p(i_1, \cdots, i_p) \prod_{j=1}^{P} x(n-i_j)$$

(4.5)

where x(n) and y(n) are the input and output signals, respectively,  $h_p(i_1, \dots, i_p)$  are the coefficients of the Volterra model, often called Volterra kernels, P is the nonlinearity order of the model, and M is the memory depth.

We can improve accuracy of the model by increasing K and M. Unfortunately, this high accuracy is obtained at the cost of unnecessary computational complexity

since the number of parameters will grow exponentially. Nevertheless, the Volterra model is well suitable for modeling dynamic nonlinear behavior.

#### 4.5.2 Memory polynomial model

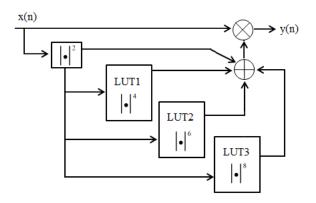

The memory polynomial model [36, 48–50] has been widely used as a behavioral modeling in digital predistortion of PAs with memory effects for many years. It corresponds to a reduction of the Volterra series in which only diagonal terms are kept. It has a reasonable compromise between computational complexity and model accuracy. The output waveform of the model is

$$y(n) = \sum_{m=0}^{M} \sum_{p=0}^{P} a_{mp} x(n-m) |x(n-m)|^{p}$$

(4.6)

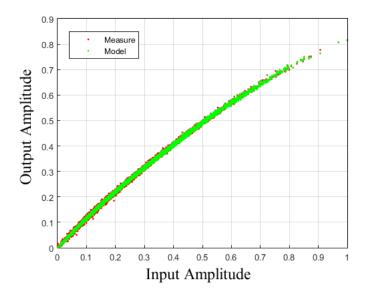

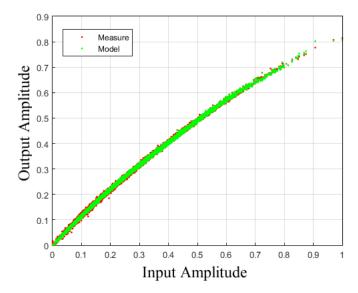

where x(n) and y(n) are the input and output signals, respectively, P is the nonlinear order, M is the memory depth and  $a_{mp}$  are the model coefficients. The comparison between the experimental data and the model is shown in Figure 4.8. The polynomial order is 7 with only even order and the memory depth is 2. As a result, the NMSE for this memory polynomial model is -35.6 dB.

Figure 4.8. Measured and modeled AM-AM characteristics comparison for memory polynomial model. The red represents the measured data and the green is for the model.

A variant of other memory polynomial models have been proposed in literature. They are Orthogonal Memory Polynomial model [51], Non-Uniform Memory Polynomial model [52, 53], Envelope Memory Polynomial model [54].

#### 4.5.3 Generalized Memory Polynomial Model

As mentioned above, the memory polynomial model is a simplified case of Volterra model which eliminates all the cross memory parts. However, as the the signal bandwidth has significantly increased, the memory polynomial model is not enough and the introduction of the cross terms in the full Volterra model is needed. A generalized form of the *p*th memory polynomial component in (4.6) can be written as:

$$\sum_{m=0}^{M} \sum_{p=0}^{P} a_{mp} x(n) |x(n-m)|^{p}, \qquad (4.7)$$

where we have inserted a local delay of m samples between the signal and its exponential part. The delay in (4.7) could be both positive and negative. If we add both these positive and negative local memory that close to the current memory to the typical memory polynomial model in (4.6), it will come out the generalized memory polynomial model [55].

$$y(n) = \sum_{p=0}^{P_a} \sum_{l=0}^{L_a} a_{pl} x(n-l) |x(n-l)|^p + \sum_{p=1}^{P_b} \sum_{l=0}^{L_b} \sum_{m=1}^{M_b} b_{plm} x(n-l) |x(n-l-m)|^p + \sum_{p=1}^{P_c} \sum_{l=0}^{L_c} \sum_{m=1}^{M_c} c_{plm} x(n-l) |x(n-l+m)|^p$$

(4.8)

where the first part is the same as memory polynomial model, while the last two terms are the cross memory with both positive and negative time shifts.  $P_a$  and  $L_a$ ,  $P_b$  and  $L_b$ ,  $P_c$  and  $L_c$  are the polynomial order and memory depth for the current, positive and negative parts, respectively,  $M_b$  and  $M_c$  are the local memory that shift from the current memory.

The generalized memory polynomial model can be seen as the advanced version of the memory polynomial model. It has a better performance, in terms of reducing spectral regrowth, than the memory polynomial model. However, it suffers a problem of higher computational complexity.

| $P_a$ | $L_a$ | $P_b$ | $L_b$ | $M_b$ | $P_b$ | $L_b$ | $M_b$ |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 7     | 2     | 2     | 2     | 1     | 2     | 2     | 1     |

Table 4.2. Memory depth and polynomial order chosen

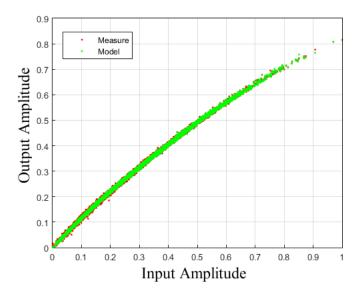

The comparison between the experimental data and the model is shown in Figure 4.9. The memory depth and the polynomial order are chosen as listed in Table 4.2. As a result, the NMSE for the generalized memory polynomial model is -35.6 dB.

Figure 4.9. Measured and modeled AM-AM characteristics comparison for generalized memory polynomial model. The red represents the measured data and the green is for the model.

#### 4.5.4 Dynamic Deviation Reduction-based Volterra Model

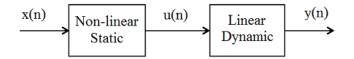

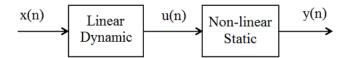

Dynamic deviation reduction-based Volterra model [56–58] is another modified and simplified version of the Volterra model. In this model, the input data are organized according to the order of dynamics involved. We remove the high order dynamics, because the nonlinear effects can be ignored with high order dynamics for most PAs. The property of linearity in the parameters has been reserved in this model. As mentioned above, the number of parameters increased exponentially with nonlinearity order and memory depth for Volterra model. However, for this model, the situation is different and the number of parameters increases almost linearly. Therefore, it is suitable to accurately model a PA with static strong nonlinearities and with long-term linear and low-order nonlinear memory effects.

The expression for this model is

$$y(n) = \sum_{p=1}^{P} h_{p,0} x^{p}(n) + \sum_{p=1}^{P} \left[ x^{p-1}(n) \sum_{i=1}^{M} h_{p,1}(i) x(n-i) \right] + \sum_{p=2}^{P} \left[ x^{p-2}(n) \sum_{i_{1}=1}^{M} \sum_{i_{2}=i_{1}}^{M} h_{p,2}(i_{1},i_{2}) x(n-i_{1}) x(n-i_{2}) \right]$$

$$(4.9)$$

where P is chosen as 7 and M is 2. The comparison between the experimental data and the model is shown in Figure 4.10. As a result, the NMSE for the dynamic deviation reduction-based model is -33.1 dB.

Figure 4.10. Measured and modeled AM-AM characteristics comparison for dynamic deviation reduction-based Volterra model. The red represents the measured data and the green is for the model.

#### 4.5.5 Rational function

A rational function is mathematically defined as the ratio of two polynomial functions, expressed as:

$$y(n) = \frac{a_0 + a_1 x(n) + \dots + a_I x^I(n)}{b_0 + b_1 x(n) + \dots + b_J x^J(n)}$$

(4.10)

where x(n) is the input and y(n) is the output of the rational function at instance n, and the highest polynomial order, I and J, are not required to be equal.

It is expected that the rational function should be able to model the PA accurately [59,60]. However, (4.10) can not compensate the memory effects. In order to include the memory effects, a new model based on the rational function was proposed [61], where memory effects were included both in the numerator and denominator, whose expression is:

$$y(n) = \frac{\sum_{p=0}^{P_n} \sum_{m_n=0}^{M_n} a_{p,m_n} x(n-m_n) |x(n-m_n)|^p}{1 + \sum_{p=0}^{P_d} \sum_{m_d=0}^{M_d} b_{p,m_d} |x(n-m_d)|^p}$$

(4.11)

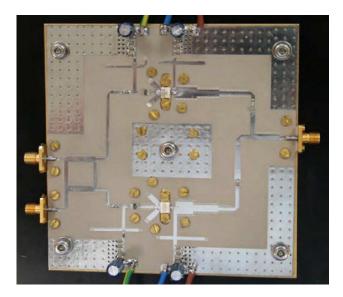

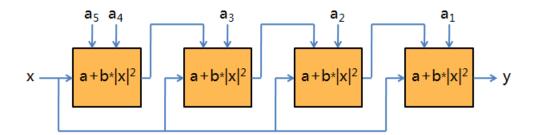

where x(n) and y(n) are the input and output signals, respectively,  $P_n$  and  $M_n$ ,  $P_d$ and  $M_d$  are the polynomial order and memory depth for the numerator and denominator, respectively. The memory effects are described with absolute terms in the denominator and with complex-envelope terms in the numerator.