# **POLITECNICO DI TORINO**

# Oxide Memristive Devices

Alladin Jasmin

A PhD Dissertation

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

DOCTOR OF PHILOSOPHY IN MATERIALS SCIENCE AND TECHNOLOGY

> Supervisor: PROF. C. F. PIRRI, Ph. D. Co-Supervisors: PROF. CARLO RICCIARDI, Ph. D. SAMUELE PORRO, Ph. D.

# Abstract

Resistive switching in metal oxide materials has recently renewed the interest of many researchers due to the many application in non-volatile memory and neuromorphic computing. A memristor or a memristive device in general, is a device behaving as nonlinear resistor with memory which depends on the amount of charges that passes through it. A novel idea of combining the physical resistive switching phenomenon and the circuit-theoretic formalism of memristors was proposed in 2008. The physical mechanism on how resistive switching occurs is still under debate. A physical understanding of the switching phenomenon is of much importance in order to tailor specific properties for memory applications. To investigate the resistive switching in oxide materials, memristive devices were fabricated starting from materials processing: low-pressure chemical vapor deposition of ZnO nanowires (NWs), low-temperature atomic layer deposition (ALD) of TiO<sub>2</sub> thin films and micro-pulse ALD of Fe<sub>2</sub>O<sub>3</sub> thin films. The distinct geometry of ZnO NWs makes it possible to investigate the effect of the electrode material, surface states and compliance to the memristive properties. A simpler method of fabricating TiO<sub>2</sub>-based devices was explored using low-temperature atomic layer deposition. This approach is very promising for device application using photoresist and polymeric substrates without thermal degradation during and after device fabrication. ALD of pure phase Fe<sub>2</sub>O<sub>3</sub> thin films was demonstrated using cyclic micro-pulses. Based on the performance of the fabricated devices, the oxide materials under this study have promising properties for the next-generation memory devices.

# Summary

This dissertation is organized as follows:

- **CHAPTER 1**. This chapter provides an overview in the field of memristor and memristive devices. A background on the circuit-theoretic and recent development in device application are given. A survey of different memristive materials is discussed in detail. The current state-of-the-art technology and application of memristors is also given emphasis.

- **CHAPTER 2**. This chapter focuses on the methodology and materials processing techniques utilized in this study. Emphasis is given in science behind low-pressure chemical vapor deposition (LPCVD) and atomic layer deposition (ALD) techniques.

- **CHAPTER 3**. This chapter presents all the oxide materials and device characterization. Results showing the effect of interface layer in ZnO NWs memristive behavior are discussed. Results of low-temperature ALD and fabrication of TiO<sub>2</sub> thin film devices are also tackled. Finally, results of micropulse ALD and fabrication of Fe<sub>2</sub>O<sub>3</sub> thin film devices are presented.

- **CHAPTER 4**. Summary and conclusion are given based on the results presented. Suggestions regarding future development in the materials processing and device characterization aspect are also presented.

# **Table of Contents**

|                                       | Abs    | tract                              | 1  |  |

|---------------------------------------|--------|------------------------------------|----|--|

| 1. <b>Review</b>                      |        |                                    |    |  |

|                                       | 1.1.   | Background                         | 5  |  |

|                                       | 1.2.   | Memristor Fundamental              | 6  |  |

|                                       | 1.3.   | Memristive Devices                 | 7  |  |

|                                       | 1.3.1  | . Electroforming                   | 7  |  |

|                                       | 1.3.2  | . Resistance States                | 8  |  |

|                                       | 1.3.3  | Switching Mechanism                | 9  |  |

|                                       | 1.4.   | Memristive Materials               |    |  |

|                                       | 1.4.1  | . Oxide Thin films                 |    |  |

|                                       | 1.4.2  | . Oxide Nanostructures             | 12 |  |

|                                       | 1.4.3  | 8. Applications                    | 14 |  |

| 2.                                    | Materi | ials Processing                    | 19 |  |

|                                       | 2.1.   | Chemical Vapor Deposition          | 19 |  |

|                                       | 2.2.   | Atomic Layer Deposition            | 22 |  |

|                                       | 2.3.   | Device Fabrication                 | 27 |  |

| 3. Materials and Device Properties    |        |                                    |    |  |

|                                       | 3.1.   | ZnO nanowires                      |    |  |

|                                       | 3.1.1  | Nanowire Synthesis and Properties  |    |  |

| <b>3.1.2. Device Characterization</b> |        |                                    |    |  |

|                                       | 3.2.   | TiO <sub>2</sub> thin films        | 49 |  |

|                                       | 3.2.1  | Thin Film Synthesis and Properties |    |  |

|    | 3.2.2   | . Device Characterization                 | 52 |

|----|---------|-------------------------------------------|----|

|    | 3.3.    | Fe <sub>2</sub> O <sub>3</sub> thin films | 54 |

|    | 3.3.1   | . Thin Film Synthesis and Properties      | 55 |

|    | 3.3.2   | . Device Characterization                 | 60 |

| 4. | Conclu  | ision                                     | 64 |

|    | Bibliog | graphy                                    | 66 |

### 1. Review

This Chapter will discuss the concept of memristor and the recent advances in the study of memristive materials and devices. Details about the circuit-theoretic formulation of memristor and the physics of memristive switching in various materials and devices will be presented.

# 1.1. Background

System complexity in biological systems, memory networks and learning processes are observed to possess brain-like features. This poses a great challenge in terms of emulating neuromorphic processes like pattern recognition, adaptive learning and memory. Neuromorphic system and information processing are two emerging technology trends that require sophisticated microelectronic devices and circuitry for fast, reliable, high-density computing. Downscaling is very important in device fabrication especially now that low dimensional device architecture equates to physical device miniaturization, efficient material resource management and low power consumption.

Different electronic devices offer alternative solution to conventional type of computing including memristors, memristive systems and spintronic devices. The idea of memristor was first theorized by Chua<sup>1</sup> in 1971 in an attempt to find a circuit-theoretic relation between electric charge q and magnetic flux  $\Phi$ . Memristors and memristive systems offer potential use in neuromorphic processes, learning systems, parallel computing and non-volatile memory devices. The state of the device depends on its current charge history and its memory is retained. Thus, memristor can retain memory even if the power is switched off.

In the vast selection of materials to be used for such applications, metal oxides like ZnO,  $TiO_2$  and  $Fe_2O_3$  are excellent choices because of abundance, ease of processing and versatility. The recent discovery of the  $TiO_2$ -based memristor by HP Labs<sup>2</sup> stirs much interest in the field of nanoelectronics. This simple device consists of a switchable insulating layer sandwiched between two metal electrodes. These devices operate through stable switching from high to low resistance states caused by the changes in the filament resistance.

### **1.2. Memristor Fundamental**

Basic circuit theory describes passive circuit elements as two-terminal devices that relate fundamental circuit variables – voltage (v), current (i), charge (q) and magnetic flux ( $\phi$ ). Six mathematical relations can be formulated relating two of the four circuit variables. Two relations arise from the concept of current (charge flow) and voltage (electromotive force). Charge is the time integral of current. Conversely, flux is the time integral of voltage. These relations can be written as,

$$dq = i \, dt \tag{1}$$

and

$$d\phi = v \, dt \tag{2}$$

The three equations describing the three basic circuit elements are:

voltage and current relation links with resistance R,

$$dv = R \, di \tag{3}$$

charge and voltage relation associates with a capacitor with capacitance C,

$$dq = C \, dv \tag{4}$$

and current and flux relation describes an inductor with inductance L.

$$d\phi = L \, di \tag{5}$$

The last equation linking flux and charge describes a quantity M with units of resistance.

$$d\phi = M \, dq \tag{6}$$

The memristor equation can be deduced to Ohm's Law when the device response becomes linear. Based on the theoretical formulation, a memristor operates under sinusoidal input wherein the voltage changes with time.

# **1.3.** Memristive Devices

There is a remarkable progress in computer and mobile telecommunication in the past decade due to improvement of memory and processor technologies. With the emergence of big data opportunities for industry and research alike, the demand for memory devices increased rapidly. Memory devices can be divided into two groups – non-volatile and volatile memories. The current platform in memory storage mechanism is based on floating gate (flash) devices – charge storage.<sup>3,4</sup> Due to scaling limits encountered by this system, alternative memory storage mechanisms are already being developed.<sup>5–9</sup> The most promising alternatives include ferroelectric switching, magnetic switching, phase-change and resistive switching<sup>10</sup>. Resistive switching has been demonstrated since the late 1960s.<sup>11,12</sup> Band model interpretation of such phenomenon is less applicable as new experimental results indicate high field in localized regions of the device after electroforming.

#### **1.3.1.** Electroforming

Electrical phenomena in many oxides are described by a nonlinear transport mechanism<sup>13–15</sup> based on the bulk, surface states and oxide-electrode interface. The insulator-conductor transition that occurs prior to obtaining a stable switching has to be surpassed by electroforming. IV measurements show that the device becomes more conductive after the electroforming process. A typical IV measurement is performed by applying electrical stress to the device. In a symmetric device, when a gradually increasing positive voltage is applied to the top electrode, oxygen vacancies drift toward the bottom electrode. This high-field induced charge transport in some cases results to phase transition<sup>16</sup> to a more conductive state of the bulk or in localized regions. For an asymmetric device on the other hand, metallic filaments are also observed to form as ion channels using active electrodes like Ag<sup>17,18</sup> and Cu.<sup>19–21</sup> Either oxygen vacancies or metallic ions forming the conducting filaments are believed to be responsible for the abrupt decrease in resistance of the insulator.

Some issues are encountered during electroforming using voltage bias in particular. As mentioned above, this process can alter the stoichiometry, phase or charge distribution within the insulator. Initial field bias applied to the device is usually higher than the operating field. It is necessary to limit the current or to set a compliance current  $I_{cc}$  in

order to prevent irreversible dielectric breakdown. Another approach to completely avoid setting the compliance current is to apply current bias (instead of voltage bias) during electroforming. Nauenheim et al.<sup>22</sup> observed stable transition into the bipolar switching without shifting to a permanent conductive state or unipolar switching mode. Moreover, it is determined that the use of low-level current (10<sup>-9</sup> A) or low scan rate prevents the cell device from overcharging. Device geometry and operating current are important factors that affect memristive property because they are correlated to the changes in local inhomogeneity during switching. Yanagida et al.<sup>23</sup> investigated the scaling effect of unipolar and bipolar switching in crossbar junction devices. They investigated the transition of non-memory, unipolar and bipolar switching based on device geometry or cell area.

#### **1.3.2. Resistance States**

The initial resistance of a memristive device called pristine state (PRS) exhibits rectifying behavior. This is because the interface between Pt and Au (typically used as inert electrodes) and most oxides form a Schottky contact.<sup>13</sup> After electroforming, the device exhibits stable resistive switching characterized by two states - high resistance state (HRS or OFF state) to low resistance state (LRS or ON state). When the device switches from HRS to LRS, it is said to have undergone SET process. On the other hand when it switches from LRS to HRS the device it called RESET process. The switching can be bipolar (BRS) or unipolar (URS) depending on the nature of electrical stress and device asymmetry related to fabrication.<sup>5</sup> In the BRS mode, the SET and RESET processes occur on different voltage polarity while in the URS mode the SET and RESET processes occur on the same polarity and the RESET depends on the current intensity. In terms of device performance, bipolar is more reliable than unipolar switching in terms of endurance as the former is influenced by applied field while the latter is dominated by thermal effects. The ON/OFF current ratio influences the power consumption and switching speed. The transition between resistance states can be a smooth curve or an abrupt jump in the current in a given threshold voltage. Several reports indicate that it is possible to obtain more than two resistance state which the memristive device can switch. Multiple filament formation, stoichiometry, surface states, compliance current and source frequency<sup>24</sup> are some factors mentioned that influence the transition to multiple resistance states.

# **1.3.3. Switching Mechanism**

Early work of Dearnaley et al.<sup>13</sup>, Oxley<sup>25</sup> and Petersen et al.<sup>26</sup> give detailed description of the physical mechanism of resistive switching in oxides and chalcogenide thin film devices. The irreversible process of electroforming proceeded by stable switching thereof are shown to be due to filament formation across the insulating layer. Structural and conductivity studies of electroformed TiO<sub>2</sub> devices give strong evidence of the localized channel formation<sup>27–29</sup>. Switching dynamics is classified into three categories based on whether redox reaction or ionic conduction happens during switching<sup>30</sup>. This includes thermochemical mechanism (TCM), valence change mechanism (VCM) and electrochemical metallization (ECM)<sup>30–32</sup>. The first category is associated with thermal effects wherein current-driven increase in temperature results to filaments formation and rupture. This category best explains unipolar resistive switching. The second category is linked to oxygen vacancy migration which causes changes in oxide stoichiometry. In this mechanism, a nonstoichiometric or multilayer oxide layer is introduced in the MIM device in order to alter the vacancy transport. The chemical control in this case is confined in the interface suggesting the dominant contribution of thin layers instead of localized filaments. Lastly in ECM mechanism, the switching depends on the metal ion diffusion from the active electrode (Ag or Cu) to the inert electrode. During the switching process, the conducting filaments can be composed of ions and vacancies.

The linearity or nonlinearity of the transport properties of MIM devices serves a clue about the nature of the charge carriers responsible for the switching. Nonlinear behavior can be accounted by ion transport or by electrode-insulator interface reaction<sup>30</sup>. It is important to note that once ion transport is taken into account, the channel length has to be of the order of atomic scale length – i.e. lattice constant or nearest neighbor distances.

#### **1.4. Memristive Materials**

Memristive effect have been observed in various metal oxides like transition metal oxides (TMOs), perovskites, multiferroics, ferroelectrics, wide band gap (high-k) dielectrics, organic-based materials like graphene oxide and polymers. On the other hand, non-oxide materials which exhibit similar effect include chalcogenides like selenides and tellurides. This suggests a wide range of material selection as building blocks of devices for memory applications<sup>33</sup>.

Several switching mechanisms were proposed for particular materials to explain the phenomenon. For example, tunneling in high-k dielectrics is widely used to explain the low current and low power transport. Metal-insulator phase transition is very much studied using  $VO_2^{34-36}$  as model material.

#### **1.4.1. Oxide Thin Films**

Titanium dioxide (TiO<sub>2</sub>) thin film development has been of much interest because of its potential use in many practical applications. There is also a need to find an alternative material to replace SiO<sub>2</sub> for memory cells and field effect transistors (FET). TiO<sub>2</sub> – based memristive devices are well investigated in the literature. Recently, Strukov et. al.<sup>2,37</sup> proposed an empirical model of TiO<sub>2</sub> resistive switching and memristance in general. In this phenomenological approach, they described the TiO<sub>2</sub> layer consisting of doped and undoped regions. The boundary between these two regions is like a "moving wall" depending on the state variable w(t) associated with the size of the doped region. When  $w(t) \rightarrow D$ , the device becomes more conducting  $(R \rightarrow R_{ON})$  and when  $w(t) \rightarrow 0$ , it becomes more insulating  $(R \rightarrow R_{OFF})$ . Thus, such system was modeled as two variable resistors connected in series. The memristance equations are written as<sup>2</sup>,

$$V(t) = \left(R_{ON}\frac{w(t)}{D} + R_{OFF}\left[1 - \frac{w(t)}{D}\right]\right)I(t),$$

(7)

where

$$\frac{dw(t)}{dt} = \mu \frac{R_{ON}}{D} I(t).$$

(8)

It is clear that the state variable w(t) is dependent on the ion mobility  $\mu$  such that

$$w(t) = \mu \frac{R_{ON}}{D} q(t).$$

<sup>(9)</sup>

When we put equation (9) to equation (7), the memristance becomes

$$M(q) = R_{OFF} \left( 1 - \mu \frac{R_{ON}}{D^2} q(t) \right).$$

<sup>(10)</sup>

Equations (7) and (10) describe current-controlled memristive switching. The memristance equation (10) explicitly depends on the internal state of the device. Although this model fits the available experimental data, one has to argue that its universality is quite limited. This linear drift description encounters unavoidable nonlinear effects as one approaches the boundaries. Pershin and Di Ventra <sup>38</sup> suggested that description of current-controlled drift and ion mobility should also account for such boundary conditions. Further refining of this model has been done with the inclusion of a window function F which ensures zero drift at the boundaries. <sup>39</sup> Other models have also been developed and implemented to accommodate other material systems. <sup>32,40–42</sup>

Direct physical evidence of oxygen vacancy generation due to  $TiO_2$  reduction during device operation has been reported. Amorphous, anatase and magneli phases are found to coexist in a working  $TiO_2$  device.<sup>28,43,44</sup> The magneli phase is the reduced  $TiO_{2-x}$  phase which exhibit metallic behavior. This reduced region predominantly carries the current across the oxide, thereby creating localized increase in temperature. Although this occurred only during high-field bias or electroforming process. High resolution x-ray photoelectron spectroscopy (XPS) results<sup>45</sup> of TiO<sub>2</sub> bilayer devices consisting of oxygen-rich (TiO<sub>x</sub>) and oxygen-deficient (TiO<sub>y</sub>) layers show evidence of oxygen drift across the interface region. Changes in the chemical binding states of  $Ti^{2p}$  peaks are measured in the three oxide regions namely:  $TiO_x$  layer,  $TiO_y$  layer and  $TiO_x$ -TiO<sub>y</sub> interface. The oxygen-deficient  $TiO_y$  layer did not exhibit significant changes in the  $TiO_x$  layer and the interface region show increase in the metallic phases  $Ti^{3+}$  peak intensity in the low resistance state.<sup>45</sup> Clearly, the  $TiO_y$  layer acts as the charge reservoir during

switching. The  $TiO_x$  layer and the interface region become more conducting as conducting filaments are formed during electroforming and SET processes.<sup>46,47</sup>

Much effort has also been done to investigate the role of intentional doping or the presence of nanoparticle interstitials in the switching behavior of several oxides. Defects have been crucial assisting field localization thereby suppressing further potential build up during bias. The presence of well-separated nanocrystals in the oxide facilitates the formation of polar charges which affects the hysteresis in the IV curve.<sup>48</sup> Al<sub>2</sub>O<sub>3</sub> MIM devices have been studied on its memory performance by embedding metal nanocrystals on the Al<sub>2</sub>O<sub>3</sub> matrix. The advantage of Ru on Al<sub>2</sub>O<sub>3</sub> is that the high-dielectric property of Al<sub>2</sub>O<sub>3</sub> accommodates trap-rich regions which act as charge storage layers.<sup>49</sup> This results in direct tunneling effect in the Al<sub>2</sub>O<sub>3</sub> bulk during bias programming.

Qin et al.<sup>50</sup> suggested that modification of the oxide-electrode interface using Ag nanoparticles enhances the memristive behavior of  $Al_2O_3$  devices. During bias in a MIM device, oxygen vacancies are influenced by a uniform electric field which enables the formation of cylindrical-shaped conducting channels parallel to the applied field. The SET and RESET processes show fluctuations in their values and this can be attributed to the random channel rupture and recovery. This is because no filament was more favored to rupture, as this is the nature of how the ensemble of filaments is initially formed. On the other hand, the presence of Ag nanoparticles alters the electric field distribution. This creates localized fields which facilitate the growth of conducting filaments while suppressing the random nature of this process. The results show minimized resistance state dispersion and lower SET and RESET voltages which translate to more stable (both endurance and retention) devices and lower power operation.<sup>50</sup> Similar improvement in the endurance has also been observed in Al-AlO<sub>x</sub> nultilayer devices. Song et al. proposed that by increasing the number of Al-AlO<sub>x</sub> layers, the number of active regions for the filament growth and rupture also increases.<sup>51</sup>

# **1.4.2.** Oxide Nanostructures

The localized nature of filament generation during resistive switching suggests the possibility of fabricating nanostructure-based memristive devices. Moreover, surface

effects and carrier dynamics can be conveniently investigated in such systems as compared to the study of filaments sandwiched in bulk devices<sup>52</sup>. Among the nanostructured memristive oxide devices reported in literature include nanowires (NW)<sup>52–61</sup> nanotube (NT)s,<sup>62</sup> nanobelts (NB)<sup>63</sup>, quantum dots (QD)<sup>64</sup> and nanoparticles (NP).<sup>65–70</sup> Due to size effect, charge localization, field distribution and impurity, the diffusion in nanostructures behave differently in comparison to bulk materials. NW-based memristive devices are of much interest because of the ease of synthesis and the possibility of fabrication of individual NW devices. This entails much more sophisticated methods in conducting detailed study of charge transport mechanism and other nanoscale physical phenomena.

Nagashima et al.<sup>52</sup> demonstrated bipolar resistive switching in fabricated single MgO/TiO<sub>2</sub> NW devices. The memristive switching of these devices was found to be affected by the different gas environments. Moreover, the nature of the transport carriers was n-type which was in contrast to the p-type character of carriers normally concentrated in conducting filaments. One particular observation was the decrease of low resistance state (LRS) when the device was exposed to oxidizing environment.<sup>52</sup> They concluded that such behavior could be due to the effect of electron compensation through NW surface oxidation with the environment. Huang et al.<sup>55</sup> utilized ZnO NWthin film junction diodes (1D) and memristive devices (1R) to show rectifying and resistive switching behaviors in one device (1D1R). One advantage of this configuration was the mitigation of sneak path currents which arose in crossbar devices. The presence of NW layer creates device asymmetry (non-symmetry Schottky barriers) as well as vacancies or surface states which facilitate stable switching.<sup>71</sup> The ZnO NW layer acts as a reservoir for oxygen vacancies readily accessible during filament formation and rupture<sup>55</sup>. Similarly, Qi et al.<sup>57</sup> reported self-rectification and self-compliance behavior during switching of single Na-doped ZnO NW devices. The fabricated device had the Pt electrode connected to the ground while the active Ag electrode connected to a voltage bias. It was observed that a chain of Ag nanoislands formed on the NW surface during electrical characterization. High spatial resolution Auger electron spectroscopy (HSR-AES) map of the Ag distribution along the NW length showed the highest concentration of Ag in the biased electrode (Ag) while the lowest concentration was found in the middle. Self-compliance enhancement was attributed to the asymmetry of electrodes and Na-doping. It was also inferred that Na-doping facilitates the segregation of Ag atoms during bias.<sup>57</sup> Dendritic Ag NP cluster formation was also observed in ultrathin devices of SiN<sub>x</sub> membranes.<sup>72</sup> However, it has to be considered that in 1D nanostructures, the fractal behavior of the filament is now limited to the axial confinement as compared to 2D systems.<sup>60</sup> Controlling such filaments was dependent on the programming current owing to the reduction of Ag ions within the switching layer through electron capture.<sup>18,73</sup> Moreover, it was shown that by changing the SET voltage in Sb-doped ZnO NW devices, multilevel resistance values could be obtained.<sup>61</sup> This was due to the fact that Sb-doping increased resistivity and thereby narrowing the voltage distribution during SET process.

Another approach implemented to obtain enhanced resistive switching was to utilize the piezoelectric property of ZnO NW. Wu and Wang<sup>59</sup> demonstrated from a piezoelectrically modulated resistive memory (PRM) device that the applied strain (tensile and compressive) drastically influenced the hysteretic I-V characteristics. The absence of central symmetry of the ZnO crystal<sup>74</sup> meant that mechanical perturbation on the crystals had effect on the ionic polarization. This gave birth to a new phenomenon called piezotronic effect. It was described as the tuning of the barrier height at the electrode-oxide interface by the strain-induced charge polarization.<sup>59</sup> They also showed that the conductance ratio was stable (~10<sup>5</sup>) with different values of applied strain. These results offer large potential for the fabrication of flexible ZnO NW-based memory devices.

# **1.4.3.** Application

In this section the overall performance of memristive devices based on particular application is discussed. It is important to consider that some device characteristics are of much importance while others can be compromised up to a certain extent. Switching properties which arise as some electrical parameter-dependent are highlighted and evaluated in relation to specific device applications.

Crossbar device architecture is now used for the fabrication of high-density nonvolatile memories.<sup>75–78</sup> The feasibility of memory devices to be implemented in the existing chip

technology is to put small-size cells into densely-packed configuration (for more scalability). Crossbar array configuration enables the selection and programming of individual memory cell. However, there are challenges that have to be addressed like sneak path current to avoid incorrect selection of memory cells during read/write process. In fact the signal from unselected devices in the crossbar array can contribute noise during operation.

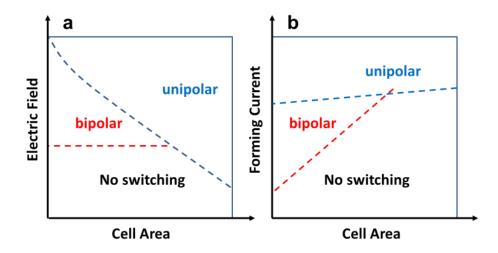

Yanagida et al.<sup>79</sup> studied the effect of cell area in the resistive switching characteristics of crossbar devices. They proposed threshold lines highlighting the boundaries between unipolar, bipolar and no switching regimes. The coverage of these regimes are mapped according to the applied electric field or forming current as a function of cell area. Fig. 1a shows the area dependence of switching with applied electric field while Fig. 1b shows the dependence with forming current.

FIG. 1. Area dependence of the different switching regimes with the applied electric field (a) and forming current (b).

Devices commonly exhibit no resistive switching when biased with low electric field or low forming current regardless of cell area. The threshold electric field necessary for bipolar switching is not much affect by the cell area. In fact, there is no noticeable effect  $(\sim 10^6 \text{ V/cm})$  with a wide range of cell area  $(10^2 \text{ to } 10^6 \text{ nm}^2)$ .<sup>79</sup> As presented in Fig. 1a, the electric field required for unipolar switching is influenced by the cell area. The smaller the cell area, the larger the electric field necessary for unipolar switching and vice versa. The forming current for unipolar switching is not that affected with the wide range of cell area being measured. On other hand, this is not the same with bipolar switching. There is a noticeable increase in the threshold current from  $10^{-9}$  to  $10^{-4}$  A when the cell area is increased in the range  $10^2$  to  $10^6$  nm<sup>2</sup>. The crossover of the two threshold lines in both diagrams supports the commonly observed unipolar switching in devices with large cell area.

Another way of connecting memristive devices in crossbar array is by stacking complementary devices.<sup>80</sup> Linn et al.<sup>78</sup> suggested that connecting two devices antiserially solves sneak path problems. Their device is composed of Cu bottom electrode and Pt top electrode with GeSe sandwiched layer. The complementary devices have the same mechanism as that of CMOS inverters wherein one of the transistors is always turned OFF, so the operating current is greatly minimized. Moreover, they also mentioned that the memory resistance has no dependence on the stored bit of information but in the pre-defined state during the write process.<sup>78</sup>

Adding nonlinearity feature to the Pt/  $TaO_x/TiO_{2-x}/Pt$  devices in a crossbar array has been shown to simplify the crossbar implementation by avoiding extrinsic device selection and by operating at low current around 10<sup>-6</sup> A.<sup>76</sup> It has been reported that the nonlinearity arises from the  $TaO_x/TiO_{2-x}$  bilayer and the resistive switching happens in the Pt/TaO<sub>x</sub> interface.<sup>76</sup>

Another switching characteristic that needs to be emphasized is the switching speed of memory devices. Volatile memory applications require several hundred picoseconds to nanoseconds of switching to accommodate fast data processing. Pulse-induced switching is usually performed to determine the high speed switching characteristics.<sup>81</sup> Lee et al.<sup>82</sup> obtained high speed switching of about 5 ns. The device, composed of HfO<sub>2</sub> switching layer and Ti buffer layer, exhibits high resistance ratio and reliable retention (about 10 years) even at 200 °C temperature. Zhang et al.<sup>83</sup> reported similar response time in Pt/STiO<sub>3</sub>:Nb junction devices. It is also reported the possibility to obtain multivalued memory states with similar switching characteristics in TiO<sub>2</sub>-based devices.<sup>84</sup> Sub-ns time response was also observed using GHz pulse generator. It has been demonstrated<sup>85</sup> that a 300 ps pulse of 1.4 V amplitude provides enough energy for switching a HfO<sub>x</sub> based device. Torrezan et al.<sup>86</sup> also reported sub-ns switching characteristics of memristor in the 100 ps timescale. Utilizing the ultrafast switching characteristics of memristive devices shortens the programming time during write

process. Moreover, this device capability offers the possibility of competing with the DRAM performance.<sup>87</sup>

Neuromorphic process is also a rich area of application where fast memristive dynamics can be exploited. Although it has also direct application in digital logic, research interest has not been reinforced due to the success of CMOS technology in this application. Early work of Widrow<sup>88</sup> in the 60s used the concept of memistor (resistor with memory) to describe and mimic the firing of the neuron. It is necessary to have electronic control over the neural output by storing the negative or positive gain values depending on how the input signals are temporally introduced.<sup>88,89</sup> In electronic devices the neural firing is generated by artificial synapses or spikes. The amplitude of such signal can be varied according to the timing of pulse namely pre-synaptic or post-synaptic spike.<sup>90–92</sup> Since this system is asynchronous, which does not require a clock like in digital logic, information processing can be done in parallel.<sup>89</sup>

Spike-timing-dependent plasticity (STDP) learning mechanism is one area of study being explored apart from the resistive switching phenomenon on various materials. The comprehensive overview of the STDP process can be found in the suggested references.<sup>93–95</sup> Ultrafast STDP was implemented in chalcogenide memristors to mimic the synaptic weight modification during pulsing.<sup>96</sup> Potentiation (increase in device conduction) and depression (decrease in device conductance) were observed when negative and positive pulses were applied, respectively. It was found out that the pulse width upper limit for the chalcogenide memristor to undergo phase change from crystalline to amorphous state is 30 ns with 1.4 V amplitude. However, this is still 5 orders of magnitude faster than that of normal synapses in biological processes (milliseconds).<sup>89</sup> Many phase-change memory devices exhibit the potentiation and depression behavior during pulsing.<sup>97–99</sup> In oxide devices, the initial pulse generates the largest change in the conductance either during potentiation or depression. The succeeding pulses tend to create saturation in the conductance values. This jump in conductance can be attributed to charge trapping and de-trapping processes which normally happen in very short time scales.<sup>100,101</sup> The conductance saturation is the effect of leakage current due to additional stress-induced defects formed after many pulsing

cycles. Detailed studies of STDP variations due to device-specific implementation have been previously reported.<sup>102,103</sup>

The potential application of memristor and memristive system is wide and a lot of areas have not yet been explored in detail. The immediate application in non-volatile memories promises fair alternative to DRAM technology. Neuromorphic and STDP application utilize device properties like fast switching dynamics, multistate and analog switching in various materials systems. Full realization of these applications relies on the fundamental science i.e. better understanding of the filaments dynamics, charge transport and defect formation in memristive materials. Thus, it is imperative to provide thorough investigation of the materials processing and device fabrication of memristive system.

## 2. Materials Processing

This chapter will discuss the growth of ZnO nanowires and  $TiO_2$  thin films as starting materials for the fabrication of memristive devices. First, low-pressure chemical vapor deposition (LPCVD) of ZnO nanowires will be described. Next, atomic layer deposition of  $TiO_2$  thin films will be discussed in detail. It will be important to also mention the dependence of materials preparation to the material properties. Therefore, this will the focus of most of the discussed.

### 2.1 Chemical vapor deposition

Interest in ZnO nanostructure studies have been growing since the development of nanoscience and technology. Sophisticated techniques were developed and improved for nanoscale processing and characterization. ZnO received much interest in areas of electronics, photonics and opto-electronics due to its unique defect chemistry. There are a variety of deposition techniques routinely used for the production of different ZnO nanostructures.<sup>104–108</sup> This includes hydrothermal technique,<sup>109–112</sup> vapor phase transport (carbo-thermal),<sup>113–118</sup> thermal oxidation<sup>119–121</sup> and chemical vapor deposition (CVD).<sup>122–125</sup>

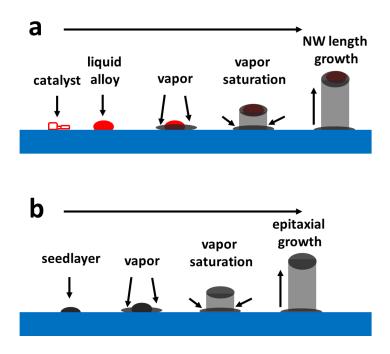

Among the above-mentioned NW growth methods, hydrothermal technique requires the lowest growth temperature (90 °C) while other techniques need higher temperature at least 300 °C. However, post-heat treatment is normally required to minimize the unnecessary impurities in hydrothermally-grown NWs. CVD has more advantages in terms of controlling growth parameters, crystallinity, intentional doping and homogeneity of ZnO NWs. CVD requires only moderate growth temperature and more control in the growth environments. It is well known that different preparation parameters affect the ZnO nanowire properties. Seed-layer has been known to enhance the epitaxial orientation of the grown ZnO NWs. Prior to the NW growth, it is required to perform the initial deposition of metal catalyst or acetated-seedlayer.<sup>122,126,127</sup> The crystal orientation of the seed-layer is independent of the substrate used.<sup>126</sup> Some reports demonstrated that surface roughness assists ZnO NW growth even in a catalyst-free substrate.<sup>118,128</sup> Yu et al.<sup>113</sup> reported the synthesis of ZnO NWs in a substrate without metal catalyst in a double-tube configuration. The purpose of using a smaller

tube is to confine the Zn vapor during reaction. This results to larger Zn-rich region in the tube thereby increasing the length of grown ZnO NWs up to 6  $\mu$ m. However, the vertical growth of nanowires is impeded due to the absence of catalyst or seedlayer for epitaxial growth.

FIG. 2. Nucleation and nanowire growth process in the presence of catalyst (a) and seedlayer (b).

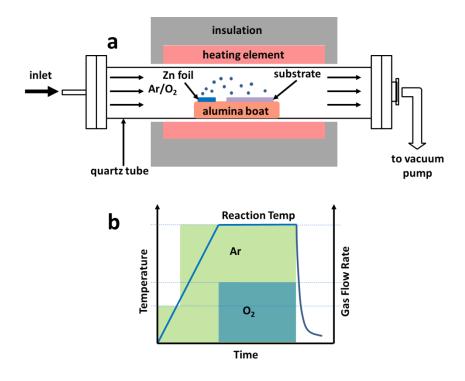

FIG. 3. Schematic diagram of the horizontal tube furnace used (a) and reaction temperature profile (b) for low-pressure chemical deposition (LPCVD) of ZnO NWs.

In this study, a 27 mM solution of zinc acetate di-hydrate was spin-coated on Pt-coated Si/SiO2 substrates, rinsed with ethanol and blown dry with  $N_2$  gas. After covering the substrate with several layers of the solution, it was annealed in air at 350 °C for 20 minutes. This procedure was repeated to have a film consisting of 10 layers.

LPCVD was performed in a typical thermal CVD system consisting of a horizontal quartz tube furnace. The tube was evacuated to about  $10^{-3}$  mTorr base pressure. Zn foil was used as Zn source. The substrate was positioned toward the downstream direction as illustrated in Fig. 3. The standard LPCVD process was done at a temperature of 650 °C for 20 minutes. The system was maintained under vacuum and Ar gas was used a carrier gas with 300 sccm flow rate during the whole process. O<sub>2</sub> gas was introduced with 50-150 sccm flow rate during the growth process.

Several LPCVD trials were made to determine the parameters affecting the growth of ZnO NW. The deposition temperature was varied from 650 to 800 °C. Homogeneous and dense growth of ZnO NWs was observed in the deposition temperature of 650 and 700 °C. The growth ZnO NW also exhibit high c-axis orientation. Previous study in our research group shows single crystal properties of an individual nanowire. Growth of

ZnO NW at 800 °C was not successful. It is possible that the Zn source was completely consumed even before  $O_2$  gas was introduced to the reaction. Adding more Zn source in the chamber and shortening the ramp up time for heating the furnace are possible remedies of the problem. However, this approach seems to be impractical and not cost-effective.

Repeatability of ZnO NW growth is very important for device application. It has been practiced that during sample preparation all the equipment has to be clean ultrasonically cleaned with ethanol. Noticeable differences in the morphology of synthesized ZnO NWs have been observed. The quartz tube is regularly cleaned to maintain the base pressure for each LPCVD process. The successive LPCVD process leaves ZnO deposits on the inner wall of the tube. This also degrades the ZnO NW growth quality and uniformity. Thus, it is imperative to always use a freshly cleaned tube to minimizes the factors that affect the variability of NW growth.

Patterned seedlayers are also used for the NW synthesis. After the spin-coating of seedlayer, standard photolithography and wet etching were done. Circular and rectangular strip patterns are used. It is also demonstrated the possibility of NW growth in sputtered ZnO thin films. These initial experiments are very important in stablishing a standard recipe for the growth of ZnO NWs.

#### 2.2. Atomic Layer Deposition

Atomic layer deposition (ALD) is a vapor phase deposition technique which utilizes surface kinetics during thin film deposition. ALD is a versatile technique of growing crystalline, polycrystalline and amorphous coatings. The early development of atomic layer epitaxy (ALE) started with a need of a robust thin film technology for electroluminescent display devices.<sup>129</sup> Recently, ALD is gradually integrated in semiconductor technology for the production of gate oxides in transistors and dielectric layers in capacitors for memory applications. The metal oxide dielectrics used include TaO<sub>x</sub>, Al<sub>2</sub>O<sub>3</sub>,<sup>130</sup> HfO<sub>2</sub> and TiO<sub>2</sub>. In the case of TiO<sub>2</sub> various metal organic precursors are used Ti source namely titanium tetrachloride (TiCl<sub>4</sub>),<sup>131</sup> titanium ethoxide (Ti(OEt)<sub>4</sub>)<sup>132</sup> and titanium isopropoxide (Ti(O<sup>i</sup>Pr)<sub>4</sub>)<sup>133</sup> among others. Moreover, the typical co-

reactant used as oxidizing precursors are water ( $H_2O$ ), hydrogen peroxide ( $H_2O_2$ ), oxygen gas ( $O_2$ ), ozone ( $O_3$ ) and other oxygen-containing organic compounds.

In a typical ALD, the substrate is exposed to gaseous chemical species that are introduced alternately and separately. This process is said to be self-limiting because the ideal ALD cycle is purely surface reactions in nature. In order to grow a sub-monolayer for each cycle, it is necessary to always have active sites on the substrate surface.<sup>134</sup> There are four steps that take place in one ALD cycle: (1) reactant A dose, typically a metal-organic ligands, (2) purge and pump step, (3) reactant B dose, typically an oxidizing compound and finally (4) purge and pump step. During the dosing of reactant A, the chemical species are chemisorbed onto the substrate. When the substrate is already saturated with reactant A, there will be no more chemisorption and the excess reactants are purged and pumped out of the chamber. This is followed by reactant B exposure. Normally,  $H_2O$  or  $O_3$  is used as co-reactant. Reactant B undergo chemisorption to the A sites until all the sites reacted. The reaction products and excess reactants are purged and pumped out of the chamber in preparation for the next ALD cycle. Substrate saturation during chemisorption is dictated by the reaction temperature.

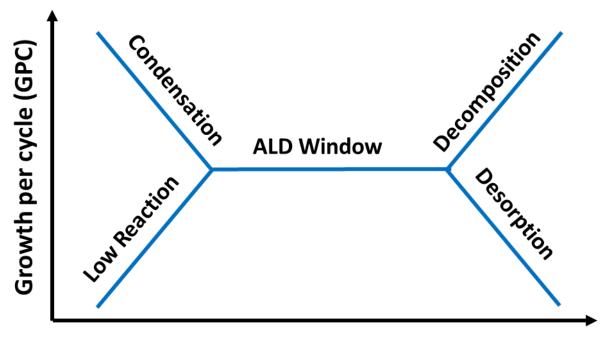

The ALD window is achieved in a temperature range where self-limiting growth occurs. If the reaction temperature is too low or too high, condensation, gas-phase reactions or decomposition may occur. This means that incomplete reactions or some CVD-like reactions due to temperature affect the growth rate. The ideal growth rate per cycle (GPC) is not influenced by the reaction temperature in the ALD window. The figure below (Fig. 4) shows the possible reactions beyond the ideal ALD window. At lower temperature, condensation or low reaction may happen. When precursor vapor is subjected to temperature lower than the temperature of vaporization, there is a possibility of condensation and physisorption of precursors even beyond saturation. This results to an increase in the ALD growth rate. One the other hand, low growth rate occurs during the reaction when the thermal energy (due to low temperature) is not high enough to activate surface reaction. At temperature higher than the ALD window, decomposition of precursors on the substrate happens thereby increasing the GPC. The

reverse effect of desorption occurs when the chemisorbed molecules do not stay on the substrate which limit saturation. This results to an uncontrolled decrease of GPC.

# Temperature

FIG. 4. Ideal ALD window and temperature dependence of growth rate.

Most ALD reactors are similar to CVD systems. The precursor reactions dictate how the system is built. In designing an ALD system, one has to consider the cyclic ALD steps. As described previously, the precursor flow is not continuous unlike in CVD. Moreover, the wide range of deposition pressure has to be considered. The exposure and purge sequence has to be optimized in any type of ALD reactor. A background discussion is given for the different types of ALD reactors namely, flow-type, showerhead, batch, plasma-enhanced and spatial ALD.<sup>135–141</sup>

**Flow-type ALD**. This reactor design is composed of a heated deposition chamber similar to a furnace. The precursor species are directly delivered to the main chamber using a carrier gas. The fluid transport during deposition is maintain to be laminar by controlling the flow rate, pulsing time and purging rate. In most cases, the precursor delivery line is also heated to avoid condensation. The main chamber can only accommodate a full wafer. This is sometimes a limitation considering large-scale manufacturing.

**Showerhead type ALD**. Precursor species delivered to the chamber are evenly distributed using a showerhead. This design prevents CVD-like reactions because it minimizes pressure gradient across the substrate area. A double-chamber design is typical in showerhead type ALD to have uniform temperature close to the substrate. The inner chamber should be of higher temperature than the outer chamber to avoid unnecessary reaction far from the substrate. This is implemented by attaching the outer wall to a cooling system.

**Batch ALD**. A large volume reactor design can accommodate multiple wafer samples for batch ALD processing. This design increases the manufacturing yield for each deposition process. This is beneficial in large-scale manufacturing because ALD is characterized as a slow deposition process for optimum thickness control. Modifications should be implemented regarding the exposure and purging rates. The precursor diffusion is much slower in batch ALD. Thus, the residence time and purging time for each half-cycle should be longer than in a single wafer reactor to maintain the optimum ALD conditions.

**Plasma-enhanced ALD**. Some precursor species require higher thermal energy to activate ALD reaction. The use of plasma energy to activate reaction is implemented without requiring high temperature. This is advantageous for thermally-sensitive precursors and substrates. Co-reactant species do have short lifetimes. Thus, the integrated plasma reactor should be optimized such that the created radicals reside very close to the substrate. PEALD is also advantageous in single reactant ALD for metal thin films.

**Spatial ALD**. In this reactor design, instead of sequential pulsing of precursors the substrate or the substrate holder is moved in the different zones in the chamber. There is continuous flow of precursors in different spatial zones in the chamber. Each spatial zone is considered as a half-reaction region. This can be implemented using a rotary reactor. Multiple flanges can be used to prevent the precursors from mixing once they are introduced to the chamber. This has an advantage in roll-to-roll deposition of flexible substrates or even textiles.

The above-mentioned reactor designs are mostly combined in a single ALD reactor to obtain optimal advantages like film uniformity, low temperature processing and high ALD throughput. For a research-grade ALD system, the integration of in situ thin film and ALD reaction diagnostics is also considered.

The high thickness control and self-limiting characteristics of the ALD process make it possible to deposit thin films in any type of substrate. Conformal ALD coating in high aspect ratio nanostructures for electronic and energy applications was demonstrated.<sup>142–</sup>

<sup>145</sup> Moreover, ALD has much advantage in low-temperature thin film processing especially in self-assembled monolayers (SAMs) and polymeric substrates.<sup>146–150</sup>

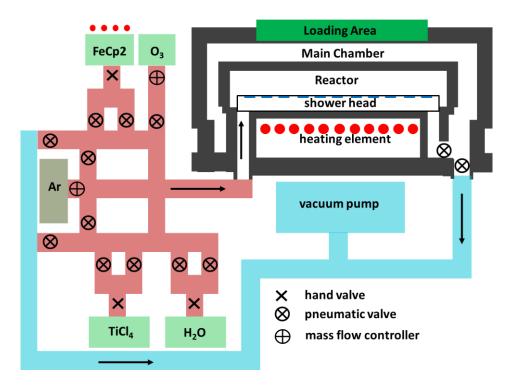

In this study, the ALD tool used was a Beneq TFS-200 model. The schematic diagram is depicted in Fig. 5. The hot wall, flow-through type ALD reactor can accommodate an 8" substrate. The reactor is enclosed in the larger main chamber. The uniformity of deposition is guaranteed also on high aspect-ratio structures (up to 1/50).

FIG. 5. Schematic diagram of the ALD reactor used for the deposition of  $TiO_2$  thin films.

# **2.3. Device Fabrication**

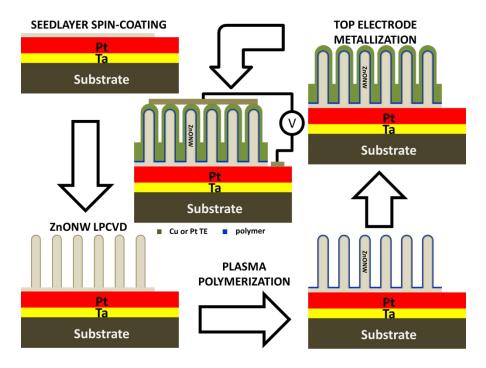

The effect of the ZnO NW interface to the memristive behavior of ZnO NW-based memristive device was investigated in this of the study. Two types of top electrodes were used: Pt and Cu. Pure ZnO NW and polymer-coated ZnO NW were used as insulating layer. A total of four types of devices were prepared.

For the fabrication of ZnO NW memristive devices, a thin Pt layer (200 nm) was deposited on top of ZnO NW layer by sputtering using a hard mask to obtain circular patterns for the top electrode. Fig. 6 shows the steps of the fabrication process.

FIG. 6. Fabrication procedure for Pt/ZnO NW/Pt memristive devices.

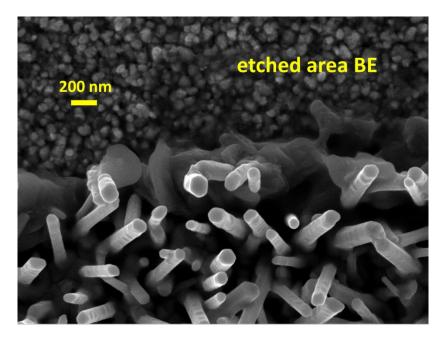

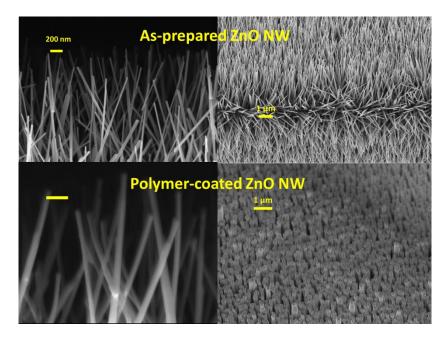

After the deposition of the top electrode, wet etching process was performed to expose the bottom electrode (Fig. 7). A dilute solution containing 1 g of HCl (37%) and 100 mL of distilled water was prepared for the etching process. A portion of the substrate was immersed to the etching solution for 30 s. Then, the etched area was washed with distilled water and dried with  $N_2$  gas. This process was repeated until the optimum continuity of the bottom electrode was obtained. For the ZnO NW-polymer (ZnO NW/PP) core-shell, plasma polymerization of acrylic acid (PPAA) was done in a PECVD system. <sup>151</sup> The ZnO NW was coated conformally with polymer as seen in Fig. 8. Cu electrode was deposited by thermal evaporation and a three-step photolithography procedure was performed to fabricate circular-patterned devices.

FIG. 7. FESEM of ZnO NW array showing the etched area exposing the bottom electrode.

FIG. 8. FESEM of as-prepared and polymer-coated ZnO NW array.

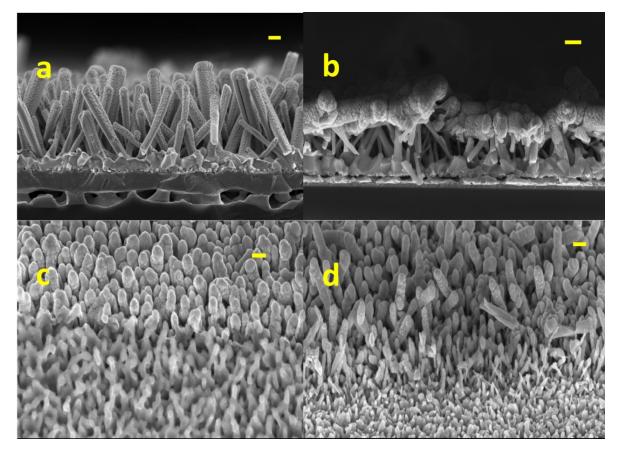

FIG. 9. FESEM of ZnO NW memristive devices: Pt/ZnO NW/Pt (a), Pt/ZnO NW/PP/Pt (b), Cu/ZnO NW/Pt (c) and Cu/ZnO NW/PP/Pt (d). scale bar = 200 nm

Conformal coating of the top electrode on the array of ZnO NWs is shown in Fig. 9. The top electrode coverage reaches the bottom part of the individual NW. It can be assumed that the whole length of the NW is fully covered with the top electrode. This means that the effective thickness of the device is equivalent to the thickness of the film at the bottom of the NW.

The pointed electrical probe is not directly used in contact with the top electrode to avoid excessive scratching during measurement. To measure the IV characteristics of these devices a tungsten coated metal cylinder (D = 1 mm). Few hundred NWs are in contact with the metal cylinder for every measurement. The measured IV characteristics is the average response of the ZnO NWs in contact with the metal cylinder. The current density can be easily calculated based on this set up. Another advantage of using the cylinder is the reduced mechanical pressure on each NW when contacting the top electrode. However, there is a limitation on how to control the contact pressure due to

the mechanical nature of the probe station in use. The use of a flexible probe solves this problem preventing damage on the device prior to electroforming.

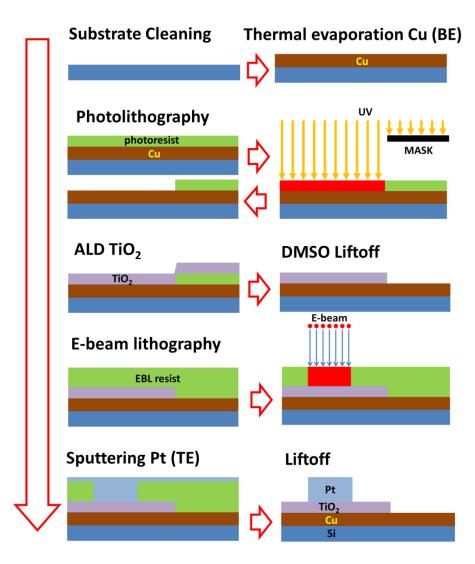

FIG. 10. Fabrication procedure for Cu/TiO2/Pt memristive devices.

Memristive devices based on  $TiO_2$  switching thin layers were fabricated using standard UV photolithography and liftoff wet etching. Standard 4" Si wafers (100, p-type) were used as substrates and washed in piranha cleaning and deionized water.

Electron beam deposition of Cu onto Si provides a continuous layer for the bottom electrode with no further patterning required. A thin Ti interlayer (20 nm) provides the adhesion of the Cu thin film on Si. This prevents portion of the Cu layer from being detached (due to poor adhesion) from the Si wafer during liftoff. The mechanical liftoff

process makes the patterning of the  $TiO_2$  thin layer more straight-forward. The procedure includes deposition of the photoresist (PR), patterning of the PR by photolithography, ALD of the  $TiO_2$  thin films and mechanical liftoff. The details of the procedure<sup>148</sup> are described below:

- Spincoating. A thin layer of PR was spincoated on the Cu bottom electrode.

- **Patterning**. A circular mask of 1.2 mm diameter was used for the standard UV photolithography.

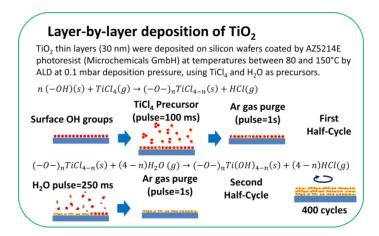

- Atomic layer deposition. Deposition of TiO<sub>2</sub> thin film (30 nm) was performed using low temperature ALD using Ar as the carrier gas. The precursor used are TiCl<sub>4</sub> and H<sub>2</sub>O.

- Liftoff. Etching of the TiO<sub>2</sub> thin layer on the patterned PR was done in ultrasonic bath at 50 °C using dimethyl sulfoxide (DMSO) until the pattern definition was clearly visible. Subsequent rinsing DMSO and deionized water was done followed by drying in N<sub>2</sub> gas.

In order to optimize the liftoff procedure for patterning of TiO<sub>2</sub> layers, several ALD tests at relatively low temperatures were achieved varying the substrate temperature between 80 and 150°C, while carrier gas flow rate (250 sccm), precursor pulse (100 ms), H<sub>2</sub>O pulse (250 ms), purging times (2000 ms) and number of ALD cycles (400) were held constant. A sample processed at 230 °C was used as a standard reference sample. Field-emission scanning electron microscopy (FESEM) was performed on the samples for the morphology and thickness measurement. The FESEM analysis results were used to determine the film growth rate at different temperature. Samples for growth rate calibration were obtained on bare Si substrates by ALD tests using different number of cycles, using the growth conditions described above. To investigate the structure of TiO<sub>2</sub> layers, Raman spectroscopy was performed using a Renishaw inVia Reflex micro-Raman spectrophotometer equipped with a cooled CCD camera. TiO<sub>2</sub> samples (50 nm) for Raman analysis were deposited using the same growth conditions described above on Si substrates with an interlayer made of e-beam evaporated Pt (100 nm) in order to avoid the presence of Si Raman scattering from the substrate, which may interfere with the TiO<sub>2</sub> signal. Samples were excited with a 785 nm wavelength

solid state laser source using 1 sec exposures with 20 iterations and a 10% power filter to avoid  $TiO_2$  crystallization due to prolonged and/or high power laser exposure.

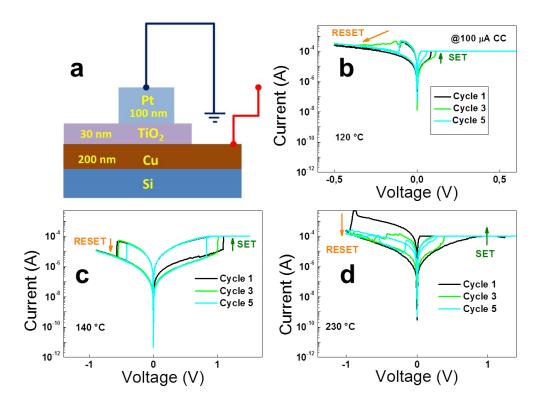

The fabricated memristive devices are made of 30 nm thick  $TiO_2$  layers deposited at 120 and 140°C and patterned using the liftoff technique described above, and on a reference  $TiO_2$  sample deposited at 230°C and patterned by standard photolithography using reactive ion etching. The Pt top electrode (100 nm) was deposited via sputtering following a liftoff procedure similar to the one described above, to obtain circular electrodes of diameter 1 mm. The use of electron beam lithography provides the capability to develop smaller features for microscale (nanoscale) top electrode patterns. The I-V electrical measurements were performed in a two-point contact probe station at room temperature, while maintaining the top (Pt) electrode electrically grounded and the bottom (Cu) electrode under DC voltage sweep.

#### **3.** Materials and Device Properties

This chapter discusses the growth, characterization and performance of synthesized ZnO nanowires and  $TiO_2$  thin film devices. The distinct structure of ZnO NWs has been utilized for more guided and localized filaments. This results to less dispersion between resistance states. The low temperature processing using ALD has been utilized for  $TiO_2$  thin film devices. This approach has posed promising advantages as far as minimizing the fabrication steps is concerned. Moreover, optimization of low temperature processing via ALD allows the use of polymeric and other thermally-sensitive substrates.

## 3.1. ZnO Nanowires

Resistive switching in ZnO NW devices is described in this section. Most of the description on device performance were based on the thin films. The typical IV characteristics of memristive devices show resistance change with change in bias polarities. As described above, this phenomenon is dominated by the formation and dissolution of conducting filaments across the sandwich oxide. However, there are still ambiguities about the origin of the switching and the description of the filament dynamics. Individual switching cycles are said to be of random behavior because the filament dimension is highly localized. The unique configuration of ZnO NWs allows the formation of nanostructure-guided filaments which translates to lesser variation in the IV characteristics.

# 3.1.1. Nanowire Synthesis and Properties

The synthesis of ZnO nanowires starts by preparing seedlayers by spin coating a 27 mM zinc acetate-ethanol solution on Si/SiO<sub>2</sub>/Ta/Pt substrate and annealing the seed layer at 350 °C for 20 minutes. LPCVD was performed in a typical thermal CVD system consisting of a horizontal quartz tube furnace.<sup>122</sup> The tube was evacuated to about 10<sup>-3</sup> mTorr base pressure. Zn foil was used as Zn source. The substrate was positioned toward the downstream direction as illustrated in Fig. 3. The standard LPCVD process was done at a temperature of 650 °C for 20 minutes. The system was maintained under vacuum and Ar gas was used as a carrier gas with 300 sccm flow rate during the whole

process. O<sub>2</sub> gas was introduced with 50-150 sccm flow rate during the growth process at 650 °C. To determine the electrical property of ZnO NWs, Pt top electrodes (200 nm) were deposited via magnetron sputtering using a hard mask (1 mm diameter). The Pt/ZnO NW/Pt devices were measured in a two-point probe configuration using Keithley 4200-SCS parameter analyzer.

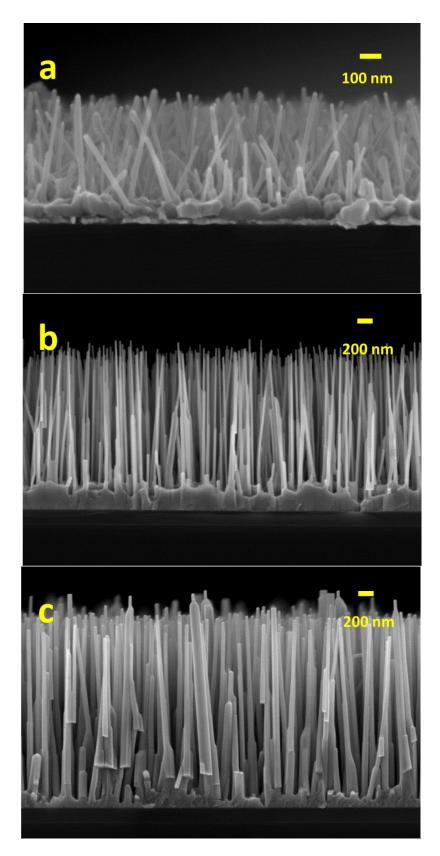

FIG. 11. Cross-section image of ZnO NWs grown with 50 sccm (a), 100 sccm (b) and 150 sccm (c)  $O_2$  flow rates.

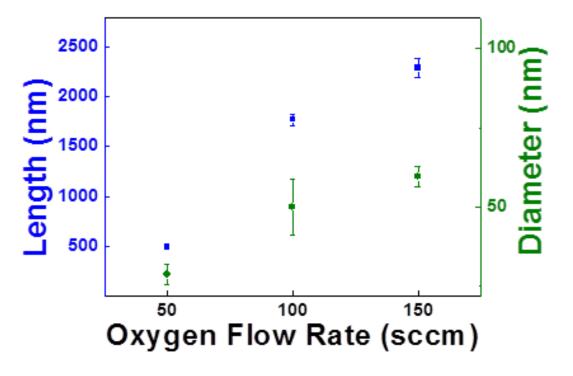

FIG. 12. ZnO NW dimensions (length and diameter) with different oxygen flow rates.

The FESEM cross-section images of the as-grown ZnO NWs with different oxygen flow rates are reported in Fig. 11. The typical length and diameter of the ZnO NWs with 50, 100 and 150 sccm flow rate are 500 nm and 30 nm, 1800 nm and 50 nm, and 2300 nm and 100 nm, respectively. The ZnO NW arrays can be described as having uniform growth in a 1cm x 1 cm substrate. A thin film of thickness about 100 nm is observed at the bottom of the ZnO NW arrays. This is much thicker than the observed features of the ZnO seed layer. It seems that this layer was formed prior to ZnO NW growth as the number of nucleation sites increases with time. The increasing trend in the ZnO NW dimension as shown in Fig. 8 has been the typical feature in O<sub>2</sub> rich CVD growth. This with is also consistent the kinetic and thermodynamic model reported previously.114,152,153

It was also demonstrated that by changing the  $O_2$  concentration inside the tube furnace, one can determine the optimal condition for the onset of nucleation and ZnO NW growth.<sup>152</sup> It is also interesting to note that by increasing the  $O_2$  flow rate, the deposition pressure significantly increases from 1 to 1.4 Torr. Several set of samples were prepared to determine the optimal condition for NW growth. Considering the non-viscous flow of Ar-Zn system, the fluid transport can be described by the equation below:

$$\frac{\partial \rho \phi}{\partial t} + \nabla \cdot (\rho \nu \phi) = \nabla \cdot (D \nabla \phi) + S$$

<sup>(11)</sup>

$\rho$  is the density of the fluid mixture, v is the fluid velocity field vector,  $\phi$  is the concentration, D is the diffusivity and S is the source term.<sup>114</sup>

# **3.1.2. Device Characterization**

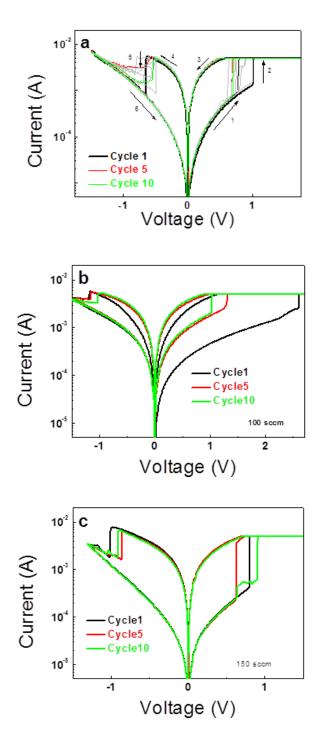

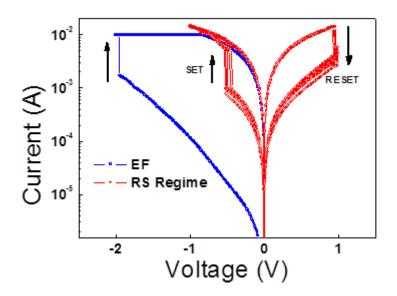

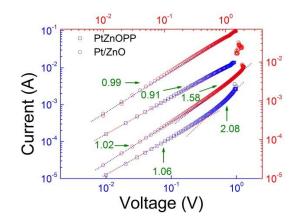

The set of devices prepared was composed of symmetric Pt electrodes. Pt is a stable metal and it does not easily oxidize. Due to the high work function of Pt (5.65 eV) and large electron affinity of ZnO, the Pt-ZnO interface creates a Schottky barrier (0.75 eV).<sup>154,155</sup> Fig. 13 reports the bipolar resistive switching of ZnO NW devices. The resistive switching in one DC cycle was measured using the following steps:

- (1) OFF: Increase positive bias starting from 0 to  $V_{max}$

- (2) SET: Transition from HRS to LRS

- (3) ON: Decrease positive bias starting from  $V_{max}$  to 0

- (4) ON: Decrease negative bias starting from 0 to  $V_{min}$

- (5) RESET: Transition from LRS to HRS

- (6) OFF: Increase negative bias starting from  $V_{min}$  to 0

In a typical cycle, the compliance current was set to 5 mA to prevent permanent breakdown. It can be seen in Fig. 13a that in the positive bias, the device is SET (ON state) around 0.7 V. When the voltage bias is turned off during the ON state, the device remains in the LRS. The device resistance state transitions from LRS to HRS during the negative bias at a RESET voltage around -0.7 V.

FIG. 13. A series of DC sweep plotted in semi-logarithmic IV shows the bipolar resistive switching characteristics of Pt/ZnO NW/Pt devices with different  $O_2$  flow rates: 50 sccm (a), 100 sccm (b) and 150 sccm (c).

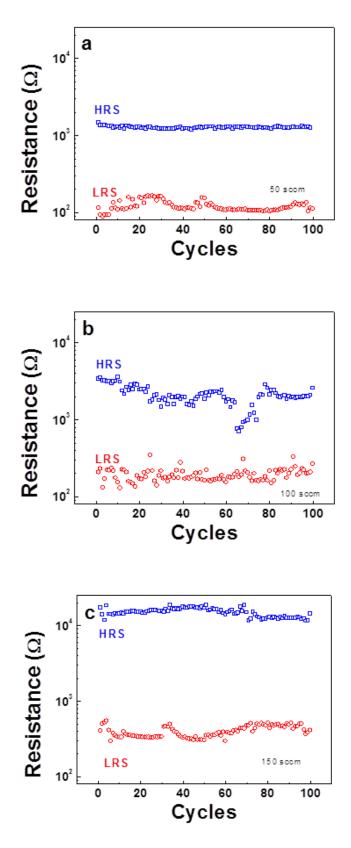

FIG. 14. Resistance characteristics of Pt/ZnO NW/Pt devices for 100 cycles measured at 0.1 V.

The first cycle in Fig. 13b shows that the SET voltage occurs at a higher value around 2.5 V. Although it can be seen that in the succeeding cycles the SET threshold decreases to 1 V, the RESET voltage is found to be around -1 V. Similarly, the device in Fig. 13c has SET voltage around 0.7 V and RESET around 0.8 V.

The stability of resistive bipolar switching of all the devices is also evaluated. The endurance plot presented in Fig. 14 shows the devices in HRS and LRS for 100 cycles. The mean values of HRS for 50, 100 and 150 sccm, respectively are  $1.3 \text{ k}\Omega$ ,  $2.1 \text{ k}\Omega$  and 15 k $\Omega$  while the mean values of LRS are 120  $\Omega$ , 190  $\Omega$  and 400  $\Omega$ . Some variations in the resistance states can be observed especially in the LRS. There is no significant variation in the HRS values of the 50 and 150 sccm devices while noticeable fluctuation is observed in the 100 sccm device.

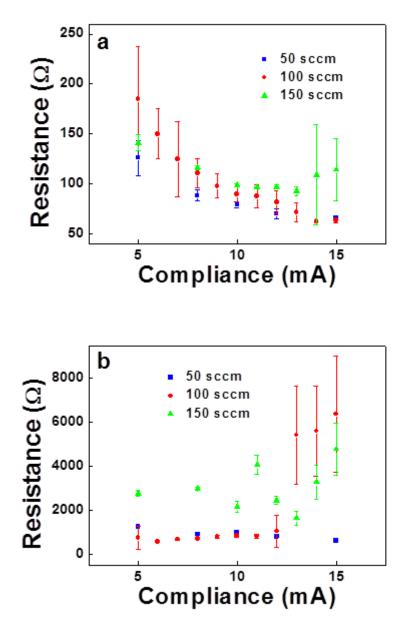

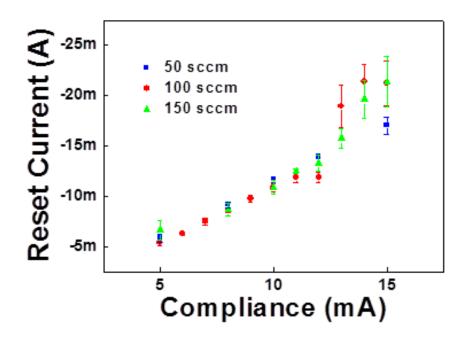

The resistance states variation is also investigated in relation to the current compliance. Fig. 15 reports the variation in LRS and HRS values for a set compliance from 5 mA to 15 mA. The value of LRS decreases with the increase in current compliance. On the other hand, there is no noticeable trend in the value of HRS with current compliance. As shown in Fig. 16, the reset current increases in magnitude with the increase in current compliance. Considering a cylindrical structure of the conducting filament, the decrease value of LRS can be attributed to a larger filament cross-section resulting to lower resistivity.<sup>156</sup> This means that the reset current required should be higher to switch the device back to HRS. The compliance-controlled LRS shows that ZnO NW-based device has potential for multistate memristive application.

FIG. 15. Variations in devices' resistance states: LRS (a) and HRS (b) with different compliance.

FIG. 16. Linear relation of compliance and reset current.

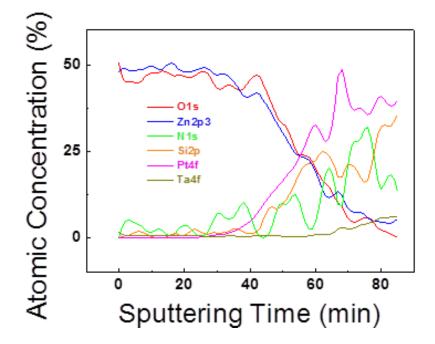

FIG. 17. XPS depth profile of ZnO NW arrays deposited on Si substrate with 150 sccm flow rate.

Fig. 17 reports the XPS depth profile of a representative ZnO NW sample processed at 150 sccm. The approximate surface composition (Zn/O in at. %) of the ZnO NW on Pt/Ta/Si is 51:49. There is a bit more oxygen than Zn content after 40 min of sputtering.

For the next set of devices 150 sccm  $O_2$  flow rate is used as the standard recipe. The Pt/ZnO NW/PP/Pt device is reported in Fig. 18. There is an abrupt increase in the conductivity from the pristine state around -2 V voltage bias. The current compliance (CC) is fixed at 10 mA to prevent Joule heating which can permanently damage the device. In order to obtain reversible switching, the voltage sweep range is set to a lower value of  $\pm$  1 V and the CC is increased. It can be observed that when the positive voltage sweep has reached about 0.9 V the device is switched OFF or RESET. The device stays in the OFF state until the voltage sweep changes polarity and has reached a value of about -0.5 V wherein the SET process occurs. The OFF state of the device is of lower resistance value compared to the device's pristine state. This can be the result of the irreversible forming process that happened prior to the RS measurement. The bipolar switching endurance reaches up to 25 cycles.

FIG. 18. The bipolar resistive switching characteristics of Pt/ZnO NW/PP/Pt device plotted in semi-logarithmic scale.

FIG. 19. The bipolar resistive switching characteristics of Cu/ZnO NW/Pt device plotted in semi-logarithmic scale.

FIG. 20. The bipolar resistive switching characteristics of Cu/ZnO NW/PP/Pt device plotted in semi-logarithmic scale.

The IV characteristics of Cu/ZnO NW/Pt and Cu/ZnO NW/PP/Pt are reported in Fig. 19 and Fig. 20, respectively. Fig. 19 shows the bipolar switching from HRS (7 k $\Omega$ ) to LRS

(800  $\Omega$ ) without electroforming process. It can also be observed that the RESET voltage variance for successive cycles is lower when compared to the SET voltage. In Fig. 20, the Cu/ZnO NW/PP/Pt device has a very high resistance in its pristine state (10<sup>7</sup>  $\Omega$ ). The CC is set to 1 mA accordingly. Unlike the Pt/ZnO NW/PP/Pt device, the electroforming process here happens in the positive bias around 2 V and the RESET voltage is around -1.3 V. After this process, the device is observed to exhibit stable switching from the high resistance state (700 k $\Omega$ ) to low resistance state (3 k $\Omega$ ). Both sets of devices exhibit reversible bipolar switching.

The ON/OFF ratio of the devices are  $\sim 10^2$  (Cu/ZnO NW/PP/Pt) and  $\sim 10^1$  (Cu/ZnO NW/Pt),  $\sim 10^1$  (Pt/ZnO NW/PP/Pt) and  $\sim 10^1$  (Pt/ZnO NW/Pt). The sharp transition from HRS (OFF state) to LRS (ON state) by voltage bias and from LRS to HRS by opposite voltage bias suggests the formation of filaments across the active layer – ZnO NW and core-shell. The current measured through these filaments can be due to Zn interstitials, oxygen vacancies and/or metallic ions. The nature of the dominant carriers for the conduction depends on the electrochemical property of the biased electrode and can be determined based on the polarity of the SET and RESET voltages.

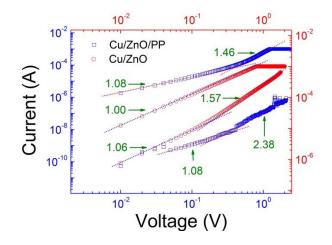

The nonlinear behavior of I with V is also investigated to understand the conduction mechanism in different resistance states. This behavior can have potential application in the neuromorphic processes and learning systems <sup>89</sup>. The double-log scale plots (Fig. 21 and 22) show that at low voltage bias of HRS and LRS, the conduction (slope ~1) obeys Ohm's Law (I  $\alpha$  V) which suggests the formation of conducting filaments. For the rest of the devices, the HRS conduction exhibit Schottky emission or thermionic emission (linear log I vs V <sup>1/2</sup>). Cu/ZnO NW/PP/Pt device on the other hand, shows a steep portion of the conduction in the high resistance state. This conduction (SCLC) which consists of three parts: Region I (trap-filled limited), Region II (steep slope) and Region III (Child's Law). This mechanism relies on the sub-bands exponentially distributed within the ZnO bandgap. The nonlinearity observed can be attributed to the presence of PPAA layer by: (i) altering the surface states of ZnO NW<sup>157,158</sup> and (ii) forming a high barrier between Cu and ZnO NW as shown by the high PRS value of this device <sup>159–161</sup>.

FIG. 21. Line fitting in log-log scale IV characteristics of pure and polymer-coated ZnO NW memristive devices with Pt TE.

FIG. 22. Line fitting in log-log scale IV characteristics of pure and polymer-coated ZnO NW memristive devices with Cu TE.

FIG. 23. Three regions of high-field conduction in Cu/ZnO NW/PP/Pt device describing space-charge limited conduction (SCLC) mechanism.

For the Cu/ZnO NW/Pt device, hole injection through the top electrode is more favorable than electron injection. Cu and ZnO NW surface contact has lower barrier height (0.45 eV) than Pt/ZnO NW due to lower work function of Cu (4.65) <sup>155,162</sup>. This indicates that when the top electrode is under positive bias,  $Cu^{Z+}$  (Z = 1 or 2) ions diffuse from the top electrode and migrate through the ZnO NW grain boundaries towards the Pt bottom electrode <sup>163</sup>. The conduction is highly field-dependent because the probability that  $Cu^{Z+}$  ions recrystallize in the ZnO NW/Pt interface and build up into a chain of conducting filament relies on the polarity, magnitude and duration of the applied bias <sup>30</sup>. The device is now switched to LRS (SET) and it can only be switched to HRS (RESET) under negative bias sufficient enough to dissolve the Cu filaments. This diffusion of  $Cu^{Z+}$  ions is totally reversible such that there is no need for electrofoming process. We also use a higher CC (10 mA) on other devices for the first switching cycle and we observed the same value for HRS. The only difference that we observed is the higher RESET current requirement for higher CC. Under this circumstance, the larger area of filament formed needs larger current to dissolve during RESET <sup>164</sup>.

The conduction in the ZnO NW-polymer devices is observed to have nonlinear behavior in the high voltage bias. As discussed above, thermionic emission is the dominant conduction mechanism in pure ZnO NW devices regardless of the top electrode used. On the other hand, in Cu/ZnONW/PP/Pt devices the conduction is dominated by SCLC. With the large energy gap between the lowest unoccupied molecular orbital (LUMO) and the highest occupied molecular orbital (HOMO), PPAA becomes a charge blocking layer for Cu<sup>Z+</sup> ions injection through the ZnO NW layer. If a positive bias is applied to the Cu electrode, the ZnO layer becomes less negative due to screening effect of the PPAA polarization. Thus, the filament formed are expected to be thinner and growing on both in PPAA and ZnO NW layers. This may be the reason why electroforming is still necessary and nonlinearity is observed even in the LRS. There may be differences in the filament growth rate in PPAA and ZnO NW layers due to the differences in the conductivity of the two layers. This can be the reason of the large voltage variance at the onset of trap-filled limited conduction for multiple switching cycles. The operating current (1 mA CC) of these devices is enough that possible modification in the PPAA happens and its insulating property enhances the RS behavior of the device. For the

Pt/ZnO/PP/Pt device, we have not observed the same behavior seemingly because of the higher operating current (10 mA CC) to form vacancies.

#### **3.2.** TiO<sub>2</sub> Thin Films

The discussion on this section is based on the published article cited in the reference.<sup>148</sup> Low temperature ALD processing of  $TiO_2$  thin films is explored for the fabrication of memristive devices. ALD can be used for the deposition of amorphous films of high quality and conformal coating. There is a wide selection of substrates where ALD is compatible in terms of area, surface roughness and porosity. The ALD growth conditions can be tuned in a way to accommodate polymeric photoresists prior to the ALD process. This approach eliminates additional patterning techniques by doing the liftoff process immediately after the ALD of  $TiO_2$  films. The use of asymmetric electrode namely Pt and Cu, provided another approach of understanding the electrochemical metallization mechanism in the formation of filaments during resistive switching.

### **3.2.1.** Thin Film Synthesis and Properties

The layer-by-layer deposition  $TiO_2$  is described by the two surface reactions below.<sup>165</sup>

$$n (-OH)(s) + TiCl_4(g) \rightarrow (-O_n)_n TiCl_{4-n}(s) + HCl(g)$$

$$\tag{12}$$

$$(-0-)_n TiCl_{4-n}(s) + (4-n)H_20(g) \to (-0-)_n Ti(OH)_{4-n}(s) + (4-n)HCl(g)$$

(13)

Fig. 24. Typical surface reactions during one ALD cycle of TiCl<sub>4</sub> and H<sub>2</sub>O pulsing.

In the first-half cycle,  $TiCl_4$  reacts with the surface OH molecules releasing HCl after the reaction. In the second half-cycle,  $H_2O$  vapor is introduced to the reaction. Surface  $TiCl_{4-n}$  reacts with  $H_2O$  molecules releasing another HCl molecule as by-product. At the end of the second-half cycle, OH species are now readily available for the next ALD cycle. Moreover, it takes several ALD cycles to completely achieve fully-coated substrate and constant ALD cycle.

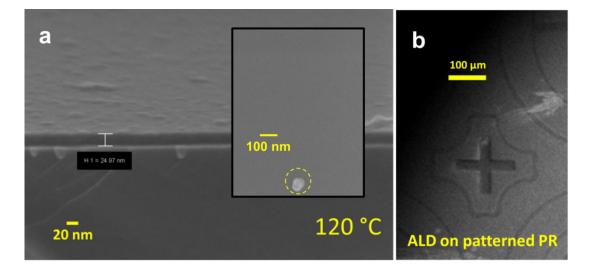

FIG. 25. FESEM image of ALD  $TiO_2$  thin film on Si substrate deposited at 120 °C (a) and effective DMSO liftoff of ALD  $TiO_2$  thin films on patterned PR (b).

TiO<sub>2</sub> films by ALD showed continuous and smooth morphology in the deposition temperature selected for this study. Fig. 25a shows a cross-section image of a film deposited at 120 °C on Si. It shows uniform thickness and homogeneous morphology from the initial ALD cycles (bottom) up to the end of the ALD process. All films deposited from 80 to 140 °C show smooth surface morphology. Excellent mechanical liftoff process is also possible in this process temperature range. This is shown by the well-defined patterns on the TiO<sub>2</sub> films after the lift off (Fig. 25b). It can be inferred from these results that in this ALD window, the polymeric PR does not degrade during the ALD process.

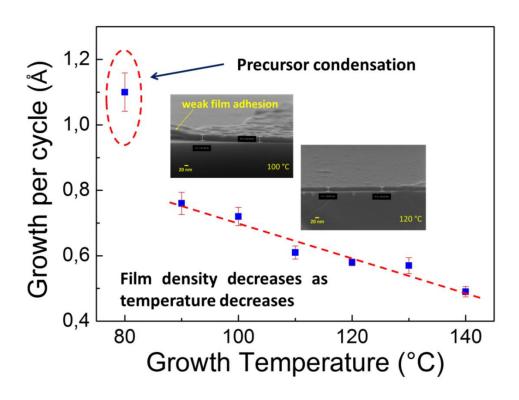

FIG. 26. Growth rate of TiO<sub>2</sub> films shows decreasing trend as temperature increases.

The growth rate per cycle (GPC) for a particular ALD process temperature was also calculated. Thickness was measured in the acquired FESEM images and divided it by number of ALD cycles. In Fig. 26, the GPC value from 90 to  $140^{\circ}$ C is less than 0.8 Å/cycle. The GPC for 80 °C is 1.1 Å/cycle. This value is much higher than what is expected in a typical ALD. There are two possible reasons for the observed increase in GPC: (i) condensation and (ii) incomplete surface reaction. During low temperature ALD processing, H-bonded OH groups dominate the surface exchange reaction. Condensation of H-bonded OH occurs, thereby increasing the number of reactive sites. In this situation there is a possibility that more precursor species participate in the ALD half-reaction beyond the surface saturation. Moreover, the presence of H<sub>2</sub>O vapor at 80 °C depends solely on the partial pressure and not on the reactor temperature. Considering these observations, only thin films prepared at 120 °C or higher were considered for device fabrication.

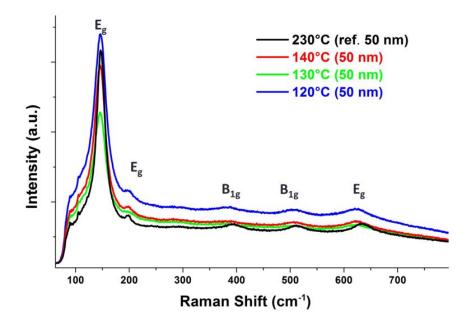

FIG. 27. Raman spectra of TiO2 thin layers on Pt deposited at 120 °C to 230 °C.

Raman spectroscopy was performed on 50-nm TiO<sub>2</sub> thin layers deposited at 120, 130, 140 and 230 °C (Fig. 27). The prominent peaks at 144, 197 and 639 cm<sup>-1</sup> are assigned to  $E_g$  mode. The peaks at 399 and 519 cm<sup>-1</sup> are assigned to the  $B_{1g}$  mode. All the peaks seen in the spectra corresponds to the anatase phase of TiO<sub>2</sub>. The peak at 144 cm<sup>-1</sup> is significantly sharper than the rest of the peaks. It is worthwhile to note that we can obtain such a sharp peak even at a very low process temperature. Previous work reported weak signal from this Raman line for films grown at 150 °C and 175 °C and it is only expected to increase around 200 °C.<sup>166</sup> Raman peaks (not shown) observed from thicker samples (500 nm) exhibit sharper features. This can be correlated to the formation of larger grains and higher surface roughness of the film.

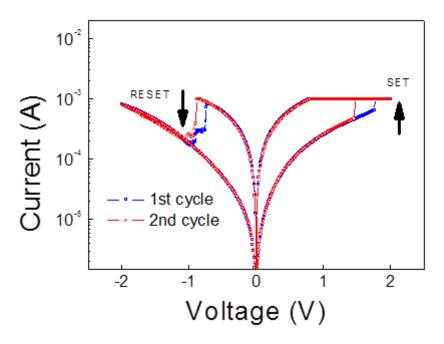

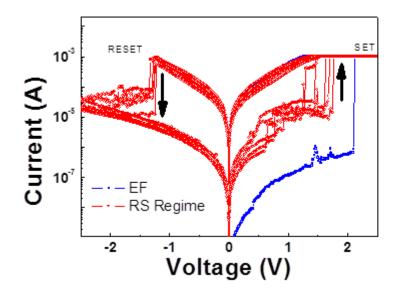

# **3.2.2. Device Characterization**

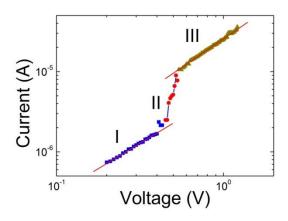

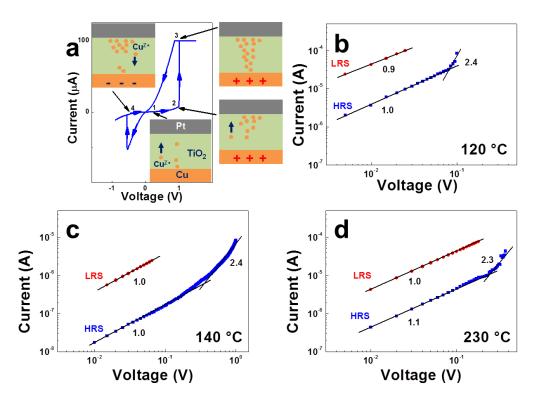

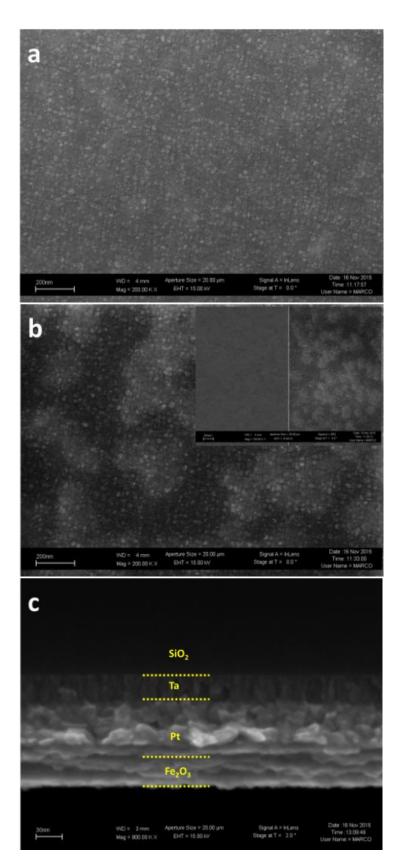

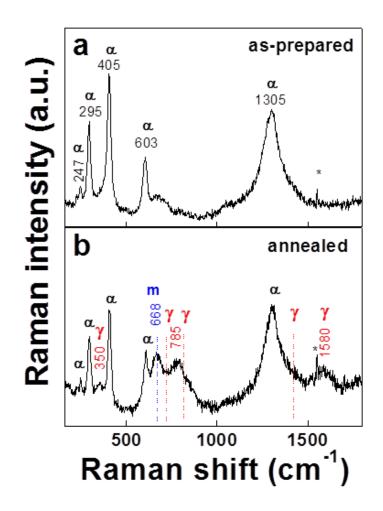

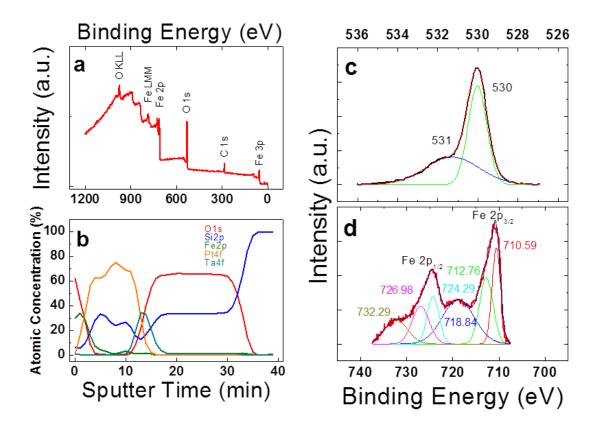

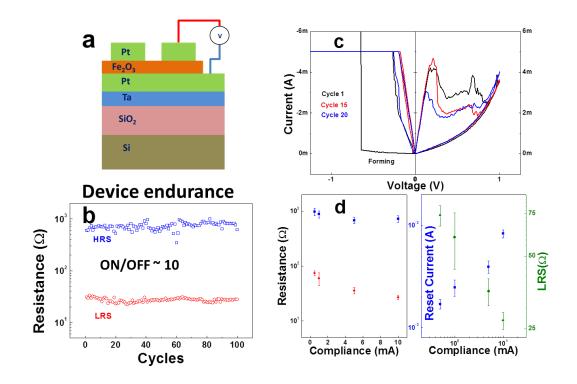

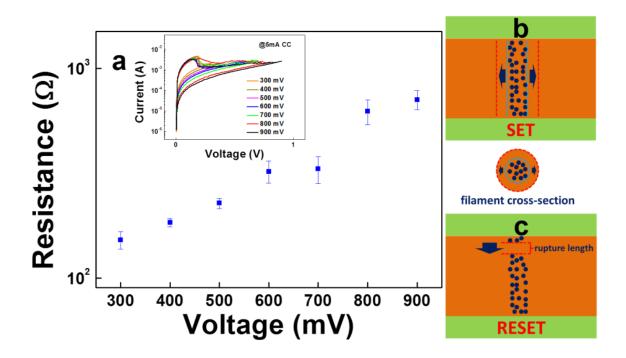

FIG. 28. Schematic diagram of the Cu/TiO<sub>2</sub>/Pt devices (a) semi-logarithmic I-V curves of devices with TiO<sub>2</sub> grown at 120 (b), 140 (c) and 230°C (d), showing the first 5 memristive cycles. The devices work in bipolar resistive switching.