# Dynamic Partial Reconfiguration for Dependable Systems

Giulio Gambardella

Giulio.Gambardella@polito.it

Submitted in total fulfillment of the requirements of the degree of Doctor of Philosophy

January 2014

Faculty of Computer Engineering Department of Control and Computer Engineering Politecnico di Torino

Herewith declare that I have produced this paper without the prohibited assistance of third parties and without making use of aids other than those specified; notions taken over directly or indirectly from other sources have been identified as such. This thesis has not previously been presented in identical or similar form to any other Italian or foreign examination board. The thesis work was conducted from 01/2011 to 12/2014 under the supervision of Prof. Paolo Prinetto at Politecnico di Torino.

### LIST OF PUBLICATIONS

### Journal papers

S. Di Carlo, **G. Gambardella**, P. Prinetto, D. Rolfo, P. Trotta: *SATTA: a Self-Adaptive Temperaturebased TDF awareness methodology for dynamically reconfigurable FPGAs*, ACM Transactions on Reconfigurable Technology and Systems (TRETS)

S. Di Carlo, **G. Gambardella**, P. Prinetto, D. Rolfo, P. Trotta: *SA-FEMIP: a Self-Adaptive Features Extractor and Matcher IP-core based on Partially Reconfigurable FPGAs for Space Applications*, IEEE Transactions on Very Large Scale Integration Systems (TVLSI)

### **Conference** papers

S. Di Carlo, **G. Gambardella**, M. Indaco, D. Rolfo, P. Prinetto: *A unifying formalism to support automated synthesis of SBSTs for embedded caches*, on Proceedings of the 9th East-West Design & Test Symposium (EWDTS), pages 39–42, 9<sup>th</sup> – 12<sup>th</sup> September 2011, Sebastopol (Ukraine).

S. Di Carlo, **G. Gambardella**, M. Indaco, D. Rolfo, P. Prinetto: *MarciaTesta: an automatic generator of test programs for microprocessors' data caches*, on Proceedings of the 20th Asian Test Symposium (ATS), pages 401–406, 20<sup>th</sup> – 23<sup>rd</sup> November 2011, New Delhi (India).

S. Di Carlo, **G. Gambardella**, M. Indaco, D. Rolfo, P. Prinetto: *Validation & Verification of an EDA automated synthesis tool*, on Proceedings of the 6th International Design and Test Workshop (IDT), pages 48–52, 11<sup>th</sup> – 14<sup>th</sup> December 2011, Beirut (Lebanon).

S. Di Carlo, **G. Gambardella**, M. Indaco, D. Rolfo, G. Tiotto, P. Prinetto: *An Area-Efficient 2-D Convolution Implementation on FPGA for Space Applications*, on Proceedings of the 6th International

Design and Test Workshop (IDT), pages 88–92, 11<sup>th</sup> – 14<sup>th</sup> December 2011, Beirut (Lebanon).

S. Di Carlo, S. Galfano, **G. Gambardella**, M. Indaco, P. Prinetto, D. Rolfo, P. Trotta: *NBTI Mitigation by Dynamic Partial Reconfiguration*, on Proceedings of the 13th Biennal Baltic Electronics Conference (BEC), pages 93–96, 3<sup>rd</sup> – 5<sup>th</sup> October 2012, Tallinn (Estonia).

S. Di Carlo, **G. Gambardella**, T. Huynh Bao, P. Prinetto, D. Rolfo, P. Trotta: *ZipStream: improving dependability in Dynamic Partial Reconfiguration*, on Proceedings of the 7th International Design and Test Symposium (IDT), pages 1–6, 15<sup>th</sup> – 17<sup>th</sup> December 2012, Doha (Qatar).

S. Di Carlo, **G. Gambardella**, P. Lanza, P. Prinetto, D. Rolfo, P. Trotta: *SAFE: a Self Adaptive Frame Enhancer FPGA-based IP-core for real-time space applications*, on Proceedings of the 7th International Design and Test Symposium (IDT), pages 1–6, 15<sup>th</sup> – 17<sup>th</sup> December 2012, Doha (Qatar).

S. Di Carlo, **G. Gambardella**, M. Indaco, I. Martella, P. Prinetto, D. Rolfo, P. Trotta: *A software-based self test of CUDA Fermi GPUs*, on Proceedings of the 18th European Test Symposium (ETS), pages 1–6, 27<sup>th</sup> – 30<sup>th</sup> May 2013, Avignon (France).

S. Di Carlo, **G. Gambardella**, M. Indaco, I. Martella, P. Prinetto, D. Rolfo, P. Trotta: *Increasing the robustness of CUDA Fermi GPU-based systems*, on Proceedings of the 19th International On-Line Testing Symposium (IOLTS), pages 234–235, 8<sup>th</sup> – 10<sup>th</sup> July 2013, Chania (Greece).

S. Di Carlo, **G. Gambardella**, P. Lanza, P. Prinetto, D. Rolfo, P. Trotta: *FEMIP: A high performance FPGA-based features extractor & matcher for space applications*, on Proceedings of the 23rd International Conference on Field Programmable Logic and Applications (FPL), pages 1–4, 2<sup>nd</sup> – 4<sup>th</sup> September 2013, Porto (Portugal).

S. Di Carlo, **G. Gambardella**, M. Indaco, P. Prinetto, D. Rolfo, P. Trotta: *Dependable Dynamic Partial Reconfiguration with minimal area & time overheads on Xilinx FPGAs*, on Proceedings of the 23rd International Conference on Field Programmable Logic and Applications (FPL), pages 1–4, 2<sup>nd</sup> – 4<sup>th</sup> September 2013, Porto (Portugal).

S. Di Carlo, **G. Gambardella**, I. Martella, P. Prinetto, D. Rolfo, P. Trotta: *Fault mitigation strategies for CUDA GPUs*, on Proceedings of the International Test Conference (ITC), pages 1–8, 6<sup>th</sup> – 13<sup>th</sup> September 2013, Anaheim (USA).

T. Sanislav, G. Mois, S. Folea, L. Miclea, **G. Gambardella**, P. Prinetto: *A cloud-based Cyber-Physical System for environmental monitoring*, on Proceedings of the 3rd Mediterranean Conference on

Embedded Computing (MECO), pages 6–9, 15<sup>th</sup> – 19<sup>th</sup> June 2014, Budva (Montenegro).

S. Di Carlo, **G. Gambardella**, P. Prinetto, D. Rolfo, P. Trotta, A. Vallero: *A novel methodology to increase fault tolerance in autonomous FPGA-based systems*, on Proceedings of the 20th International On-Line Testing Symposium (IOLTS), pages 87–92, 7<sup>th</sup> – 9<sup>th</sup> July 2014, Platja d'Aro (Spain).

S. Di Carlo, **G. Gambardella**, P. Prinetto, F. Reichenbach, T. Løkstad, G. Rafiq: *On enhancing fault injection's capabilities and performances for safety critical systems*, on Proceedings of the 17th Euromicro Conference on Digital System Design (DSD), pages 583–590, 27<sup>th</sup> – 29<sup>th</sup> August 2014, Verona (Italy).

## **CONTENTS**

| Lis | List of Figures vii |         |                                                                 |    |

|-----|---------------------|---------|-----------------------------------------------------------------|----|

| Lis | st of T             | ables   |                                                                 | x  |

| 1   | Intr                | oductio | n                                                               | 1  |

| 2   | Dep                 | endabil | ity issues in digital systems: an overview                      | 5  |

|     | 2.1                 | Single  | Event Effects                                                   | 6  |

|     |                     | 2.1.1   | Physical causes                                                 | 9  |

|     |                     | 2.1.2   | Single Event Transient in digital logic                         | 10 |

|     |                     | 2.1.3   | Single Event Upset in SRAM                                      | 14 |

|     | 2.2                 | NBTI:   | Causes and Effects                                              | 16 |

|     |                     | 2.2.1   | Effects on digital logic                                        | 20 |

|     |                     | 2.2.2   | Effects on SRAM memories                                        | 22 |

| 3   | FPG                 | A archi | tecture and Dynamic Partial Reconfiguration                     | 25 |

|     | 3.1                 | FPGA    | Families                                                        | 26 |

|     |                     | 3.1.1   | Antifuse-based FPGAs                                            | 28 |

|     |                     | 3.1.2   | Flash-based FPGAs                                               | 29 |

|     | 3.2                 | SRAM    | -based FPGAs                                                    | 31 |

|     | 3.3                 | Dynan   | nic Partial Reconfiguration                                     | 33 |

| 4   | Enh                 | ancing  | dependability of dynamically partially reconfigurable systems   | 41 |

|     | 4.1                 | Depen   | dable DPR with minimal Area & Time overheads on Xilinx FPGAs    | 42 |

|     |                     | 4.1.1   | Xilinx approach                                                 | 42 |

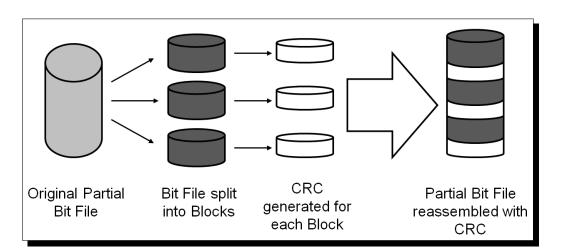

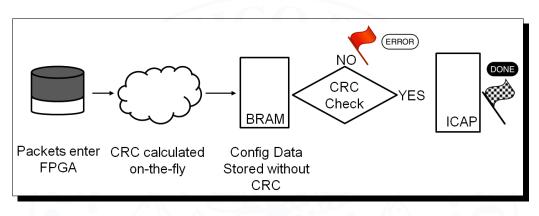

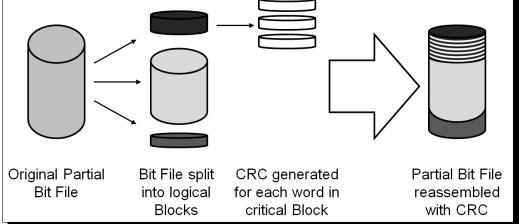

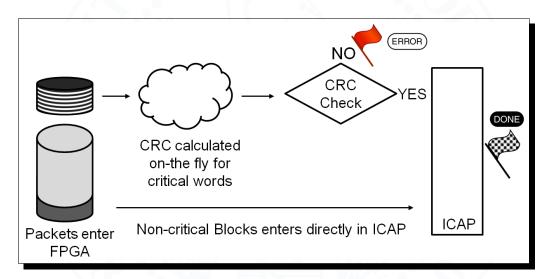

|     |                     | 4.1.2   | Proposed Methodology                                            | 44 |

|     |                     |         | 4.1.2.1 Partial bitstream file splitting                        | 45 |

|     |                     |         | 4.1.2.2 DfD#1: Critical links protection                        | 48 |

|     |                     |         | 4.1.2.3 DfD#2: Critical modules protection                      | 48 |

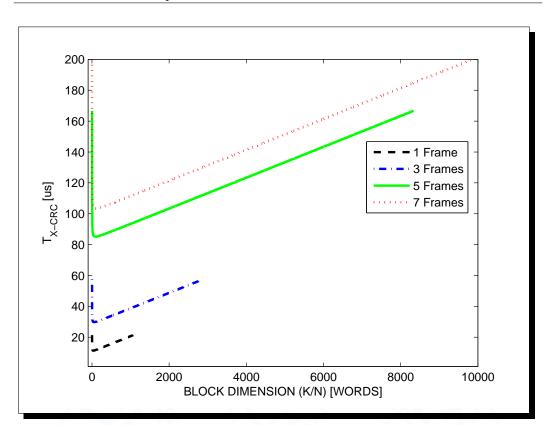

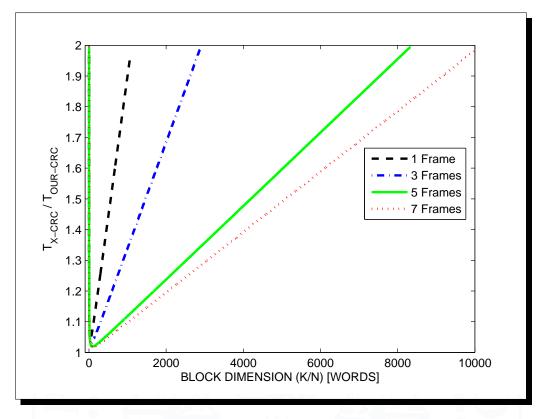

|     |                     | 4.1.3   | Experimental results                                            | 48 |

|     |                     |         | 4.1.3.1 Xilinx approach implementation                          | 49 |

|     |                     |         | 4.1.3.2 Proposed approach implementation                        | 50 |

|     |                     |         | 4.1.3.3 Comparison                                              |    |

|     | 4.2                 | ZipStr  | eam: improving dependability in Dynamic Partial Reconfiguration | 55 |

| Bi | Bibliography |          |                                                                                                 |      |

|----|--------------|----------|-------------------------------------------------------------------------------------------------|------|

| 5  | Con          | clusions |                                                                                                 | 93   |

|    |              | 4.4.3    | Experimental results                                                                            | . 86 |

|    |              | 4.4.2    | SATTA integration methodology                                                                   | . 83 |

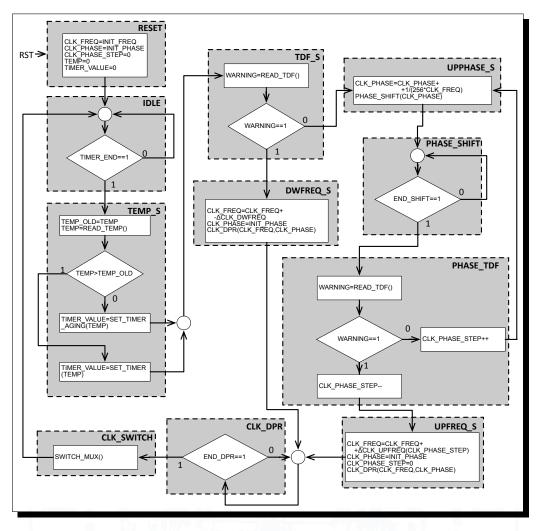

|    |              |          | 4.4.1.4 Manager                                                                                 | . 79 |

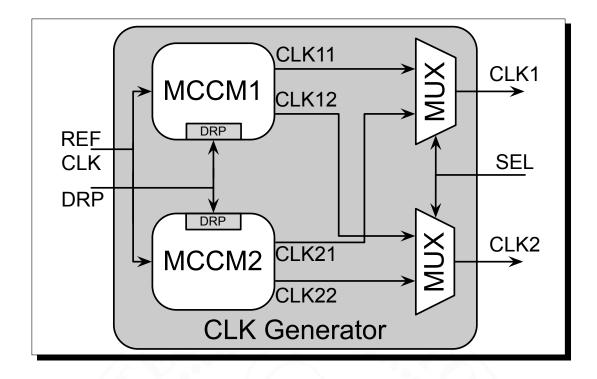

|    |              |          | 4.4.1.3 CLK Generator                                                                           | . 77 |

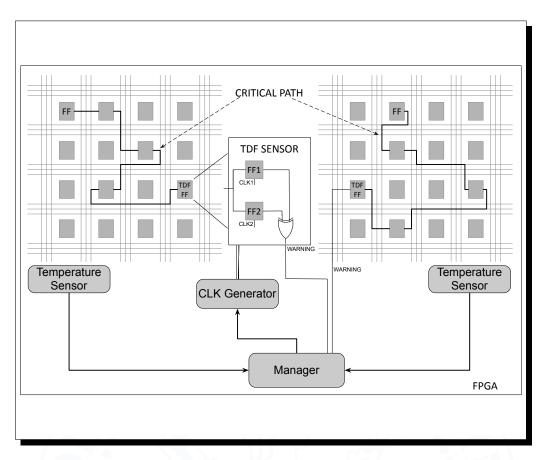

|    |              |          | 4.4.1.2 TDF Sensor                                                                              | . 76 |

|    |              |          | 4.4.1.1 Temperature Sensor                                                                      | . 74 |

|    |              | 4.4.1    | SATTA sensors organization and architecture                                                     | . 73 |

|    | 4.4          |          | a Self-Adaptive Temperature-based TDF awareness methodology for dy-<br>lly reconfigurable FPGAs |      |

|    |              | 4.3.3    | Experimental results                                                                            |      |

|    |              | 4.3.2    | Case study                                                                                      | . 66 |

|    |              |          | 4.3.1.3 DfD#3: Smart external controller                                                        | . 65 |

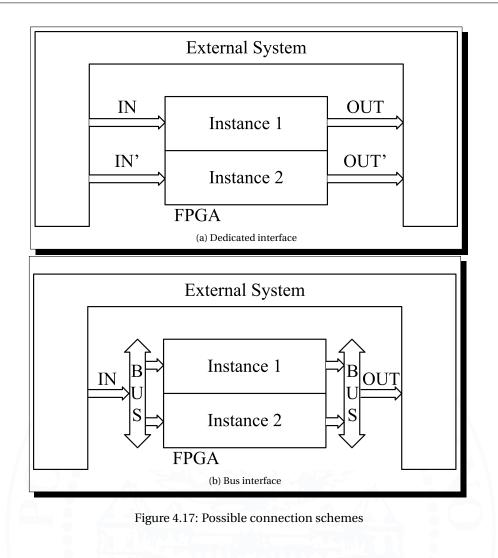

|    |              |          | 4.3.1.2 DfD#2: Using different interfaces                                                       | . 65 |

|    |              |          | 4.3.1.1 DfD#1: Static connection avoidance                                                      | . 64 |

|    |              | 4.3.1    | Proposed Methodology                                                                            | . 64 |

|    | 4.3          | NBTI N   | litigation by Dynamic Partial Reconfiguration                                                   | . 64 |

|    |              | 4.2.3    | Experimental results                                                                            | . 60 |

|    |              |          | 4.2.2.3 Design-for-Dependability rule                                                           | . 59 |

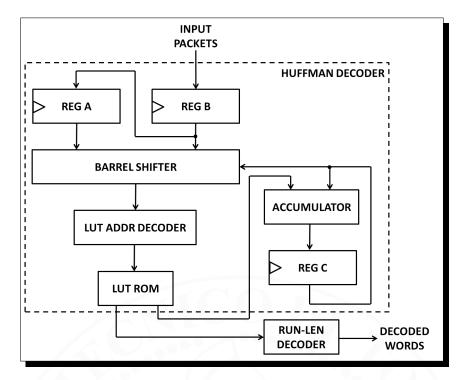

|    |              |          | 4.2.2.2 Hardware Decompressor                                                                   | . 58 |

|    |              |          | 4.2.2.1 Compression Algorithm                                                                   | . 57 |

|    |              | 4.2.2    | ZipStream Methodology                                                                           | . 56 |

|    |              | 4.2.1    | Compression Algorithms overview                                                                 | . 55 |

### LIST OF FIGURES

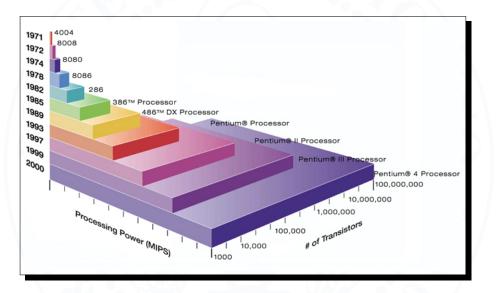

| 1.1  | Moore's Law applied at Intel's processors                                                 | 1  |

|------|-------------------------------------------------------------------------------------------|----|

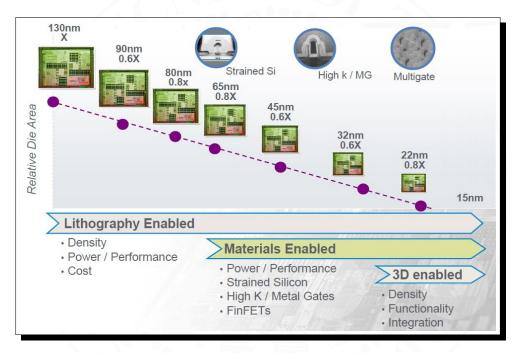

| 1.2  | 3 different technology enablers in recent nodes (by Global Foundries)                     | 2  |

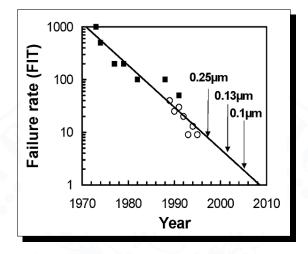

| 1.3  | Required failure rates over years [25]                                                    | 3  |

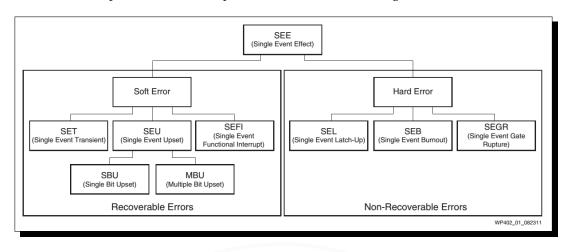

| 2.1  | Types of Single Event Effects [65]                                                        | 7  |

| 2.2  | Impact of a high-energy particle in a CMOS structure [54]                                 | 8  |

| 2.3  | Differential flux for atmospheric neutrons, protons, muons and pions at ground level      |    |

|      | in Marseille, France [7]                                                                  | 9  |

| 2.4  | Representation of charge collection in a silicon junction immediately after (a) an ion    |    |

|      | strike, (b) prompt (drift) collection, (c) diffusion collection, (d) the junction current |    |

|      | induced as a function of time [9]                                                         | 11 |

| 2.5  | Funneling in an n+/p silicon junction following an ion strike: (a) electrostatic poten-   |    |

|      | tial and (b) electron concentration [30]                                                  | 12 |

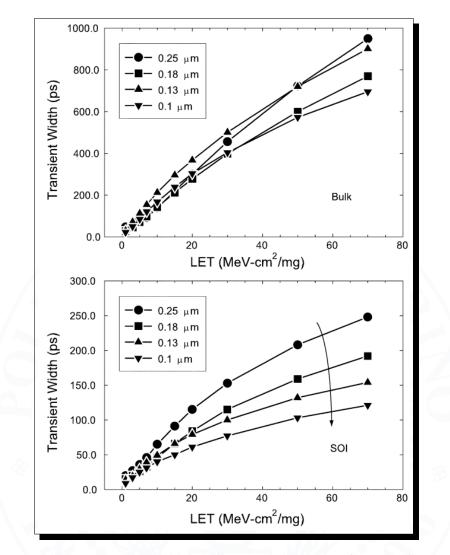

| 2.6  | Single-event transient width in bulk and SOI devices as a function of LET and technol-    |    |

|      | ogy scaling [21]                                                                          | 13 |

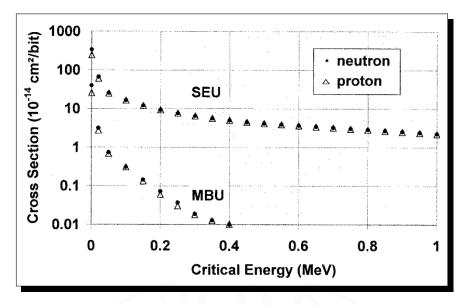

| 2.7  | SEU and MBU cross sections versus critical energy [61]                                    | 15 |

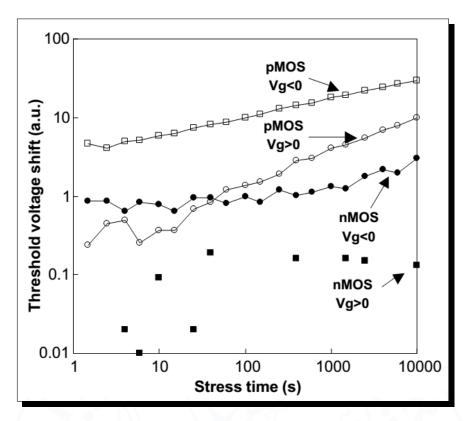

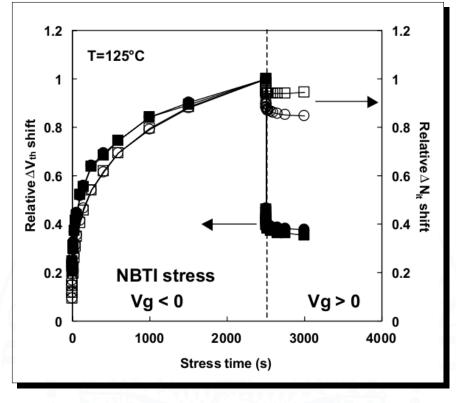

| 2.8  | Vth shift as a function of stress time [31]                                               | 17 |

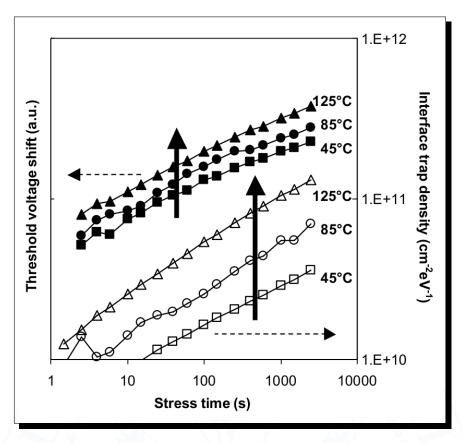

| 2.9  | Vth shift and interface traps creation as a function of stress time for three different   |    |

|      | temperatures[31]                                                                          | 18 |

| 2.10 | Relative shifts for traps and Vth versus stress time [31]                                 | 19 |

| 2.11 | Stress and recovery phases on transistor [57]                                             | 20 |

| 2.12 | Threshold voltage degradation during stress and recovery phases [57]                      | 21 |

| 2.13 | 6 Transistor SRAM cell                                                                    | 23 |

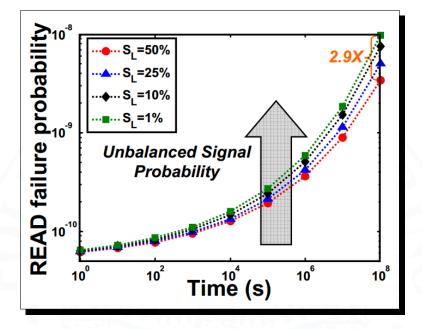

| 2.14 | Read failure probability with different static probablityes [37]                          | 24 |

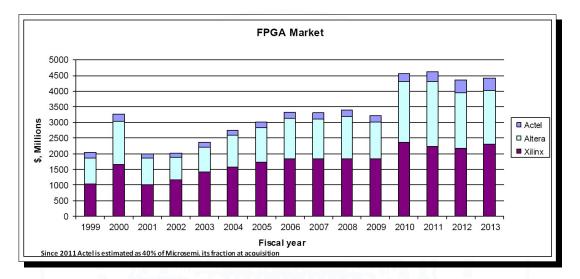

| 3.1  | FPGA market share in recent years                                                         | 26 |

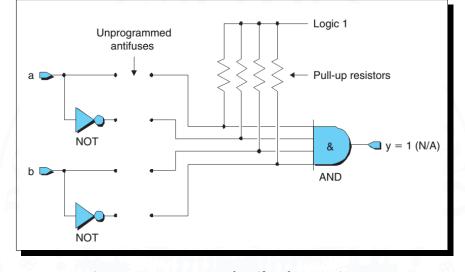

| 3.2  | Unprogrammed antifused connections [44]                                                   | 28 |

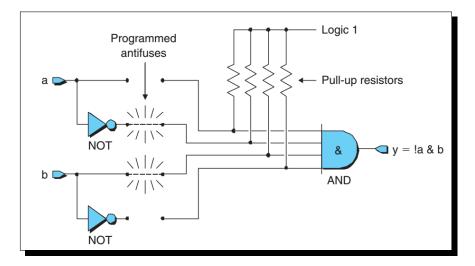

| 3.3  | Programmed antifused connections [44]                                                     | 29 |

| 3.4  | Floating Gate transistor [44]                                                             | 30 |

| 3.5  | Adaptive Logic Modules architecture [4]                                                   | 32 |

| 3.6  | Configurable Logic Block architecture [69]                                                | 32 |

| 3.7  | Slice architecture [69]                                                                   | 33 |

| 3.8  | Dynamic Partial Reconfiguration - Basic Idea                                              | 34 |

| 3.9  | Partial Reconfiguration software flow [71]                                                | 36 |

|------|-------------------------------------------------------------------------------------------|----|

| 3.10 | Partial Bitstream download [71]                                                           | 37 |

| 3.11 | Reconfiguration by mean of external microprocessor [71]                                   | 38 |

| 4.1  | Xilinx solution - Bitstream generation                                                    | 43 |

| 4.2  | 01                                                                                        |    |

| 4.3  | Reconfiguration time of Xilinx solution                                                   |    |

| 4.4  | Our software solution                                                                     | 46 |

| 4.5  | Our Hardware Solution                                                                     | 46 |

| 4.6  | Comparison between proposed solution and Xilinx solution $\ldots \ldots \ldots \ldots$    | 47 |

| 4.7  | Critical connections and cores                                                            | 49 |

| 4.8  | Reconfiguration time with 2 Frames                                                        | 50 |

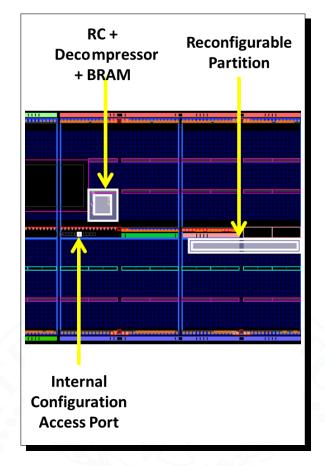

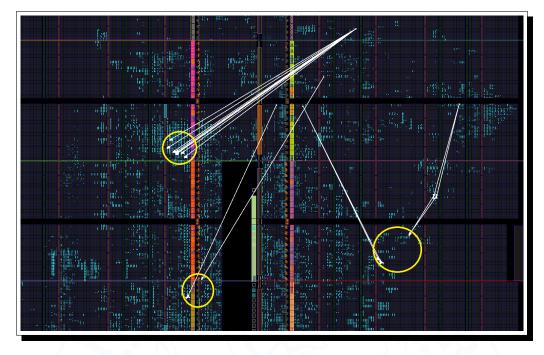

| 4.9  | PlanAhead Device View                                                                     | 51 |

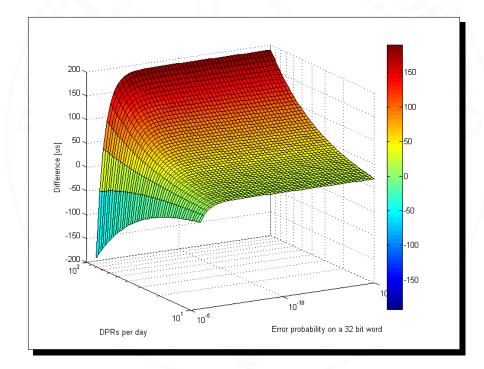

| 4.10 | Difference of DPRs time in 1 day - 2 Frames                                               | 53 |

| 4.11 | Difference of DPRs time in 1 day - 4 Frames                                               | 54 |

| 4.12 | Difference of DPRs time in 1 day - 8 Frames                                               | 54 |

| 4.13 | Decompressor architecture                                                                 | 59 |

| 4.14 | Example of protecting the critical blocks                                                 | 61 |

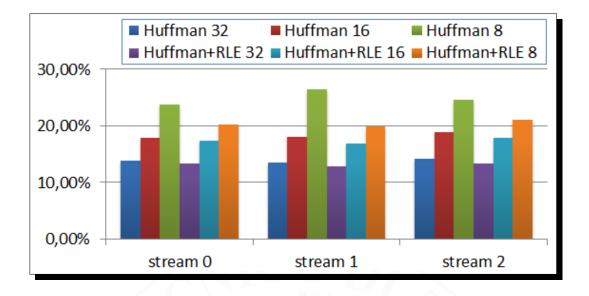

| 4.15 | Compression rates for streams 0, 1 and 2                                                  | 62 |

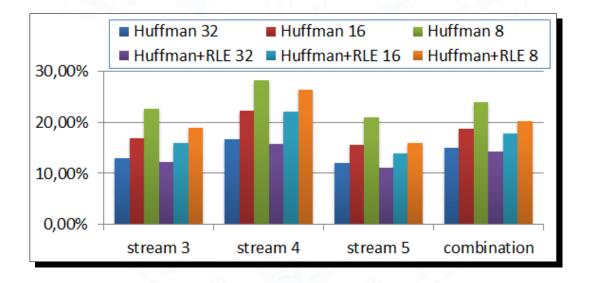

| 4.16 | Compression rates for streams 3, 4, 5 and average                                         | 62 |

| 4.17 | Possible connection schemes                                                               | 66 |

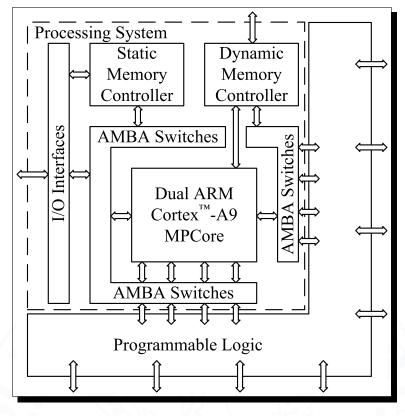

| 4.18 | $Zynq^{TM}$ Architecture                                                                  | 67 |

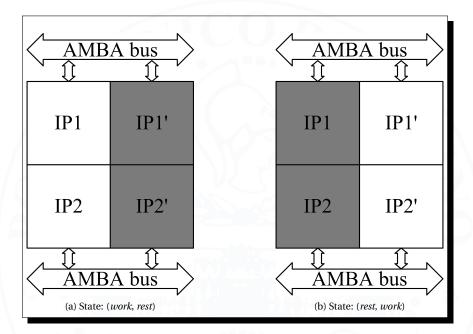

| 4.19 | Graphic representation of IP-core states within the FPGA                                  | 68 |

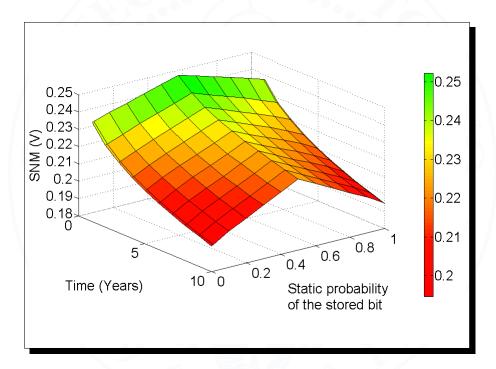

| 4.20 | Signal Noise Margin degradation in function of time (measured in years) and static        |    |

|      | probability (probability to have '1' in a SRAM cell)                                      | 69 |

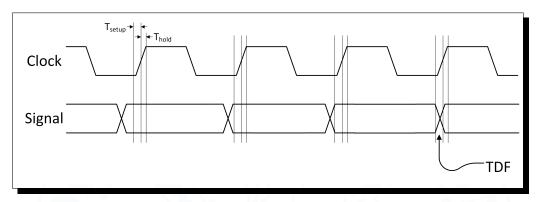

| 4.21 | Example of Transition Delay Fault. A signal connected to the input of a register or flip- |    |

|      | flop violates the set-up time changing its value in correspondence to the clock rising    |    |

|      | edge and thus increasing the probability of sampling a wrong value. $\ldots$              | 71 |

| 4.22 | SATTA overall architecture. TDF detection and mitigation is implemented inserting         |    |

|      | in the design: (i) a set of temperature sensors, (ii) a set of TDF sensors, (iii) a clock |    |

|      | generator, (iv) and a global manager.                                                     | 74 |

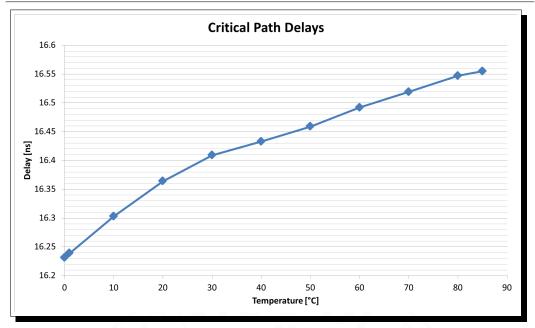

| 4.23 | Example of a critical path delay variation w.r.t. temperature in Virtex 4 Devices         | 75 |

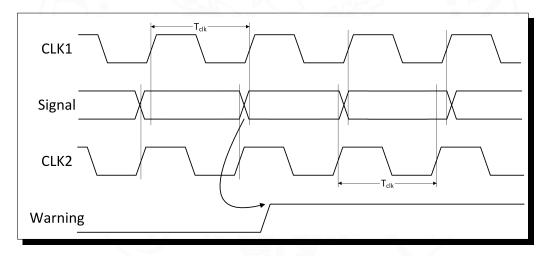

| 4.24 | Behavior of the TDF sensor                                                                | 76 |

| 4.25 | Clock Generator internal architecture                                                     | 78 |

| 4.26 | ASM describing the behavior of the Manager                                                | 80 |

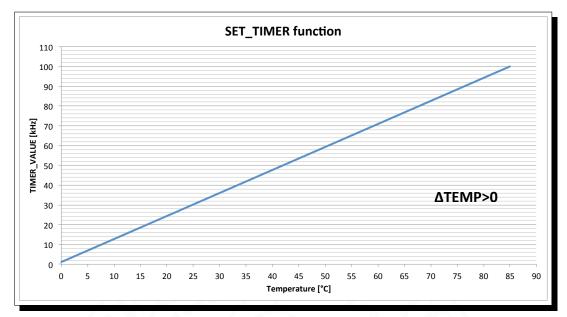

| 4.27 | Sampling periods with respect to temperature                                              | 82 |

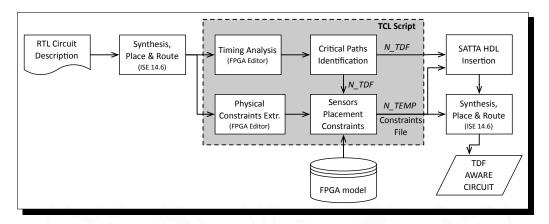

| 4.28 | SATTA integration flow. It enables to automate the insertion of all sensors and struc-    |    |

|      | tures required to implement the TDF detection and compensation                            | 83 |

|      |                                                                                           |    |

| 4.29 | Example of a timing analysis report generated using the Xilinx Timing Analyzer tool.                                                                 | 84 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.30 | Example of User Constraints File (.ucf) extracted running Xilinx FPGA Editor tool after design implementation.                                       | 85 |

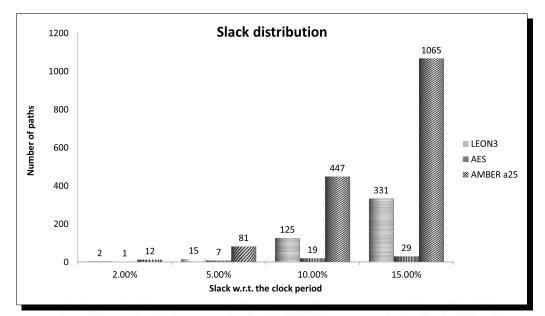

| 4.31 | Paths slack distribution. The y axis represents how may paths have a delay included in a range of the nominal clock period identified on the x axis. | 87 |

| 4.32 | Leon3-based SoC critical paths and temperature sensors floorplan                                                                                     | 88 |

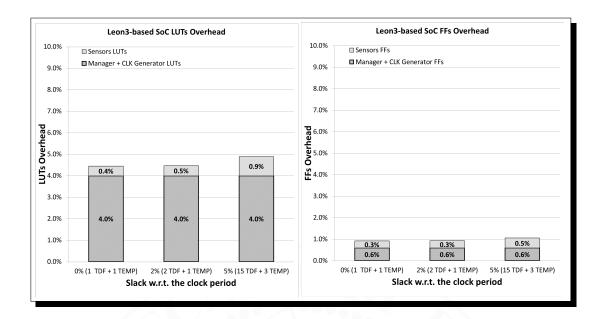

| 4.33 | SATTA LUTs and FFs overhead when applied to the Leon3-based SoC case study                                                                           | 89 |

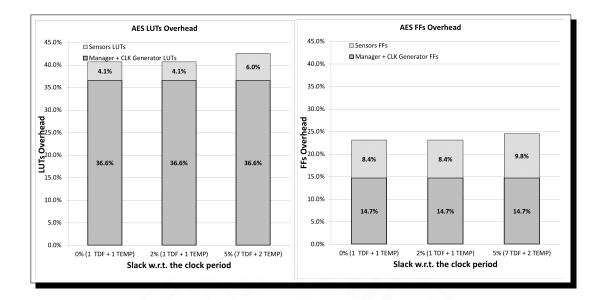

| 4.34 | SATTA LUTs and FFs overhead when applied to the AES case study                                                                                       | 90 |

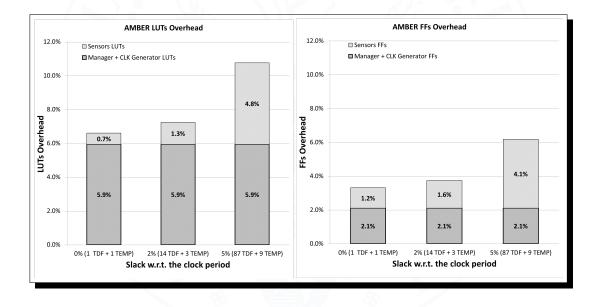

| 4.35 | SATTA LUTs and FFs overhead when applied to the AMBER case study                                                                                     | 90 |

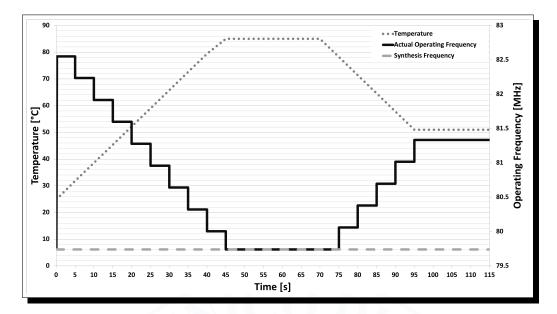

| 4.36 | Simulated operating frequency trend with temperature variations                                                                                      | 92 |

## LIST OF TABLES

| 3.1 | Comparison among FPGA families                                        | 27 |

|-----|-----------------------------------------------------------------------|----|

| 3.2 | Partial Reconfiguration command sequence                              | 39 |

| 4.1 | Area occupation and reconfiguration time of different implementations | 52 |

| 4.2 | Synthesis Results                                                     | 86 |

| 4.3 | SATTA synthesis results                                               | 88 |

Confidence is what you have before you understand the problem

Woody Allen

### **INTRODUCTION**

ustomer needs and market requirements have acted as a constant push to technology during the past 40 years, somehow following Moore's prediction. This driving force had, on the one hand, led to great benefits in terms of computational power and lower cost, while, on the other hand, caused several headaches to dependability engineers. The

Figure 1.1: Moore's Law applied at Intel's processors

so-called die shrinking for digital logic, as summarized by the ITRS, can be defined as "scaling of the MOSFETs for leading-edge logic technology in order to maintain historical trends of improved device performance" [34].

Such a continuous scaling has been characterized of several phases, depending on the methodology adopted to achieve the scaling. As shown in Figure 1.2, three main Technology Enablers have been identified:

- Lithography: optical lithography scaling has been the exploited by the semiconductor industry for several generations, and enabled classical geometrical CMOS scaling by economically decreasing the resolution, feature size and die area of devices at every subsequent technology node. Due the challenges associated with scaling the wavelength of the light source used for modern optical lithography systems and theoretical optical limits [36], industry had to make a step forward to the basic geometrical scaling;

- 2. **Materials**: in order to follow Moore's law beyond the limits of wavelength scaling, new materials have been employed in technology nodes after 65 nanometers. Among them, the most important innovations, as reported by Intel in [45], have been the introduction of: High-k dielectric replacing silicon dioxide to guarantee higher impedance; metal gates for planar CMOS technologies replacing poly-silicon to decrease electrical resistance; strained silicon, in order to increase channel mobility by mean of compressive (for PMOS) or tensile (for NMOS) strain;

Figure 1.2: 3 different technology enablers in recent nodes (by Global Foundries)

3. **3D**: the traditional flat two-dimensional planar gate has been replaced with a thin threedimensional silicon fin that rises up vertically from the silicon substrate, allowing the insertion of multiple gate accesses. Further then to create the so-called FinFET transistor, 3D technology has been exploited also to build IC composed of multiple layers of active components. The scaling is then emulated, since the actual transistor dimension is not-scaled or scaled very little, but the components per area is anyway increasing.

In the past, the technological reliability margins that were available to achieve the required failure rate levels were always sufficiently high. Also reliability could be guaranteed at the 130nm technology level, based on accelerated stress experiments [25]. When the device geometries are scaled into the range of 65nm CMOS technologies and below, however, the available reliability margins are strongly reduced, implying new paradigms in reliability approaches 1.3.

At every technology node, as it may be expected, the gain in terms of performances, speed and

Figure 1.3: Required failure rates over years [25]

possibly cost of ICs does not come for free. In the sub-micron era, miniaturization affects several aspects of the produced device: MOS leakage current has been proved to increase due to direct tunnelling [60], thus raising static power consumption.

As a secondary effect, the increase of die temperature in modern silicon-based devices act as a major hard failure cause. Experimental results shows that scaling has a significant and increasing impact on processor hard failure rates, due to the increase in processor temperature. The maximum temperature reached by a 65nm processor is 15 degrees Kelvin higher than that reached by a 180nm processor. The failure rate for a 65nm processor is 316% higher than the failure rate at 180nm, with similar reliability qualification [35].

Another major issue due to technology scaling and dramatically enhanced at high temperature has been identified as process variation. Advanced CMOS technology includes two major types of process variability: local (intradie) and global (interdie). Local variability is the parametric changes of identical MOSFETs across a short distance. Global variability refers to such changes for identical MOSFETs separated by a longer distance or fabricated at a different time [52]. The

#### 1. INTRODUCTION

effects at system level of both intradie and interdie variation feature another criticality: non predictiveness. Thus, no countermeasures further then worst case design has been ever taken into account for safety critical applications.

The works presented in this thesis tries to face new dependability issues in modern reconfigurable systems, exploiting their special features to take proper counteractions with low impact on performances. The thesis is organized following the reasoning that have been made during the research phases. First of all, the most critical dependability issues of recent technology nodes are evaluated in Chapter 2, highlighting the two main effects that the research tackled.

Following, Chapter 3 will give the reader the chance of understanding the reconfigurable architecture, namely FPGA, that has been adopted in the research experiments, focusing on the Dynamic Partial Reconfiguration feature.

The methodologies adopted to increase the overall dependability of dynamically and partially reconfigurable systems will be explained in Chapter 4, while the conclusions of the research carried out will be eventually drawn in Chapter 5.

Simplicity is prerequisite for reliability

Edsger W. Dijkstra

### DEPENDABILITY ISSUES IN DIGITAL SYSTEMS: AN OVERVIEW

ependability has been defined as the quality (previously referred as trustworthiness and continuity) of the delivered service such that reliance can justifiably be placed on this service [42].

More recently, the term dependability has described as the composition of four main properties, namely:

- **R**eliability: the probability that a piece of equipment or component will perform its intended function satisfactorily for a prescribed time and under stipulated environmental conditions;

- Availability: the probability that the system will be functioning correctly at any given time;

- Maintenability: the ease with which a product can be maintained in order to cope with a changed environment;

- **S**afety: the freedom from undesired and unplanned event that results in a specific level or loss (i.e. accidents).

that are usually referred as RAMS.

The achievement of high level of dependability in digital systems is critical whenever the life of a human being is in charge of the digital system itself. Ad-hoc devices must be adopted in those situations, guaranteeing a low level of risk.

Accordingly, safety critical systems often rely on the adoption of old technology nodes, even if they introduce longer design time w.r.t. consumer electronics. In fact, functional safety requirements, due to international directives like IEC-61508 [32] for industrial applications and ISO-26262 [33] for automotive, are increasingly pushing industry in developing innovative methodologies to design high-dependable systems with the required diagnostic coverage.

More recently, commercial off-the-shelf (COTS) devices adoption began to be considered for safety-related systems. Real-time requirements, the need for the implementation of computationally hungry algorithms and lower design costs are pushing industries in this direction. These design choices have a significant impact on the dependability capabilities and diagnostic coverage measurements. FPGAs are more and more adopted in safety-critical applications thanks to their flexibility, high parallelism and increased performances. These features have been achieved because FPGAs have been aggressively moving to lower gate length technologies. The scaling of technology has an adverse impact on the reliability of the underlying circuits in such architectures. Various different physical phenomena have been recently explored and demonstrated to impact the reliability of circuits in the form of both transient error susceptibility and permanent failures.

On November 5, 2001, a processor reset occurred on board the Microwave Anisotropy Probe (MAP), a NASA mission to measure the anisotropy of the microwave radiation left over from the Big Bang. The reset caused the spacecraft to enter a safe mode from which it took several days to recover. NASA assembled a team of engineers, including experts in radiation effects to tackle the problem. They observe that the processor reset occurred during a solar event characterized by large increases in the proton and heavy ion fluxes emitted by the sun [11]. As dimensions shrink to below 90 nm, SEEs in all devices (ASICs and FPGAs) and in all safety critical applications must be considered [65]. Section 2.1 will give an overview, from the causes to the effects, of Single Event Effects (SEE).

Apart from the increased vulnerability of the circuits to transient errors, there is an increase in the impact of different aging phenomena that result in permanent failures of the devices and interconnect. Therefore, the aggravation of such aging phenomena like Hot-Carrier Effect (HCE), Time Dependent Dielectric Breakdown (TDDB), Electromigration (EM), Thermal Cycling, Stress Migration, and Negative Bias Thermal Instability (NBTI) need to be analysed carefully in such FP-GAs designed using newer technologies. Among them, NBTI has been forecast to be main aging phenomenon in future technologies and has been addressed during my research. Section 2.2 will underline NBTI root causes and device-level effects to better understand how to tackle them.

### 2.1 Single Event Effects

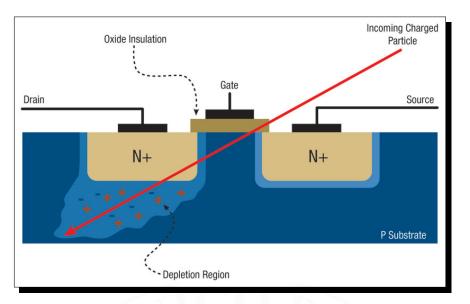

Single Event Effects (SEE) in microelectronics are caused when highly energetic particles present in the natural space environment (e.g., protons, neutrons, alpha particles, or other heavy ions) strike sensitive regions of a microelectronic circuit (see Figure 2.2). Depending on several factors, the particle strike may cause no observable effect, a transient disruption of circuit operation, a change of logic state (i.e., nondestructive SEE or soft errors), or even permanent damage to the device or integrated circuit (IC), the so called destructive SEE or hard errors [20].

Soft errors are upsets to the device operation and are self-correcting in time or are correctable

Figure 2.1: Types of Single Event Effects [65]

by rewriting a memory element, and they can be classified as:

- Single-event transients (SETs) result when a high-energy particle impacts a combinatorial path of a device and can induce a voltage/current spike. If the pulse-width of this spike is sufficient and at the right time, it can propagate through the logic;

- Single-event upsets (SEUs) are the result of high-energy particles causing a change in the state of a memory element (SRAM, flash, flop, or latch). SEUs can be categorized as single-bit or multi-bit upsets (SBUs or MBUs);

- Single-event function interrupts (SEFIs) are disruptions to normal device operation (beyond a simple corruption of user data). These types of effects alter the functionality of the circuit and typically require reconfiguration/reset or power cycling for recovery.

Errors that cause lasting damage to the device are classified as hard errors. The three subclasses of hard errors are:

- Single-event latch-up (SEL) is a circuit latch-up induced by radiation. This latch-up can be either permanent or disappear with power cycling;

- Single-event burnout (SEB) is a short-circuiting caused when a high-energy ion impacts a transistor source, causing forward biasing. SEBs are typically a threat to power MOSFETs, high-voltage diodes, and similar circuits;

- Single-event gate rupture (SEGR) is a plasma spiked caused by a high-energy ion impact, resulting in rupture of the gate oxide insulation [65].

#### 2. DEPENDABILITY ISSUES IN DIGITAL SYSTEMS: AN OVERVIEW

Figure 2.2: Impact of a high-energy particle in a CMOS structure [54]

Natural radiation that causes SEE in digital circuits may come from various sources. At ground level, one can distinguish two major sources of radiation:

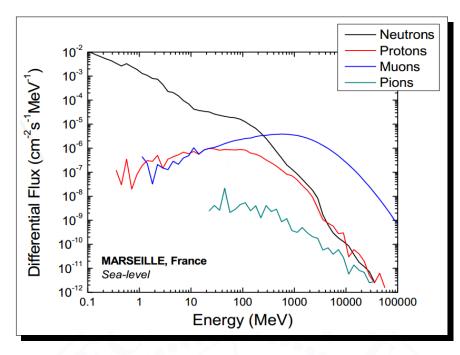

- 1. *atmospheric radiation environment*: elementary particles and electromagnetic radiation are produced in the Earth's atmosphere when a primary cosmic ray (of extraterrestrial origin) enters the atmosphere. The term cascade means that the incident particle (generally a proton, a nucleus, an electron or a photon) strikes a molecule in the air so as to produce many high energy secondary particles (photons, electrons, hadrons, nuclei) which in turn create more particles, and so on (see Figure 2.3).

- 2. *telluric radiation sources*: Natural radioisotopes contained in the Earth's crust are the principal natural sources of  $\alpha$ ,  $\beta$  and  $\gamma$  radioactivity but only the alpha-particle emitters present a reliability concern in microelectronics. Beta and gamma processes are indeed not able to deposit a high enough amount of energy susceptible to significantly impact the microelectronic circuit operation. The presence of alpha-particle emitters in electronic devices can be classified as materials that are naturally radioactive (they contain a fraction of radioactive nuclei) or materials that contain residual trace of radioactive impurities. Currently, several types of alpha particle emitters have been identified at wafer, packaging and interconnection levels, including lead in solder bumps, uranium and thorium in silicon wafers and in molding compounds, more recently hafnium in new high-lž gate and platinum in silicide materials [7].

Figure 2.3: Differential flux for atmospheric neutrons, protons, muons and pions at ground level in Marseille, France [7]

Nondestructive SEE can lead to different system malfunction. From what concerns FPGA devices, particular emphasis has been established in Single (Multiple) Event Upset (SEU and MEU) in static random access memories (SRAM) and single-event transients (SET) in logic.

### 2.1.1 Physical causes

There are two primary methods by which ionizing radiation releases charge in a semiconductor device: direct ionization by the incident particle itself and ionization by secondary particles created by nuclear reactions between the incident particle and the device:

• *Direct Ionization*: it appears when an energetic charged particle passes through a semiconductor material it frees electron-hole pairs along its path as it loses energy. When all of its energy is lost, the particle comes to rest in the semiconductor, having travelled a total path length referred to as the particle's range. The term *linear energy transfer* (LET) is used to describe the energy loss per unit path length of a particle as it passes through a material. Direct ionization is the primary charge deposition mechanism for upsets caused by heavy ions, where we define a heavy ion as any ion with atomic number greater than or equal to two (i.e., particles other than protons, electrons, neutrons, or pions). Lighter particles such as protons do not usually produce enough charge by direct ionization to cause upsets in memory circuits, but recent research has suggested that as devices become ever more susceptible, upsets in digital ICs due to direct ionization by protons may occur [20];

• *Indirect Ionization*: even if direct ionization by light particles does not usually produce enough charge to cause upsets, protons and neutrons can both produce significant upset rates due to indirect mechanisms. As a high-energy proton or neutron enters the semiconductor lattice it may undergo an inelastic collision with a target nucleus. These reaction products can now deposit energy along their paths by direct ionization. Because these particles are much heavier than the original proton or neutron, they deposit higher charge densities as they travel and therefore may be capable of causing an SEU. Inelastic collision products typically have fairly low energies and do not travel far from the particle impact site. They also tend to be forward-scattered in the direction of the original particle.

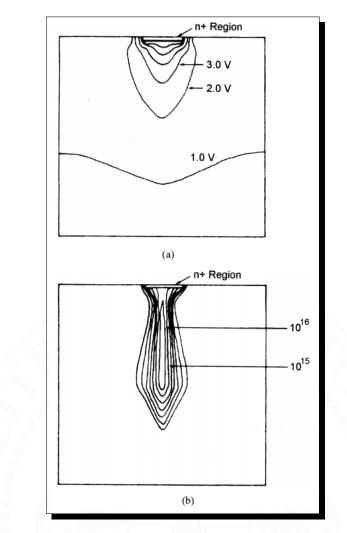

After a particle hits the device, the charge is then released and collected in the device structure. When a particle strikes a microelectronic device, the most sensitive regions are usually reversebiased p/n junctions, as shown in Figure 2.4. The high field present in a reverse-biased junction depletion region can very efficiently collect the particle-induced charge through drift processes, leading to a transient current at the junction contact. Strikes near a depletion region can also result in significant transient currents as carriers diffuse into the vicinity of the depletion region field where they can be efficiently collected. Charge generated along the particle track can locally collapse the junction electric field due to the highly conductive nature of the charge track and separation of charge by the depletion region field. as shown in Figure 2.5 This funnelling effect can increase charge collection at the struck node by extending the junction electric field away from the junction and deep into the substrate, such that charge deposited some distance from the junction can be collected through the efficient drift process.

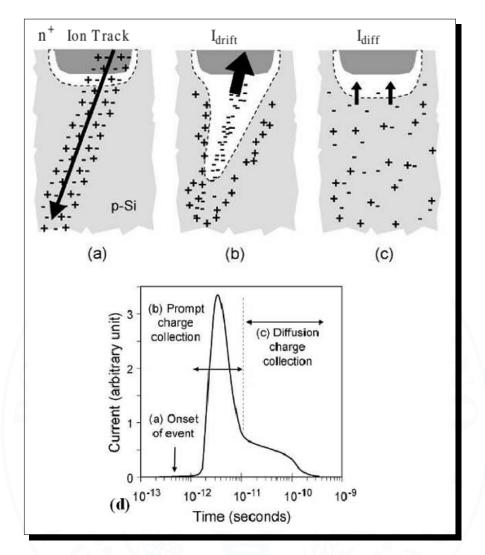

#### 2.1.2 Single Event Transient in digital logic

A Single Event Transient (SET) is any temporary voltage disturbance that occurs in an integrated circuit following the passage of an ionizing particle through the IC. SETs occur in both digital and analog ICs (SETs in digital circuits are referred to as DSETs and those in analog circuits as ASETs). SETs occur in devices manufactured with silicon CMOS, bipolar, or BiCMOS, or III-V technology. SETs are generated at internal circuit nodes, but whether they are detected depends on a number of factors. [11] DSETs are momentary voltage or current disturbances that, although they don't cause an upset in the circuit actually struck by an energetic particle, may propagate through subsequent circuitry and eventually cause an SEU when they reach a latch or other memory element. At least four criteria must be met for a DSET to result in a circuit error:

1. The particle strike must generate a transient capable of propagating through the circuit

Figure 2.4: Representation of charge collection in a silicon junction immediately after (a) an ion strike, (b) prompt (drift) collection, (c) diffusion collection, (d) the junction current induced as a function of time [9]

2. DEPENDABILITY ISSUES IN DIGITAL SYSTEMS: AN OVERVIEW

Figure 2.5: Funneling in an n+/p silicon junction following an ion strike: (a) electrostatic potential and (b) electron concentration [30]

- 2. There must be an open logic path through which the DSET can propagate to arrive at a latch or other memory element

- 3. The DSET must be of sufficient amplitude and duration to change the state of the latch or memory element

- 4. In synchronous logic, the DSET must arrive at the latch during a clock pulse enabling the latch

The probability that momentary glitches will be captured as valid data in combinational logic increases linearly with frequency because the frequency of clock edges increases [21]. With the

increase of circuit speeds, also the ability of a given transient to propagate increases. Nonetheless, also the duration of transients decreases. Due to both their greater ability to propagate in high-speed circuits and their higher probability of capture by subsequent storage elements such as latches, DSETs have been predicted to become endemic in deep sub-micron digital ICs. In

Figure 2.6: Single-event transient width in bulk and SOI devices as a function of LET and technology scaling [21]

bulk CMOS devices, a clear scaling trend emerges, namely that peak current significantly decreases with technology scaling. This decrease to be primarily due to the smaller cross-sectional area presented by the struck drain junction for diffusive charge collection (more than 6 times smaller at 0.1 m compared to 0.25 m), in combination with the higher well doping levels of the scaled technologies (which further decrease charge collection efficiency).

The situation is different for Silicon over Insulator (SOI) technologies, where the buried oxide prevents charge collection from the substrate and therefore the size of the drain is unimportant. Figure 2.6 indicates that DSETs in SOI technologies are generally less than 250ps in duration, much faster than in the bulk devices. In addition, the SOI DSET durations decrease with technology scaling, consistent with the fact that SOI collection is dominated by fast collection within the body volume, which shrinks with gate length. These differences in transient pulse widths have significant implications for DSET propagation in bulk and SOI technologies. Once a DSET has been produced in the struck device, its evolution through the digital logic can be predicted. Research usually exploit inverter chains to understand the behaviour and the propagation of DSETs. Transients that can propagate without attenuation are obviously a concern, although it must be remembered that propagation of the DSET is only the first of four conditions that must be met for a DSET to become an SEU. The DSET must still have an open logic path to a latch, meet the timing parameters of the latch, and arrive during a sensitive timing window to become an error.

### 2.1.3 Single Event Upset in SRAM

Single event upsets in memory circuits are a key issue for advanced CMOS technologies. A single particle hitting a very dense device, like SRAM, can produce severe consequences.

Single-bit upsets (SBU) and multiple-bit upsets (MBU) are important in both terrestrial and space applications. With technology scaling, the number of upsets per chip will typically increase due to higher circuit density and may also increase due to higher circuit sensitivity. For SRAM circuits, MBUs are particularly important since the MBU sensitivity can limit the effectiveness of error correcting codes (ECC) [29]. Early SRAM was more robust against single event because of high operating voltages and the fact that data was stored as the state of a bi-stable circuit made up of two large cross-coupled inverters, each strongly driving the other to keep the bit in its programmed state. However, with each successive SRAM generation, reductions in cell collection efficiency due to the shrinking cell depletion volume have been swamped out by big reductions in operating voltage and reductions in node capacitance. Thus SRAM single bit Single Error Rate (SER) increased with each successive generation [8]. Figure 2.7 shows the SEU and MBU cross sections for a chosen energy of 400 MeV. As expected from nuclear physics, the behaviour of neutrons and protons above 100 MeV (i.e., protons, easier to produce and control, replace neutrons).

It is seen that the increase of the MBU cross section when the critical energy is decreasing is faster than the SEU one, and that the ratio of these two cross sections exhibits large variation. Starting from three orders of magnitude, it tends to only one order of magnitude. The fast increase of the two cross sections at very low critical energy is due to the increasing participation of the light

Figure 2.7: SEU and MBU cross sections versus critical energy [61]

particles. At very low critical energies, the SEU and MBU cross sections are almost governed by geometrical probabilities. The number of SEUs depends on the size of the sensitive volume and the deposited energy in this volume. As far as the MBUs are concerned, the distance between the bits is a third important characteristic. Device downscaling thus clearly induces soft error rate concerns. MBUs are particularly worrying because they are the most difficult to correct since they effects multiple bits in the same word [61].

Recent Soft Error Rate (SER) testing result of SRAM-based FPGAs from Actel [1] shows a significant and growing risk of functional failures due to the corruption of configuration data, especially when the system has higher densities. The number of upsets per 1 million gates per day increases because of the altitude dependent increase in neutron flux density. It is expected that neutroninduced soft errors get worse by a factor of two as we move from  $0.13\mu$  to  $0.09\mu$  technology.

The radiation induced soft errors have become one of the most important and challenging failure mechanisms in modern electronic devices. SER of commercial chips is controlled to within 100-1000 FITs. Compared to most hard failure mechanisms that produce failure rates on the order of 1-100 FIT, the SER of a low-voltage embedded SRAM can easily be 1000 FIT/Mbit. Therefore, a four-phase approach to deal with them is in progress [58]

- 1. Methods to protect chips from soft errors (prevention).

- 2. Methods to detect soft errors (testing).

- 3. Methods estimate the impact of soft errors (assessment).

- 4. Methods to recover from soft errors (recovery)

### 2.2 NBTI: Causes and Effects

Bias temperature instability (BTI) is a degradation phenomenon occurring mainly in MOS Field Effect Transistors (MOSFETs).

Even though the exact root causes of the degradation are not yet well understood, it is now commonly admitted that under a constant gate voltage and an elevated temperature a build up of positive charges occurs either at the interface Si/SiO2 or in the oxide layer leading to the reduction of MOSFET performances. Nevertheless, this degradation remained marginal for many years, but with aggressive scaling of MOS transistors this phenomenon became important.

In order to improve the transistors performances, nitrogen atoms were introduced into the oxide layer by different nitridation processes, but mostly by thermal annealing. This nitridation step is intended both to give a better control on the gate leakage current and to avoid the boron atoms, used to dope the poly-silicon gate, to flow through the oxide into the substrate.

Besides, the general trend was that most of the devices turned out to be surface-channel devices instead of buried-channel ones in recent technologies to counter the short-channel effects inherent of the downscaling process and to improve the performances.

As a consequence of both the introduction of the nitridation process step and the use of surfacechannel devices, researchers ascribed an enhanced BTI-like degradation of p-MOSFETs under negative bias and elevated temperatures, the so-called **NBTI effect**.

By definition, bias temperature instabilities are observed when either a capacitor or a transistor is stressed at relatively high temperatures (typically ranging from  $80^{\circ}C$  to  $150^{\circ}C$ ) under a low and constant gate voltage while the source/drain and well electrodes are grounded.

The symmetry of stress conditions along the channel proves that this degradation is not related to channel carrier transport. Generally, it is observed that after an NBTI stress, the saturated drain current value ( $I_{dsat}$ ) is reduced. The forward and reverse values of the saturated drain current both degrade identically, demonstrating the symmetry of the stress. By the same time, the threshold voltage ( $V_{th}$ ) is increased as well as the S/D series resistance.

Altogether, the degradation of these parameters demonstrates the build-up of positive charges close or at the interface of  $Si - SiO_2$  and yields to a lower level of performance for the transistor. For short stress times, the off-leakage current is decreasing due to the shift of the  $I_d/V_g$  curves linked to the threshold voltage shift. Nevertheless, in some cases, an increase of the GIDL observed at low fields may overcome this decrease and limit the performances of the circuit by an increased consumption.

The instabilities exist in most of the configurations, for either p-MOSFETs or n-MOSFETs, and whatever a negative bias and/or a positive bias is applied, except for the n-MOSFET under positive bias, which does exhibit almost no degradation. Nevertheless, as shown in Figure 2.8, applying NBTI stress conditions (i.e. negative gate voltage) on p-MOSFETs represents the most degrading case.

Figure 2.8: Vth shift as a function of stress time [31]

So far, the microscopic details of the NBTI degradation are not clearly understood but there is a general agreement to say that there is generation of traps at the  $Si - SiO_2$  interface during negative BTI aging.

But, to understand the impact of the NBTI degradation up to circuit level, it is important to make the link with device parameters such as threshold voltage. As NBTI degradation is mainly a buildup of charges at the interface in a symmetrical configuration along the channel, the threshold voltage parameter is more relevant to describe the degradation than other parameters such as the saturated drain current.

As already discussed above, the NBTI degradation is known to be activated with temperature. For many researchers, the degradation of electrical parameters is mostly linked to the creation of interface traps, especially in ultra thin oxides.

Figure 2.9 shows the temperature dependence of the interface traps creation and the threshold voltage shift for a given set of stress conditions and varying temperatures. If the threshold voltage is only influenced by the creation of interface traps at the interface, these two parameters should have similar apparent temperature activations.

If the threshold voltage shift would have been explained solely by the interface traps creation,

Figure 2.9: Vth shift and interface traps creation as a function of stress time for three different temperatures[31]

similar activation energies would have been found for both phenomena. Different activation energies imply that another process has to be taken into account in order to explain the threshold voltage shift. It is reasonable to think that this second component is related to charges into the oxide.

Effectively, under a constant voltage stress such as under NBTI stress conditions, an increase of the number of oxide defects is known to occur, which leads the oxide to break once a critical limit is reached. But defects can also be present in the oxide previously to the stress, induced either by impurities or strain relaxation during the latter process phases.

In this case, applying an oxide field would increase the trapping efficiency of charges in those defects. Thus, the second component of the NBTI degradation could then be either holes trapped onto oxide defects, pre-existent to the stress or created during the stress, or slow states present close to the interface.

Applying a positive gate bias consecutively to a negative bias stress is known to neutralize both trapped holes and/or positively charged slow states.

In order to determine the relative importance of the interface traps and the positive charges into the oxide on the threshold voltage, an electrical neutralization phase, where the device is positively gate biased, is introduced after a normal, continuous negative gate bias stress.

The relative shifts for the interface trap density (open symbols) and for the threshold voltage (filled symbols) versus the stress time are presented in Figure 2.10.

The main feature is a strong reduction (more than 50%) of the threshold voltage under the posi-

Figure 2.10: Relative shifts for traps and Vth versus stress time [31]

tive bias, when the interface trap density remains almost unchanged. First, the absence of a large variation of the trap density under the positive bias is worth noticing. The possible repassivation of the *Si* dangling bonds, as the hydrogen species might move back to the  $SiO_2/Si$  interface when the bias polarity is changed, appears to be negligible. This result, in agreement with the results obtained by adding additional delay between stress and measurement as described above, is another clue that the threshold voltage does not depend only on the interface trap density and the recovery effect should not be addressed with a diffusion controlled annealing model.

Consequently, the threshold voltage shift that consists of the difference of the threshold voltage shifts before and after the electron injection represents the contribution of positive charges induced during the stress by hole trapping into the oxide.

This shift presents almost no temperature dependence, which is expected for defect generation by hole trapping as the tunnelling effect involved in the charging is hardly temperature dependent. The small temperature dependence observed experimentally is only to be explained by a variation of the effective hole capture cross-section with temperature.

The positive charges build-up within the oxide observed experimentally can still be explained either by holes trapped in oxide defects or by the charging of slow states. Both trapped holes and positively charged slow states can be neutralized by a further electron injection under positive bias for few minutes as in Figure 2.10. Though, they should present a different recharging behavior when the slow states can be recharged under a small negative bias whereas holes trapped into the oxide cannot, as they need larger energies to get back into the oxide and to restore the positive charge.

### 2.2.1 Effects on digital logic

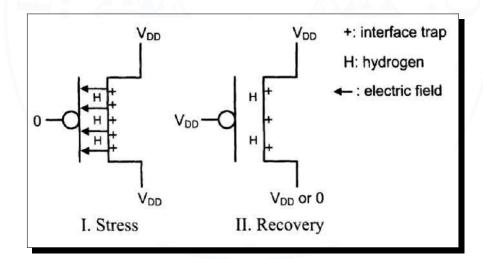

NBTI occurs under negative gate voltage (e.g.,  $V_{gs} = -V_{DD}$ ) and is measured as an increase in the magnitude of threshold voltage. It mostly affects the PMOS transistor and degrades the device drive current, circuit speed, noise margin, and the matching property. Indeed, as gate oxide gets thinner than 4nm, the threshold voltage change caused by NBTI for the PMOS transistor has become the dominant factor to limit the life time, which is much shorter than that defined by hot-carrier induced degradation (HCI) of the NMOS transistor.

For a PMOS transistor, there are two phases of NBTI, depending on its bias condition. These two phases are illustrated in Figure 2.11, assuming the substrate is biased at VDD. In Phase I, when  $V_g = O(V_{gs} = -V_{DD})$ , positive interface traps are accumulating.

Figure 2.11: Stress and recovery phases on transistor [57]

This phase is usually referred as "stress" or "static NBTI".

In Phase II, when  $V_g = V_{DD}$  ( $V_{gs} = O$ ), holes are not present in the channel and no new interface traps are generated, instead, H diffuses back and anneals the broken Si-H. As a result, the number of interface traps is reduced during this stage and the NBTI degradation is recovered. Phase II is usually referred as "recovery" and has a significant impact on the estimation of NBTI during the dynamic switching.

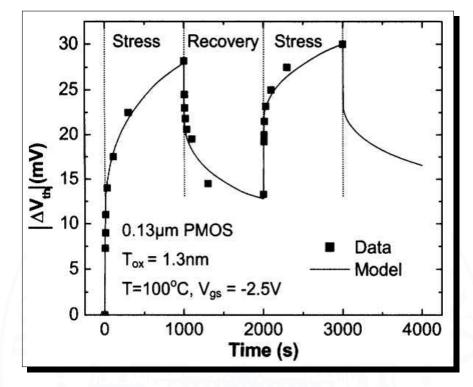

Figure 2.12: Threshold voltage degradation during stress and recovery phases [57]

In a realistic circuit, the gate switches between 0 and  $V_{DD}$ . For a PMOS transistor, the condition of  $V_g = V_{DD}$  removes NBTI stress and anneals interface traps. The degradation of  $V_{th}$  on the PMOSFET devices causes changing on the behavior of the gates. First of all, NBTI degrades the drain current of the transistor, and this causes a decrease of rising time of the gates.

The degradation in delay shows a power dependency to time with a fixed exponent of 1/6. Several method are studied at gate-level to decrease the delay degradation, in example transistor resizing of only the pull-up side of the gate, sleep mode with lower  $V_{DD}$ , power-gating like  $V_{DD}$  clamping with virtual supply voltage etc.

The drain or on current is important in analog and digital circuits. In digital circuits, with MOS-FETs being switches, charging and discharging capacitors, higher drain current leads to faster capacitor charging and higher frequency operation.

The delay time is

$$t_d = \frac{C|V_{DD}|}{I_D} = \frac{2LC}{W\mu_{eff}C_{OX}(V_{DD} - V_{th})^2}$$

(2.1)

where *C* is the capacitance and  $V_{DD}$  the supply voltage [59].

NBTI stress leads to  $l_{eff}$  reduction and  $V_{th}$  increase, both giving delay time increases. As we can see in the equation, the circuit impact will be greater for lower operating voltage, because of the reduced  $V_g - V th$ , so the impact is predicted to increase in new technology nodes.

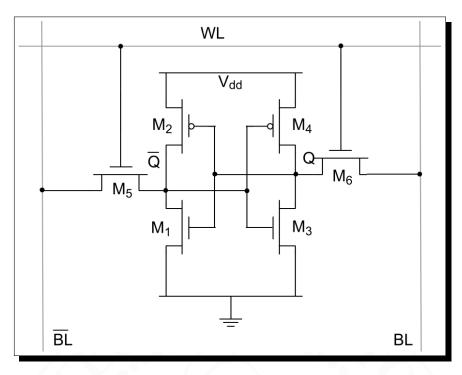

### 2.2.2 Effects on SRAM memories

Considering SRAM memories, the NBTI induces a degradation of the robustness of the cells (i.e., their capability to safety store a bit). A good metric to qualify the effect of NBTI in a memory cell is the *Static Noise Margin* (SNM), i.e., the minimum *DC* noise voltage necessary to change the stored value [12].

Figure 2.13 above shows a 6T cell with the wordline, bitlines , and internal nodes. During a read operation, the bitline  $\overline{BL}$  is discharged through the access transistor and the pull down transistor which causes the voltage at node Q to rise. In order for the cell to maintain its state, it is necessary that the voltage at Q not rise above the trip point of the inverter formed by M3 and M4. The voltage difference between this inverter trip point and the voltage at node Q is the read SNM of the cell.

SNM can be computed as the length of the side of a maximum square nested between the two voltage transfer characteristic (VTC) curves (i.e., for each back-to-back inverters) of SRAM cell. Simple simulation has shown that SNM of an SRAM cell can degrade with time under NBTI [37]. SNM of SRAM is particularly important during two operations, that is, the HOLD (i.e., stand-by mode) and READ phases. When the word line is turned off and cell is holding the data, HOLD SNM can be computed. During the HOLD phase the cell state is relatively insensitive to the variation in the threshold of PMOS transistors due to NBTI.

The smaller the SNM is, the lower the reliability of the cell becomes. Unfortunately, the  $V_{th}$  shift

Figure 2.13: 6 Transistor SRAM cell

induced by NBTI causes an SNM degradation, which in turn reflects itself on the stability of the cell. Because of the symmetric layout of the cell, the  $V_{th}$  shift is maximum if the stored value's zero-probability is near to 0 or 1. Clearly, the best case happens when the stored value is '0' for the 50% of the time, which means that both pMOS transistors age in the same way. Figure 2.14 depicts the relationship between the read failure probability and the signal probability. As predicted, failure probability becomes higher when the signal probability is unbalanced.

Figure 2.14: Read failure probability with different static probablityes [37]

You do not really understand something unless you can explain it to your grandmother.

Albert Einstein

# FPGA ARCHITECTURE AND DYNAMIC PARTIAL RECONFIGURATION

ield Programmable Gate Arrays (FPGAs) are integrated circuits designed to be configured by the user (hence field-programmable) one or multiple times. Configuration is generally specified using a hardware description language that is an input to synthesis tool that creates a binary configuration file. This file can be loaded through a configuration port to the FPGA device. This semiconductor device is thus not restricted to a specific hardware function, but the user can freely implement any logical function that can be performed by an ASIC, by properly configuring the FPGA. Designers must then properly evaluate when to adopt an FPGA in their design or rather select an ASIC-based design flow.

FPGA based systems are usually characterized of:

- low non recurrent engineering, due to low development and tool costs;

- reconfigurability and rapid prototyping, allowing to verify and validate hardware implementation in a fast and accurate way;

- simpler and faster design cycle, since tools are managing placing, routing in a fast and accurate way allowing the faster TTM as well;

- · limited resources, fixed according to the chosen FPGA device;

- higher power consumption.

On the other hand, ASIC systems are usually characterized by:

- lower recurrent engineering, since for high volume designs, unit costs are very low;

- higher performances, in terms of speed and power efficiency;

- high design flexibility, without any limit in number and kind of resources;

- very difficult design and long design time, due to floor planning, routing that must be checked and validated.

At the highest abstraction level and at the earliest design phase, it basically comes down to a scalability versus a flexibility question. ASICs are advantageous when it comes to high port density applications. FPGAs are advantageous when it comes to feature velocity with a shortened time-to-market requirement.

Clearly, in the time-to-market driven era, FPGA market share is constantly increased, with 3 major players sharing the big pot: Xilinx, Altera and Actel, as shown in Figure 3.1.

In the following, Section 3.1 will highlight the different FPGA families currently available in the

Figure 3.1: FPGA market share in recent years

market, while Section 3.2 will focus on the most widely adopted FPGA type, the SRAM-based FP-GAs that allows the adoption of Dynamic Partial Reconfiguration, carefully explained in Section 3.3.

# 3.1 FPGA Families

A first distinction of FPGAs can be made based on where configuration is stored on-chip. FPGA's configuration can be either volatile or non volatile, and one have advantages respect to other. Modern FPGAs adopt one of these three methods to storage configuration:

- **FLASH-based**: flash-based FPGAs use flash memory as a primary resource for configuration storage, and doesn't require SRAM; this technology has an advantage of being less power consumptive and is also more tolerant to radiation effects;

- **ANTIFUSE-based**: antifuse-based FPGAs can be programmed only on "burned" to conduct current. The antifuses are normally open circuit and, when programmed, form a permanent, passive, low-impedance connection, leading to the fastest signal propagation. They provides excellent protection against design pirating and cloning;

- **SRAM-based**: configuration data is stored in Static RAM memory cells. Since SRAM is volatile and can't keep data without power source, such FPGAs must be configured upon start-up. The SRAM cells maintaining configuration require about 6 to 7 MOS per connection; these extra transistors take up extra silicon and increase area. Moreover the external memory needed to load configuration data on the internal SRAM requires extra board space which increases board and component cost to the overall system. The main advantage is the possibility to re-program FPGA at any time and configuration time is smaller than other solutions such Flash-based.

Table 3.1 lists the main features of the three different main FPGA families, comparing them and assessing their main features.

| Feature               | Antifuse-based | Flash-based      | SRAM-based    |  |

|-----------------------|----------------|------------------|---------------|--|

| Volatility            | Non-volatile   | Non-volatile     | Volatile      |  |

| Technology            | Previous nodes | Previous nodes   | State-of-art  |  |

| Re-programmability    | No             | Yes, but limited | Yes, infinite |  |

| Area occupation       | Low            | Medium           | High          |  |

| Programmability Speed | Slow           | NA               | Fast          |  |

| Security              | High           | High             | Limited       |  |

| Power Consumption     | Low            | Medium           | Medium        |  |

| Rad Hardness          | Yes            | No               | No            |  |

Table 3.1: Comparison among FPGA families

Further then being distinguished according to the configuration methodology, there are two main architectures for FPGAs internal architecture, namely fine-grained and coarse-grained. A fine-grained architecture consists of a large number of small logic blocks (e.g. transistors, small macro cells) that allow the user to configure each block to act as any 3-input function, such as a primitive logic gate (AND, OR, NAND, etc.) or a storage element.

A coarse-grained architecture consists of a smaller number of larger and more powerful logic blocks, such as flip-flops and Look-Up Tables. A fine-grain array has many configuration points

to perform very small computations, and thus requires more data bits during configuration. The fine-grain programmability is more amenable to control functions, while the coarser grain blocks with arithmetic capability are more useful for data-path operations. An important consideration with regard to architectural granularity is that fine-grained implementations require a relatively large number of connections to connect small blocks. In coarse-grained devices the amount of connections into the blocks decreases compared to the amount of functionality they can support. This is important because interconnections are usually the major cause of signal delays and will strongly affect design timing performances.

# 3.1.1 Antifuse-based FPGAs

As aforementioned, antifuse-based FPGAs can be programmed only once by "burning" the connections as required at design phase. Figure 3.2 shows how connections are available in the first use of the FPGA device. All the possible links are actually left unconnected. In order to program

Figure 3.2: Unprogrammed antifused connections [44]

the FPGA device at performing the needed function, some of the available links are set up, by applying pulses of relatively high voltage and current to the device's inputs. This process will convert the insulating amorphous silicon in conducting poly-silicon. After the device has been properly programmed, it will look like the one pictured in Figure 3.3

Systems implemented exploiting such technology will feature relatively high speed and low power requirements. The primary advantage of anti-fuse programming technology is its low area. With metal-to-metal anti-fuses, no silicon area is required to make connections, decreasing the area overhead of programmability.

However, this decrease is slightly offset by the need for large programming transistors that supply

Figure 3.3: Programmed antifused connections [44]

the large currents needed to program the antifuse.

On the other hand, the achieved level of flexibility is really low, since they can be programmed only once. Furthermore, since anti-fuse-based FPGAs require a non-standard CMOS process, they are typically well behind in the manufacturing processes that they can adopt compared to other technologies. Furthermore, the fundamental mechanism of programming, which involves significant changes to the properties of the materials in the fuse, leads to scaling challenges when new IC fabrication processes are considered [40]. The main field in which these devices are used is the military one, either thanks to the intrinsic rad-hardness (they are relatively immune radiation effects like SEEs) and high level of security (their configuration data is buried deep inside them, making it almost impossible to reverse-engineer the design [44]).

## 3.1.2 Flash-based FPGAs

Several families of devices use Flash memory to hold FPGA configuration information. Flash memory is non-volatile array and can only be written a finite number of times, since it worn-out quite fast. The non volatility of Flash memory means that the data written to it remains when power is removed.

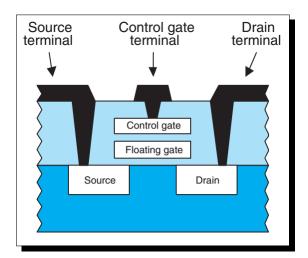

Flash memories technology is based on the use of floating gate transistor, as shown in Figure 3.4. In its unprogrammed state, the floating gate is uncharged and doesn't affect the normal operation of the control gate. In order to program the transistor, a relatively high voltage is applied between the control gate and drain terminals. This causes the transistor to be turned hard on, and energetic electrons force their way through the oxide into the floating gate in a process known as hot (high energy) electron injection. When the programming signal is removed, a negative charge

#### 3. FPGA ARCHITECTURE AND DYNAMIC PARTIAL RECONFIGURATION

Figure 3.4: Floating Gate transistor [44]

remains on the floating gate. This charge is very stable and will not dissipate for more than a decade under normal operating conditions [44].

The programming circuitry, such as the high and low voltage buffers needed to program the cell, contributes an area overhead not present in other FPGA devices. However, this cost is relatively modest as it is amortized across numerous programmable elements. In comparison to antifuse, an alternative non-volatile programming technology, Flash-based FPGAs are reconfigurable and can be programmed without being removed from a printed circuit board.

The stored charge on the floating gate inhibits the normal operation of the control gate and, thus, distinguishes those cells that have been programmed from those that have not. This means we can use such a transistor to form a memory cell. Drawbacks to using Flash memory to store FPGA configuration information stem from the techniques necessary to write to it. As mentioned, Flash memory has a limited write cycle lifetime and often has slow write speeds. The number of write cycles varies by technology, but is typically hundreds of thousands to millions. Additionally, most Flash write techniques require higher voltages compared to normal circuits, so they require additional off-chip circuitry or structures such as charge pumps on-chip to be able to perform a Flash write. Another disadvantage of flash-based devices is that they cannot be reprogrammed an infinite number of times, due to charge build-up in the oxide that eventually prevents a flash-based device from being properly erased and reprogrammed.

On the other hand, they do not require extra storage or hardware to program at boot-up. In essence, a Flash-based FPGA can be ready immediately [28].

## 3.2 SRAM-based FPGAs

SRAM memory are the most widely adopted storage element for current FPGA technologies, since it provides fast and infinite reconfigurations at very low price. This is due to the fact that SRAM cells are made with the same CMOS technology on FPGA logic, thus simplifying the production process.

On the other hand, SRAM means that, once a value has been loaded into an SRAM cell, it will remain unchanged unless it is specifically altered or until power is removed from the system. So, configuration data will be lost when power is removed from the system, so these devices always have to be reprogrammed when powered on, thus requiring another non-volatile memory array to store configuration information to be loaded at start-up. Furthermore, if compared with the other aforementioned technologies, SRAM cell is large and dissipates significant static power because of the leakage current.

Altera Stratix or Xilinx Virtex families are examples of coarse-grained SRAM-based FPGAs. More specifically, Xilinx and Altera FPGAs are modular tile-based devices. No matter which device is chosen, the FPGA consists of the same basic building blocks tiled over and over again. In Xilinx FPGAs they are called CLBs (i.e., Configurable Logic Blocks), while in Altera devices are named ALM (i.e., Adaptive Logic Modules).

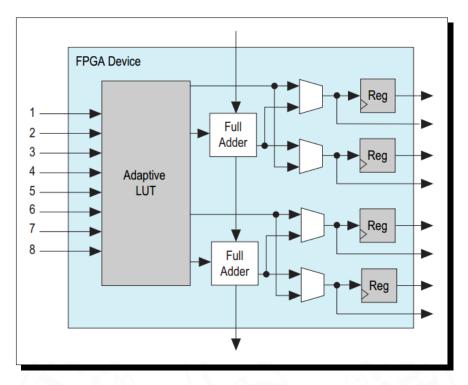

Altera FPGAs internal architecture is made up of logic array blocks, called LABs. LABs are made up of ALMs that can be configured to implement logic, arithmetic, and register functions. Each LAB consists of ten ALMs, various carry chains, shared arithmetic chains, control signals, a local interconnect, and register chain connection lines. The local interconnect transfers signals between ALMs in the same LAB. The direct link interconnect enables the LAB to drive into the local interconnect of its left and right neighbours. Register chain connection transfers the output of the ALM register to the adjacent ALM register in the LAB [4]. Internally, each ALM features 8inputs with four registers, as shown in Figure 3.5.

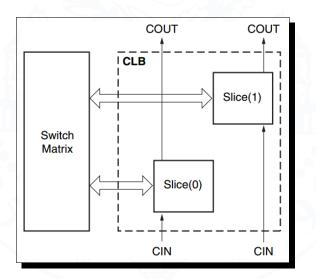

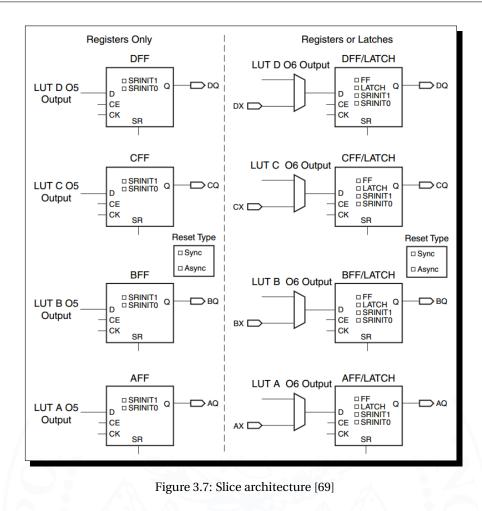

Figure 3.6 shows the internal architecture of a CLB, adopted in Xilinx devices. that is the smallest piece of logic from the perspective of the interconnect structure. In the most recent Xilinx technology, each slice contains 4 Look Up Tables (LUT) and 8 flip-flops; only some slices can use their LUTs as distributed RAM. Each LUT can be configured as either one 6-input LUT (64-bit ROMs) with one output, or as two 5-input LUTs (32-bit ROMs) with separate outputs but common addresses or logic inputs [73]. Each LUT output can optionally be registered in a flip-flop. Four such LUTs and their eight flip-flops as well as multiplexers and arithmetic carry logic form a slice, and two slices form a configurable logic block (CLB) (see Figure 3.7). Four of the eight flip-flops per slice (one per LUT) can optionally be configured as latches. The slice also contains extra multiplexers (MUXFx and MUXF5) to allow a single slice to be configured for wide logic functions of up to eight inputs. A handful of other gates provide extra functionality in the slice, including an XOR gate to complete a 2-bit full adder in a single slice, an AND gate to improve multiplier imple-

# 3. FPGA ARCHITECTURE AND DYNAMIC PARTIAL RECONFIGURATION

Figure 3.5: Adaptive Logic Modules architecture [4]

Figure 3.6: Configurable Logic Block architecture [69]

mentations in the logic fabric, and an OR gate to facilitate implementation of sum-of-products chains. Each slice connects to the general routing fabric through a configurable switch matrix and to each other in the CLB through a fast local interconnect.

Modern SRAM-based FPGAs, further then CLB or ALM, features special purpose architectural building blocks to enhance overall performances. These building blocks are designed to give users special bricks, like Block RAMs, clocking technology, DSP slices, SelectIO technology (for Xilinx devices), to perform ad-hoc tasks at relatively high performances.

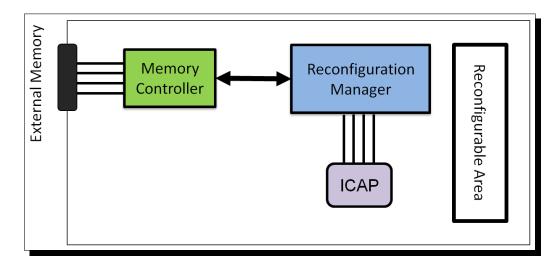

# 3.3 Dynamic Partial Reconfiguration

SRAM-based FPGA technology provides the flexibility of on-site programming and re-programming without going through re-fabrication with a modified design, as pointed out in Section 3.2. In the

aforementioned technology, Dynamic Partial Reconfiguration (DPR) takes this flexibility one step further, allowing the modification of an operating FPGA design by loading a partial configuration file, usually referred as partial bitstream. While a full bitstream file is intended to configure the whole FPGA, thus writing the information all along the configuration memory, partial BIT files can be downloaded to modify reconfigurable regions in the FPGA, only. This process is carried out without compromising the integrity of the applications running on those parts of the device that are not being reconfigured, both the static portion of the FPGA and the possible other reconfigurable modules that are not undergoing the reconfiguration process.

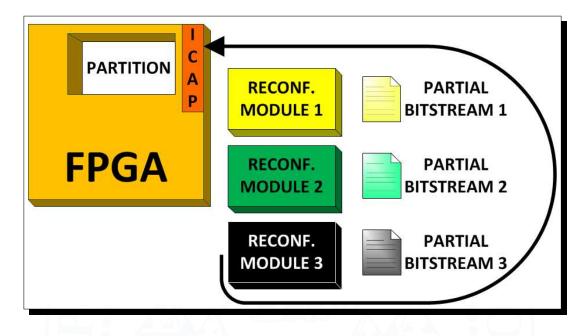

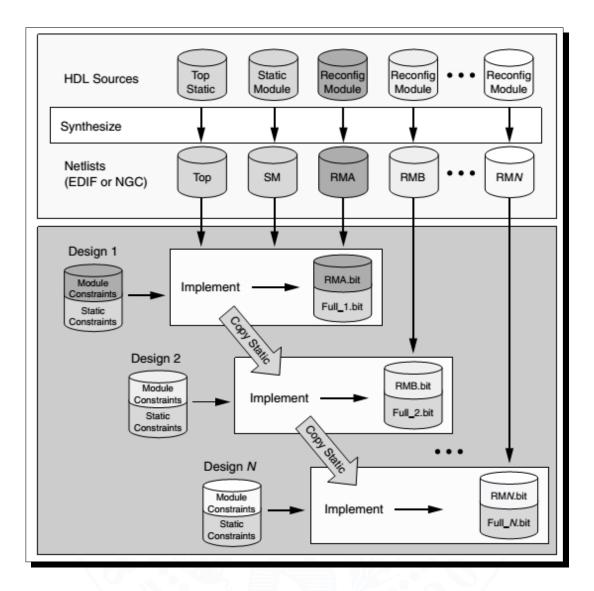

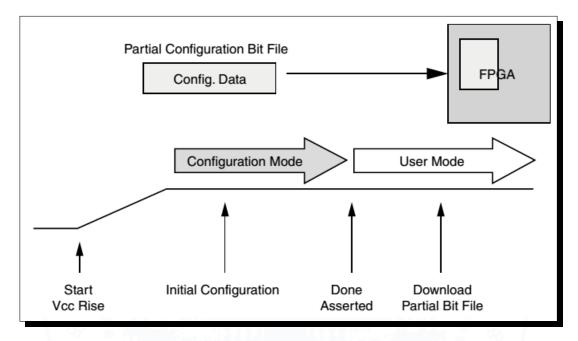

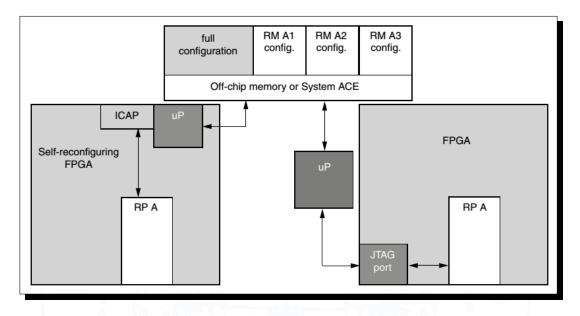

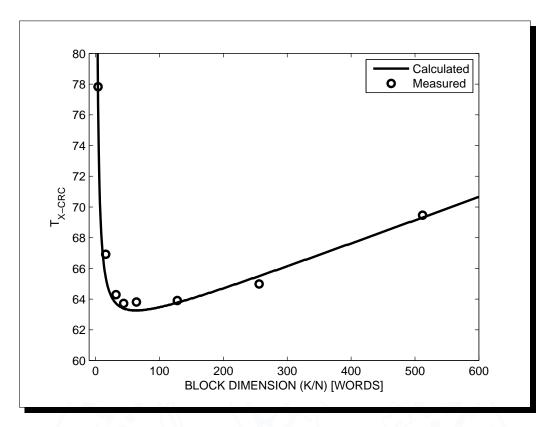

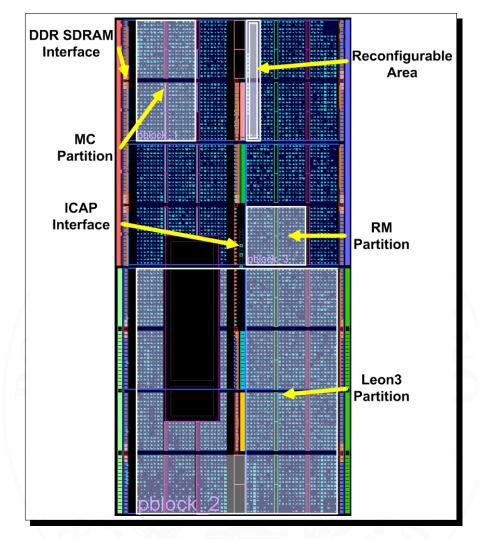

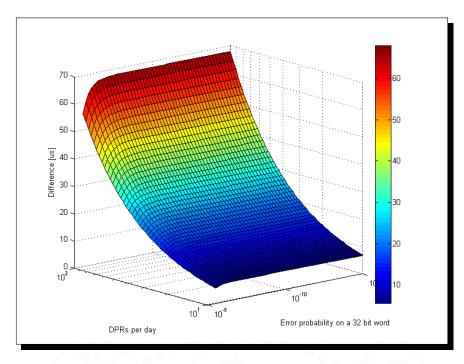

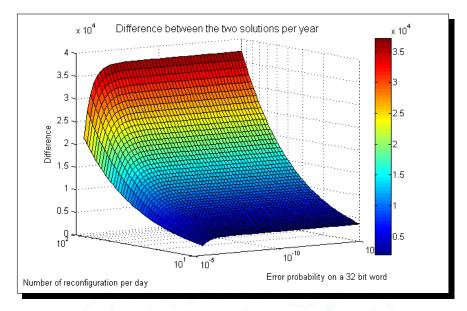

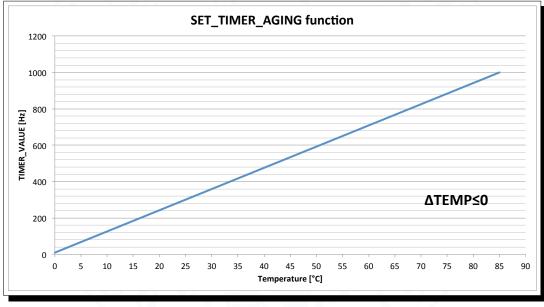

Figure 3.8: Dynamic Partial Reconfiguration - Basic Idea