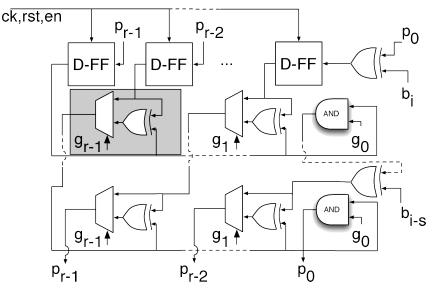

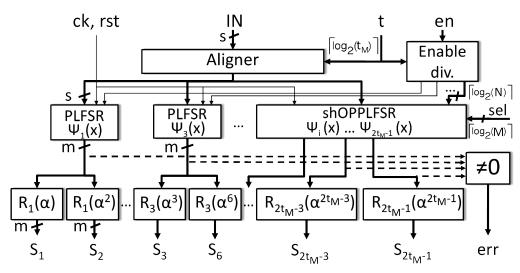

architecture is reported in Fig. 5.1. It enables to dynamically change the generator polynomial of the LFSR. This is a key feature in the implementation of an adaptable BCH encoder.

Figure 5.1: Architecture of a *r*-bit PPLFSR with *s*-bit parallelism [60].

The gray box of Fig. 5.1 highlights the basic adaptable block of this circuit. It exploits a multiplexer, controlled by one of the coefficients of the desired divisor polynomial, to dynamically insert an XOR gate at the output of one of the related D-type flip-flops composing the register. The *s* vertical stages of the circuit implement the parallelism of the PPLFSR computing the state at clock cycle i+s, based on the state at cycle i. However, this solution has high overhead. In fact, such PPLFSR is able to divide by all possible *r*-bit polynomials, while just well selected divisor polynomials are required.

Although Chen at al. deeply analyze the encoding process and the issues related to the storage of parity bits, the decoding process is scarcely analyzed, without providing details on how adaptability is achieved. Four different correction modes, namely t = (9, 14, 19, 24) are considered in [37] for a BCH code defined on  $GF(2^{13})$  with a block size of 512B (every 2 KB page of the flash is split in four blocks). The selection of the 4 modes is based on considerations about the number of parity bits to store. However, there is no provision to understand whether additional modes can be easily implemented. As an example, when selecting correction modes in which the size of the codeword is not a multiple of the parallelism of the decoder, alignment problems arise,

which are completely neglected in the paper.

### 5.2 Optimized Architectures of Programmable Parallel LFSRs

In this section, we will introduce an optimized block to perform an adaptable remainder computation. In fact, one of the most recurring operations in BCH encoding/decoding is the remainder computation between a polynomial representing a message to encode/decode and a generator/minimal polynomial of the code, that depends on the selected correction capability. The PPLFSR of Fig. 5.1 can perform this operation [37].

An *r*-bit PPLFSR can potentially divide by any *r*-bit polynomial by properly controlling its configuration signals  $(g_0 \dots g_{r-1})$ . However, in BCH encoding/decoding, even considering an adaptable codec, just well selected divisor polynomials are required (e.g., the generators polynomials  $g_9(x)$ ,  $g_{14}(x)$ ,  $g_{19}(x)$ ,  $g_{24}(x)$  of the four implemented correction modes of [37]). This computational block is therefore highly inefficient. Moreover, the set of divisor polynomials required in a BCH codec usually share common terms among each other. Such terms can be exploited to generate an optimized PPLFSR (OP-PLFSR) architecture.

Let us consider, as an example, the design of a r=15-bit programmable LFSR able to divide by two polynomials  $p_1(x) = x^{15} + x^{13} + x^{10} + x^5 + x^3 + x + 1$  and  $p_2(x) = x^{13} + x^{12} + x^{10} + x^5 + x^4 + x^3 + x^2 + x + 1$  using a *s*=8-bit parallelism.

A traditional PPFLSR implementation would require  $15 \times 8 = 120$  gray boxes (i.e., 120 XORs-MUXs). According to this implementation, this PPLFSR could divide by any  $2^{15} = 32,768$  possible 15-bit polynomials, even if just 2 polynomials (i.e., the 0.006% of its full potential) are required.

An analysis of the target divisor polynomials can be exploited to optimize the PPLFSR architecture. Table 5.1 reports the binary representation of the two polynomials.

In it, three categories of polynomial terms can be identified:

- 1. Common terms (represented in bold), i.e., terms defined in all considered polynomials ( $x^{13}$ ,  $x^{10}$ ,  $x^5$ ,  $x^3$ , x, and 1 in Table 5.1). For these terms, an XOR will be always required in the PPLFSR, thus saving the area dedicated to the MUX and the related control logic.

- 2. Missing terms (represented in underlined italic zeros), i.e., terms not defined in any of the considered polynomials,  $(x^{14}, x^{11}, x^9, x^8, x^7 \text{ and } x^6 \text{ in Table 5.1})$ . For these

|                                                                      | -          | -        | -              |

|----------------------------------------------------------------------|------------|----------|----------------|

|                                                                      | $x^{1}$    | -        | 1              |

|                                                                      | $x^2$      | 0        | 1              |

| (x)                                                                  | $x^3$      | -        | 1              |

| id <i>p</i> 2 (                                                      | $x^4$      | 0        | 1              |

| (x) an                                                               | $x^5$      | -        | 1              |

| of <i>p</i> 1                                                        | $x^6$      | ō        | $\overline{o}$ |

| ation                                                                | $x^7$      | ō        | $\overline{0}$ |

| senta                                                                | $\chi^{8}$ | ō        | $\overline{0}$ |

| repre                                                                | $x^{6}$    | ō        | $\overline{0}$ |

| of the                                                               | $x^{10}$   | -        | 1              |

| ample                                                                | $x^{11}$   | ō        | $\overline{o}$ |

| An exa                                                               | $x^{12}$   | 0        | 1              |

| Table 5.1: An example of the representation of $p_1(x)$ and $p_2(x)$ | $x^{13}$   | -        | 1              |

| Tab]                                                                 | $x^{14}$   | ō        | $\overline{0}$ |

|                                                                      | $x^{15}$   | -        | 0              |

|                                                                      |            | $p_1(x)$ | $p_2(x)$       |

81

terms both the XOR and the related MUX can be avoided.

3. Specific terms, i.e., terms that are specific of a subset of the considered polynomials  $(x^{15}, x^{12}, x^4, x^2 \text{ in Table 5.1})$ . These terms are the only ones actually required.

We can therefore implement an optimized programmable LFSR (OPPLFSR) with three main building blocks:

- 1. each common present term (i.e., columns of all "1" of Table 5.1) needs an XOR, only;

- 2. each common absent term (i.e., columns of all "0" of Table 5.1) needs neither XOR nor MUX;

- 3. each specific term has a gray box, as Fig. 5.1;

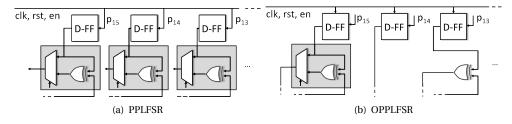

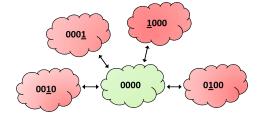

Fig. 5.2 shows the resulting design for the portion  $x^{15}$ ,  $x^{14}$  and  $x^{13}$ .

Figure 5.2: Example of the resulting PPLFSR (a) and OPPLFSR (b) with 8-bit parallelism for  $x^{15}$ ,  $x^{14}$  and  $x^{13}$  of  $p_1(x)$  and  $p_2(x)$  [60]

This optimization also applies to polynomials with very different lengths. As an example, an OPPLFSR with single bit parallelism and able to divide by  $p_1(x) = x^{225} + x + 1$  and  $p_2(x) = x + 1$ , would only require a single adaptable block, compared to the 226 blocks required by a normal PPLFSR. Furthermore, the advantage of the OPPLFSR increases with the parallelism of the block. In fact, with the same 2 polynomials, a 8-bit OPPLFSR would require 8 adaptable blocks compared to  $226 \times 8 = 1,808$  adaptable blocks of a traditional PPLFSR.

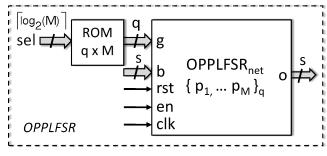

For sake of generality, Fig. 5.3 shows the high-level architecture of a generic OPPLFSR. Such a block is able to divide by a set  $p_1(x), ..., p_M(x)$  of polynomials. We denote with q the number of required gray boxes.

Figure 5.3: High-level architecture of the OPPLFSR [60]

The OPPLFSR interface includes: a *s*-bit input port (b) used to feed the data, a  $\lceil \log_2 (M) \rceil$ bit input port (sel) used to select the polynomial of the division, and a *s*-bit port (o) providing the result of the division. Two blocks compose the OPPLFSR: *OPPLFSR<sub>net</sub>* and *ROM*. The OPPLFSR<sub>net</sub> represents the complete network, partially shown in the example of Fig. 5.2. Given the output of the ROM, the q-bit signal g controls the MUXs of the q gray boxes (Fig. 5.2) according to the selected polynomial. The ROM is optimized accordingly with the design of the OPPLFSR, which leads to a reduced ROM and to a lower area overhead w.r.t. a full PPLFSR.

### 5.3 BCH Code Design Optimization

In this section, we address first the issue of choosing the most suitable set of polynomials for an optimized adaptable BCH code. Then, we propose a novel block, shared between the adaptable BCH encoder and the decoder, which reduces the area overhead of the resulting codec core.

### 5.3.1 The choice of the set of polynomials

The optimization offered by the OPPLFSR introduced in Section 5.2, may become ineffective if not properly exploited. It depends on the number and on the terms of the shared divisor polynomials implemented in the block. As an example, an excessive number of shared polynomials may make it difficult to find common terms, leading to an unwilled increase of the area overhead. Therefore, the choice of the polynomials to share is critical and must be properly tailored to the overall design.

Let us denote by  $\Omega$  the set of *t* generators  $g_i(x)$  and *t* minimal polynomials  $\psi_i$  which fully characterize an adaptable BCH code (see Section 5.1). Since for  $GF(2^m)$  several

primitive polynomials  $\psi_i(x)$  can be used to define the code, several set  $\Omega_i$  can be constructed. Choosing the most suitable set  $\Omega_i$  is critical to obtain an effective design of the OPPLFSR. On the one hand, it can be shown that the complexity of  $\Omega_i$  increases with m [92, 118, 132]. On the other hand, the current trend is to adopt BCH codes with high values of m (e.g.,  $GF(2^{15})$ ) because current flash devices features a worse bit error rate [52]. Therefore, a simple visual inspection of each set  $\Omega_i$  is not feasible to find the most suitable set of polynomials. An algorithmic approach is mandatory.

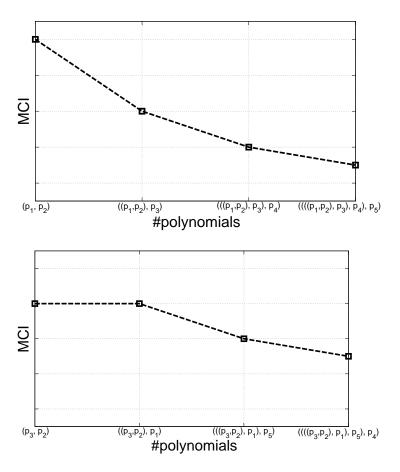

Each set  $\Omega_i$  can be classified resorting to a *Maximum Correlation Index* (MCI). We define as  $MCI(p_1, p_2, ..., p_N)$  the maximum number of common terms shared by a generic set of polynomials  $p_1, p_2, ..., p_N$ . As an example, the polynomials of Table 5.1 have  $MCI(p_1, p_2) = 12$ .

In the sequel, we introduce an algorithm to assess each set  $\Omega_i$  according to its MCI. Given  $i = \{1, ..., Y\}$ , for each set  $\Omega_i$ :

- 1. consider  $\Omega_i = \{p_1, ..., p_N\}$  and  $v_0 = p_1$ ;

- 2. determine the polynomial  $p_h$  such that the partition  $S_{i,1} = (v_0, p_h)$  has the maximum  $MCI(v_0, p_h)$ , where  $h = \{1, ..., N\}$  and  $p_h \neq v_0$ ;

- 3. determine the polynomial  $p_k$  such that the partition  $S_{i,1} = ((v_0, p_h), p_k)$  has the maximum  $MCI(v_0, p_h, p_k)$ , where  $k = \{1, ..., N\}$  and  $p_k \neq p_h \neq v_0$ ;

- 4. repeat step 3 until all polynomials have been considered in the partition  $S_{i,1}$ ;

- 5. change the starting polynomial to the next one, e.g.,  $v_0 = p_2$ , considering  $S_{i,2}$  and repeat steps 2-4;

- 6. when  $v_0 = p_N$ , consider the next set  $\Omega_{i+1}$ .

The algorithm ends when all sets  $\Omega_i$  have been analyzed. For each  $\Omega_i$ , the output is a set of partitions:

$$S_{i,j} = \{S_{i,1}, S_{i,2}, \dots, S_{i,N}\}$$

(5.5)

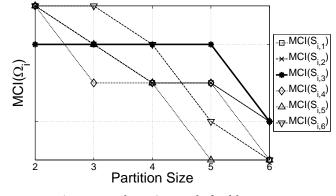

Fig. 5.4 graphically shows the MCI of two partitions generated from two different starting points, for an hypothetical set  $\Omega_i$ .

Fig. 5.4 shows that MCI always has a decreasing trend with the size of the partition *S*. This is straightforward since adding a polynomial may only decrease or keep constant

Figure 5.4: MCI examples of two hypothetical partitions  $S_{i,1}$  and  $S_{i,2}$

the current value of MCI. The curves, reported in 5.4, are critical in the choice of the most suitable set of polynomials for an optimized BCH code. For each partition  $S_{i,j}$  with  $j = \{1...N\}$ , we can compute the average MCI ( $MCI_{avg}$ ) as:

$$MCI_{avg}(S_{i,j}) = \frac{1}{N} \sum_{l=1}^{N-1} MCI_l$$

(5.6)

Eq. 5.6 applies to each set  $\Omega_i$  where  $i = \{1...Y\}$ .

The best partition of the set  $\Omega_i$  is then computed selecting the one with maximum  $MCI_{avg}$ :

$$S_{best_i} = \arg\max_{j} \left[ MCI_{avg} \left( S_{i,j} \right) \right]$$

(5.7)

85

Finally, Eq. 5.8 compares the best partition of each set  $\Omega_i$  to find the best set of polynomials:

$$S_{bestBCH} = argmax[S_{best_i}]$$

(5.8)

Eq. 5.8 defines the family of polynomials  $S_{bestBCH}$ , with the maximum average number of common terms.

|       |       |                       |       | 1                     |                       | ŀ     |   |

|-------|-------|-----------------------|-------|-----------------------|-----------------------|-------|---|

|       | $x^6$ | <i>x</i> <sup>5</sup> | $x^4$ | <i>x</i> <sup>3</sup> | <i>x</i> <sup>2</sup> | $x^1$ | 1 |

| $p_1$ | 1     | 0                     | 1     | 0                     | 0                     | 1     | 0 |

| $p_2$ | 1     | 1                     | 0     | 1                     | 0                     | 1     | 1 |

| $p_3$ | 1     | 0                     | 1     | 1                     | 1                     | 1     | 1 |

| $p_4$ | 0     | 1                     | 1     | 0                     | 0                     | 0     | 1 |

| $p_5$ | 1     | 1                     | 0     | 1                     | 1                     | 0     | 1 |

| $p_6$ | 0     | 0                     | 1     | 0                     | 0                     | 1     | 1 |

Table 5.2: An example of  $\Omega_i$

Let us provide an example to support the understanding of the algorithm. Suppose to consider a single set  $\Omega_i$  composed of the polynomials of Table 5.2. The steps of the algorithm are:

- 1. Let us start with  $v_0 = p_1$

- 2. We first evaluates  $MCI(p_1, p_2) = 3$ ,  $MCI(p_1, p_3) = 4$ ,  $MCI(p_1, p_4) = 3$ . Since  $MCI(p_1, p_3) = 4$  is the maximum, the resulting partition is  $S_{i,1} = \{p_1, p_3\}$

- 3. The next step considers  $MCI((p_1, p_3), p_2) = 3$  and  $MCI((p_1, p_3), p_4) = 3$ . It is straightforward that the choice of either  $p_2$  or  $p_4$  does not affect the final value of the  $MCI_{avg}$ .

Given  $\Omega_i$  with starting point  $p_1$ , it can be shown that the final partition is  $S_{i,1} = \{((p_1, p_3), p_4), p_2\}$  with a  $MCI_{avg} = (4+3+3)/4 = 2.5$  from Eq. 5.6.

The complete algorithm iterates this computation for all possible starting points. Fig. 5.5 graphically shows the output of the MCI associated with each partition  $S_{i,j}$  calculated for the following starting point  $j = \{1, 2, 3, 4\}$ .

According to Eq. 5.7,  $S_{i,2}$  (the bold line) is the  $S_{best_i}$  of the example of Table 5.2, with a  $MCI_{avg}(S_{i,j}) = 4$ .

Figure 5.5: The MCI Trend of Table 5.2 [60]

### 5.3.2 Shared Optimized Programmable Parallel LFSRs

Let us assume to design an adaptable BCH code with correction capability from 1 up to  $t_M$ . Such a code needs to compute remainders of the division of:

- the message m(x) by (potentially) all generator polynomials from  $g_1$  up to  $g_{t_M}$ , for the encoding (5.2);

- the codeword c(x) by (potentially) all minimal polynomials from  $\psi_1(x)$  up to  $\psi_{2t_M-1}(x)$ , to compute the set of syndromes required during the decoding phase.

In a traditional implementation, these computations are performed by two separate set of LFSRs. In this chapter, we propose to devise a shared set of LFSRs able to: (i) perform all these computations, and (ii) reduce the overall cost in terms of resources overhead. Therefore, we can adopt the same shared set of LFSRs both in the encoding and decoding processes. This is possible since in a flash memory these operations are, in general, not required at the same time.

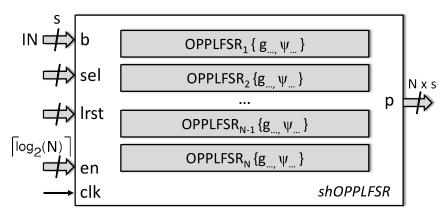

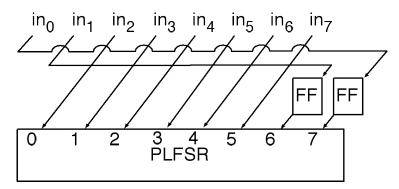

The OPPLFSR, introduced in Section 5.2, is the main building block of the set of shared LFSRs. Therefore, we will refer hereafter to such set of LFSRs as shared OPPLFSR (shOPPLFSR). Fig. 5.6 shows the high-level architecture of the shOPPLFSR. Its interface includes: a *s*-bit input port (IN) used to input the data to be divided, a  $\lceil \log_2(N) \rceil$ -bit input port (en) used to enable each OPPLFSR, an input port (sel) used to select the proper polynomial by which each OPPLFSR has to divide, and a N × s-bit port (p) providing the result of the division.

Figure 5.6: The shOPPLFSR architecture is composed by multiple OPPLFSRs

Given *N* OPPLFSRs and a maximum correction capability  $t_M$ , each OPPLFSR<sub>i</sub> performs the division by a set of generator polynomials g(x) and minimal polynomials  $\psi(x)$ . Such shOPPLFSR can be seen as an optimized programmable LFSR able to:

- divide by all generator polynomials from  $g_1(x)$  to  $g_{t_M}(x)$ ;

- divide by specific subsets of minimal polynomials from Eq. 5.1, as well.

An improper choice of the shared polynomials g(x) and  $\psi(x)$  can dramatically reduce the performance of the overall BCH codec. Also the partitioning strategy adopted is critical to maximize the optimization in terms of area, minimizing the impact on the latency of encoding/decoding operations.

The algorithm presented in Section 5.3.1 provides a valuable support for the exploration of this huge design space. In fact, the proposed method can be exploited to properly partition polynomials into the different OPPFLSRs of Fig. 5.6, in order to maximize the optimization of the resulting shOPPFLSR. Such optimization should not be obtained following blindly the outcomes of the algorithm, but always tailoring them to the specific design. Regarding this topic, Section 5.6 provides more details about our experimental setup and the related experimental results.

### 5.4 Adaptable BCH Encoder

In this section, we propose an adaptable BCH encoder which exploits the shOPPLFSR of Section 5.3. According to the BCH theory, the shOPPLFSR of Fig. 5.6 is a very efficient circuit to perform the computation expressed in Eq. 5.2. However, in the encoding phase,

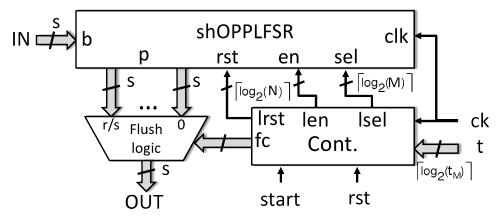

the message m(x) must be multiplied by  $x^r$  before calculating the reminder of the division by g(x) (see Eq. 5.2). This can be obtained without significant modifications of the architecture of shOPPFLSR. It is, in fact, enough to input the bits of the message directly in the most significant bit of the LFSR, instead than starting from least significant bit. Fig. 5.7 shows the high-level architecture of the adaptable encoder.

Figure 5.7: High-level architecture of the adaptable encoder highlighting the three main building blocks and their main connections.

The encoder's interface includes: a *s*-bit input port (IN) used to input the *k*-bit message to encode starting from the most significant bits, a  $\lceil \log_2(t_M) \rceil$ -bit input port (t) selecting the requested correction capability in a range between 1 and  $t_M$ , a start input signal used to start the encoding process and a *s*-bit output port (OUT) providing the *r* parity bits. Three blocks compose the encoder: a *shOPPLFSR*, a *flush logic* and a *controller*.

The shOPPLFSR performs the actual parity bits computation. According to the BCH theory, adaptation is achieved by supporting the computation of remainders with  $t_M$  generator polynomials, one for each value t may assume. The controller achieves this task in two steps: (i) enabling the proper OPPLFSR through the len signal, and (ii) selecting the proper polynomial through the lsel signal, according to the desired correction capability t. Then, it manages the overall encoding process based on two internal parameters:

- 1. the number of *s*-bit words composing the message (fixed at design time)

- 2. the number of produced *s*-bit parity words, that depends on the selected correction capability. The flush logic splits the *r* parity bits into *s*-bit words, providing them in

output, one per clock cycle.

To further optimize the encoding and the decoding process, since in a flash memory these operations are not required at the same time, the encoder's shOPPLFSR can be merged with the shOPPLFSRs that will be employed in the syndrome computation (see Section 5.5.1), thus allowing additional area saving.

### 5.5 Adaptable BCH Decoder

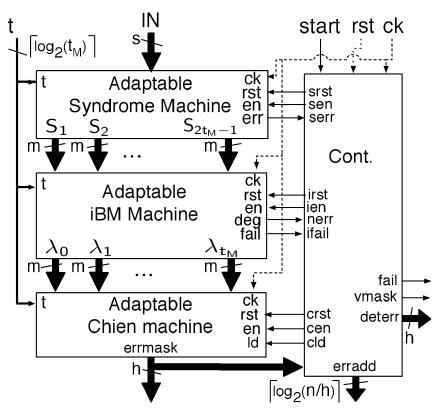

Fig. 5.8 presents the high-level architecture of the proposed adaptable decoder. The decoder's interface includes: a *s*-bit input port (IN) used to input the *n*-bit codeword to decode (starting from the most significant bits), a  $\lceil \log_2(t_M) \rceil$ -bit input port (t) to select the desired correction capability, a start input signal to start the decoding and a set of output ports providing information about detected errors. In particular:

- deterr is a  $\lceil \log_2(t_M) \rceil$  -bit port providing the number of errors that have been detected in a codeword. In case of decoding failure it is set to 0;

- erradd and errmask provide information about the detected error positions. Assuming the codeword split into h-bit words, erradd is used as a word address in the codeword and errmask is a h-bit mask whose asserted bits indicate detected erroneous bits in the addressed word. The parallelism h of the error mask depends on the parallelism of the Chien machine, as explained later in this section;

- vmask is asserted whenever a valid error mask is available at the output of the decoder;

- fail is asserted whenever an error occurred during the decoding process (e.g., the number of errors is greater than the selected correction capability);

- end is asserted when the decoding process is completed.

The full decoder therefore includes four main blocks: (1) the *Adaptable Syndrome Machine*, computing the syndromes of the codeword, (2) the *Adaptable inversion-less Berlekamp Massey (iBM) Machine*, that elaborates the syndromes to produce the error locator polynomial, (3) the *Adaptable Chien Search Machine* in charge of searching for the error positions, and (4) the *Controller* coordinating the overall decoding process.

Figure 5.8: High-level architecture of the adaptable decoder, highlighting the four main building blocks: the adaptable syndrome machine, the adaptable iBM machine, the adaptable Chien machine, and the controller in charge of managing the overall decoding process

### 5.5.1 Adaptable Syndrome Machine

Fig. 5.9 shows the high-level architecture of the proposed adaptable syndrome machine with correction capability  $1 \le t \le t_M$ .

According to Section 5.2, remainders can be calculated by a set of Parallel LFSRs (PLF-SRs) whose architecture is similar to the one of the PPLFSR of Fig. 5.1, with the only difference that the characteristic polynomial is fixed (XOR gates are inserted only where needed, without multiplexers). Each PLFSR computes the remainder of the division of the codeword by a different minimal polynomial  $\psi_i(x)$ . Given two correction capabilities  $t_1$  and  $t_2$  with  $t_1 < t_2 \le t_M$ , the set of  $2t_1$  minimal polynomials generating the code for  $t_1$  is a subset of those generating the code for  $t_2$ . To obtain adaptability of the correction capability in a range between 1 and  $t_M$ , the syndrome machine can therefore be designed to compute the maximum number  $t_M$  of remainders required to obtain  $2t_M$

Figure 5.9: Architecture of the adaptable Syndrome Machine

syndromes. Based on the selected correction capability t, only the first t PLFSRs out of the  $t_M$  available in the circuit are actually enabled through the *Enable div.* network of Fig. 5.9.

A full parallel syndrome calculator, including  $t_M$  PLFSRs, requires a considerable amount of resources that are underutilized in the early stages of the flash lifetime when reduced correction capability is required. To optimize the adaptable syndrome machine and to trade-off between complexity and performance, we exploit the shOPPLFSR introduced in Section 5.2. The architecture proposed in Fig. 5.9 includes two sets of LF-SRs for remainder computation: (i) conventional PLFSRs, and (ii) shOPPLFSR. Conventional PLFSRs are exploited for parallel fast computation of low order syndromes required when the requested correction capability is below a given threshold. shOPPLFSR is designed to divide for selected groups of minimal polynomials not covered by the fixed PPLFSRs. It represents a shared resource utilized when the requested correction capability increases. It enables area reduction at the cost of a certain time overhead. The architectural design, chosen for the fixed PLFSRs and the OPPLFSR, enables to trade-off hardware complexity and decoding time, as it will be discussed in Section 5.6.

It is worth to mention here that the parallel architecture of the PLFSR, coupled with the adaptability of the code, introduces a set of additional word alignment problems that must be addressed to correctly adapt the syndrome calculation to different values of *t*. The syndrome machine receives the codeword in words of *s* bits, starting from the most

Figure 5.10: Example of the schema of a byte aligner for t = 2 and s = 8

significant word. When the number of parity bits does not allow to align the codeword to the parallelism *s*, the unused bits of the last word are filled with 0. To correctly compute each syndrome, the parity bit  $r_0$  of the codeword must enter the least significant bit of each LFSR. The aligner block of Fig. 5.9 assures this condition by properly right-shifting the codeword while it is input into the syndrome machine. Let us consider the following example: k = 2KB, m = 15, t = 2, s = 8 and therefore  $r = m \cdot t = 30$ . Since 30 is not multiple of s = 8, the codeword is filled with two zeros and  $p_0$  is saved in position 2 of the last byte of the codeword ( $m_{2047} m_{2046}...m_1 m_0 p_{29} p_{28}...p_1 p_0 00$ ). In this case the PLFSRs require a 2-bit alignment, implemented by the network of Fig. 5.10. It simply delays the last 2 input bits resorting to two flip-flops, whose initial state has to be zero, and properly rotates the remaining input bits. Changing the correction capability of the decoder changes the number of parity bits of the codeword, and therefore the required alignment. Given the parallelism *s* of the decoder, a maximum of *s* alignments must be provided and implemented in the *Aligner* block of Fig. 5.9.

With the proper alignment, the PLFSRs can perform the correct division and the evaluators can provide the required syndromes. The evaluators are simple combinational networks involving XOR operations, according to the Galois Fields theory (readers may refer to [102] for specific implementation details).

### 5.5.2 Adaptable Berlekamp Massey Machine

In our adaptable codec, we implemented the inversion-less Berlekamp-Massey (iBM) algorithm proposed in [142] which is able to compute the error locator polynomial  $\lambda(x)$  in *t* iterations.

The main steps of the computation are reported in Alg. 1. At iteration *i* (rows 2 to 12), the algorithm finds an error locator polynomial  $\lambda(x)$  whose coefficients solve the first *i* equations of (5.3) (row 4). It then tests if the same polynomial solves also *i* + 1 equations (row 5). If not, it computes a discrepancy term  $\delta$  so that  $\lambda(x) + \delta$  solves the first *i* + 1 equations (row 9). This iterative process is repeated until all equations are solved. If, at the end of the iterations, the computed polynomial has a degree lower than *t*, it correctly represents the error locator polynomial and its degree represents the number of detected errors; otherwise, the code is unable to correct the given codeword.

| Algorithm 1 Inversion-less Berlekamp-Massey alg.                |  |  |  |  |  |  |  |

|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| 1: $\lambda(x) = 1, k(x) = 1, \delta = 1$                       |  |  |  |  |  |  |  |

| 2: for $i = 0$ to $t - 1$ do                                    |  |  |  |  |  |  |  |

| 3: $d = \sum_{j=1}^{t} \left( \lambda_j \cdot S_{2i-j} \right)$ |  |  |  |  |  |  |  |

| 4: $\lambda(x) = \delta \lambda(x) + d \cdot x \cdot k(x)$      |  |  |  |  |  |  |  |

| 5: <b>if</b> $d = 0$ OR $Deg(\lambda(x)) > i$ <b>then</b>       |  |  |  |  |  |  |  |

| $6: \qquad k(x) = x^2 \cdot k(x)$                               |  |  |  |  |  |  |  |

| 7: else                                                         |  |  |  |  |  |  |  |

| 8: $k(x) = x \cdot k(x)$                                        |  |  |  |  |  |  |  |

| 9: $\delta = d$                                                 |  |  |  |  |  |  |  |

| 10: end if                                                      |  |  |  |  |  |  |  |

| 11: i=i+1                                                       |  |  |  |  |  |  |  |

| 12: end for                                                     |  |  |  |  |  |  |  |

| 13: if $Deg(\lambda(x)) < t$ then                               |  |  |  |  |  |  |  |

| 14: output $\lambda(x)$ , $Deg(\lambda(x))$                     |  |  |  |  |  |  |  |

| 15: else                                                        |  |  |  |  |  |  |  |

| 16: output FAILURE                                              |  |  |  |  |  |  |  |

| 17: end if                                                      |  |  |  |  |  |  |  |

The architecture of the iBM machine is intrinsically adaptive as long as one guarantees that the internal buffers and the hardware structures are sized to deal with the worst case design (i.e.,  $t = t_M$ ). The coefficients of  $\lambda(x)$  are m-bit registers whose number depends on the correction capability. In the worst case, up to  $t_M$  coefficients must be stored for each polynomial.

The adaptable iBM machine therefore includes two m-bit register files with  $t_M$  registers to store these coefficients. Whenever the requested correction capability is lower than  $t_M$ , some of the registers will remain unused. The number of multiplications performed during the computations also depends on t. Row 3 requires t multiplications, while row 4 requires t multiplications to compute  $\delta \lambda_i(x)$  and t multiplications to compute  $d \cdot x \cdot k(x)$ .

We implemented a serial iBM Machine including 3 multipliers for  $GF(2^m)$  to perform multiplications of rows 3 and 4. It can perform each iteration of the iBM algorithm in 2*t* clock cycles (*t* cycles for row 3 and *t* cycles for row 4) achieving a time complexity of  $2t^2$  clock cycles. This implementation is a good compromise between performance and hardware complexity. An input *t* dynamically sets the number of iterations of the algorithm, thus implementing the adaptation.

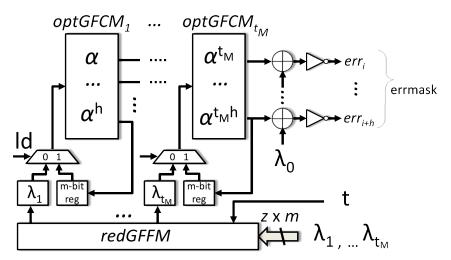

### 5.5.3 Adaptable Chien Machine

The overall architecture of the proposed adaptable Chien Machine is shown in the Fig. 5.11. The machine first loads into  $t_M$  m-bit registers the coefficients from  $\lambda_1$  to  $\lambda_{t_M}$  of the error locator polynomial  $\lambda(x)$  computed by the iBM machine (ld = 0). The actual search is then started (ld = 1). At each clock cycle, the block performs h parallel evaluations of  $\lambda(x)$  in GF(2<sup>*m*</sup>) and outputs a h-bit word, denoted as errmask. Each bit of errmask corresponds to one of the h candidate error locations that have been evaluated. Asserted bits denote detected errors. This mask can then be XORed (outside the Chien Machine) with the related bits of the codeword in order to correct the detected erroneous bits.

Figure 5.11: Architecture of the proposed parallel adaptable Chien Machine with parallelism equal to h

The architecture of Fig. 5.11 provides an adaptable Chien machine with lower area consumption than other designs [37], having, at the same time, a marginal impact on performance. Four interesting features contribute to such optimization: (i) constant multipliers substructure sharing, (ii) adaptability to the correction capability, (iii) improved fast skipping to reduce the decoding time, and (iv) reduced full GF multipliers area. In the sequel, we briefly address each feature.

The first feature is represented by the optimized GF Constant Multipliers (optGFCM) networks of Fig. 5.11. The *h* parallel evaluations are based on equation (5.4). In the worst case ( $t = t_M$ ), the parallel evaluation of equation (5.4) requires a matrix of  $t_M \times h$  constant Galois multipliers. They multiply the content of the  $t_M$  registers by  $\alpha$ ,  $\alpha^2$ , ...,  $\alpha^{t_M}$ , respectively. However, we can note that each column of constant GF multipliers shares the same multiplicand. Therefore, we can iteratively group their best-matching combinations [39] into the  $t_M$  optGFCM networks of Fig. 5.11. Such optGFCMs provide up to 60% reduction of the hardware complexity of the machine with no impact on performance.

The second feature is the adaptability of the Chien machine. The rows of the matrix define the parallelism of the block (i.e., the number of evaluations per clock cycles), while the columns define the maximum correction capability of the block. Whenever the selected correction capability t is lower than  $t_M$ , the coefficients of the error locator polynomial of degree greater than t are equal to zero and do not contribute to equation (5.4), thus allowing us to adapt the computation to the different correction capabilities.

The third feature stems from a simple observation. Depending on the selected correction capability t, not all the elements of  $GF(2^m)$  represent realistic error locations. In fact, considering a codeword composed of k bits of the original message and  $r = m \cdot t$  parity bits, only  $k + m \cdot t$  out of  $2^m$  elements of the Galois field represent realistic error locations. Given that an error location L is the inverse of the related GF element ( $L = 2^m - 1 - i$ ), the elements of  $GF(2^m)$  in which the error locator polynomial must be evaluated are in the following range:

$$\begin{bmatrix} \underline{\alpha^{2^{m}-1}} , \underline{\alpha^{2^{m}-k-m\cdot t}} \\ \text{error location L=0 error location } L=k+m\cdot t-1 \end{bmatrix}$$

(5.9)

All elements between  $\alpha^0$  and  $\alpha^{2^{m-k-m\cdot t}}$  can be skipped to reduce the computation time. Differently from fixed correction capability fast skipping Chien machines, this interval is not constant here but depends on the selected *t*. The architecture of Fig. 5.11 implements an adaptable fast skipping by initializing the internal registers to the coefficients of the error corrector polynomial multiplied by a proper value  $\beta_{ini}^t = \alpha^{2^m-k-m\cdot t-1}$ . For each value of *t*,  $t_M$  *m*-bit constant values corresponding to  $\beta_{ini}^t$ ,  $(\beta_{ini}^t)^2$ , ...,  $(\beta_{ini}^t)^{t_M}$ must be stored in an internal ROM (not shown in Fig. 5.11) and multiplied by the coefficients  $\lambda_i$  using a full GF multiplier. This is connected with the last feature, the reduced GF Full Multipliers (redGFFM) network of Fig. 5.11. Each full GF multiplier has a high cost in terms of area. Since they are used only during initialization of the Chien, the redGFFM adopts only  $z \leq t_M$  full GF multipliers. It also includes a ( $\lambda$ ) input port to input z coefficients, per clock cycles, of the error locator polynomial. This network enables to reduce area consumption, at a reasonable cost in terms of latency.

For the sake of brevity, a detailed description of the controller required to fully coordinate the decoder's modules interaction is omitted.

### 5.6 Experimental Results

This section provides experimental data from the implementation of the adaptable BCH codec proposed on a selected case study.

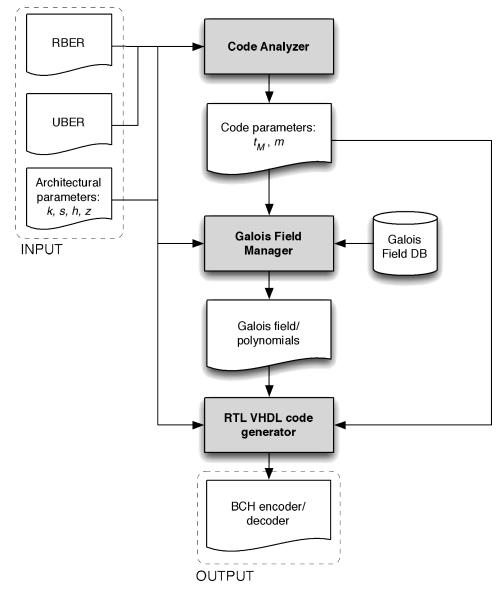

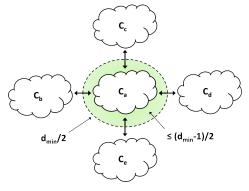

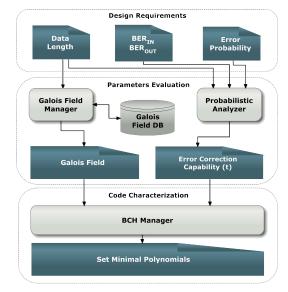

### 5.6.1 Automatic generation framework

To cope with the complexity of a manual design of these blocks, a semi-automatic generation tool named ADAGE (ADaptive ECC Automatic GEnerator) [54] able to generate a fully synthesizable adaptable BCH codec core following the proposed architecture has been designed and exploited in this experimentation extending a preliminary framework previously introduced in [28]. The overall architecture of the framework is in Fig. 5.12.

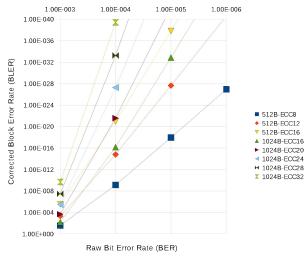

The code analyzer block represents the first computational step required to select the desired code correction capability based on the Bit Error Rate (BER) of a page of the selected flash [107]. The BER is the fraction of erroneous bits of the flash. It is the key factor used to select the correction capability. Two values of BER must be considered. The former is the raw bit error rate (RBER), i.e., the BER before applying the error correction. It is technology/environment dependent and increases with the aging of the page [23, 143]. The latter is the uncorrectable bit error rate (UBER), i.e., the BER after the application of the ECC, which is application dependent. It is computed as the probability of having more than *t* errors in the codeword (calculated as a binomial distribution of randomly occurred bit errors) divided by the length of the codeword [48]:

$$UBER = \frac{P(E > t)}{n} = \frac{1}{n} \sum_{i=t+1}^{n} {n \choose i} \cdot RBER^{i} \cdot (1 - RBER)^{n-i}$$

(5.10)

Given the RBER of the flash and the target UBER, Eq. 5.10 can be exploited to compute the maximum required correction capability of the code and consequently the value

Figure 5.12: BCH codec automatic generation framework.

of *m* that defines the target GF. Given these two parameters, the Galois Field manager exploits an internal polynomials database to generate the set of minimal polynomials and the related generator polynomials for the selected code.

Finally, the RTL VHDL code generator combines these parameters and generates a RTL description of the BCH encoder and decoder implementing the architecture illustrated in this paper.

The whole framework combines Matlab software modules with custom C programs. The full framework code is available for download at http://www.testgroup.polito. it in the Tools section of the website.

### 5.6.2 Architectural-layer characterization

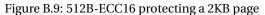

In our specific design, the ECC sub-system has been implemented to work on a full page of the flash (i.e., k = 4KB). We considered a target UBER equal to 1E-11, as in [106]. Based on equation (5.10), Table 5.3 reports the correction capability required to achieve the target UBER considering the RBERs of the various programming algorithms characterized in Chapter 4. Clearly the correction capability required to satisfy the target UBER constraints increases over time. As expected, from the reliability standpoint, the worst performance is provided by the ISPP-RV algorithm. This algorithm requires at the end of the life of the device a correction capability of 450 errors per page. This value would require a considerable hardware and performance overhead that leads to the conclusion that memory pages using the ISPP-RV algorithm will necessarily provide a reduced endurance. For this reason we selected as target maximum correction capability 88 errors per page corresponding to the requirement of the ISPP-SV algorithm at the end of life. Given the selected value of k and t the resulting code is designed over GF(2<sup>16</sup>) (i.e., m = 16).

Table 5.3: Correction capability required by the ECC to achieve a target UBER=1E-11 (Every element of the table reports the memory RBERs for the different programming algorithms (pattern independent) as characterized in Chapter 4, and the needed correction capability).

| Alg/progr. cycles | 1             | 100            | 1000           | 10000          | 100000            |

|-------------------|---------------|----------------|----------------|----------------|-------------------|

| ISPP-RV           | 1.000E-06 / 3 | 6.104E-05 / 11 | 3.052E-04 / 28 | 1.526E-03 / 88 | 9.0332 E-03 / 450 |

| ISPP-SV           | 1.000E-06 / 3 | 1.000E-06 / 3  | 2.747E-04 / 26 | 3.357E-04/29   | 1.000E-03 / 65    |

| ISPP-DV           | 1.000E-06 / 3 | 1.000E-06 / 3  | 3.052E-05 / 8  | 3.052E-05 / 8  | 9.155E-05 / 14    |

In the remaining of this section the ECC sub-system will be characterized to show the different trade-offs offered by its programmability. It is worth to mention here that our ECC implementation features a 8-bit parallelism to meet the I/O parallelism of the target flash, and a 8-bit parallelism of the Chien machine allowing 8 evaluations per clock cycle to speed-up the decoding process. Table 5.4 reports the area required for this block synthesized using Synopsys DesignCompiler with the STM-45nm [46] technology library. The full design works at 100MHz clock frequency.

Table 5.4: ECC encoder and decoder area footprint. Synthesis has been performed using the STM-45nm technology library.

|         | Area ( $\mu m^2$ ) |

|---------|--------------------|

| Encoder | 169931.76          |

| Decoder | 514398.40          |

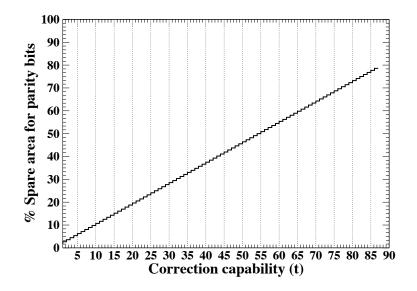

Let us start with the evaluation of the amount of redundancy (i.e., parity bits) introduced by the ECC. In the worst case (e.g., t = 88) the code requires to store  $m \cdot t = 16 \cdot 88 =$ 1408bits. This accounts for about 78.5% of the spare area available on our device that corresponds to 224B per page. ECC parity bits, are not the only extra information stored in a flash memory. High-level functions such as filesystem management and wear-leveling need to save considerable amount of information and when the spare are is not enough a certain amount of pages of the flash must be reserved, thus reducing the overall flash capacity. However, looking at Fig. 5.13, if reduced correction capability is required, either because the device is in the early stage of its life, or because a more reliable programming algorithm is applied, the spare area occupation can be reduced up to 74% (3.57% occupation for t = 3). This provides a high degree of freedom for the flash memory controller.

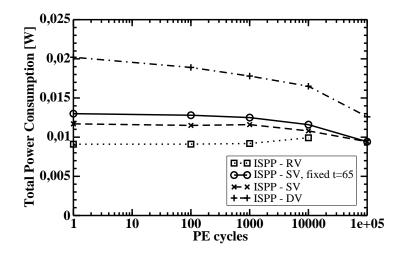

The choice of t also makes it possible to tune the ECC latency and its power consumption.

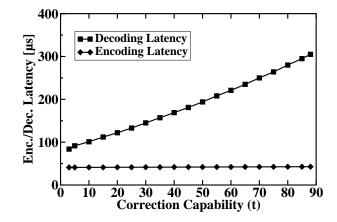

Fig. 5.14 shows that, carefully tuning the correction capability, the ECC subsystem can introduce a significant save in the decoding time compared to the worst case (t = 88). Simulations have been performed in the worst case conditions, i.e., t errors injected into the last bits of the page to make sure that the Chien machine has to evaluate the full page in order to find the corrupted bits. The encoding latency is instead almost constant regardless of the selected correction capability.

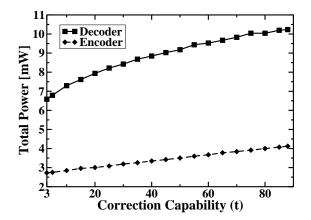

Similarly to the ECC latency also the ECC power consumption can be traded-off by carefully selecting the correction capability. Fig. 5.15 shows that, also in this case, we can reach up to  $\sim$ 33% of saving in the decoding power consumption when reducing the correction capability.

Figure 5.13: Percentage of spare area dedicated for storing parity bits as a function of the selected correction capability.

Figure 5.14: Worst case ECC encoding and decoding latency. Simulations have been performed at a clock frequency of 100MHz.

Figure 5.15: Worst case ECC power consumption.

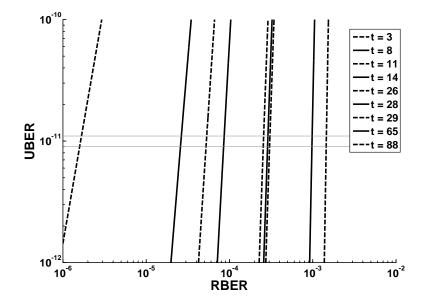

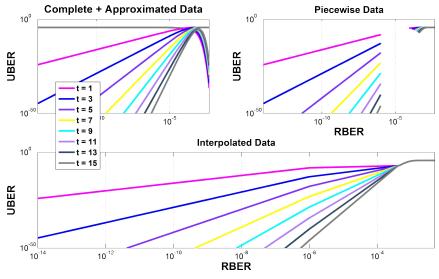

To conclude the characterization of the designed programmable ECC sub-system, Fig. 5.16 reports the relation between UBER and RBER for the selected correction mode obtained by plotting equation (5.10). The figure shows an additional degree of freedom the controller can achieve in which also the UBER can be tuned together with the other parameters.

Figure 5.16: RBER vs. UBER relationship for the selected code and selected correction modes.

### **SUMMARY**

This chapter proposed a BCH codec architectures and its related automatic generation framework which enables its code correction capability to be selected in a predefined range of values. Designing an ECC system whose correction capability can be then modified in-field has the potentiality to adapt the correction schema to the reliability requirements the flash encounters during its life-time, thus maximizing performance and reliability. Experimental results on a selected NAND flash memory architecture proved that the proposed solution reduces spare area usage, decoding time, and power dissipation whenever small correction capability can be selected. The whole design process was supported by the novel ADaptive ECC Automatic GEnerator (ADAGE) design environment. ADAGE is a fully customizable tool aimed at automatic generation of adaptable BCH architectures. ADAGE is able to automatically generate the VHDL code of the designed adaptable BCH-based architecture. Such a code can be thoroughly simulated, validated and synthesized on ASIC or FPGA.

| $g_{24}$                                                                                        | <b>g</b> 23                                                                                  | $g_{22}$                                                                                 | $g_{21}$                                                                             | $g_{20}$                                                                         | $g_{19}$                                                                      | $g_{18}$                                                                  | $g_{17}$                                                              | $g_{16}$                                                       | $g_{15}$                                                   | $g_{14}$                                               | <b>g</b> 13                                        | $g_{12}$                                        | $g_{11}$                                    | $g_{10}$                                | $g_9$                               | $g_8^8$                          | <b>g</b> 7                   | $g_6$                    | $g_5$                |                                                                                                                |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------|-------------------------------------------------|---------------------------------------------|-----------------------------------------|-------------------------------------|----------------------------------|------------------------------|--------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|

| 0x 0141AE126215097403F13F41BE936020FAA0D6D486AD40BE0BED62DC87C4D8CF945A4D2A804411217E82829127AD | 0x 0102924C5CEA2B43968EFF54D1E0FAB54DEBFDC54428EDAE6FE2EE724B79CBC072C19CEB766864091E5551A38 | 0x 01D6ECB0041A40258ADA46542DB3657CFA042227D7CAADD770809ACC680C2886C0EACDC8D81D34565F7FC | 0x 015E830624B4D708788177787CA2DC6C89F7558E799E84DD1027034F4DEC7476ADA565B11240FB4EE | 0x 01CA788668B1303E48C4A41BE62900685C4A42DB04E267A642AC82884176194501F076D19CF53 | 0x 01B54AFF801C5EBB55EA214ADCCB051347A16418268264264299431B25E5B7CE34F402D938 | 0x 016240D5F338473A9653892D4DDC334AEF9FE78E9B835C10D1C9106B14AA4AB4BD5CD4 | 0x 019755B57BEBA0DD4C284FE4B4F4549C194CA6E75E542322123EAB270447821712 | 0x 01BE62D0F7C4D16FCCDD3CE20D7998280B591702D452F3541A51DA955D8 | 0x 01E12C4539A437988318B8B0A756426E93CD5001031DCB5DC430A0C | 0x 01E59154D4757E35CBDCE8247F4686EACC2C96C8209D848BDCE | 0x 012E919C715C15310DA7103C0AB656C7FE330613197631D | 0x 018FB50FA2969CDC5EAFA1C24BD9E5AA92A2227EC668 | 0x 01E8B4BA11F717E75A1F5E0EC4FBCD65DA8FFF24 | 0x 018B24C1E935C04DC6BC73E0BDB98405C4EA | 0x 01D6634FC565E6012E441926C07B8D59 | 0x 01F28E94D9B550543AC42286CF418 | 0x 01E573FBB06E46A828C1C770C | 0x 018FBE36E3B716D8BCE32 | 0x 0163C68D766635253 | זמטור סיטי סריוריזמוטו לסולווטוווומו בעלובססרמ אונוו מור נסדובסלסוומווו8 וורעממכרווומו סנרוופ טו רסבווורנכוונס |

Table 5.5: Generator polynomial expressed with the corresponding hexadecimal string of coefficients

# Снартев

# **CROSS-LAYER OPTIMIZATION FRAMEWORK**

# Contents of this chapter

6.1 EF<sup>3</sup>S Framework

- 6.2 Cross-layer Optimized NAND flash access modes

- 6.3 Storage services at work

he goal of this thesis is to enhance the degree of run-time reconfigurability of an MLC NAND Flash controller through the provision of user-selectable differentiated memory access modes based on an adaptive ECC decoding structure (architecture-level adaptivity) combined with an adaptable memory programming circuitry (physical layer adaptivity).

After having considered the flexibility and the trade-offs in the physical layer and in the ECC sub-system in isolation, this thesis also aims at characterizing the tuning range achievable with such modes. Acting upon their parameters at the same time, the main purpose is to show unprecedented degrees of adaptivity to application requirements in the reliability/performance/power optimization space, thus identifying a set of differentiated access modes that can be configured in the memory controller.

For this purpose, an extensive modeling, simulation and implementation framework has been designed and implemented: EF<sup>3</sup>S [56]. EF<sup>3</sup>S is an an easy-to-use, highly configurable, and modular advanced EDA tool which aims at supporting the design of flash-

based systems. It offers the possibility of modeling: the physical NAND device, the memory controller, the NAND flash driver, the Flash File System (including wear leveling and garbage collection), and the application workloads. This framework enable an accurate quantification of the trade-offs between the quality metrics of NVMs accesses on a set of real-life work-loads and benchmark applications. EF3S has been set up to assess the analog and the digital parts of an MLC NAND flash memory sub-system in an homogeneous 45nm industrial technology substrate.

The chapter is organized as follows: Section 6.1 introduces the developed framework called EF<sup>3</sup>S. Sections 6.2 and 6.3 explores the trade-offs proposed by the cross-layer optimization in the NAND memory controller and shows the performance of the proposed system on a set of real-life applications, respectively.

# 6.1 EF<sup>3</sup>S Framework

EF<sup>3</sup>S enables designers to evaluate the NVM subsystem characteristics (e.g., power consumption, latency, performances, aging) resorting to both synthetic workloads and real traces automatically extracted from real applications.

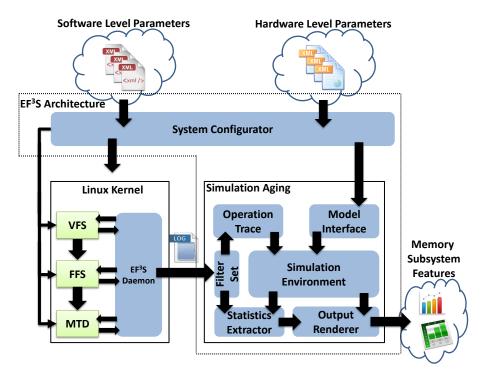

$EF^{3}S$  is designed for a Linux based environment featuring a Flash File System (FFS), the Linux Memory Technology Device (MTD), and operating system support for raw flash management, including wear leveling and garbage collection. The whole framework combines Linux scripts, C programs, and Matlab software modules. Figure 6.1 shows the  $EF^{3}S$  architecture.  $EF^{3}S$  comprises three main modules:

- *System Configurator*: the user interface in charge of collecting different design parameters to properly configure the target NVM subsystem;

- *EF<sup>3</sup>S daemon*, embedded in the Linux Kernel, in charge to monitor the target application workload profiling flash memory operations. Extracted data are then exploited by the Simulation Aging.

- *Simulation Aging*, that elaborates information provided by the System Configurator and the EF<sup>3</sup>S daemon, simulates the behavior of the target flash memory, and outputs the desired statistics. They include information about throughput, power consumptions, reliability, and aging of the considered system. To assist users in the design space exploration, Fig. 6.1 provides combined and synoptic views of the EF<sup>3</sup>S architecture.

Figure 6.1: EF<sup>3</sup>S Architecture

In the next section, the different modules composing EF<sup>3</sup>S will be analyzed in detail.

# 6.1.1 System Configurator

Designing a NVM subsystem requires the investigation of several design choices, whose characteristics must be specified to EF<sup>3</sup>S in order to carry out the desired simulations. The *System Configurator* is in charge of collecting these information items. NVM characteristics can be classified into *Hardware Level* and *Software Level* parameters. These design choices fully characterize the NVM subsystem and can be provided in input to the system configuration through a set of dedicated configuration files. The remainder of this section will detail each specific configuration item available in EF<sup>3</sup>S.

**Software Level parameters** Software Level design parameters include: the target application and workload, the selected Flash File System, the Wear Leveling algorithm, and the Garbage Collection strategy.

The workload, i.e., the system application interaction with the NVM subsystem, is one of the most critical elements to properly evaluate specific software applications. Two main parameters allow the designer to configure the target workload:

- *Workload Type*. The user may select a set of internally generated workloads produced resorting to the FileBench software suite [7, 134], or resort to a custom workload generated profiling the execution of a custom software application reflecting the specific mission of the simulated system.

- *Workload Running Time*. It is the time for which the workload is executed and profiled. It has to be large enough to perform a significant amount of operations on the system thus collecting enough information about the system's behavior.

In addition, the System Configurator also enables to select among the following system's design choices:

- Flash File System (FFS). The selected Flash File System and its configuration parameters strongly affect the NVM performance. EF<sup>3</sup>S is designed to enable simulations using different Linux based Flash Filesystems including YAFFS2 (Yet Another Flash File System 2), UBIFS (UBI File System) [13] or JFFS2 (Journaling Flash File System 2) [12].

- *Garbage Collection* and *Wear Leveling* algorithms can be switched among a selection of available strategies that depend on the selected filesystem.

- *Caches*. In the NVM Subsystem Software Stack several level of caches at the Virtual File System (VFS) and Flash File System (FFS) level are used. These caches can be enabled or disabled to reflect the desired system configuration.

Software Level parameters are used by the System Configurator to properly instrument the Linux Kernel as well.

**Hardware Level parameters** At the Hardware Level, EF<sup>3</sup>S enables the user to configure the NVM subsystem acting on the flash memory, the ECC and the flash interconnection type.

The target flash memory can be configured according to the following parameters:

- *Logical Parameters*. Include page size, block size (or pages per block), device partition size (or blocks per partitions) and total size (or number of device partitions).

- *Operational Parameters*, which may be found on the device datasheet. Such parameters include:

- device clock frequency;

- read/program/erase elementary physical operations specifications (e.g., program verify algorithm [144]);

- elementary operation timing and power consumptions, with the possibility of defining time or aging dependent values;

- *Bare Memory Reliability Model* to be used for reliability status estimation of the memory. Raw Bit Error Rate (RBER) may be assumed as a measure of the reliability status of the bare flash memory as widely presented in Chapter 3.

All provided parameters may be time or memory aging dependent. An accurate formalism has been introduced to allow designers to specify parameters according to either program/erase cycles or time intervals (e.g., flash operation latencies strongly depend on the aging of the memory).

Together with the target flash memory, the ECC subsystem can be also fully configured according to the following parameters:

- ECC family, chosen between BCH, LDPC, Reed Solomon (RS)[40] and Product Codes[139];

- *correction capability* or *target reliability*, measured as UBER (Uncorrectable Bit Error Rate) value, i.e., the error rate after applying ECC [107];

- message length, with the possibility to apply the code to portions of a page;

- *adaptability*, i.e., a fixed correction capability ECC schema versus a variable one can be chosen [59, 144];

- encoding/decoding *latency and power consumptions* or *implementation technology*, in terms of technology node used to synthesize the ECC, and possibly running clock frequency upper limit.

Finally, the Interconnection System is characterized by the Flash *Interconnection Type* with the rest of the system, i.e., the particular topology of interconnection and protocol.

# 6.1.2 EF<sup>3</sup>S daemon

The EF<sup>3</sup>S daemon interacts with the basic Linux software modules required to deal with flash based storage systems. In particular it filters and records exchanged data between FFS and MTD in order to collect flash memory operation traces.

For sake of comprehension, it is worth mentioning here that the MTD [94] is a driver that provides a uniform interface to different (raw) flash chips. The MTD, if properly instrumented, emulates the presence of a raw NAND flash chip, providing thus the capability to run even when no physical memory devices are available.

In particular, EF<sup>3</sup>S daemon is instrumented to produce a log file of all flash operations required by the target application workload. This log file is pivotal to Simulation Aging to analyze the system's behavior and provide output statistics.

### 6.1.3 Simulation Aging

The Simulation Aging is responsible for simulating the configured NVM subsystem.

The *Filter Set* is the main interface of the Simulation Aging with the EF<sup>3</sup>S daemon. It contains a set of filters, based on regular expressions, which are applied to the log file produced by the EF<sup>3</sup>S daemon during the execution of the target application. The log file must be properly filtered before performing the required aging simulations according to user requirements. After filtering, a sequence of operations (hereinafter referred to as operation trace) is produced. Each operation is described according to a custom formalism:

## $\langle time \rangle \langle r/w(/e) \rangle \langle page(/block) address \rangle$

where:  $\langle time \rangle$  is the time when the operation was issued;  $\langle r/w(/e) \rangle$  represents the operation type (*r* stands for read, *w* for write, *e* for erase);  $\langle page(/block) address \rangle$  is the operation target page or block address.

The *Model Interface* acts as an interface between the System Configurator and the Simulation Environment. It elaborates the hardware specific configuration parameters in order to setup the simulation of the computed operation traces. In particular, this module evaluates the piecewise functions defining the Flash Operational Parameters: the right subinterval is identified and expressions are evaluated. The model interface also evaluates the reliability model equations. Finally, the Model Interface module sets the ECC characteristics and correction capability required to satisfy specifications and

computes the ECC run-time parameters such as encoding/decoding latencies and power, resorting to previously characterized ECC schema.

*Simulation Environment* is the core module of the Simulation Aging. Here all data are combined. The operations to simulate the memory aging are read from the operation trace. Each operation is emulated using the parameters that are concurrently updated by the Model Interface, according to the status (i.e., aging) of the simulated flash memory. At the same time, the Simulator Environment estimates the relevant NVM subsystem features (e.g., average operation latency and throughput, average power and energy per operation, and aging of the pages) that are then provided in output. Of course, produced output accuracy stems from the input models and data accuracy.

The *Statistics Extractor* works in parallel to the Simulation Environment. By solely analyzing the input operation traces, this module extracts statistics about the Flash memory usage, like number of read, write or erase operations per page or block, write/read intensity (ratio between read and write operations) and total number of operations.

Finally, the *Output Renderer* manages the data produced by the Simulator Environment and the Statistics Extractor, to offer a meaningful and synoptic vision of the reliability, performance and behavior of the simulated system by a means of plots, graphs and tables which are automatically generated.

In the next section, EF<sup>3</sup>S is employed to enable an accurate quantification of the trade-offs between the quality metrics of NVMs accesses on a set of real-life work-loads and benchmark applications, showing the valuable results of the proposed SONVM architecture.

### 6.2 Cross-layer Optimized NAND flash access modes

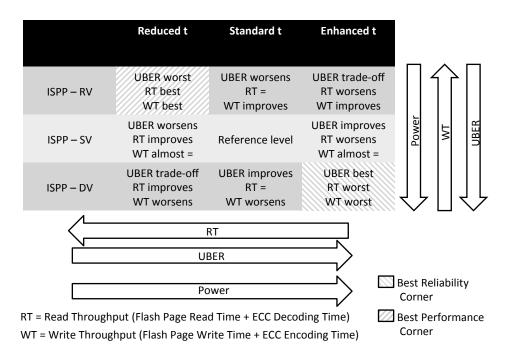

The EF<sup>3</sup>S framework enables an accurate quantification of the trade-offs between the quality metrics of NVMs accesses on a set of real-life work-loads and benchmark applications. Fig. 6.2 provides an overview of how the NAND flash sub-system reacts when selecting different programming algorithms and ECC correction capabilities. Three main parameters of the flash are considered in Fig. 6.2:

- the UBER of the flash;

- the read throughput (RT), i.e., the number of page read requests per second the system is able to serve;

111

• the write throughput (WT), i.e., the number of write requests per second the system is able to serve.

Figure 6.2: Set of access modes provided when tuning the programming algorithm and the ECC correction capability in a cross-layer adaptation framework.

If we consider the ISPP-SV programming algorithm with an ECC designed for UBER of 1E-11 as a reference operating point, the following behaviors can be foreseen:

- UBER worsens when lower values of *t*, or programming algorithms with reduced verifications are used.

- WT is mainly affected by the programming algorithm. As pointed out in Fig. 5.14 the ECC encoding time is almost constant regardless the selected correction capability.

- RT is mainly affected by the selected ECC correction capability that directly affects the ECC decoding time (see Fig. 5.14). It increases if a lower *t* is used.

- The combination of reduced *t* and ISPP-RV represents the best performance corner, but offers the worst reliability.

- The combination of increased *t* and ISPP-DV represents the best reliability corner, but offers the worst performances.

- In the bottom-left and upper-right access modes in the table, the UBER stems from a trade-off between correction strength and the chosen algorithm

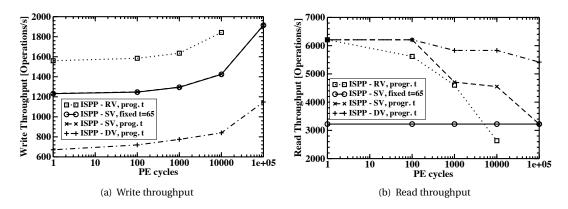

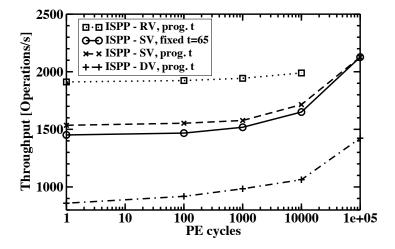

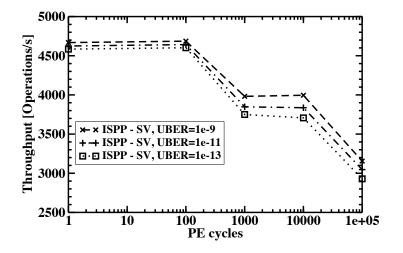

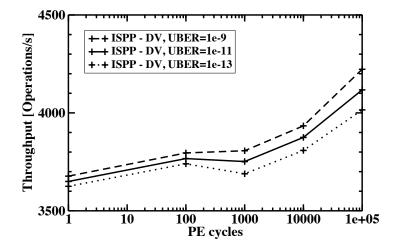

An example of these trends can be appreciated in Fig. 6.4. It shows how the modulation effect of RT and WT (for a target UBER= $10^{-11}$ ), achievable by changing the programming algorithm selection and ECC correction strength, varies over time along with memory aging. The correction capability of the ECC is adapted as aging increases according to Table 3 to preserve the target UBER in spite of memory aging. For the sake of comparison, the figure shows the performances of a non-adaptive controller using the ISPP-SV programming algorithm and a fixed correction capability *t* = 65 required to meet the target UBER at the end of the memory lifetime.

|            |           | PE cycles |          |          |          |          |  |  |  |

|------------|-----------|-----------|----------|----------|----------|----------|--|--|--|

| UBER       | ISPP alg. | 1         | $10^{2}$ | $10^{3}$ | $10^{4}$ | $10^{5}$ |  |  |  |

|            | RV        | 1         | 9        | 24       | 80       | >88      |  |  |  |

| $10^{-9}$  | SV        | 1         | 1        | 22       | 25       | 58       |  |  |  |

|            | DV        | 1         | 1        | 6        | 6        | 11       |  |  |  |

|            | RV        | 3         | 11       | 28       | 88       | 450      |  |  |  |

| 10-11      | SV        | 3         | 3        | 26       | 29       | 65       |  |  |  |

|            | DV        | 3         | 3        | 8        | 8        | 14       |  |  |  |

|            | RV        | 4         | 13       | 31       | >88      | >88      |  |  |  |

| $10^{-13}$ | SV        | 4         | 4        | 30       | 33       | 70       |  |  |  |

|            | DV        | 4         | 4        | 10       | 10       | 17       |  |  |  |

Figure 6.3: Adaptation of the ECC correction capability to the flash aging for different programming algorithms and target UBER

Fig. 6.4 (a) clearly shows that, acting on the programming algorithm, we can modify the write performances of the flash with 30% improvement obtained with *ISPP-RV prog. t* used instead of *ISPP-SV fixed t*. Moreover WT modulation capability is preserved over memory cycling. The non-adaptive and the adaptive ISPP-SV solutions are almost overlapped because encoding latencies are barely affected by the ECC correction strength. Fig. 6.4 (b), instead, shows that we can tune the RT of the system by using ISPP-DV as opposed to ISPP-RV. In these cases the RT can be improved by 36% or degraded by 59% calculated at program/erase (PE) cycle 10k, respectively, and compared to the reference adaptive ISPP-SV solution. Of course, the RT degradation of ISPP-RV is the price to pay for its WT improvement. The comparison of the *ISPP-SV prog. t* curve with the baseline

Figure 6.4: WT and RT comparison among different configurations of the controller for a target  $UBER=10^{-11}$

*ISPP-SV fixed t* curve shows that tuning the ECC correction capability over the life of the flash enables a significant improvement of the RT with no penalties on WT.

Fig. 6.4 (b) also shows that, in the early stage of the memory life, the modulation capability of RT is marginal. The reason lies in the similar RBER figures of programming algorithms in fresh devices. On one hand this means that RT boost with respect to the reference case will be achieved only after hundreds PE cycles. On the other hand, this also means that in fresh devices WT can be broadly modulated at marginal RT penalty.

Overall, Fig. 6.4 shows a usage model of the access modes: the correction capability is used to preserve a target UBER over flash life, whereas the programming algorithm is used to trade WT with the RT. At a given PE cycle, a higher RT can be achieved by switching the programming algorithm (i.e., from *ISPP-SV prog. t* to *ISPP-DV prog. t*), and the ECC correction strength (since ISPP-DV needs a lower *t* to preserve the target UBER with respect to ISPP-SV). The WT can be traded-off similarly. Finally, Fig. 6.4 (b) clearly shows that for most of memory life, the non-adaptive approach results in a significant device under-utilization from the RT standpoint.

Other usage models are clearly feasible. For instance, switching from *ISPP-SV prog. t* to *ISPP-DV prog. t*, while keeping *t* unchanged, results into a minimization of the UBER figure beyond  $10^{-11}$  leaving RT unaltered at the cost of WT. Similarly, a switch to *ISPP-RV progr. t* achieves a WT improvement. If at the same time we decrease *t* the UBER is largely degraded while improving RT. Otherwise with a constant *t* the UBER is degraded to lower extent but RT is unaltered.

Finally, the upper-left access mode in Fig. 6.2 can be used in those cases where an ultra-low power operating mode is required while, at the same time, largely degrading UBER and therefore application-perceived reliability are accepted. This could be the case of a mobile system which is about to drain its battery: the user will then decide whether to keep using it in spite of the reduced quality of service or to power it off. In contrast, the lower-right access mode in Fig. 6.2 provides the best achievable reliability at the cost of increased power consumption and largely degraded performance.

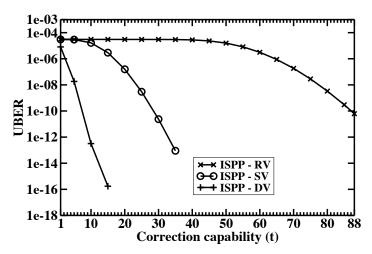

Fig. 6.5 summarizes the way UBER can be tuned by selecting different ECC correction capability or programming algorithm. Values in the figure are computed considering the RBER of the flash at 10,000 PE cycles, i.e., quite late in the flash lifetime. Similarly to the performances, Fig. 6.5 shows that we can achieve important trade-offs in the reliability of the access mode, with the possibility of varying the UBER of the NVM system of several orders of magnitude.

Figure 6.5: Trade-off on the storage reliability by selecting different programming algorithms and different ECC correction capability. UBER is computed at 10,000 PE cycles of the flash.

In order to properly exploit the advantages provided by the proposed adaptive NAND Flash controller, a strategy to decide which memory access mode to use at run-time is of course mandatory. While a complete discussion of this topic is out of the scope of this thesis, a set of preliminary insights can be provided here. There are essentially two factors that must be considered, at run-time, to properly select the available tuning knobs:

1. the application reliability/performance/power requirements and

#### 2. the memory aging.

The first factor is static for a given application or for selected portions of data of an application. Even if not straightforward, applications can be carefully profiled in order to assign different reliability/performance/power requirements to the different set of data they manage. The application profile can be then exploited to choose the best storage service for each type of information. We envision in this thesis to split the flash memory into different partitions providing different services based on Fig. 6.2, according to the requirements of the application to be executed on the target system. Each application can be then instrumented in order to redirect its memory access to the partition providing the access mode that is more suited for the specific data that is going to be accessed. A single application can therefore benefit from data stored in different partitions with different services in order to optimize the overall system performance.

While for a given access mode the selected programming algorithm is in general constant over the memory life-time, the ECC correction capability must be continuously tuned to compensate for the memory aging. Several models in the literature correlate the RBER of a page to the number of performed PE cycles [130]. If this information is constantly tracked during flash operations it can be exploited to adapt the ECC correction capability according to the selected aging model. In this context, one of the most efficient and easy solutions is to demand this operation to the Flash Translation Layer (FTL) or to the File System. At each programming operation the PE cycles of the pages are incremented and stored together with other file system related information. This value can then be exploited at run-time to select the best correction capability every time the page is programmed.

#### 6.3 Storage services at work

To appreciate the benefits of differentiated flash access modes on the execution of a set of real applications, we constructed a simulation environment running under the Linux Operating System. User applications communicate with the Linux Virtual File System (VFS) that decouples the application from the specific file system. YAFFS (Yet Another Flash File System) [15] is the selected flash memory file system. YAFFS is an open-source, fully documented flash memory file system whose source code can be easily modified and instrumented to perform required simulations. Finally, the NAND Driver or Memory Technology Device (MTD) communicates with the flash memory controller in charge of performing the requested operations on the flash device. The MTD has been instrumented to emulate operations on a NAND flash memory with 4,096 blocks of 128 pages, with a page size of 4 kB. YAFFS has been also instrumented to trace the list of operations performed through the MTD. Read, write and erase operations have been traced. The log essentially contains information about the sequence of operations, the target page address and the timing. To obtain unbiased measurements of the flash performances both VFS and YAFFS caches have been disabled.

Several file system benchmarks are available on the Internet (e.g. IOzone [8], Postmark [81], SPEC benchmarks [11], Filebench [134], etc.). We selected the Filebench benchmark for our analysis. It is an open source File System benchmark originally developed by Sun Microsystem and now by FSL (File systems and Storage Lab) group of the Computer Sciences Department of the Stony Brook University, NY (USA). It provides a large variety of behaviors, also named *personalities*, specified using the Workload Model Language (WML) [7]. They either perform simple file I/O operations, or emulate complex I/O activities.

Among the available personalities, we selected three benchmark applications:

- varmail: has different threads performing create-append-sync, read-append-sync, read and delete operations on the files (representing emails) contained in a single directory (workload similar to Postmark);

- *webserver*: opens, reads and closes multiple files in a directory tree while appending data in log file;

- *videoserver*: reads a file set containing videos that are actively served, and writes another file set containing videos that are available but currently inactive.

One of the main characteristic that differentiate the three selected benchmarks is the ratio between the number of read operations (*#R*) and the number of write operations (*#W*). This is a critical parameter that influences the type of access mode required by the application to maximize its performance. Table 6.1 summarizes this information. *varmail* is a typical example of write intensive application requiring fast programming of the flash. On the contrary, *videoserver* is a read intensive application requiring fast read access to the data stored in flash. Finally, *webserver* is between the other two benchmarks and performs a more equalized set of read and write operations to the flash.

| Personality | #R/#W    |

|-------------|----------|

| varmail     | 32.46%   |

| webserver   | 153.41%  |

| videoserver | 1084.70% |

Table 6.1: #R/#W ratios of different Filebench personalities

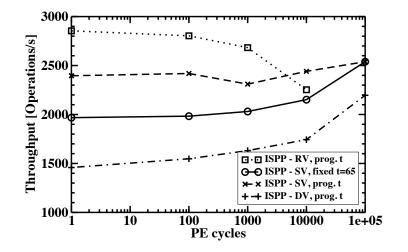

Figure 6.6: Varmail throughput for a fixed UBER= $10^{-11}$

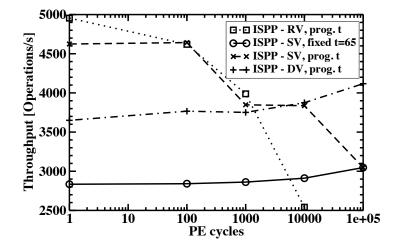

Fig. 6.6,6.7 and 6.8 show the opportunities the controller programmability provides to the three applications for a target UBER= $10^{-11}$ . All figures report the overall application throughput, i.e., number of operations (read or program operations) performed on the flash per unit of time. Comparison is again performed with a non-adaptive controller using the ISPP-SV programming algorithm and fixed ECC with *t*=65. Erase operations have been neglected in the calculations of the throughput. In fact, the analysis of the benchmark traces reports that the number of erase operations is far lower than the number of program operations).

Looking at Fig. 6.6, that reports the throughput of *varmail*, it is evident that *ISPP-RV prog. t* enables a significant improvement of the overall performances of the application. This improvement comes however with a reduced endurance of the flash due to the high

Figure 6.7: Webserver throughput fixed UBER=10<sup>-11</sup>

RBER introduced by this programming algorithm when the number of PE cycles exceeds 10,000.

If we move, instead, to the opposite application profile represented by the read intensive *videoserver* reported in Fig. 6.8 we can notice an interesting result. Looking at the overall flash lifetime, the *ISPP-SV prog. t* seems the best option for this application even if looking at Fig. 6.4 we could expect better performances from *ISPP-DV prog. t*. The main motivation for this behavior is that the flash programming time is dominant over the flash read time and therefore it negatively influences the overall application performances. This opens new opportunities for the proposed controller. In fact, Fig. 6.8 suggests that not only the ECC correction capability must be adapted to compensate for page aging. In this specific application profile, the ISPP-DV can be selected when the flash reaches more then 10,000 PE cycles to sustain the overall performance and reliability level.

The last situation represented by *webserver* (Fig. 6.7) obviously provides an intermediate behavior. In this situation *ISPP-DV prog. t* reduces the overall performances and is therefore not a good choice for the application. However, both *ISPP-SV prog. t* and *ISPP-RV prog. t* introduce significant performance improvements.

Figure 6.8: Videoserver throughput fixed UBER= $10^{-11}$

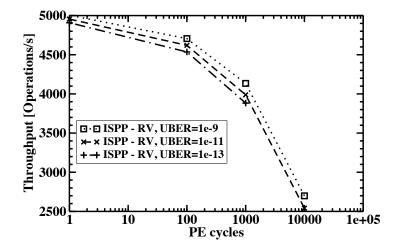

The analysis performed so far highlights how the proposed flash memory controller improves the performance of selected applications when mapped to dedicated access modes. The same programmability can be also exploited to provide access modes with different reliability levels as reported in Fig. 6.9, 6.10, and 6.11 for the *videoserver* application. In this comparison we considered a standard reliability service (UBER= $10^{-11}$ ), an enhanced reliability service (UBER= $10^{-13}$ ) and a reduced reliability service (UBER= $10^{-9}$ ).