VLSI decoding architectures: flexibility, robustness and performance

Carlo Condo Advisors: Guido Masera, Amer Baghdadi

February 18, 2014

# Contents

| 1        | Intr | oducti  | ion                                                     | 17        |

|----------|------|---------|---------------------------------------------------------|-----------|

|          | 1.1  | Motiva  | ation                                                   | 18        |

|          | 1.2  | Outlin  | e and contributions                                     | 20        |

| <b>2</b> | LD   | PC and  | d turbo code decoding                                   | <b>25</b> |

|          | 2.1  | LDPC    | and turbo codes                                         | 26        |

|          |      | 2.1.1   | Turbo codes                                             | 26        |

|          |      | 2.1.2   | LDPC codes                                              | 27        |

|          | 2.2  | LDPC    | and turbo code decoding algorithms                      | 29        |

|          |      | 2.2.1   | Turbo codes decoding algorithm                          | 29        |

|          |      | 2.2.2   | LDPC codes decoding algorithm                           | 30        |

|          | 2.3  | LDPC    | and turbo code decoders                                 | 33        |

|          |      | 2.3.1   | Turbo code decoders                                     | 33        |

|          |      | 2.3.2   | LDPC code decoders                                      | 34        |

|          |      | 2.3.3   | Turbo/LDPC decoders                                     | 35        |

| 3        | Flex | xible a | rchitectures for channel decoding                       | 37        |

|          | 3.1  | Topolo  | ogies for NoC-based channel decoding                    | 38        |

|          |      | 3.1.1   | NoC architecture for channel decoding                   | 39        |

|          |      | 3.1.2   | Simulation tool for NoC analysis                        | 42        |

|          |      | 3.1.3   | Analysis of NoCs for LDPC code decoding                 | 42        |

|          |      | 3.1.4   | Analysis of NoCs for turbo and LDPC code joint decoding | 43        |

|          | 3.2  | NoC-b   | based turbo/LDPC decoder architecture                   | 45        |

|          |      | 3.2.1   | LDPC decoding core                                      | 45        |

|          |      | 3.2.2   | Turbo decoding core                                     | 46        |

|          |      | 3.2.3   | Decoder synthesis and comparison                        | 46        |

# CONTENTS

|                                                  | 3.3                                                                                       | Recon                                                                                                     | figuration of NoC-based channel decoders              | 48                                                                                                                                                                                  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                                                                                           | 3.3.1                                                                                                     | Decoder Reconfiguration                               | 48                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.3.2                                                                                                     | Reconfiguration: cases and examples                   | 53                                                                                                                                                                                  |

|                                                  | 3.4                                                                                       | VLSI                                                                                                      | implementation of a reconfigurable turbo/LDPC decoder | 59                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.4.1                                                                                                     | Decoding Cores                                        | 59                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.4.2                                                                                                     | Supported Standards                                   | 65                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.4.3                                                                                                     | Implementation Results                                | 67                                                                                                                                                                                  |

|                                                  | 3.5                                                                                       | Joint a                                                                                                   | application and communication NoC simulator           | 73                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.5.1                                                                                                     | Proposed simulation environment                       | 74                                                                                                                                                                                  |

|                                                  | 3.6                                                                                       | Power                                                                                                     | reduction methods for NoC-based channel decoders      | 79                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.6.1                                                                                                     | NoC-based decoding: practical issues                  | 79                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.6.2                                                                                                     | Traffic reduction and optimization                    | 85                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.6.3                                                                                                     | Performance results                                   | 88                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.6.4                                                                                                     | Hardware architecture                                 | 93                                                                                                                                                                                  |

|                                                  |                                                                                           | 3.6.5                                                                                                     | Implementation                                        | 96                                                                                                                                                                                  |

| 4 Early stopping of iterations for LDPC decoding |                                                                                           | oping of iterations for LDPC decoding                                                                     | 101                                                   |                                                                                                                                                                                     |

|                                                  |                                                                                           |                                                                                                           |                                                       |                                                                                                                                                                                     |

|                                                  | 4.1                                                                                       | Early                                                                                                     | stopping criteria                                     | 102                                                                                                                                                                                 |

|                                                  | 4.1<br>4.2                                                                                |                                                                                                           | stopping criteria                                     |                                                                                                                                                                                     |

|                                                  |                                                                                           | Multi-                                                                                                    |                                                       | 103                                                                                                                                                                                 |

|                                                  | 4.2                                                                                       | Multi-<br>MSES                                                                                            | Standard Early Stopping Criterion                     | 103                                                                                                                                                                                 |

| 5                                                | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                             | Multi-<br>MSES<br>MSES                                                                                    | Standard Early Stopping Criterion                     | 103<br>107                                                                                                                                                                          |

| 5                                                | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                             | Multi-<br>MSES<br>MSES<br>or resi                                                                         | Standard Early Stopping Criterion                     | <ol> <li>103</li> <li>107</li> <li>110</li> <li>115</li> </ol>                                                                                                                      |

| 5                                                | <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>Erre</li></ul>                                | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ                                                                | Standard Early Stopping Criterion                     | <ol> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> </ol>                                                                                                         |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> </ul>              | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ                                                                | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> </ul>                                                                                            |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> </ul>              | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error                                                       | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> </ul>                                                                               |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> </ul>              | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error<br>5.2.1                                              | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> <li>117</li> </ul>                                                                  |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> </ul>              | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error<br>5.2.1<br>5.2.2                                     | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> <li>117</li> <li>118</li> </ul>                                                     |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> </ul>              | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                   | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> <li>117</li> <li>118</li> <li>119</li> </ul>                                        |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> <li>5.2</li> </ul> | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                   | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> <li>118</li> <li>119</li> <li>120</li> </ul>                                        |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> <li>5.2</li> </ul> | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Unequ          | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> <li>117</li> <li>118</li> <li>119</li> <li>120</li> <li>120</li> </ul>              |

| 5                                                | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Erre</li> <li>5.1</li> <li>5.2</li> </ul> | Multi-<br>MSES<br>MSES<br>or resi<br>Unequ<br>Error<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Unequ<br>5.3.1 | Standard Early Stopping Criterion                     | <ul> <li>103</li> <li>107</li> <li>110</li> <li>115</li> <li>116</li> <li>116</li> <li>117</li> <li>117</li> <li>118</li> <li>119</li> <li>120</li> <li>120</li> <li>121</li> </ul> |

|   | 5.4 | A prac   | tical case of study                           | 122 |

|---|-----|----------|-----------------------------------------------|-----|

|   | 5.5 | Hardwa   | are structure, implementation and comparisons | 128 |

| 6 | Cha | annel co | oding for deep space communications           | 133 |

|   | 6.1 | Concat   | enation of turbo and LDPC codes               | 134 |

|   |     | 6.1.1    | Proposed FEC scheme                           | 134 |

|   |     | 6.1.2    | Simulations and performance comparisons       | 135 |

|   | 6.2 | Unified  | decoder for concatenated turbo and LDPC codes | 142 |

|   |     | 6.2.1    | Unified LDPC/turbo decoding architecture      | 142 |

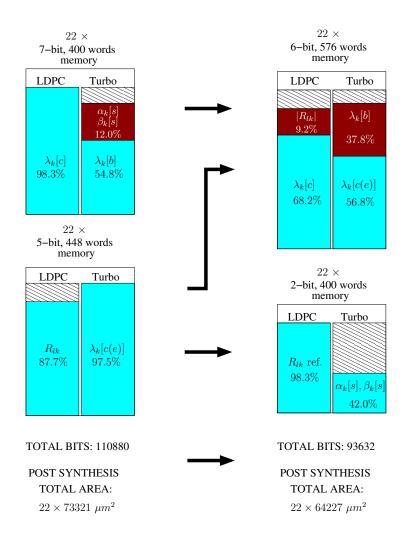

|   |     | 6.2.2    | Memory                                        | 144 |

|   |     | 6.2.3    | Implementation                                | 148 |

| 7 | Add | litional | contributions and conclusions                 | 151 |

|   | 7.1 | Additio  | onal contributions                            | 151 |

|   | 7.2 | Conclu   | sion and future perspectives                  | 151 |

# CONTENTS

# List of Figures

| 2.1  | Turbo code encoder                                                                                               | 26 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Turbo code trellis                                                                                               | 27 |

| 2.3  | LDPC code $\mathbf{H}$ matrix and Tanner graph                                                                   | 28 |

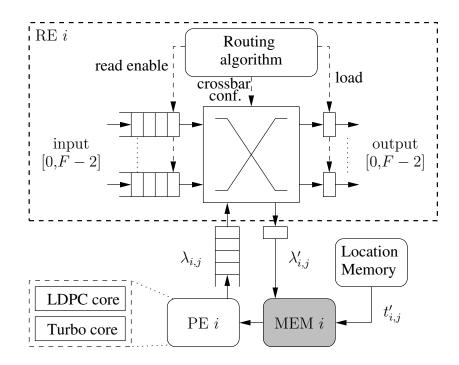

| 3.1  | Node structure                                                                                                   | 40 |

| 3.2  | LDPC decoding core                                                                                               | 45 |

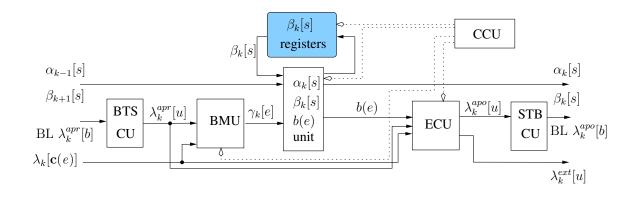

| 3.3  | Turbo decoding core (SISO)                                                                                       | 46 |

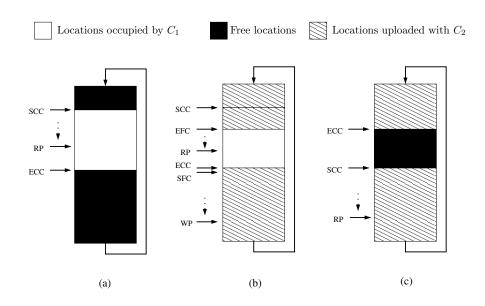

| 3.4  | Memory reconfiguration process: (a) Decoding of $C_1$ ; (b) Upload of reconfiguration                            |    |

|      | data required for $C_2$ (phases $\Phi_1$ to $\Phi_3$ and $\Phi_5$ ); (c) First iteration of $C_2$ and concurrent |    |

|      | upload of reconfiguration data $(\Phi_4)$                                                                        | 49 |

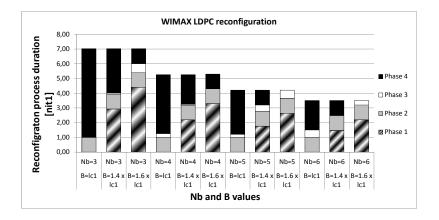

| 3.5  | WiMAX LDPC reconfiguration case                                                                                  | 54 |

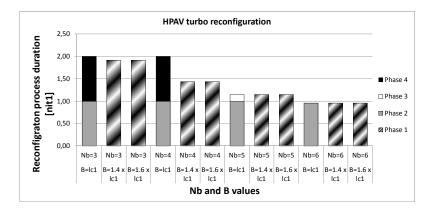

| 3.6  | HPAV turbo reconfiguration case                                                                                  | 54 |

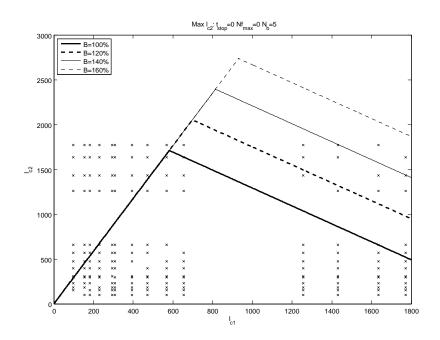

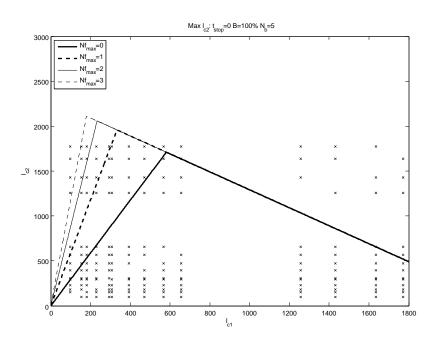

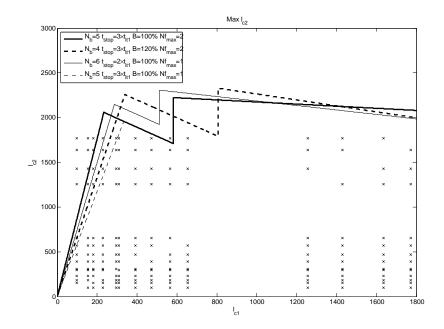

| 3.7  | Maximum $l_{c2}$ plot with varying B                                                                             | 55 |

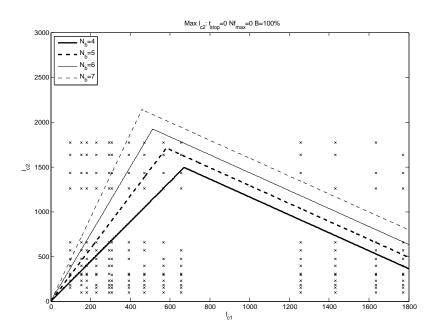

| 3.8  | Maximum $l_{c2}$ plot with varying $N_b$                                                                         | 55 |

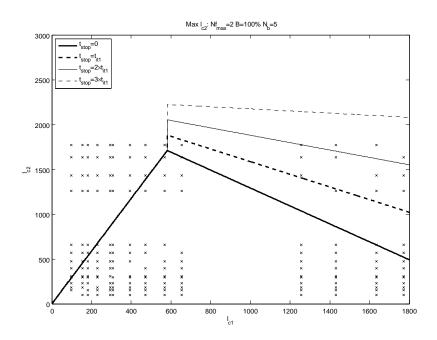

| 3.9  | Maximum $l_{c2}$ plot with varying $t_{stop}$                                                                    | 56 |

| 3.10 | Maximum $l_{c2}$ plot with varying $Nf_{max}$                                                                    | 56 |

| 3.11 | Maximum $l_{c2}$ plot, different solutions                                                                       | 57 |

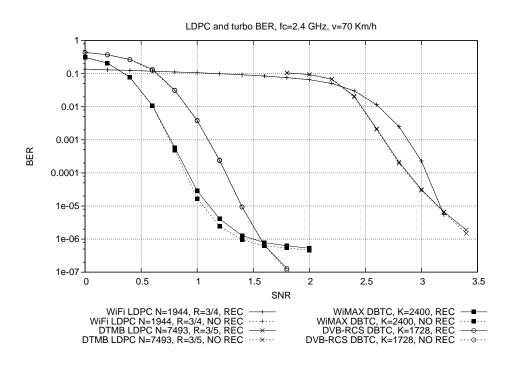

| 3.12 | LDPC and turbo BER with and without reconfiguration loss, AWGN channel, BPSK                                     |    |

|      | modulation                                                                                                       | 58 |

| 3.13 | Memory organization, WiMAX maximum usage percentages                                                             | 60 |

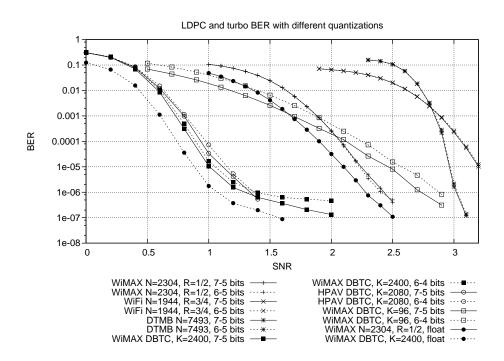

| 3.14 | LDPC and turbo BER with quantization change, AWGN channel, BPSK modulation                                       | 61 |

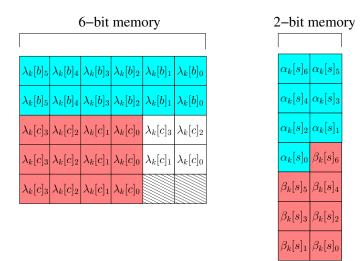

| 3.15 | Turbo mode in-depth memory organization                                                                          | 61 |

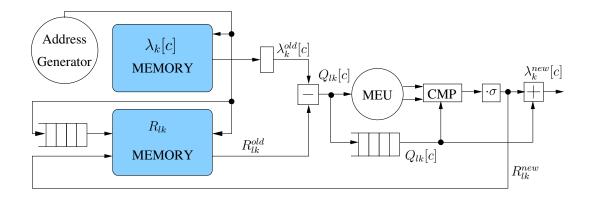

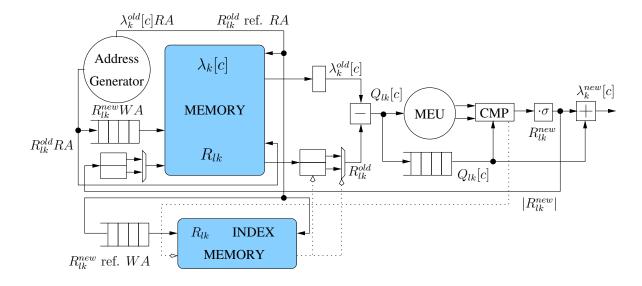

| 3.16 | LDPC decoding core                                                                                               | 62 |

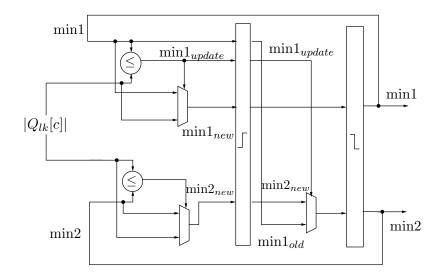

| 3.17 | Minimum Extraction Unit                                                                                          | 63 |

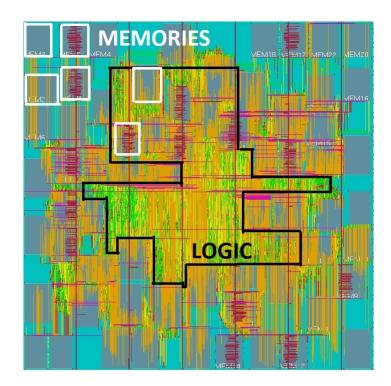

| 3.18 | Implementation A layout screenshot                                                                               | 69 |

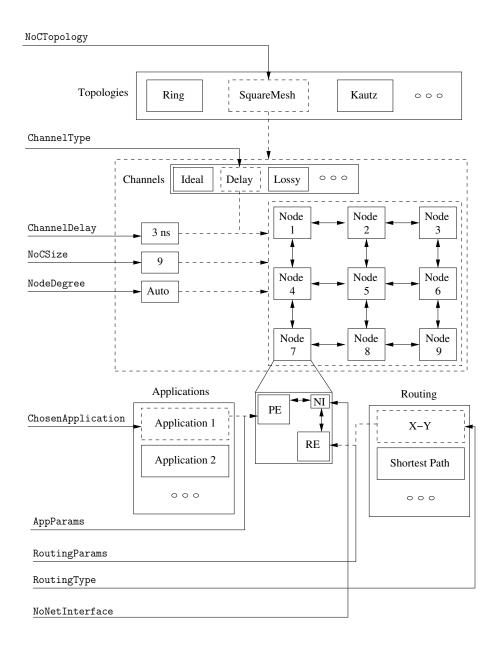

| 3.19 | JANoCS network definition via parameters                                                                         | 76 |

### LIST OF FIGURES

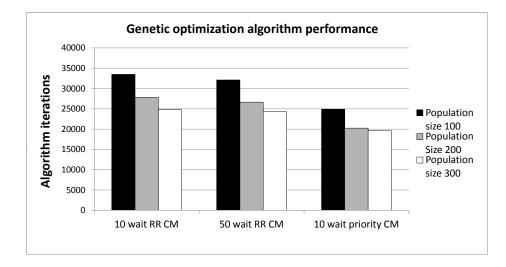

| 3.20 | Performance of genetic algorithm based barrel construction                              | 77  |

|------|-----------------------------------------------------------------------------------------|-----|

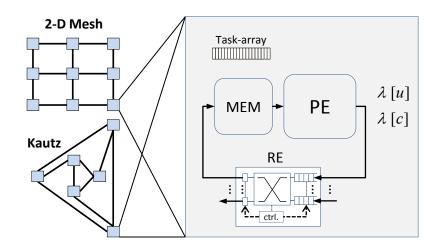

| 3.21 | NoC-based parallel decoder structure                                                    |     |

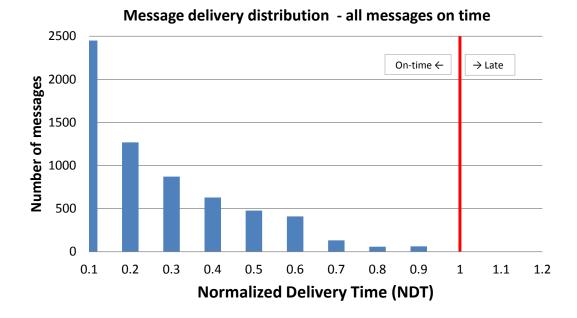

| 3.22 | 2 Message normalized delivery time distribution - all messages reach the destination on |     |

|      | time                                                                                    | 83  |

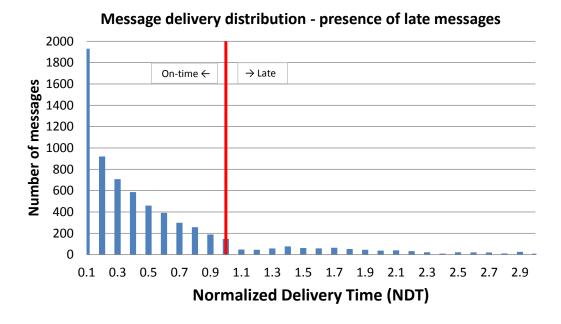

| 3.23 | Message normalized delivery time distribution - some messages do not reach the desti-   |     |

|      | nation on time                                                                          | 84  |

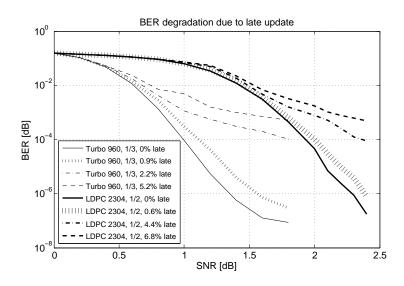

| 3.24 | BER degradation due to late information update                                          | 84  |

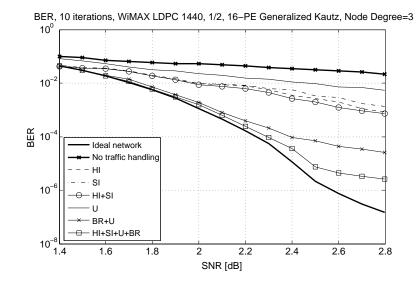

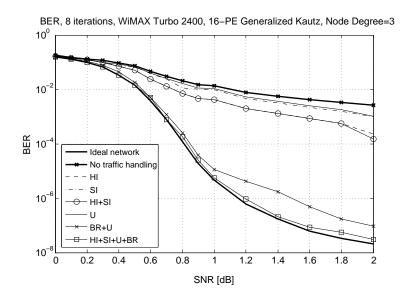

| 3.25 | Impact of the proposed techniques and their combinations - LDPC codes                   | 89  |

| 3.26 | Impact of the proposed techniques and their combinations - turbo codes                  | 90  |

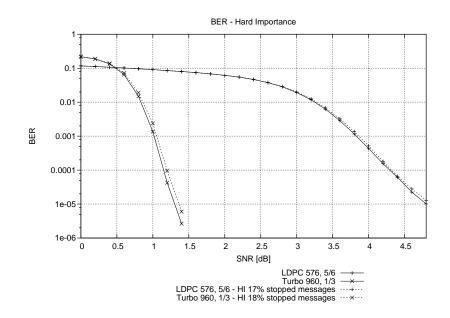

| 3.27 | Impact of HI on BER                                                                     | 90  |

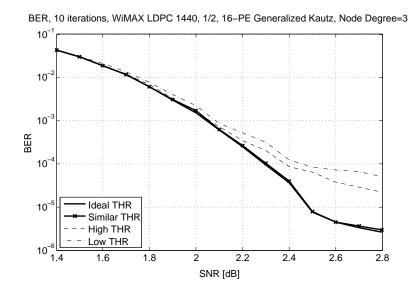

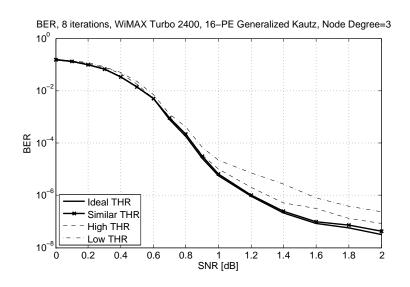

| 3.28 | Impact of different threshold choices on HI+SI+U+BR - LDPC codes                        | 91  |

| 3.29 | Impact of different threshold choices on HI+SI+U+BR - turbo codes $\hdots$              | 91  |

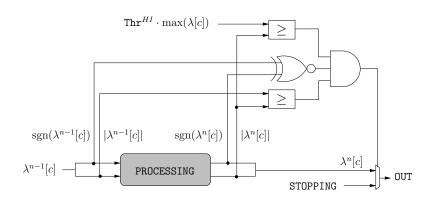

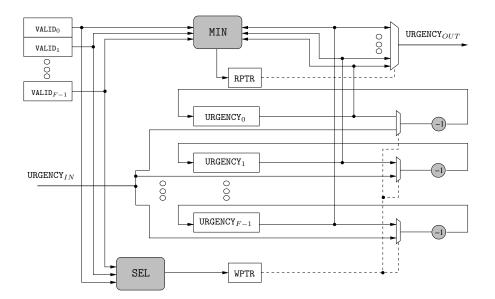

| 3.30 | HI implementation for LDPC codes - STOPPING message                                     | 93  |

| 3.31 | Urgency-based buffer reordering                                                         | 94  |

| 4.1  | Average SYN for WiMAX $N=864 r=3/4$ in case of successful and impossible decoding       | 105 |

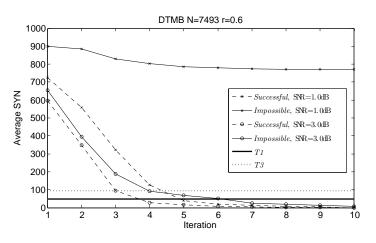

| 4.2  | Average SYN for DTMB $N=7493 r=3/5$ in case of successful and impossible decoding       | 105 |

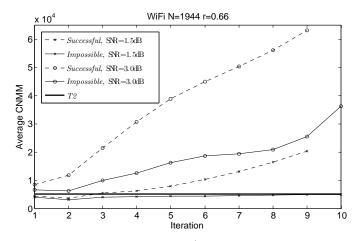

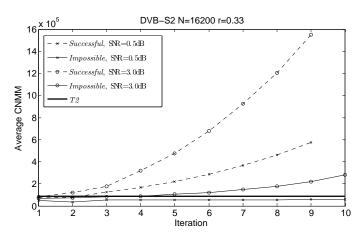

| 4.3  | Average CNMM for Wifi $N=1944 \ r=2/3$ in case of successful and impossible decoding    | 106 |

| 4.4  | Average CNMM for DVB-S2 $N=16200 r=1/3$ in case of successful and impossible            |     |

|      | decoding                                                                                | 106 |

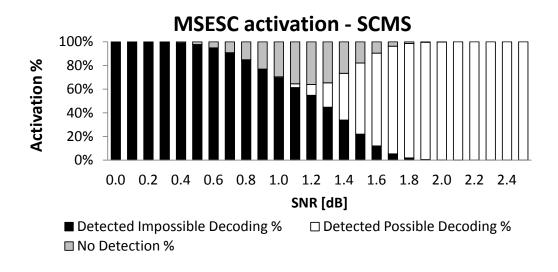

| 4.5  | Activation percentages of MSESC for WiMAX 2304, 1/2                                     | 107 |

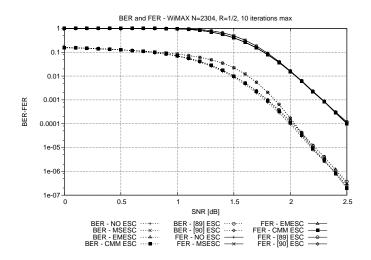

| 4.6  | BER and FER curves with Early Stopping Criteria                                         | 108 |

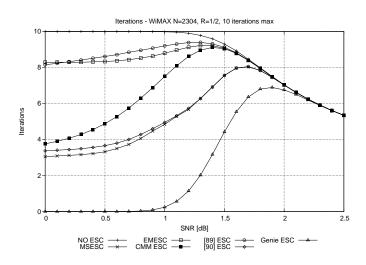

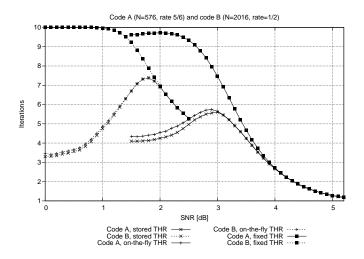

| 4.7  | Average number of iterations with different ESCs                                        | 108 |

| 4.8  | Average number of iterations with MSESC and different thresholds                        | 109 |

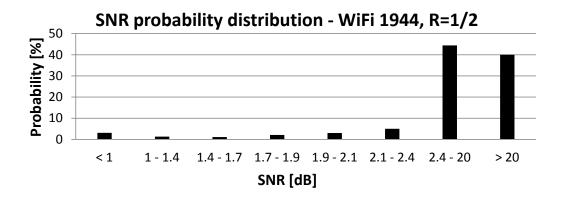

| 4.9  | SNR probability distribution for WiFi 1944, 1/2 $\ldots$                                | 113 |

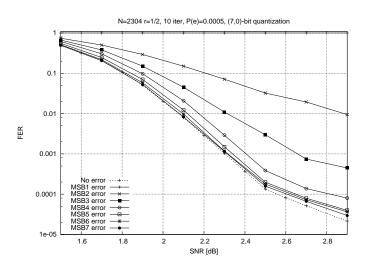

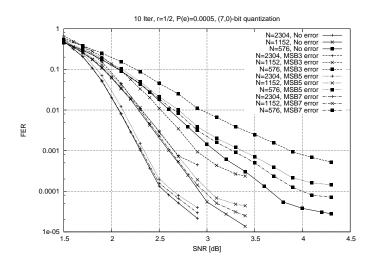

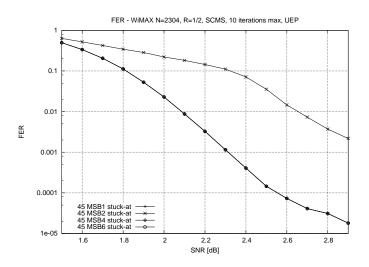

| 5.1  | FER - errors on different MSBs                                                          | 117 |

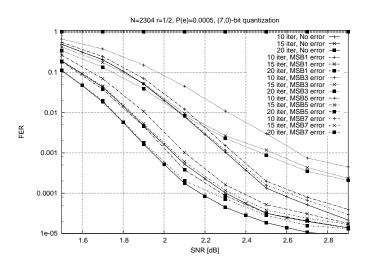

| 5.2  | FER - errors on different MSBs and variation of $It_{max}$                              | 118 |

| 5.3  | FER - errors on different MSBs and variation of code size                               | 118 |

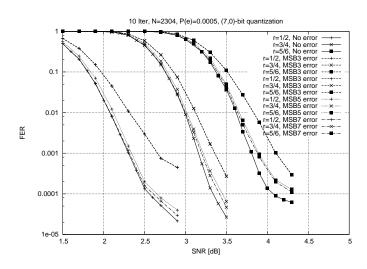

| 5.4  | FER - errors on different MSBs and variation of code rate                               | 119 |

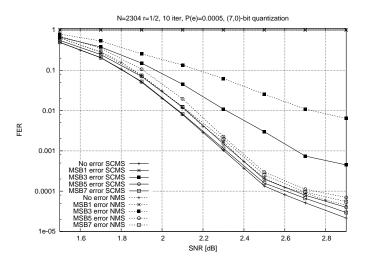

| 5.5  | FER - errors on different MSBs and variation of decoding algorithm                      | 120 |

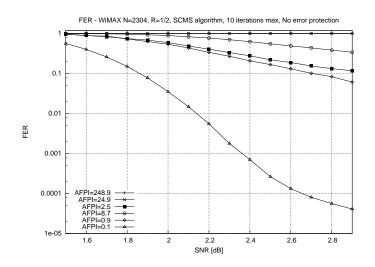

| 5.6  | FER with different AFPI - No error protection                                           | 123 |

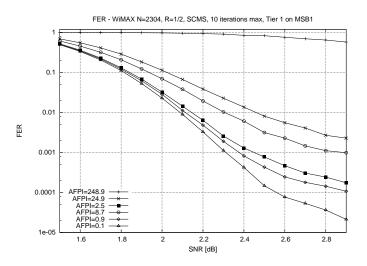

| 5.7  | FER with different AFPI - Tier 1 on MSB1                                                | 124 |

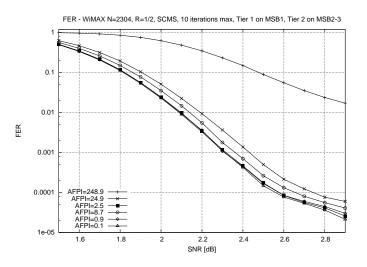

| 5.8  | FER with different AFPI - Tier 1 on MSB1, Tier 2 on MSB2-3                              | 126 |

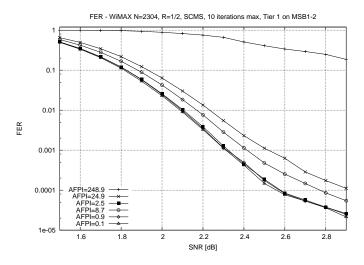

| 5.9  | FER with different AFPI - Tier 1 on MSB1-2                                                 | 126 |

|------|--------------------------------------------------------------------------------------------|-----|

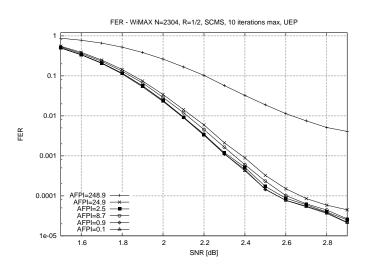

| 5.10 | FER with different AFPI - Complete UEP                                                     | 126 |

| 5.11 | UEP performance in presence of stuck-at bits                                               | 127 |

| 5.12 | LLR rearranged bits for burst error protection                                             | 128 |

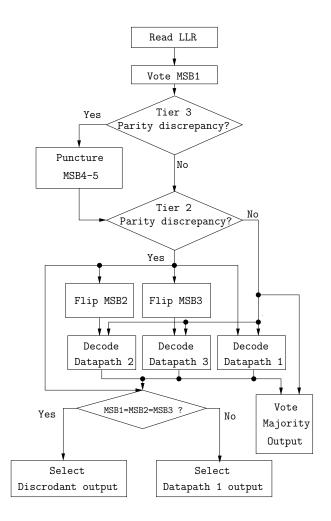

| 5.13 | UEP logic flow in the considered case of study                                             | 129 |

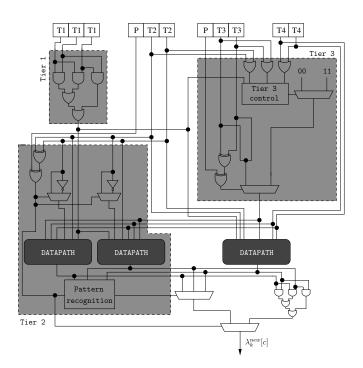

| 5.14 | UEP hardware structure                                                                     | 130 |

|      |                                                                                            | 105 |

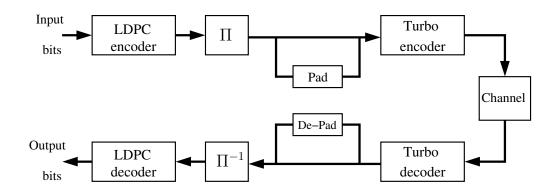

| 6.1  | Serial concatenation of LDPC and turbo codes FEC scheme                                    | 135 |

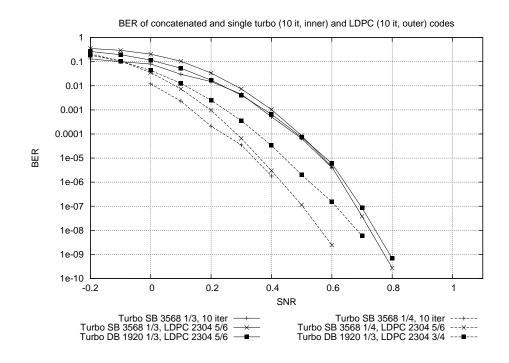

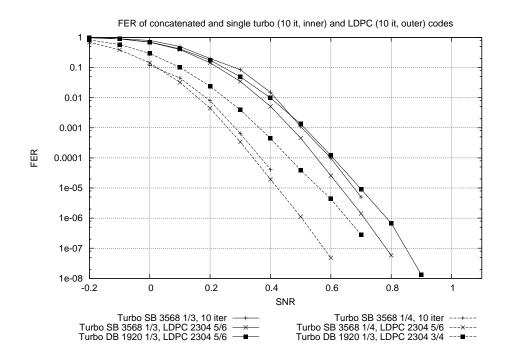

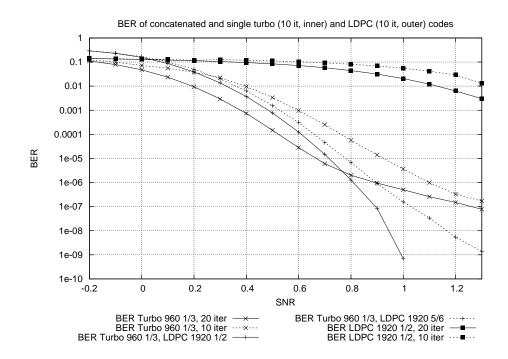

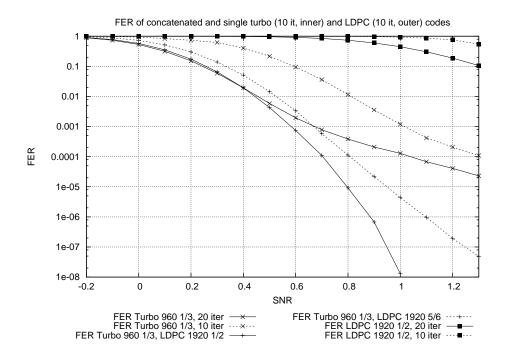

| 6.2  | Concatenated LDPC and turbo BER, AWGN channel, BPSK modulation $\ldots \ldots \ldots$      | 137 |

| 6.3  | Concatenated LDPC and turbo FER, AWGN channel, BPSK modulation                             | 137 |

| 6.4  | LDPC and DB turbo BER, concatenated and single-code, AWGN channel, BPSK mod-               |     |

|      | ulation                                                                                    | 138 |

| 6.5  | LDPC and DB turbo FER, concatenated and single-code, AWGN channel, BPSK mod-               |     |

|      | ulation                                                                                    | 138 |

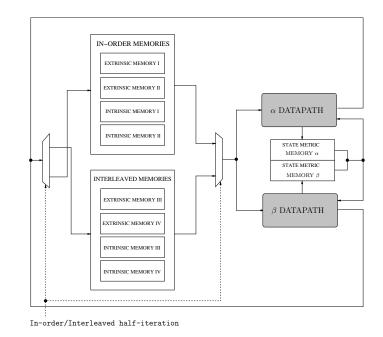

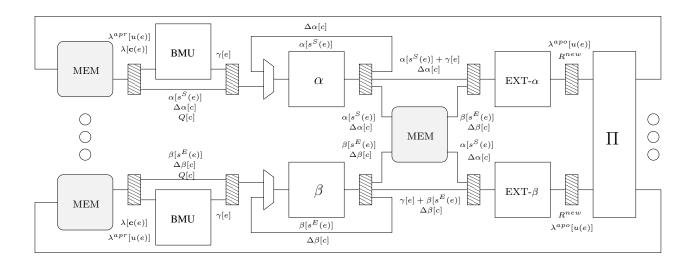

| 6.6  | Unified LDPC/turbo decoder overall block diagram                                           | 143 |

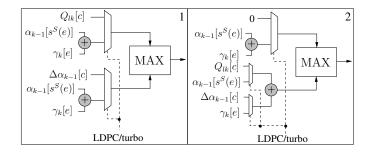

| 6.7  | Unified LDPC/turbo decoding datapath block diagram                                         | 143 |

| 6.8  | Unified LDPC/turbo comparator components, with inputs used in the $\alpha$ unit $\ldots$ . | 144 |

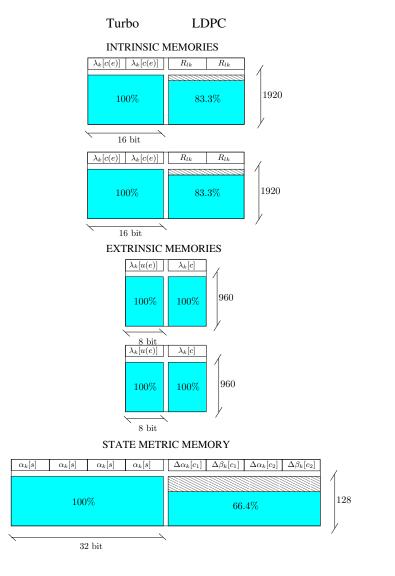

| 6.9  | Unified turbo/LDPC decoder memory sharing scheme                                           | 146 |

# List of Tables

| 3.1  | Throughput $[Mb/s]/Area[mm^2]$ for WiMAX LDPC $N = 2304$ , $r = 1/2$ code, for different                                                 |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | topologies, parallelism $P$ , node degree $D$ , routing algorithms and node architectures.                                               |    |

|      | Frequency is 300 MHz, technology is CMOS 90 nm. Results are obtained for parameters                                                      |    |

|      | $RL = 0, SCM, R = 0.5 \dots \dots$ | 42 |

| 3.2  | Throughput [Mb/s]/Area[mm <sup>2</sup> ] for WiMAX LDPC $N$ = 2304, $r$ = 1/2 code, for gen-                                             |    |

|      | eralized Kautz topology, parallelism $P$ , node degree $D$ , routing algorithms and node                                                 |    |

|      | architectures. Frequency is 300 MHz, technology is CMOS 90 nm. Results are obtained                                                      |    |

|      | for parameters $RL = 0$ , $SCM$ , $R = 0.5$                                                                                              | 42 |

| 3.3  | Throughput $[Mbits/s]/Area[mm2]$ for NoC based architectures supporting all WiMAX                                                        |    |

|      | turbo and LDPC codes                                                                                                                     | 43 |

| 3.4  | LDPC/Turbo architectures comparison: CMOS technology process (TP), processing                                                            |    |

|      | area occupation $(A_{core})$ , total area occupation $(A_{tot})$ normalized area occupation for                                          |    |

|      | 65nm technology (An), clock frequency $(f_{clk})$ , peak power consumption (Pow), data                                                   |    |

|      | width (DW), maximum number of iterations $(It_{max})$ , code length $(N)$ and rate $(r)$ and                                             |    |

|      | throughput $(T)$                                                                                                                         | 47 |

| 3.5  | Reconfiguration phases $\Phi_i$ : $t_a^{\Phi_i}$ , available clock cycles during $\Phi_i$ and $l_a^{\Phi_i}$ number of                   |    |

|      | locations that can be written in $t_a^{\Phi_i}$                                                                                          | 51 |

| 3.6  | IEEE 802.16e standard throughput $(T)$ , 10 iterations for LDPC, 8 for Turbo                                                             | 65 |

| 3.7  | IEEE 802.11n standard throughput $(T)$ with different $f_{core}$ and NoC sizes, 10 iterations                                            | 66 |

| 3.8  | Reconfiguration cases in intra- and inter-standard combinations. Dark gray: percent-                                                     |    |

|      | age of code combinations requiring decoder pausing. Light gray: percentage of code                                                       |    |

|      | combinations requiring 0 < $N_f \leq 2.$ White: all code combinations reconfigurable with                                                |    |

|      | $N_f = 0$ . Throughput obtained with 10 iterations for LDPC, 8 for Turbo                                                                 | 66 |

| 3.9  | CMMB and DTMB standard throughput $(T)$ , 10 iterations $\ldots \ldots \ldots \ldots \ldots$                                             | 67 |

| 3.10 | Throughput $(T)$ results for each standard, with every implementation                                                                    | 70 |

| 3.11 | Area efficiency $(A_{eff})$ for different codes and implementations. N/A: code not sup-                       |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | ported. Dash: results not available                                                                           | 70  |

| 3.12 | LDPC/Turbo architectures comparison: Decoder parallelism $P$ , CMOS technology pro-                           |     |

|      | cess (TP), processing area occupation $(A_{core})$ , total area occupation $(A_{tot})$ normalized             |     |

|      | area occupation for 65nm technology (An <sub>tot</sub> ), clock frequency $(f_{clk})$ , peak power con-       |     |

|      | sumption (Pow), energy efficiency $(E_{eff})$ , data width (DW), maximum number of                            |     |

|      | iterations (It <sub>max</sub> ), code length (N) and rate (r), interleaver size (K) and throughput (T)        | 71  |

| 3.13 | Percentages of late messages (% late) and stopped or not sent messages (% stop) for                           |     |

|      | no traffic handling (No TH) and combinations of the proposed methods on 16-PE and                             |     |

|      | 32-PE generalized Kautz and 2D-Mesh NoCs, at BER= $10^{-5}$                                                   | 87  |

| 3.14 | Effect of traffic handling on area occupation (CMOS 90 nm technology, post-layout                             |     |

|      | results)                                                                                                      | 96  |

| 3.15 | Effect of traffic handling on power consumption (CMOS 90 nm technology, 1.0 V supply)                         | 96  |

| 3.16 | Performance and energy consumption comparison (CMOS 90 nm technology, $1.0~\mathrm{V}$                        |     |

|      | supply)                                                                                                       | 98  |

| 3.17 | LDPC/Turbo architectures comparison: CMOS technology process (Tp), total area                                 |     |

|      | occupation ( $A_{tot}$ , normalized area occupation for 65nm technology ( $An_{tot}$ ), clock fre-            |     |

|      | quency $(f_{clk})$ , peak power consumption (Pow), energy efficiency $(E_{eff})$ , maximum                    |     |

|      | number of iterations (It <sub>max</sub> ), code length $(N)$ and rate $(r)$ , interleaver size $(K)$ and      |     |

|      | throughput (T), Area efficiency $(A_{eff})$                                                                   | 98  |

| 4.1  | Effect of MSESC on complexity (A), average power consumption (P) and energy per                               |     |

|      | decoded frame (E <sub>F</sub> ) ( It <sub>max</sub> = 10, CMOS 90 nm technology, 1.0 V supply, post-layout) 1 | 10  |

| 4.2  | Implementations comparison on average iterations $(It_{AVG})$ and energy $(E_F)$ for Wifi                     |     |

|      | N=1944,r=1/2 code SNR probability distribution (CMOS 90 nm, 1.0 V, post-layout) 1                             | 13  |

| 5.1  | UEP - Sustainable single stuck-at bits 1                                                                      | .27 |

| 5.2  | UEP - area occupation, power consumption (90 nm CMOS, 200 MHz) 1                                              | 31  |

| 6.1  | Performance comparison among FEC schemes 1                                                                    | .39 |

| 6.2  | Memory requirements                                                                                           | 47  |

# Acronyms

| AFPI   | Average Failures Per Iteration                  |

|--------|-------------------------------------------------|

| AP     | All Precalculated                               |

| ASIC   | Application-Specific Integrated Circuit         |

| ASIP   | Application-Specific Instruction-set Processors |

| ASNoC  | Application-Specific NoC                        |

| ASP    | All local Shortest Paths                        |

| AWGN   | Additive White Gaussian Noise                   |

|        |                                                 |

| BER    | Bit Error Rate                                  |

| BL     | Bit-Level                                       |

| BMU    | Branch Metric Unit                              |

| BP     | Belief Propagation                              |

| BR     | Buffer Reordering                               |

| BTC    | Block Turbo Code                                |

| BTS CU | Bit-To-Symbol Conversion Unit                   |

|        |                                                 |

| CC     | Convolutional Code                              |

| CMOS   | Complementary Metal Oxide Semiconductor         |

| CN     | Check Node                                      |

| CNMC   | Check Node Mean Checksum                        |

| CNMM   | Check Node Mean Magnitude                       |

| СМ     | Collision Management                            |

| CTC    | Convolutional Turbo Code                        |

|        |                                                 |

| DB     | Duo-Binary or Double-Binary                     |

| DBTC   | Duo-Binary Turbo Code                           |

| DCM           | Delay Colliding Message                                                            |

|---------------|------------------------------------------------------------------------------------|

| ECC           | End of Current Configuration (Chapter 3.4) or Error<br>Correcting Code (Chapter 4) |

| ECU           | Extrinsic Computation Unit                                                         |

| EFC           | End of Future Configuration                                                        |

| EMESC         | Erased Massages Early Stopping Criterion                                           |

| ESC           | Early Stopping Criterion                                                           |

|               |                                                                                    |

| FEC           | Forward Error Correction                                                           |

| FER           | Frame Error Rate                                                                   |

| FIFO          | First In First Out                                                                 |

| FIT           | Failures In Time                                                                   |

| $\mathrm{FL}$ | FIFO Length                                                                        |

| $\mathrm{FT}$ | FIFO length Traffic spreading                                                      |

| HI            | Hard Importance                                                                    |

| IC            | Inner Code                                                                         |

| IDD           | Impossible Decoding Detection                                                      |

| IP            | Intellectual Property                                                              |

|               |                                                                                    |

| JANoCS        | Joint Application and Network-on-Chip Simulator                                    |

|               |                                                                                    |

| LDPC          | Low Density Parity Check                                                           |

| LLR           | Logarithmic Likelihood Ratio                                                       |

| LSB           | Least Significant Bit                                                              |

| LT            | Luby Transform                                                                     |

| MAP     | Maximum-A-Posteriori                    |

|---------|-----------------------------------------|

| MEU     | Minimum Extraction Unit                 |

| MP-SoC  | Multi-Processor System-on-Chip          |

| MSB     | Most Significant Bit                    |

| MSESC   | Multi-Standard Early Stopping Criterion |

| MTBF    | Mean Time Between Failures              |

|         |                                         |

| NB-LDPC | Non-Binary LDPC                         |

| NDT     | Normalized Delivery Time                |

| NED     | NEtwork Description                     |

| NI      | Network Interface                       |

| NMS     | Normalized Min-Sum                      |

| NoC     | Network on Chip                         |

| OC      | Outer Code                              |

| PE      | Processing Element                      |

| PP      | Partially Precalculated                 |

|         |                                         |

| QC-LDPC | Quasi-Cyclic LDPC                       |

| QoS     | Quality-of-Service                      |

|         |                                         |

| RE      | Routing Element                         |

| RL      | Route Local                             |

| RP      | Read Pointer                            |

| RR      | Round Robin                             |

| RSC     | Recursive Systematic Convolutional      |

| SISO    | Soft-Input Soft-Output                  |

| SB     | Single-Binary                  |

|--------|--------------------------------|

| SBTC   | Single-Binary Turbo Code       |

| SCC    | Start of Current Configuration |

| SCM    | Send Colliding Message         |

| SCMS   | Self-Corrected Min-Sum         |

| SFC    | Start of Future Configuration  |

| SI     | Soft Importance                |

| SNR    | Signal-to-Noise Ratio          |

| SoC    | System-on-Chip                 |

| SRD    | Symbol Reliability Difference  |

| SSP    | Single Shortest Path           |

| STB CU | Symbol-To-Bit Conversion Unit  |

| SW     | Sliding Window                 |

|        |                                |

| U      | Urgency                        |

| UEP    | Unequal Error Protection       |

|        |                                |

| VN     | Variable Node                  |

| WP     | Write Pointer                  |

Chapter 1

# Introduction

### 1.1 Motivation

The field of communications, both wireless and wired, has seen in the last decades an unprecedented development. Every day, we use tens of different devices to store, receive and exchange information. Regardless of their specific function, they are all characterized by a common component: the channel decoder. Forward Error Correction (FEC) or channel coding is a technique present in all kinds of communication standards: by encoding the transmitted information, it is possible to detect and correct errors introduced during the transmission due to a noisy channel. Diverse FEC schemes are currently used and both literature and industry continuously propose new codes and code combinations.

The design of an efficient channel decoder is a challenging task, since many variables come into play. First of all, although the quest for better performance, simple hardware and small overhead is continuous, decoders are still complex components that implement computationally intensive algorithms. In fact, they often account for a large part of the device Silicon footprint and power consumption, and they are a potential bottleneck in increasing the system throughput. Secondly, the most recent nanometric fabrication technologies are not able to guarantee degrees of reliability as high as before. Finally, the rate at which new standards are introduced and the wide number of codes and related parameters considered by each one of them require decoders to be adaptable and flexible. New design approaches and new solutions at architectural level are consequently necessary to face these continuously evolving needs.

Covolutional Turbo Codes (CTCs) [1] ()and Low-Density Parity-Check (LDPC) codes [2] yield very good error correction capabilities and rely on iterative decoding algorithms. They are considered in a large number of standards, both alone and concatenated with other codes, for a variety of applications: wireless communications (WiMAX [3], WiFi [4], 3GPP-LTE [5]), wired communications (HpAV [6]), broadcasting (DVB-S2 [7], CMMB [8], DTMB [9]) and space communications (CCSDS [10]). Every standard can foresee different code types, which in turn can support hundreds of different code parameter combinations: even a channel decoder targeting a single standard must be extremely flexible. Obviously, flexibility comes at cost in speed, area occupation and power consumption.

The design of a channel decoder can be a critical task, due to the complexity of the system and the wide number of constraints usually involved. In particular, technological constraints (e.g. nanotechnologies) and application bounds (standard specifications) result in problematic design of mainly four types of channel decoders:

• multi-standard decoders, flexible with respect to existing standards (legacy-proof) and to future standards (future-proof);

#### 1.1. MOTIVATION

- low-power consumption decoders;

- reliable decoders, able to correct errors within the memories;

- high-performance decoders, with extremely high error correction capabilities.

Stemming from previous studies on flexible LDPC decoders, this thesis work has been mainly focused on the development of flexible turbo and LDPC decoder designs, and on the narrowing of the power, area and speed gap they might present with respect to dedicated solutions. Additional studies have been carried out within the field of increased code performance and of decoder resiliency to hardware errors.

### **1.2** Outline and contributions

In the above described context, several contributions have been proposed and will be presented in the rest of this manuscript which is organized as follows:

- Chapter 2 gives a brief overview on turbo and LDPC codes. The theory base behind these codes is reviewed, and the most common decoding algorithms are described. The state of the art on current decoder implementations is finally presented.

- 2. Chapter 3 regroups several main contributions in the design and implementation of flexible channel decoders. The first part concerns the design of a Network-on-Chip (NoC) serving as an interconnection network for a partially parallel LDPC decoder. This study follows a former analysis that identified the best combination of design choices for an application specific NoC used in a turbo decoder. The NoC simulator used in [11] is modified and extended to LDPC codes as well, while additional topologies and design choices are taken in account. Joining the new results with those in [11], a best-fit NoC architecture is selected and a complete multi-standard turbo/LDPC decoder is designed and implemented. This decoder serves as the starting point for a study on the reconfiguration of NoC-based channel decoder. Every time the code is changed, the decoder must be reconfigured: this usually translates on the overwriting of one or more memories, with the new data brought by dedicated buses. A number of variables influence the duration of the reconfiguration process, starting from the involved codes down to decoder design choices. Their effect is evaluated in order to achieve a reconfiguration architecture capable to sustain as many codes as possible. The flexible decoder designed before is subsequently modified, including also the proposed reconfiguration technique: three implementations are presented, characterized by different decoder parallelism degrees, supported codes and achieved throughput. NoC-based decoders, while granting flexible connectivity among all their nodes, can be burdened with long transmission times. To meet with often high throughput requirements, it is not always possible to wait for the transmitted information to reach its destination: to evaluate the impact of the interconnection network on the performance of a decoder, and vice versa, a Joint Application and NoC Simulator (JANoCS) is proposed and presented. It is a generic tool for concurrent simulation of processing elements and interconnection for Multi-Processor Systemson-Chip (MP-SoCs), and it is useful for design space exploration in cases where processing and communication need to be jointly optimized. JANoCS is then applied to the turbo/LDPC decoder case to analyze the impact of late information delivery: correct functionality can be ensured with a high NoC clock frequency, but to avoid the power consumption increase traffic

reduction and optimization methods are devised, tested and implemented.

The main contributions of the work presented in this chapter are:

- a NoC simulator used to obtain the achievable throughput and an estimation of the NoC area occupation, given the network details and the communication needs of the processing elements;

- a best-fit NoC design targeting both turbo and LDPC code decoding;

- a multi-standard partially parallel turbo/LDPC decoder based on the designed NoC;

- an analysis of the reconfiguration problem in NoC-based decoders;

- the design of a multi-standard reconfigurable turbo/LDPC decoder, with three different implementations targeting different sets of standards;

- the JANoCS simulator, for concurrent application-communication simulation of generic MP-SoCs;

- the identification and analysis of the late message delivery issue in partially parallel turbo/LDPC decoders, with the evaluation of its impact on the decoder performance;

- the design of four power reduction techniques that tackle the late message delivery issue and avoid power-hungry solutions: the proposed methods are implemented within the reconfigurable decoder;

- the validations of the designed solutions, carried out with appropriate tools on synthesized, placed and routed circuits;

The obtained results have been presented at, published in or submitted to

- DASIP'11 conference [12]

- DATE'12 conference [13]

- IEEE Transactions on Circuits and Systems I [14]

- DSD'13 conference [15]

- Springer Circuits, Systems & Signal Processing [16]

- 3. In Chapter 4 a study on the early stopping of iterations for LDPC decoders is presented. Iterative decoders typically fix a maximum number of available iterations for the decoding of a frame, but a codeword might be corrected in less iterations, or the maximum number might not be enough. For this reason, many decoders employ Early Stopping Criteria (ESCs) that try to identify situations in which additional iterations are useless. In this chapter we propose a new

criterion that observes the evolution of simple metrics and via on-the-fly threshold computation outperforms the state of the art in terms of both iteration and energy saving.

The main contributions of the work presented in this chapter are:

- an early stopping criteria for LDPC decoding that is adaptive to both code parameters and channel conditions, and identifies efficiently both correct codewords and impossible decoding;

- the hardware implementation of the proposed criterion and evaluation of its impact on performance and energy consumption under realistic channel conditions;

The obtained results have been presented at, published in or submitted to

- IET Communications [17]

- 4. Chapter 5 portrays a study on the resilience of LDPC decoders under the effect of memory errors. Due to the soft nature of the stored values, LDPC decoders will be affected differently according to the meaning of the wrong bits: ad-hoc error protection techniques can consequently be applied to different bits according to their significance. The proposed Unequal Error Protection (UEP) allows to recover from errors on most significant bits, limits the impact of errors on least significant bits, and ensures the decoder performance also in presence of large numbers of errors. The main contributions of the work presented in this chapter are:

- an extensive analysis of the sensitivity to errors of LDPC decoders, depending on decoding algorithm, quantization, iterations, code size and rate;

- the proposal of the UEP method and the evaluation of its effectiveness;

- the design and implementation of the hardware structure of proposed method in a case of study;

The obtained results are going to be submitted to IEEE Transactions on Computers.

5. In Chapter 6 the serial concatenation of LDPC and turbo codes is presented, set within the framework of deep space communications. These are characterized by critical spacecraft-to-Earth transmissions: the long distances and low power available require very good FEC schemes. The proposed FEC joins the performance of turbo codes at low Signal-to-Noise Ratio (SNR) with that of LDPC codes at high SNR, and outperforms both current deep-space FEC schemes and concatenation-based FECs. A decoder for the proposed FEC scheme is designed and implemented.

The main contributions of the work presented in this chapter are:

- a novel FEC scheme based on the serial concatenation of LDPC and turbo codes, and its comparison against current solutions;

- a low complexity, low power decoder design targeting the proposed FEC: it relies on a shared datapaths and on a smart memory sharing structure that avoids the need for memory interleaving when changing decoding mode;

The obtained results have been presented at, published in or submitted to

- SPACOMM'13 conference [18]

- IEEE Transactions on Aerospace and Electronic Systems [19]

- 6. Finally, Chapter 7 draws the conclusions. Additional contributions by the author are briefly addressed [20–22], together with ongoing work and future perspectives.

Chapter 2

# LDPC and turbo code decoding

### 2.1 LDPC and turbo codes

Channel coding is a technique applied to most communication systems: the encoding of transmitted information allows, at reception, to detect and correct errors introduced by a noisy channel. In this section we introduce two powerful types of codes, employed in a variety of standards targeting different applications: turbo codes and Low-Density Parity-Check (LDPC) codes.

#### 2.1.1 Turbo codes

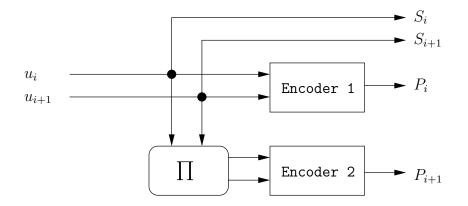

Turbo codes have been proposed for the first time by Claude Berrou in [1] in the early Nineties: they are obtained from the parallel concatenation of two Convolutional Codes (CC), as shown in Fig. 2.1. Information bits are fed to both encoders, but not in the same order, since an interleaver  $\Pi$  is placed before the second convolutional encoder.

Figure 2.1: Turbo code encoder

The ratio between the number of information bits fed to the encoder and the number of encoder output bits determines the code rate r. The number of concurrent bits injected in the turbo encoder, i.e. the size of input symbols, determines if the turbo code is Single Binary (SB, one-bit symbols) or Duo-Binary (DB, two-bit symbols). While turbo encoders can work with infinite streams of bits, for practical purposes standards work with finite frame sizes, that effectively consider turbo codes as block codes. The number of input symbols is identified by K, while the frame is constituted of Nsymbols.

As the first practical codes with performance close to the Shannon limit, turbo codes have immediately known widespread study and usage. Most of the standards that use turbo codes rely on two Recursive Systematic Convlutional (RSC) encoders. This means that the information bits are explicitly present in the encoded sequence  $(S_i \text{ and } S_{i+1} \text{ in Fig. } 2.1)$ .

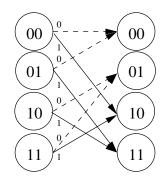

Figure 2.2: Turbo code trellis

According to the structure of the turbo encoder, a code can be pictured as a sequence of trellises, a representation exploited during the decoding process. In Fig. 2.2, each node of the trellis graph is a possible state of the encoder: the left ones are starting states, and the right ones are ending states. Edges are linked to input symbols: so, it is possible to move from the starting state to the ending state according to the received bits.

#### 2.1.2 LDPC codes

LDPC codes are block error correcting codes explored for the first time by Robert Gallager in the early Sixties [2]. LDPC codes were shown impractical to use until the late nineties, when they were rediscovered by MacKay and Neal [23]. LDPC codes took hold thanks to the powerful computational hardware available and to the advent of approximated decoding algorithms.

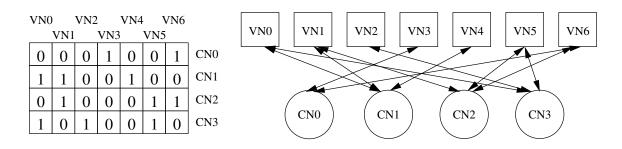

The key characteristic of an LDPC code is its binary parity check **H** matrix, constituted of N columns and M rows: **H** specifies all the valid codewords of the code. These codewords are identified by the set of vectors x of N bits for which  $\mathbf{H} \cdot x' = 0$ , where  $(\cdot)'$  is the transposition operator, meaning that the M parity check constraints defined by the matrix rows must be all verified. The **H** matrix is sparse: this means that, with respect to the dimensions of the matrix, very few non-zero entries are present. Their placement is the main task in the construction of the code, since the achievable error correcting performance is heavily influenced by the relative positioning of the ones among the zeros. While **H** is used in the decoding process, the information bits u are encoded as  $x = u \cdot \mathbf{G}$ , where **G** is a  $K \times N$  generator matrix that can be obtained from **H** and K = N - M.

Many representations of the  $\mathbf{H}$  matrix are possible, but the Tanner graph representation is commonly used in the decoding process. The Tanner graph identifies a bipartition of the  $\mathbf{H}$  matrix, with the Variable Nodes (VNs) representing the columns and the Check Nodes (CNs) representing the

Figure 2.3: LDPC code **H** matrix and Tanner graph

rows. Consequently, VNs are associated to the N bits of the codeword, whereas CNs correspond to the M parity-check constraints. An edge between CN l and VN k is present if a non-zero entry is found in row l, column k of **H**. Fig. 2.3 shows an example **H** matrix, with seven VNs and four CNs, with the relative Tanner graph.

### 2.2 LDPC and turbo code decoding algorithms

Based on the aforementioned code representations, this section presents turbo and LDPC code decoding algorithms.

#### 2.2.1 Turbo codes decoding algorithm

The turbo decoder is made of two constituent decoders, referred to as Soft-In-Soft-Out (SISO) or Maximum-A-Posteriori (MAP) decoders connected in an iterative loop by the means of the interleaver  $\Pi$  and the de-interleaver  $\Pi^{-1}$ . Each constituent decoder performs the so called BCJR algorithm [24] that starting from the intrinsic and *a priori* information produces the extrinsic information. Let *k* be a step in the trellis representation of the constituent CC, and *u* an uncoded symbol. Each constituent decoder computes  $\lambda_k[u] = \sigma \cdot (\lambda_k^{apo}[u] - \lambda_k^{apr}[u] - \lambda_k[\mathbf{c}^u])$  where  $\sigma \leq 1$  [25],  $\lambda_k^{apo}[u]$  is the *a*-posteriori information,  $\lambda_k^{apr}[u]$  is the *a priori* information and  $\lambda_k[\mathbf{c}^u]$  is the systematic component of the intrinsic information. According to [24] a-posteriori information is computed as

$$\lambda_k^{apo}[u] = \max_{e:u(e)=u}^* \{b(e)\} - \max_{e:u(e)=\tilde{u}}^* \{b(e)\}$$

(2.1)

where  $\tilde{u} \in \mathcal{U}$  is an uncoded symbol taken as a reference (usually  $\tilde{u} = \mathbf{0}$ ) and  $u \in \mathcal{U} \setminus {\tilde{u}}$  with  $\mathcal{U}$  the set of uncoded symbols; e is a trellis transition and u(e) is the corresponding uncoded symbol. Several exact and approximated expressions are available for the  $\max^* {x_i}$  function [26]: for example, it can be implemented as  $\max\{x_i\}$  followed by a correction term (Log-MAP), often stored in a small Look-Up-Table (LUT). The correction term, usually adopted when decoding binary codes, can be omitted with minor Bit-Error-Rate (BER) performance degradation (Max-Log-MAP). The term b(e) in (2.1) is defined as:

$$b(e) = \alpha_{k-1}[s^{S}(e)] + \gamma_{k}[e] + \beta_{k}[s^{E}(e)]$$

(2.2)

$$\alpha_k[s] = \max_{e:s^E(e)=s}^* \left\{ \alpha_{k-1}[s^S(e)] + \gamma_k[e] \right\}$$

(2.3)

$$\beta_k[s] = \max_{e:s^S(e)=s}^{*} \left\{ \beta_{k+1}[s^E(e)] + \gamma_k[e] \right\}$$

(2.4)

$$\gamma_k[e] = \lambda_k^{apr}[u(e)] + \lambda_k[\mathbf{c}(e)]$$

(2.5)

where  $s^{S}(e)$  and  $s^{E}(e)$  are the starting and the ending states of e,  $\alpha_{k}[s^{S}(e)]$  and  $\beta_{k}[s^{E}(e)]$  are the forward and backward state metrics associated to  $s^{S}(e)$  and  $s^{E}(e)$  respectively. The term  $\lambda_{k}[\mathbf{c}(e)]$ represents the intrinsic information received from the channel.

For practical implementations, the size of a turbo codeword is fixed to limited values, but it can

be quite large. The BCJR algorithm requires a forward (2.3) and a backward (2.4) recursion over the codeword symbols to compute (2.1) and it can be unacceptable both in terms of latency and of complexity. For this reason, decoding is usually constrained to a portion of the codeword, called *window*, long enough not to cause performance degradation, that allows to meet the demanding throughput requirements of most standards: it is the Sliding Window (SW) technique [27], that has evolved in diverse methods to improve metric initialization and exchange. Bordering windows, in fact, exchange information on the edge symbols in order to continue the decoding.

#### 2.2.2 LDPC codes decoding algorithm

The most common algorithm to decode LDPC codes is the *Belief Propagation* (BP) algorithm. The BP algorithm, also known as probability propagation and sum-product algorithm, uses iterative message passing between the nodes to update bit error probabilities. It was invented by Gallager in 1963, and reinvented by MacKay and Neal [28]. It is most commonly implemented in its logarithmic form: in this version, the metrics on which is taken the decision on bits are Logarithmic Likelihood Ratios (LLRs).

There are two main scheduling schemes for the BP: two-phase scheduling and layered scheduling [29]. The two-phase scheduling relies on the Tanner graph representation of **H**: every iteration is composed of a CN phase, in which the parity check constraints defined by **H** are computed, and a subsequent VN phase, that takes in account the results of the CN phase to update bit LLRs. In the layered scheduling, instead, a single type of node is present, and parity-check constraints are grouped in layers so that there are no edges between nodes belonging to the same layer. Each layer is associated to a component code: they are decoded in sequence by propagating LLRs from one layer to the following one [29].

Let  $\lambda[c]$  represent the LLR of symbol c and, for column k in **H**, bit LLR  $\lambda_k[c]$  is initialized to the corresponding received soft value, according to the estimated channel conditions. Then, for all parity constraints l in a given layer, the following operations are executed:

$$Q_{lk}[c] = \lambda_k^{old}[c] - R_{lk}^{old} \tag{2.6}$$

$$A_{lk} = \sum_{n \in N(l), n \neq k} \Psi(Q_{ln}[c])$$

$$(2.7)$$

$$\delta_{lk} = \prod_{n \in N(l), n \neq k} \operatorname{sgn}(Q_{ln}[c])$$

(2.8)

$$R_{lk}^{new} = -\delta_{lk} \cdot \Psi^{-1}(A_{lk}) \tag{2.9}$$

$$\lambda_k^{new}[c] = Q_{lk}[c] + R_{lk}^{new} \tag{2.10}$$

$\lambda_k^{old}[c]$  is the extrinsic information received from the previous layer and updated in (2.10) to be propagated to the succeeding layer. Term  $R_{lk}^{old}$ , pertaining to element (l,k) of **H** and initialized to 0, is used to compute (2.6); the same amount is then updated in (2.9),  $R_{lk}^{new}$  (the CN-to-VN message), and stored to be used again in the following iteration. In (2.7) and (2.8) N(l) is the set of all bit indexes that are connected to parity constraint l. The decoded vector y is obtained by observing the sign of all  $\lambda_k[c]$  at the end of each iteration, and the syndrome SYN is consequently obtained as

$$SYN = \sum_{l=1}^{M} \mathbf{H}_l \cdot y' \tag{2.11}$$

The BP algorithm involves some complex computations, in particular  $\Psi(\cdot)$  in (2.7) and (2.9) that requires the calculation of a hyperbolic tangent. In [30] a possible approximation of the  $\Psi(\cdot)$  function causing limited performance loss is presented:

$$R_{lk}^{new} \approx -\delta_{lk}' \cdot \min_{n \in N(l), n \neq k} \left\{ |Q_{nk}| \right\},$$

(2.12)

where  $\delta'_{lk} = \sigma \cdot \delta_{lk}$  and  $\sigma \leq 1$ . It is usually referred to as Normalized-Min-Sum (NMS) approximation. The Self-Corrected-Min-Sum (SCMS) approximation [31], while based on the same concept, combines (2.12) with a dynamic correction. When  $Q^i_{lk}[c]$  is computed at the  $i^{th}$  iteration, it is compared with  $Q^{i-1}_{lk}[c]$ . If their signs are different,  $Q^i_{lk}[c]$  is substituted with zero for the current iteration, inducing a conservative behavior in presence of the uncertainty represented by a sign change.

A particularly interesting exploitation of the similarities between turbo and LDPC codes has been proposed in [32], that allows to use the same decoding algorithm for both types of code. Every row of **H** is seen as a turbo code with trellis length equal to the row weight: a direct link between turbo and LDPC codes is drawn, and turbo decoding algorithms like BCJR can be applied to LDPC codes with minor adjustments. The BCJR-based LDPC decoding relies on the fact that binary LDPC codes have a 2-state trellis: state metrics can consequently be expressed as differences  $\Delta \alpha[c]$  and  $\Delta \beta[c]$ , reducing the quantization noise. Considering the Max-Log-MAP approximation [25], the CN-to-VN message update becomes:

$$\Phi(x,y) = \max(x,y) - \max(x+y,0)$$

(2.13)

$$R_{lk}^{new} = \Phi(\Delta \alpha_k[c], \Delta \beta_k[c])$$

(2.14)

$$\Delta \alpha_k = \Phi(\Delta \alpha_{k-1}[c], Q_{lk}[c]) \tag{2.15}$$

$$\Delta\beta_k = \Phi(\Delta\beta_{k+1}[c], Q_{lk}[c]) \tag{2.16}$$

where  $\Delta \alpha[c]$  and  $\Delta \beta[c]$  at the edge of the trellis are initialized as the minimum value of the dynamic range.

### 2.3 LDPC and turbo code decoders

This section gives an overview on current turbo and LDPC decoder solutions, focusing on both separate and joint implementations.

#### 2.3.1 Turbo code decoders

Since turbo codes are a well-established technology used in a wide variety of applications, the literature is ripe with many practical implementations of turbo decoders: successful solutions for turbo decoding have been proposed in the past years [33,34]. The latest trends in the community have seen an increased interest towards differentiation in high-performance decoders, low power decoders and flexible decoders.

The parallel decoder presented in [35] targets the 3GPP-LTE standard, characterized by high throughput requirements. They are met through the usage of 8 radix-4 SISOs, a common enough choice for high-throughput designs. Communication among cores is enforced by means of shared memory banks. The proposed architecture manages to avoid memory access contentions, and allows to reduce the bottleneck usually associated with turbo code interleaving. The resulting decoder yields a small area, and moderate to high throughputs, with very low power consumption when targeting a 100 MB/s throughput. A similar approach is employed in [36], where even higher performance peaks are reached. The decoder is again tailored for the 3GPP-LTE standard. The described architecture relies on 64 processing cores, internally structured as radix-4 SISOs: the decoder yields 1.28 Gb/s at 400 MHz and 6 iterations. Obviously, the price for such outstanding results is payed in terms of complexity (8.3 mm<sup>2</sup> in 65 nm Complementary Metal Oxide Semiconductor, CMOS, technology) and power consumption (845 mW).

A more flexible architecture is devised in [37], where a decoder targeting both 3GPP-LTE and Mobile WiMAX standards is proposed. The different natures of the considered turbo codes (singlebinary in 3GPP-LTE and duo-binary in Mobile WiMAX) is tackled by means of bit-to-symbol and symbol-to-bit conversions [38], addressed later in Section 3.2 and 3.4 of this manuscript, that allow almost complete memory sharing. Moreover, a novel dual-mode interleaver is introduced that reduces the overhead relative to the implementation of the native ARP [3] and QPP [5] respective interleavers. The resulting multi-standard decoder can reach up to 186 Mb/s with moderate complexity.

The sliding window technique [27] is one of the most widely employed in turbo decoders. The SISO proposed in [39] implements this technique in its standard form, with dummy state metric initialization and sliding step of one trellis. Deeply pipelined architectures have been proposed in order to reduce the memory requirements [40]. These have been improved thanks to the tailbiting technique: the

WiMAX decoder proposed in [41] avoids the cumbersome initialization by considering the turbo code as a circular structure, and allows for consistent throughput enhancement. The improvement of the dummy recursion and an ad-hoc contention-free memory architecture allow the decoder presented in [42] to yield low complexity and low power consumption. Moreover, smart initialization of the dummy recursion results in faster decoding algorithm convergence, and consequently fewer necessary iterations for correct decoding.

Flexibility and multi-standard support is achieved in [43] by means of partially parallel decoder based on Application Specific Instruction-set Processors (ASIPs). Support is given for 3GPP-LTE, WiMAX and DVB-RCS standards, reaching a maximum throughput of 170 Mb/s and yielding good efficiency. Different ASIPs are used for the in-order and interleaved phases of the decoding process, and the complexity and latency are kept in check via smart information exchange networks and pipeline idle time minimization.

#### 2.3.2 LDPC code decoders

The literature on LDPC code decoders, much like in the turbo case, has shown a trend towards design specialization targeting a particular performance aspect.

The flexible LDPC decoder described in [44] is one the first work to consider a Network-on-Chip (NoC) as a possible interconnection structure. Together with the design of processing elements, the design of the application-specific NoC is carried out in detail: it is shown that many of the characteristics of general purpose NoCs are not necessary, thus reducing the overhead commonly associated with complex interconnections. The complete decoder is arranged on a toroidal mesh topology.

An extremely low-power and high performance decoder is designed in [45], targeting the WiMAX standard. Low power consumption is obtained through very low working frequency: a very high throughput is achieved via a high internal parallelism, adaptable to the code thanks to the regular structure of the WiMAX codes. Implemented in 65 nm CMOS technology, at 40 MHz, more that 1 Gb/s throughput is obtained, with a total power consumption of 29.5 mW. A similar design approach is carried out in [46]: the decoder, however, targets high throughputs and low complexity. A higher frequency of 110 MHz is used to obtain 1 Gb/s throughput, consuming 115 mW and occupying half of the area of [45].

A decoder with extremely good error correction capabilities is shown in [47]. It is designed targeting LDPC convolutional codes, that can be obtained from quasi-cyclic LDPC codes. Again, the regular structure of these codes allows for easy design of largely parallel structure. Up to 2 Gb/s are obtained with a frequency of 100 MHz.

#### 2.3.3 Turbo/LDPC decoders

Few recent works have focused on extending the concept of flexible decoders not only to multiple codes, but also to multiple code types, providing complete support for whole standards.

The work in [48] describes the design of a multi-standard turbo/LDPC decoder based on ASIPs and the sharing of memories between the two code types. Each ASIP has two separate datapaths, one for each decoding mode: eight ASIPs are instantiated and connected via a simple but flexible interconnection network, that can be reconfigured when switching decoding mode to adapt to the different communication patterns. Also in [49] is presented an ASIP-based decoder, that includes convolutional code decoding as well. This work is characterized by extremely small area occupation and high achievable frequency, that helps to meet most throughput requirements for the considered standards.

The works presented in [50–52] exploit commonalities between turbo and LDPC decoding to design a unified architecture for multiple standards. By interpreting LDPC codes as a series of turbo codes, as introduced in Section 2.2, the BCJR algorithm can be applied to both code types. The shared datapath and memories result in an overall area much lower than separate dedicated decoder implementations.

# Chapter 3

# Flexible architectures for channel decoding

With the term flexibility regarding channel decoding it is intended the ability of a decoder to support different codes and types of codes, enabling its usage in a wide variety of situations. The degree of flexibility of a decoder can be limited to a single standard, or even multiple ones. Much research has been done in this sense after the great increase in number of standards, standard complexity and code variety witnessed during the last years. Next generation wireless standards such as DVB-S2 [7], IEEE 802.11n (WiFi) [53], IEEE 802.3an (10GBASE-T) [54]. 3GPP-LTE [5] and IEEE 802.16e (WiMAX) [3] often feature multiple codes (e.g. LDPC, Turbo) where each code comes with various code lengths and rates. The necessity for flexible channel decoder intellectual properties (IPs) is evident: however, the design of flexible decoders can be challenging due to the often unforgiving throughput requirements and narrow constraints of decoder latency, power and area. Following these challenges, this chapter presents extensive research in the field of flexible channel decoder architectures: the aim of this study is to produce a flexible, reconfigurable architecture and to tackle its power consumption issues. A study on NoCs and their application to a decoder design is carried out in Section 3.1 and 3.2, while Section 3.3 and 3.4 address the decoder reconfiguration and improve on the previous design. An ad-hoc simulation tool is presented in Section 3.5, and used in Section 3.6 to devise decoder power reduction techniques.

# 3.1 Topologies for NoC-based channel decoding

Even if the implementation of turbo and LDPC code decoders is a well studied problem in the literature, two critical needs emerged in the last years: i) achieving high throughput, ii) granting flexibility and interoperability. The intrinsic differences between the turbo and LDPC decoding algorithms and their iterative nature make the design of high throughput, flexible turbo/LDPC decoder architectures a challenging task.

As said before, in both turbo and LDPC decoders high throughput is generally achieved by employing parallel architectures [55,56], where several processing elements (PEs) perform the decoding algorithm concurrently on different portions of the received frame. However, PEs require a large communication bandwidth and an efficient interconnection structure to concurrently read/write data from/to the memory. High throughput PEs able to support both turbo and LDPC decoding [48–52] can be implemented as Application-Specific-Integrated-Circuits (ASICs) or ASIPs. In general, ASIC solutions achieve higher throughput with lower complexity as compared to ASIP implementations. However, ASIP architectures are usually more flexible than ASIC ones.