# POLITECNICO DI TORINO

### SCUOLA INTERPOLITECNICA DI DOTTORATO

Doctoral Program in Electronic and Communication Engineering

### Final Dissertation

# **Analog-Digital System Modeling for Electromagnetic Susceptibility Prediction**

A case study: Integrated Circuits and Communication Networks in Aerospace Environment

# Michele Fontana

Tutor prof. F. Canavero

Co-ordinator of the Research Doctorate Course prof. I. Montrosset

# **Abstract**

The thesis is focused on the noise susceptibility of communication networks. These analog-mixed signal systems operate in an electrically noisy environment, in presence of multiple equipments connected by means of long wiring. Every module communicates using a transceiver as an interface between the local digital signaling and the data transmission through the network. Hence, the performance of the IC transceiver when affected by disturbances is one of the main factors that guarantees the EM immunity of the whole equipment. The susceptibility to RF and transient disturbances is addressed at component level on a CAN transceiver as a test case, highlighting the IC features critical for noise immunity.

A novel procedure is proposed for the IC modeling for mixed-signal immunity simulations of communication networks. The procedure is based on a gray-box approach, modeling IC ports with a physical circuit and the internal links with a behavioural block. The parameters are estimated from time and frequency domain measurements, allowing accurate and efficient reproduction of non-linear device switching behaviours. The effectiveness of the modeling process is verified by applying the proposed technique to a CAN transceiver, involved in a real immunity test on a data communication link. The obtained model is successfully implemented in a commercial solver to predict both the functional signals and the RF noise immunity at component level.

The noise immunity at system level is then evaluated on a complete communication network, analyzing the results of several tests on a realistic CAN bus. After developing models for wires and injection probes, a noise immunity test in avionic environment is carried out in a simulation environment, observing good overall accuracy and efficiency.

# Acknowledgements

This thesis was financed by EADS Innovation Works, now Airbus Group Innovation, under a collaboration framework with the EMC Group of Politecnico di Torino.

I gratefully acknowledge the EADS support that allowed me to carry out my research activity. In particular, I owe sincere thanks to Richard Perraud, who acted as the reference person with EADS Innovation Works for the project. He has always been very helpful and supportive and he has constantly dedicated high interest to the progresses of my activity. I had also the pleasant opportunity to work with Christian Marot and the other people of the EMC research group at EADS IW in Toulouse, France. I had the opportunity to learn much from them about electronics in avionic environment and many important progresses were achieved by means of the fruitful discussions we held together.

I would also like to thank Prof. Canavero, the advisor of this thesis, for allowing me to carry out my PhD research activity at Politecnico di Torino. His encouragement and support throughout the development of the activity were a relevant factor during my Ph.D. I also wish to thanks the whole EMC Group for making my time an interesting and enjoyable working experience. In particular, I am very grateful to Luca Rigazio and Prof. Ivano Maio for their help in the test measurements carried out in the research lab.

Finally, i would like to thank Dr. Todd Hubing for giving me the possibility of spending four months at the Clemson University International Center for Automotive Research (CUICAR), Greenville, SC, USA. His guidance and his profound experience on PCBs and integrated circuits were invaluable for my work and allowed me to significantly progress in the research development with the analysis of the transient noise effects on a IC in the Clemson Vehicular Electronics Laboratory.

# **Contents**

| Al | Abstract |          |                                                              |     |  |  |

|----|----------|----------|--------------------------------------------------------------|-----|--|--|

| A  | cknow    | ledgem   | nents                                                        | iii |  |  |

| 1  | Intr     | oductio  | n                                                            | 1   |  |  |

|    | 1.1      | Outlin   | e of the Thesis                                              | 2   |  |  |

| 2  | EM       | C of Int | regrated Circuits                                            | 3   |  |  |

|    | 2.1      | Integra  | ated circuit parameters                                      | 3   |  |  |

|    |          | 2.1.1    | Technology and Frequency                                     | 3   |  |  |

|    |          | 2.1.2    | IC current and I/O ports                                     | 5   |  |  |

|    |          | 2.1.3    | Power supply voltage                                         | 7   |  |  |

|    | 2.2      | EM en    | nissions                                                     | 7   |  |  |

|    | 2.3      | EM su    | sceptibility in integrated circuits                          | 8   |  |  |

|    |          | 2.3.1    | Noise margins                                                | 9   |  |  |

|    |          | 2.3.2    | Perturbation effects on digital circuits                     | 10  |  |  |

|    | 2.4      | EM Su    | asceptibility Measurement Techniques                         | 13  |  |  |

|    |          | 2.4.1    | Test Methods for Harmonic Signal Susceptibility Measurements | 13  |  |  |

|    |          | 2.4.2    | Test Methods for Transient Susceptibility Measurements       | 17  |  |  |

|    |          | 2.4.3    | Susceptibility Measurements at System Level                  | 19  |  |  |

|    | 2.5      | EM In    | nmunity Models                                               | 20  |  |  |

|    |          | 2.5.1    | Failure criteria definition                                  | 20  |  |  |

|    |          | 2.5.2    | Circuits Models                                              | 23  |  |  |

|    |          | 2.5.3    | Behavioural Models                                           | 24  |  |  |

|    |          | 2.5.4    | Macromodels                                                  | 25  |  |  |

|    | 2.6      | Chapte   | er Summary                                                   | 31  |  |  |

| 3  | Con      | nmunica  | ation Network Immunity Analysis                              | 33  |  |  |

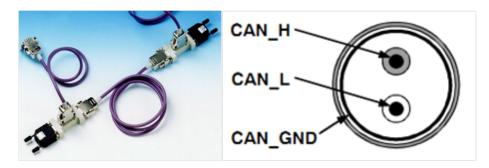

|    | 3.1      | Test C   | ase: Controller Area Network                                 | 33  |  |  |

|    |          | 3.1.1    | Physical Layer                                               | 35  |  |  |

|    |          | 3.1.2    | CAN Transceiver Port Analysis                                | 37  |  |  |

|    | 3.2      | EMC I    | Evaluation of CAN transceiver                                | 40  |  |  |

|    |          | 3.2.1    | Susceptibility to RF noise                                   | 40  |  |  |

|    |          | 3.2.2    | Susceptibility to EFT noise                                  | 44  |  |  |

vi CONTENTS

|    |         | 3.2.3    | Chapter Summary                        | 47        |

|----|---------|----------|----------------------------------------|-----------|

| 4  | IC N    | Aodelin  | g Procedure for EM Immunity Evaluation | 49        |

|    | 4.1     | IC Mo    | deling Procedure                       | 49        |

|    |         | 4.1.1    | Block Structure Identification         |           |

|    |         | 4.1.2    | Logic state static characterization    | 53        |

|    |         | 4.1.3    | Port parasitic element evaluation      |           |

|    |         | 4.1.4    | Internal block behavioural modeling    |           |

|    |         | 4.1.5    | ESD protection structure analysis      |           |

|    | 4.2     | IC Mo    | del Validation                         |           |

|    | 4.3     |          | nity Simulation at component level     |           |

|    | 4.4     |          | er Summary                             |           |

| 5  | Syst    | em-Lev   | el Noise Susceptibility Assessment     | 65        |

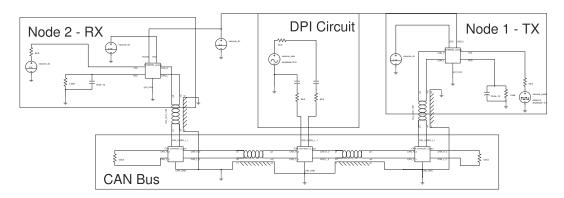

|    | 5.1     | CAN I    | Bus DPI Test                           | 65        |

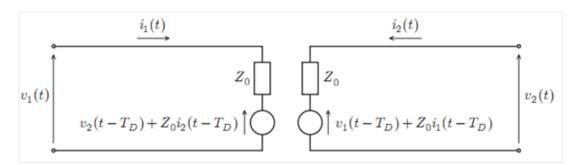

|    |         | 5.1.1    | Cable Characterization                 | 68        |

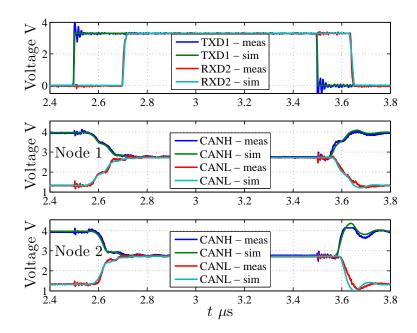

|    |         | 5.1.2    | Noise Immunity Simulation              | 69        |

|    | 5.2     | CAN I    | Bus BCI Test                           |           |

|    |         | 5.2.1    | Injection Probe Modeling               |           |

|    | 5.3     | Chapte   | er Summary                             |           |

| 6  | Con     | clusions | S                                      | <b>79</b> |

| Li | st of A | Acronyr  | ms                                     | 81        |

| Li | st of I | Publicat | tions                                  | 89        |

# Chapter 1

# Introduction

Electromagnetic Compatibility (EMC) is defined as the ability of an equipment or a system to perform satisfactorily in its electromagnetic environment without introducing intolerable interference into any other electrical apparatus in that environment. The electromagnetic compatibility concerns two main phenomena, that are the emission of spurious noise and the susceptibility, either conducted or radiated.

The electromagnetic compatibility is a key factor in the design of electronic systems and equipments. In the past few years the ability of Integrated Circuits (IC) to safely operate in an environment of increasing interferences from radio frequencies has been reduced. Concerns related to EMC increased when low emission and high immunity to radio-frequency interference (RFI) signals appeared as performance factors in integrated circuits. The evolution of electronic components parameters required deep understanding of sources affecting EMC of electronic systems. The increasing complexity of ICs associated with growing problems related to immunity and emission led to the development of susceptibility and emission models. The models are used not only by IC manufacturers to check if components pass EMC specifications, but also by users to test the EMC at system level. The development of a model reproducing the EMC behavior of a component is a real challenge, since it must be sufficiently specific and compatible with simulations proposed by the most common tools. In most cases, the validity of EMC models is based on the quality of the characterization of certain parameters. EMC characterization requires knowledge in terms of methodology and EMC standards.

The measurement standards provide methods to extract the emission spectrum and susceptibility level, either conducted or radiated in integrated circuits. Integrated circuits, with system internal oscillations, are important sources of electromagnetic pollution, attacking certain frequency bands by means of conducted or radiated coupling and considerably degrading wireless communications and even endangering the security of some systems.

This thesis focuses on the IC modeling of electromagnetic immunity, analyzing the effects of interferences on analog and digital circuits. In particular, the main topic is the analysis of ICs used in communication networks and buses, as their use is often required in noisy environments where high levels of electromagnetic interference (EMI) affects the usual functionality. The IC performance is assessed firstly at component level and afterwards at equipment level according to official standards depending on the context in which they are used. The development of a

2 Introduction

novel procedure to model the behaviour of complex mixed-signal ICs will be proposed to take into account the susceptibility features in a simulation environment. The goal of the activity is to be able to simulate the robustness to noise of a complete communication system. The obtained voltage and current signals are computed under the noise stress and used by the designer to evaluate the system performance, checking the compliace to official standards in an early design phase.

The activity was carried out in the EMC Group of the Department of Electronics and Telecommunication of Politecnico di Torino, Italy. EADS Innovation Works (IW) financed the research and several tests in avionic environment were done in the EADS IW labs in Toulouse, France. Furthermore, the activity related to the immunity analysis towards transient noise has been done in Clemson Vehicular Electronics Laboratory (CVEL) of Clemson University International Center for Automotive Research (CUICAR) located in Greenville, SC, USA.

### 1.1 Outline of the Thesis

The outline of this thesis is as follows.

In Chapter 2, EMC-related features of ICs are considered. The technological trend, the strong scaling of IC parameters and the reduced noise margins are highlighted as a main reason for the growing EM emission and susceptibility problems. The main effects of EMI on digital designs are highlighted and the test setups for measuring IC susceptibility to RF and transient noise are detailed. Afterwards, a summary of the available IC models for immunity characterization is presented.

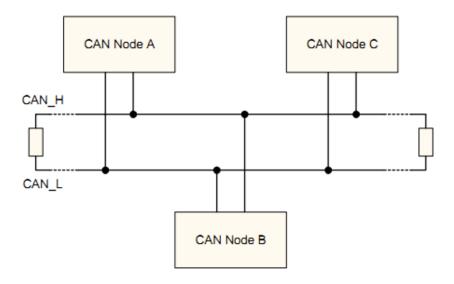

Chapter 3 outlines a thorough analysis of the IC immunity in communication networks at component level. The IEC characterization of a Controller Area Network (CAN) transceiver performance when affected by noise is detailed and carried out on several ICs as a test case. The impact of RF and transient noise on CAN bus is evaluated analyzing non-linearities and the non-idealities limiting common-mode noise rejection.

In Chapter 4, a novel modeling procedure based on an Analog Mixed-Signal (AMS) block structure is described, for the generation of IC immunity models from real measured data. Its accuracy is validated on a CAN transceiver model, comparing the immunity threshold obtained from measurements with simulation data.

In Chapter 5, the CAN network susceptibility to RF noise is addressed at system level. Shielded twisted wires are characterized as transmission lines and their impact on the global system immunity is analyzed in different test setups. Modeling the noise injection capability of an injection probe, the immunity of a CAN bus is evaluated by simulation and validated with measurements.

Chapter 6 provides the main conclusions that can be drawn from the results of this Thesis.

# **Chapter 2**

# **EMC of Integrated Circuits**

The design of electronic systems becomes more and more complex. The push for functionality is ever increasing, while cost and time-to-market should be kept as low as possible. At the same time, as technology advances, new challenges show up, also because the environment in which the equipment is supposed to operate becomes harsher. In modern equipments the functionality is embedded in one or more integrated circuits through the use of analog and digital electronic circuits. Substrate noise modeling and EMI have become dominant noise sources in mixed-signal designs. The root cause of any failure due to susceptibility can be always brought back to an electronic component being unable to withstand the interference. In the following sections, a research upon state-of-the-art EMC topics related to integrated circuits is presented.

## 2.1 Integrated circuit parameters

In the past few years, an evolution of physical and electrical parameters of electronic components has occurred. A research [1] collected informations and trends about integrated circuit technology. The results are summarized in the International Technology Roadmap for Semiconductor (ITRS,[2]), which provides very detailed insight into the evolution of the microelectronics industry, highlighting trends, technology targets, and milestones for the next 15 years. It also describes the evolution of EMC problems in the years to come with the technological evolution of semiconductors and electric parameters. Another road-map focuses on design automation tools with a chapter related to EMC [3]. From these road-maps, a subset of parameters and associated trends has been extracted, focusing on the processor frequency, gate currents, I/O trends, and noise margin evolution.

#### 2.1.1 Technology and Frequency

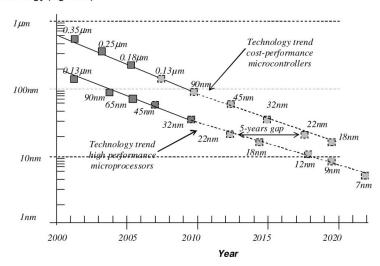

Studies on semiconductor technology have shown significant advancement on the next technological steps of ICs. Fig. 2.1 shows IC technology scale-down over the next years for high-performance microprocessors and cost-performance microcontrollers. It can be seen that the embedded microcontrollers use technologies nearly five years after their introduction in high-end microprocessors. This technological reduction related to MOS channel length follows a linear

trend. High performance microprocessor technology in a decade passed from 0.13  $\mu m$  in 2000 to 32 nm in 2010. In the same time microcontrollers passed from 0.35  $\mu m$  to 90 nm. With each lithography scaling step, the linear dimensions are reduced approximately by a factor of 0.7 such that the silicon area is reduced by a factor of 2. By 2022, the ITRS road map projects the minimum physical gate length of transistors to be close to 7 nm, which is considered by most researchers to be the physical limit of silicon.

#### Technology (log scale)

Figure 2.1. Technology scale-down toward nano-scale devices associated with microprocessor and microcontroller manufacture [2]

Figure 2.2. Microprocessor and microcontroller frequency increase until 2020 [2].

The microprocessor frequency depends on the channel length of IC transistors, therefore their

speed increases with technology scale-down. Fig. 2.2 shows the frequency evolution of microcircuits according to the technological dimensions.

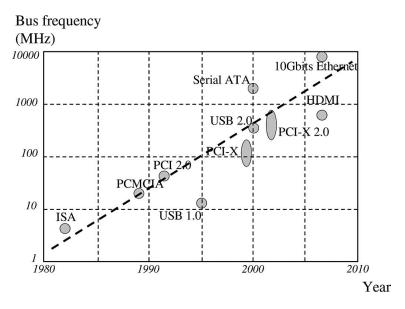

Figure 2.3. Frequency increase of data bus transfer [2].

According to ITRS 2007, the on-chip clock frequency is increasing (14 GHz predicted for 2012) as well as the communication speed between chips. To reach these higher speeds and reduce power requirements, ICs are designed with transistors that require less supply voltage (0.5 V in 2022) to lower the power consumption. As logic thresholds reduce accordingly, the noise margin is going down, resulting in more vulnerability to EMI. By 2022, processors are expected to run at 20 GHz; the saturation scenario considers several limiting factors such as MOS mobility degradation, interconnect delay, and power dissipation. Parallel architectures may compensate for these limitations while maintaining the pace in performance improvements.

The frequency increase also concerns the data transfer between ICs, as shown in Fig. 2.3. Universal Serial Bus (USB), Peripheral Component Interconnect (PCI), and serial Advanced Technology Attachment (ATA) protocols have been developed to operate around 1 GHz while new protocols approaching 10 GHz have been specified with an increased bandwidth to support ultrahigh-speed data transfer.

#### 2.1.2 IC current and I/O ports

The technology evolution of semiconductors leads to a reduction of gate currents; as shown in Table 2.1, switching currents decrease with the smaller size of channel transistor. Intrinsically, this should have a positive impact on the transient switching noise. However, the steady increase in IC complexity, power consumption, and faster switching speeds jeopardizes these benefits in terms of *di/dt* noise. Even if peak current amplitude consumed by a gate is constantly decreasing, the number of simultaneously switching gates increases especially when many functions are working in parallel on the same circuit. In high density circuits such as microprocessors, hundreds of

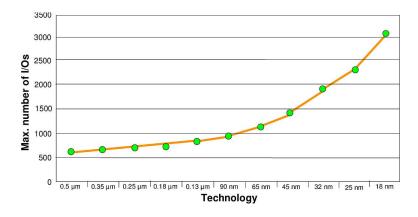

thousands gates switch at the same time, causing high amplitude current peaks. Moreover, starting with 90-nm technology, chips with more than 1000 I/Os may be designed. The simultaneous switching of active buffers may thus be the dominant contributor to parasitic emissions. Fig. 2.4 shows the evolution of the maximum number of I/Os per chip, which follows a quasi-exponential law. An accurate evaluation of I/O behavior and its transient current consumption are of utmost importance for emission and immunity prediction.

| Technology     | External supply (V) | Average Current (A) | Gate density (/mm²) | Gate current peak (mA/gate) | Capacity (fF/gate) |

|----------------|---------------------|---------------------|---------------------|-----------------------------|--------------------|

| 1.2 µm (1985)  | 5 V                 | <1                  | 8 K                 | 1.1                         | 60                 |

| 0.8 µm (1990)  | 5 V                 | <1                  | 15 K                | 0.9                         | 40                 |

| 0.5 µm (1993)  | 5 V                 | 3                   | 28 K                | 0.75                        | 30                 |

| 0.35 µm (1995) | 5-3.3 V             | 12                  | 50 K                | 0.6                         | 25                 |

| 0.25 µm (1997) | 5-2.5 V             | 30                  | 90 K                | 0.4                         | 20                 |

| 0.18 µm (1999) | 3.3-2.0 V           | 50                  | 160 K               | 0.3                         | 15                 |

| 0.12 µm (2001) | 2.5-1.2 V           | 150                 | 240 K               | 0.2                         | 10                 |

| 90 nm (2004)   | 2.5-1.0 V           | 186                 | 480 K               | 0.1                         | 7                  |

| 65 nm (2006)   | 2.5-0.7 V           | 236                 | 900 K               | 0.07                        | 5                  |

| 45 nm (2008)   | 1.8-0.8 V           | 283                 | 2000 K              | 0.05                        | 3                  |

Table 2.1. Evolution of key parameters versus technology node [2].

Figure 2.4. Maximum number of I/Os in ICs [2].

2.2 – EM emissions

#### 2.1.3 Power supply voltage

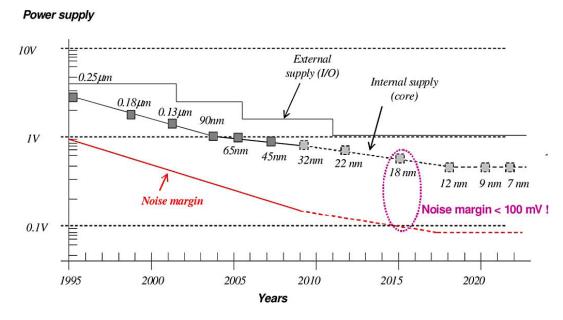

The trend in terms of IC technology is the steady decline of supply voltages. In Fig. 2.5, variation of supply voltages in future technologies is shown. The external I/O supply, which represents the nominal voltage of the technology, varies step by step (5 V, 3.3 V, 2.5 V, 1, 8 V). The supply voltage decreases with technology scale-down from 5 V to 1 V in 90 nm; the reduction of noise margin associated with lower supply voltages is noticed. The noise margin has been reduced by a factor of 10 in 20 years and goes below 100 mV in 2015. The power supply voltages of integrated circuits are steadily reduced in order to reduce the consumption of the circuits and to allow the reduction of oxide thickness and hence increased switching speeds. The supply voltages of integrated circuits do not decrease at the same rate as the reduction in the size of transistors for two reasons: the threshold voltage of transistors decreases with increasing leakage current and voltage levels are standardized to ensure the compatibility between interconnected systems or circuits. A reduced noise margin means an increased sensitivity to external interference.

Figure 2.5. Continuous decrease of power supply voltages [2].

#### 2.2 EM emissions

The EM spurious emissions arise in electronic components from the current used during switching of elementary circuits such as inverters. The evolution of transistor technologies and the abundance of elementary circuit logic within the electronic components involve greater power consumption and increased noise. The performances of microprocessors, using multiple clocks with different frequencies, and of ICs at higher operating frequencies create spurious emission spectra towards the high frequencies which could disrupt sensitive applications. Assessments were done on integrated circuit improvements expected for the next years and spurious emission levels until 2020

Figure 2.6. Evolution of the peak emission level over the last few years and projection until 2020 [1].

are shown in Fig. 2.6, given the requirements of both IC manufacturers and customers. Without any EMC optimization strategy, the parasitic emission will increase in the next years. IC users show a strong demand for fabrication of electronic devices with low emissions. Integrated circuits built without EMC optimization suffer from high noise emissions and require decoupling capacitors, protection and filtering at the circuit board. In early 2000, the gap was reduced by almost 20 dB between noise emissions levels of EMC non-optimized ICs and those that incorporate new EMC design rules. Without EMC optimization, the technology trend toward more complex and faster designs is expected to lead to increased emission levels (Fig. 2.6, upper curve). Although EMC optimization techniques have partially filled the gap between IC customer requests and IC performance (Fig. 2.6, middle curve), new innovative techniques need to be investigated to compensate for the induced parasitic effects of technology scale-down. In 2020, the required efficiency of these techniques should allow a reduction in unintended emissions of 40 dB. Despite these continuous efforts, there is a gap between IC customer requests and intrinsic IC performance. Not only do generic low-emission design guidelines need to be generalized and integrated in design flows, but advanced design techniques should also be applied to respond to IC customer pressure for less conducted and radiated noise.

# 2.3 EM susceptibility in integrated circuits

The origin of IC susceptibility lies in many physical phenomena. The use of radio link and integrated circuits more or less noisy generates an electromagnetic field in a non-negligible space where many critical electronic components can be found; conducted and radiated disturbances are transformed into currents and voltages in integrated circuits, which can cause malfunction or even destruction. The main sources of electromagnetic fields are natural, such as lightnings, or produced by other electronic components such as equipment, mobile phones, radar sources and

wireless base stations that can generate RF interference in integrated circuits. EM disturbances can be classified according to their energy levels and their frequency bands. As it is explained later in the document, disturbances act in different ways according to if their fundamental frequency is included or not in the operating bandwidth of the integrated circuit.

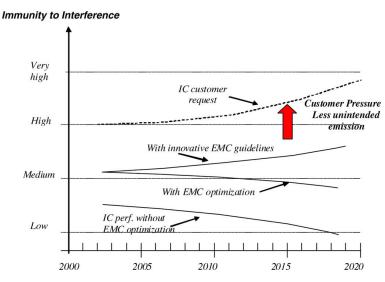

Figure 2.7. Diverging trends between IC immunity requirements and increased susceptibility with technology improvements [1].

The technological trend toward lower noise margins, the growing integration of I/O structures and higher bus speeds should lead to increased susceptibility of integrated circuits for radio frequency interference. Fig. 2.7 shows the different trends in the evolution of IC susceptibility: customer requirements and IC performance with and without EMC optimization. The actual level of IC immunity, without EMC performance, is low and tends to decline in the years to come. With the application of EMC design rules an increase in component immunity is expected in the future. Generic high-immunity design guidelines should be introduced in design flows, as a response to IC customer pressure for higher immunity.

#### 2.3.1 Noise margins

The reduction of supply voltages in MOS technology has a direct impact on the inner workings of digital ICs, particularly regarding thresholds of logic gates. Each MOS circuit technology operates according to a standard voltage levels for I/O, which represent the two logic states. The voltage levels associated with each state accept a tolerance zone limited by specified voltages:  $V_{IH}$  and  $V_{OH}$  for high logic state and  $V_{IL}$  and  $V_{OL}$  for low logic state. In order to guarantee nominal operation of the circuit, the definition of switching zones must comply with rules assuring a certain immunity to noise. The noise margins are directly related to circuits supply voltages, meaning that they depend on the evolution of MOS technologies. Fig. 2.5 compares threshold levels of different CMOS technologies. Table 2.2 shows the evolution of high level noise margins  $(NM_H)$  and low level noise margins  $(NM_L)$  for digital design technologies. It is clear that the constant decline in

noise margins makes integrated circuits more sensitive, significantly increasing the susceptibility of electronic components.

| Technology | $V_{OH}$ | $V_{IH}$ | $NM_H$ | $V_{IL}$ | $V_{OL}$ | $NM_L$ |

|------------|----------|----------|--------|----------|----------|--------|

| CMOS 5V    | 4.44V    | 3.5V     | 0.94V  | 1.5V     | 0.5V     | 1V     |

| CMOS 2.5V  | 2.3V     | 1.7V     | 0.6V   | 0.7V     | 0.2V     | 0.5V   |

| CMOS 1.8V  | 1.2V     | 1.17V    | 0.03V  | 0.7V     | 0.45V    | 0.25V  |

Table 2.2. Noise margin evolution in CMOS technology

### 2.3.2 Perturbation effects on digital circuits

Digital integrated circuits are inherently less susceptible to EM interference than their analog counterparts: a natural resistance against EM disturbances is given by voltage thresholds between logic levels, leading to a higher immunity to interferences; however this does not mean that they are completely immune to it. EMI has been observed to have two distinct effects on digital devices [4, 5, 6]. The first one is false switching or static failure, which occurs when interference is of sufficient amplitude to cause an otherwise static logic signal to appear to change state. The second effect is that of EMI-induced delays. It has been observed that significant changes in the propagation delay of a device occur at much lower amplitudes of EMI than those that cause false switching. These changes lead to violations of critical timing constraints, such as the minimum set-up and hold times of flip-flops, which are referred as dynamic failure. Unlike static failures, dynamic failures are dependent on the phase of the EMI relative to a logic transition. In a worst case situation, depending on the total EMI level, digital integrated circuits can fail a complete data transmission because some significant bits were permanently flipped into another state owing to a particularly strong EMI injection. Nevertheless, as long as realistic EMI levels are considered and if some basic precautions are taken in order to reduce and prevent the injection of EMI into the circuit, digital ICs exhibit a higher immunity to EMI than analog ones, because of their threshold levels.

The coupling of an interference with a circuit may lead to different results and their effects are classified according to electrical and physical damages they provoke:

- Single error: the disturbance signal is interpreted as a valid logic input and a wrong output signal is generated [7].

- Repeated error: the disturbance signal is continuously applied on the circuit leading to a long-term degradation.

- Irreversible error: the circuit is driven by an interference signal into an instable state where chaos phenomena are observed [8].

- Physical damage: high-power transient signals can provoke physical damages in the circuit such as cracks or melted components; Elecro-static discharges cause such type of harm due to localized heating which melts certain circuit elements [9].

In the following sections, examples of digital errors due to harmonic signal interferences are shown, obtained from HSpice simulation of a TI SN74AHC04 buffered inverter model; errors are characterized visualizing the output signal with and without superimposing disturbance in the input port.

#### Static errors

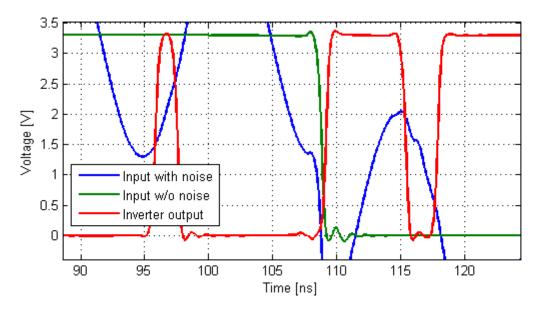

Figure 2.8. Static error due to harmonic interference

The disturbance signal superimposed to input signal produces incorrect changes of the logic level of the output. Such errors are defined as "glitches" and their presence is strongly linked to the EM interference amplitude. From a functional point of view, a glitch appears when the sum of logic input signal and interference overcomes the noise margin and the commutation threshold.

In Fig. 2.8 glitches are caused by a harmonic signal with a 2 V amplitude superimposed on the inverter input signal, whose power supply voltage is  $V_{dd}=3.3$  V. A similar scenario is found if the circuit is disturbed by a transient signal, such as a pulse, or if an interference couples with power supply voltage or with clock signal [10], affecting the whole circuit behavior instead of only a single component.

#### **Dynamic errors**

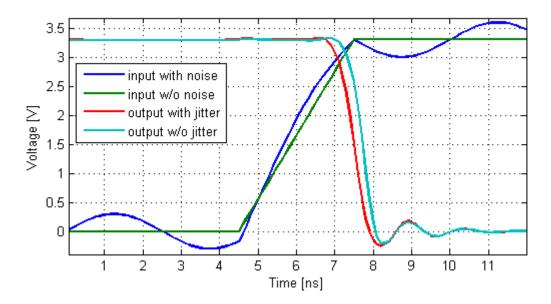

This error type appears during logic signal commutations; the disturbance effects upon logic commutations cause two effects depending on interference amplitude: jitter and pseudo-commutations. The output is affected by jitter when an input signal influenced by interference during the logic commutation phase crosses voltage threshold  $V_{IH}$  or  $V_{IL}$  earlier or later than expected, therefore modifying propagation time  $t_p$  through the logic gate that could lead to violations of critical timing

constraints. In Fig. 2.9 jitter is caused by a harmonic signal with a 0.4 V amplitude superimposed on the inverter input signal, provoking an output logic commutation after  $t_p=1.2$  ns instead of standard  $t_p=1.5$  ns propagation time obtained from the inverter data-sheet.

Figure 2.9. Jitter caused by harmonic interference

Pseudo-commutations appear when input signal rise or fall time is slow compared to harmonic interference period; the input signal crosses the voltage logic thresholds  $V_{IH}$  and  $V_{IL}$  multiple times leading to additional spurious commutations on the output port.

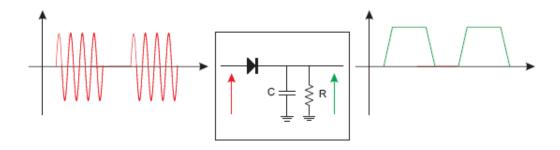

#### Rectification

EM interference effects on IC are divided in literature into In-Band or Out-Band perturbation depending on whether the disturbance signal bandwidth is included or not into the IC operating frequency range; the distinction is done due to the different EMC problems they provide. As shown in Fig. 2.10, an out-band high frequency disturbance, reaching a sensitive and non-linear circuit node in an integrated circuit, mixes with the wanted signal and induces a non linear distortion [11] known as *rectification*. It has been first observed in PN junctions of bipolar transistor [12, 13] and it refers to the distortion of the signal amplitude as well as to the position of spectral components. When nonlinear circuits are excited with a sinusoidal signal, the frequency spectrum of the output contains a spectral component at the original fundamental frequency, as well as spectral components at multiples of the fundamental frequency (harmonic frequencies) [14]. Harmonic distortion is particularly harmful because the harmonic components associated with the nonlinear distortion of a sinusoidal out-of-band EMI signal, may appear in the signal band, even if the EMI frequency band is not interfering with the wanted signal band. From then on, filtering or removing interfering EMI harmonic component(s) becomes very difficult.

Moreover, a component at DC appears as well, depending on the even-order nonlinear behavior

Figure 2.10. Rectification effect caused by harmonic interference

[15]; the DC shift phenomenon, which arises when this DC component is accumulated (e.g. in a capacitor), is extremely harmful because the correct DC operating region of a given circuit may radically change under influence of an interfering EMI signal.

### 2.4 EM Susceptibility Measurement Techniques

Several different experimental techniques described in this section have been developed to describe the impact of disturbances on the functional behavior of integrated circuits. The main objective of these measures is to determine frequency and disturbance power levels which the circuit under test is susceptible to; EM susceptibility criteria are defined upon observable physical quantities such as IC output voltages. The disturbance origins can be very different and interference signals present various time domain waveforms. The disturbance waveform is clearly important as it affects the interfering signal coupling with the device under test and therefore the susceptibility measurements; the relevance of measures outcomes will be acceptable only if the injected signal is as close as possible to the disturbance type under review. Waveforms of EM disturbances can be divided into two categories:

- Harmonic signals: a sinusoidal signal is injected in the DUT either at a fixed frequency

and power level (continuous wave) or amplitude modulated in order to observe how the

circuit behaves when attacked by a constant disturbance. EM susceptibility measurement

techniques for harmonic signals are grouped under the standard IEC 62132 [16].

- Transient signals: these disturbances present various waveforms and their effects mainly depend on the energy contained in pulse and transition times. The spectral content of this type of aggression could reach very high frequencies due to fast rise and fall times. Susceptibility measurement methods for impulses, Electrostatic Discharge (ESD), Electrical Fast Transients (EFTs), Surges and Electrical Over-Stress (EOS) are described in the standard IEC 62215 [17].

#### 2.4.1 Test Methods for Harmonic Signal Susceptibility Measurements

Tests are performed by injecting a continuous disturbance signal or an amplitude modulated one with a power-amplified signal generator. Differences between test methods depend on the config-

uration set up to inject the signal into the circuit. The standard IEC 62132 [16] is dedicated to IC susceptibility to RF over a frequency range originally up to 1 GHz. The most mature susceptibility measurements are the WBFC, BCI and DPI approaches which guarantee a high degree of repeatability and correlation, but recently some additional methods have been proposed, as detailed in Table 2.3.

| Standard    | Description                                   | Stage in 2011          |

|-------------|-----------------------------------------------|------------------------|

| IEC 62132-1 | General Conditions and Definitions            | International standard |

| IEC 62132-2 | TEM-Cell and Wide-band TEM-Cell Method (GTEM) | International standard |

| IEC 62132-3 | Bulk Current Injection (BCI)                  | International standard |

| IEC 62132-4 | Direct RF Power Injection (DPI)               | International standard |

| IEC 62132-5 | Work Bench Faraday Cage (WBFC)                | International standard |

| IEC 62132-6 | Local Horn Injection Antenna (LIHA)           | New proposal           |

| IEC 62132-7 | Mode Stirred Chamber                          | New proposal           |

| IEC 62132-8 | IC Strip-line                                 | New proposal           |

| IEC 62132-9 | Near Field Scan Immunity (NFSI)               | New proposal           |

Table 2.3. Standard IEC 62132 - Measurement of IC susceptibility

#### **Direct Power Injection - DPI**

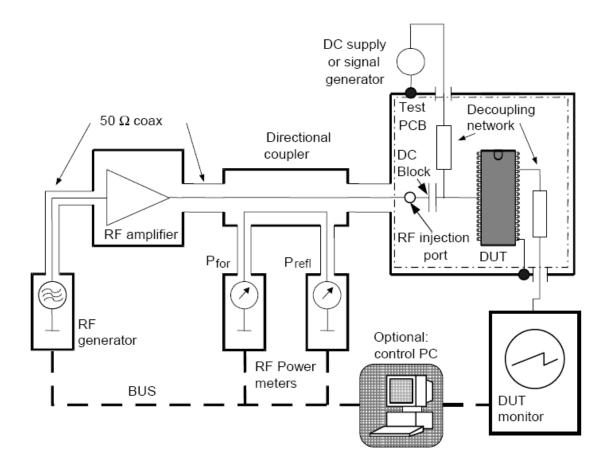

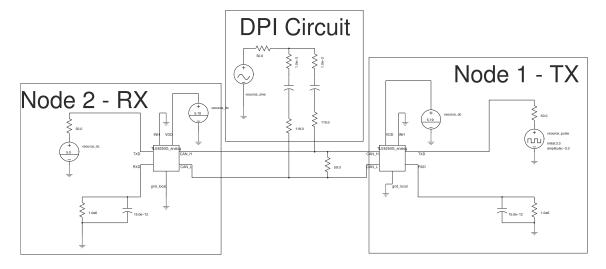

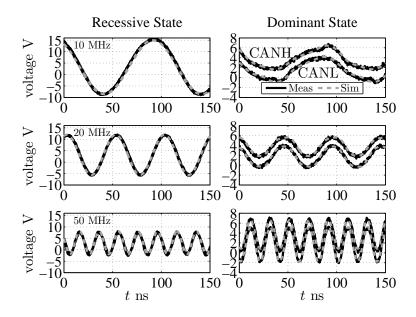

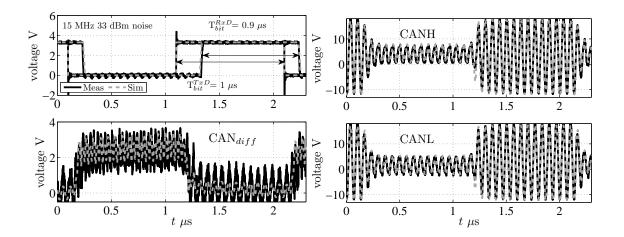

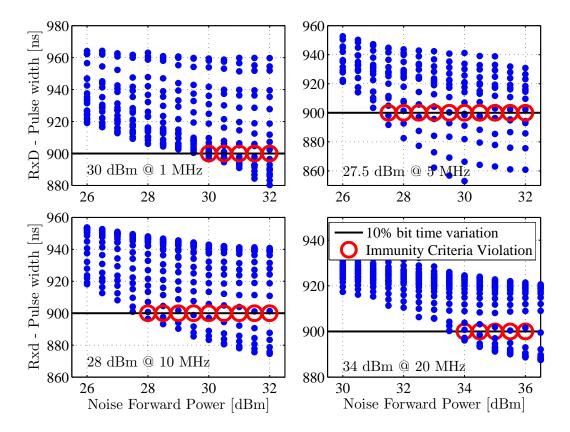

This measurement technique is described in the standard IEC 62132-4 [18] and in a frequency range between 150 kHz and 1 GHz. The measurement setup is shown in Fig. 2.11.

The frequency variable RF generator provides the disturbance that is amplified by the connected RF amplifier. The directional coupler and the RF power meters are used to measure the actual forward power injected into the DUT. At the RF injection port the RF power is delivered to the test PCB. To avoid supplying DC into the amplifier output, the RF amplifier is decoupled by a DC block, which is by default a capacitor of 6.8 nF. The DC supply is prevented from getting RF power by a decoupling network that has a high RF impedance on the side that is connected to the RF injection path.

To monitor the behavior of the DUT, an oscilloscope can be used; to decouple the RF signal crosstalk of the DUT from the low frequency measurement performed by the oscilloscope, a second decoupling network is used. In order to understand the influence of each individual pin, each pin that is expected to be exposed to RF disturbance should be tested individually. Multiple pin testing is permissible into pins of differential mode systems.

The nature of this measurement makes it very suitable to be incorporated directly in circuit simulators.

#### **Bulk Current Injection - BCI**

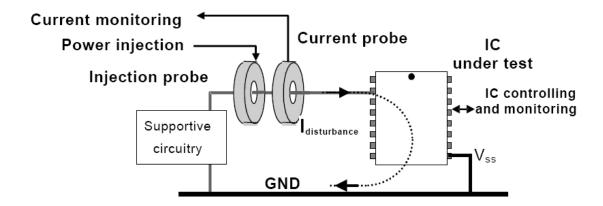

This method is used to inject a disturbance current in a DUT. This technique is derived from a standard measurement technique for characterizing automotive equipment and is currently defined in a frequency range between 150 kHz and 1 GHz in the standard IEC 62132-3 [19]. The measure-

Figure 2.11. Direct Power Injection measurement setup

ment reproduces the induced current that is generated in the real world by electromagnetic field coupling into the wires of a system.

Two electrically shielded magnetic probes are clamped on one or a combination of wires that are connected to the DUT, as depicted in Fig. 2.12. The first probe is for the injection of RF power that induces the disturbance current onto the wires. The second probe is used for monitoring the induced current on the same wires. The disturbance current flows in a loop comprising: wires, the selected IC's pins to the power supply voltage, ground path and supportive circuitry. This supportive circuit provides the IC functional elements as source and load. The supportive circuitry is directly connected to the IC. When the equivalent RF impedance of the supportive circuitry is larger than 50  $\Omega$ , then a bypass capacitor is recommended. The by-pass capacitance, to be used at the supportive circuitry side, may also be needed to confine the loop area in which the induced current will be flowing. The main problem which prevents this measurement method to be used in circuit simulations is the fact that the magnetic coupling between the current probe and the wire is not exactly known; moreover, it is difficult to inject the current in a specific pin due to probe volume.

Figure 2.12. Bulk Current Injection measurement setup

### Work Bench Faraday Cage - WBFC

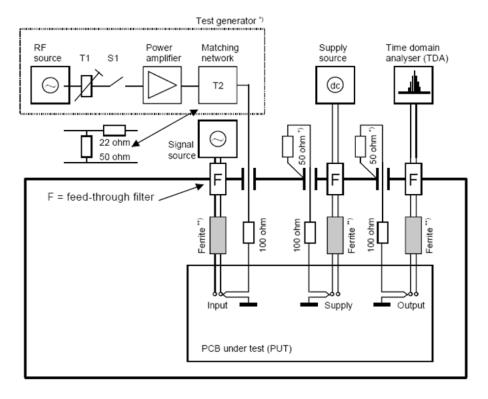

The workbench Faraday cage is a standard method [20] for carrying out conducted immunity measurements to EM common mode disturbances in a 150 kHz - 1 GHz bandwidth.

Figure 2.13. Work Bench Faraday Cage measurement setup

The IC is inserted into a Faraday cage in order to isolate the circuit from the external EM

environment, as depicted in Fig. 2.13. The disturbance signal is injected through a conducted resistance on the circuit. Filters are inserted at each interface of the cage to limit the spreading of RF in measuring devices. However, the scope of this measurement setup is very restricted, since it is only applicable to electronic products that are connected to external wiring: it is therefore not a suitable measuring method to measure e.g. small wireless appliances. Finally, this method is not practical to simulate.

#### 2.4.2 Test Methods for Transient Susceptibility Measurements

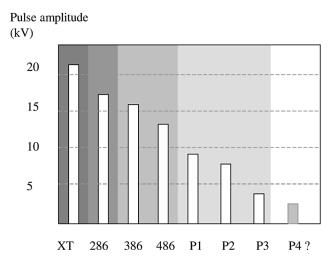

The need to characterize the susceptibility of circuits is not limited to study the effects of harmonic disturbances. Indeed, these past few years many publications have shown that circuits were more sensitive to transient disturbances. M. Camp and H. Garbe research [21] evaluates the effects of fast transients on several PC hardware architectures, and it appears that the transient susceptibility of circuits increases with the arrival of new generations of processors as summarized in Fig. 2.14. The joint contribution of lower supply voltages, the increased integration of transistors and higher frequencies of operation are the main reasons for this decrease of immunity of integrated circuits.

Figure 2.14. Immunity to transients tends to decrease with computer generation [21].

In recent years, the majority of analyses and studies on the characterization of the immunity of circuits to transient disturbances are about the effects of electrostatic discharge (ESD). However, transient disturbances are not limited to ESD; the disruptive effect of different types of transition depends on the energy they carry and therefore on their electrical characteristics such as their waveform, amplitude, rise time, duration, and repetition rate. The different transients are defined in the following way:

- ESD [22]: transfer of electric charge between bodies at different electrostatic potentials in proximity or through direct contact.

- 2. EFT [23]: test with bursts consisting of a number of fast transients, coupled into power supply, control, signal or earth port of electronic equipment. Significant parameters for the

test are the high amplitude, the short rise time, the high repetition rate and the low energy of the transients. They are generated from the interruption of inductive loads, relay contact bounce, etc.

3. Surge [24]: transient wave of electrical current, voltage, or power propagating along a line or a circuit and characterized by a rapid increase followed by a slower decrease. It is generated by a power system switching or by a lightning stroke.

Transient signal energy is certainly low, but the probability that a disturbance of this type affects an electronic circuit is relatively high. Indeed, in the semiconductor industry, these natural disturbances are one of the main causes of component failure [9], along with Electrical Overstress (EOS). EOS disturbances include many different types of pulses and they include high-energy disturbances such as lightning and electromagnetic pulse. Damages caused by this type of disturbance are generally large and can cause interconnection destruction and oxide breakdown. There are many mechanisms of generation of transients, which give rise to short pulses with relatively large voltages and currents. Transients is a source of disturbance whose threat to electronic systems is increasing, and more particularly to ICss; therefore manufacturers must address these problems during the qualification phase of their products. Testing methods were developed and standardized in order to study circuit robustness.

#### **Very Fast Transmission Line Pulsing - VF TLP**

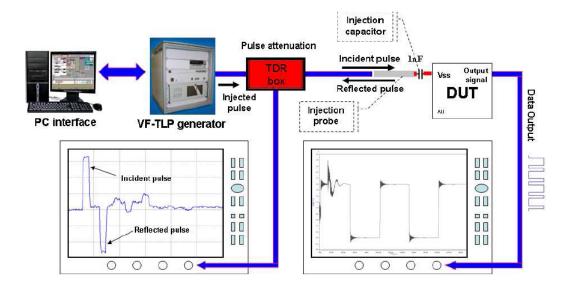

Figure 2.15. VF-TLP test bench

Over the years new ways of testing have emerged to characterize the behavior of electrical circuits in high current environment when stressed by ESD or other transients. So far Transmission Line Pulsing (TLP) [25] and Very Fast Transmission Line Pulsing (VF-TLP) tests [26] have

been introduced to describe respectively the sensitivity of the circuits of a Human Body Model (HBM) and Charged Device Model (CDM) ESD stress. These techniques are used to obtain a I-V static characteristic of ESD protection structures to extract the essential parameters for optimization. However, these testers are not limited only to this type of experiments since they allow to characterize the susceptibility level of integrated circuits to ESD. In fact, ESD is now regarded as an electromagnetic interference which can cause errors in integrated circuits. This type of study is done to determine the ESD levels of disturbance for which there appears a failure: it is an ESD characterization at the functional level. Studies based on the measurement principle VF-TLP were used to analyze the effects of disturbances on simple circuits and complex operating conditions [27]. This test bench is composed of a pulse generator controlled by a computer used to control the electrical parameters of the pulse (width and amplitude). An oscilloscope is added to the system in order to visualize the pulses injected into the circuit and it is connected to a Time Domain Reflectometry (TDR) box which allows to view independently incident and reflected pulses. This measurement method is similar to the DPI method because the ESD pulses are directly injected into a line connected either to supply or to ground via a capacitance selected to not filter the interfering signal. The different results obtained with this method confirm that the VF-TLP pulse generator itself is an excellent solution to evaluate the susceptibility of an integrated circuit operating during transient interference signals. This technique is particularly useful in the evaluation of the behavior of integrated circuits during a fast transient because it allows to choose the configuration of input pulses. However, this technique requires the establishment of a test bench incorporating relatively expensive equipment, which may limit its use.

#### 2.4.3 Susceptibility Measurements at System Level

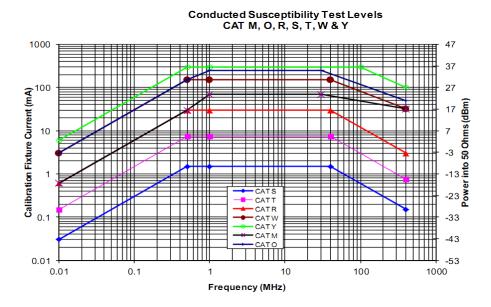

The main test for conducted susceptibility testing of electronic systems is the widely used Bulk Current Injection (BCI). A number of reasons make this technique extremely attractive. On one hand, BCI permits a susceptibility screening at the early design stages of units and subsystems at moderate costs and with limited investment of time. On the other hand, it is a fast and noninvasive procedure, and allows for onboard testing in case of large and complex systems. Consequently, BCI-based techniques have progressively gained the attention of several international standards, spanning from the aerospace [28] to the automotive [29] sectors. For the avionic environment, the BCI test determines whether equipment will operate within performance specifications when the equipment and its interconnecting wiring are exposed to a level of RF modulated power from 10 kHz to 400 MHz, by injection probe induction onto the power lines or on the interface circuit wiring. The test is made to qualify an equipment into a category defining the conducted RF test levels it can withstand, according to the thresholds depicted in Fig. 2.16. The category to be applied to a system or equipment frequently must be chosen before the internal RF environment of the aircraft is known. Further, many systems or equipments are designed with the intent that they will be installed in several different types of aircraft. Therefore the equipment manufacturer should design, test and qualify the equipment to the category consistent with expected location, exposure and use.

Figure 2.16. Minimum RF immunity level for aerospace systems depending on equipment category.

### 2.5 EM Immunity Models

The analysis of susceptibility is not limited to the characterization on a real experimental basis; there is a need to develop models for predicting susceptibility of the IC because, in the design phase of integrated circuits, experimental methodologies for immunity characterization are not available. The model must be able to predict with good precision the circuit behavior differences after being attacked by interference signals with varying amplitudes and waveforms, while remaining simple enough to keep simulation time to a minimum and to facilitate integration of the model into the stream of design tools. Moreover it is important to implement an immunity model taking into account the circuit non-linear behaviour. However all these features which an immunity model should have are in conflict with each other and this makes the operation of building an immunity model a complex research task and not fully mature yet. In this section the main strategies of immunity modeling at different levels of abstraction are shown and several immunity models are overviewed.

#### 2.5.1 Failure criteria definition

In order to be able to predict the susceptibility of an integrated circuit during the design phase, the definition of a failure criterion is required; after simulation, data is processed to check if signals are in agreement with the chosen failure criterion. The interference signal amplitude is increased until failure criterion on observed signal output is violated. In this paragraph a list of failure criteria at integrated circuit level is presented, which can be easily checked in a simulation environment.

#### **Template waveforms**

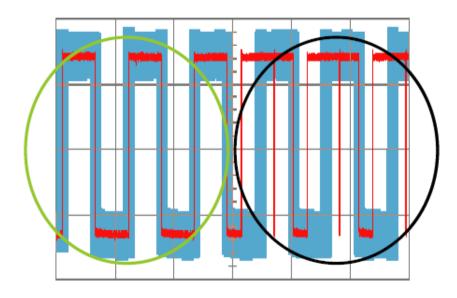

When checking immunity on ICs, several digital signals critical for the correct circuit behavior are monitored and their waveforms are compared to a default template signal, where maximum allowed deviations from standard high and low voltage levels are defined; rise and fall time variations are also checked in order to evaluate if jitter violates a threshold and consequently provoke a digital failure.

Figure 2.17. Template waveform failure criteria [30]

In Fig. 2.17 an EM immunity test applying template waveform criteria is shown. A micro-controller output signal is periodically toggled; when interference couples with the IC, the output signal waveform depicted in red is modified and it is compared with a default template (shown in blue). On the area marked with a green circle, the signal doesn't violate template thresholds and therefore immunity test is passed, while on the area marked with a black circle the interference corrupts the waveform and the immunity test is failed.

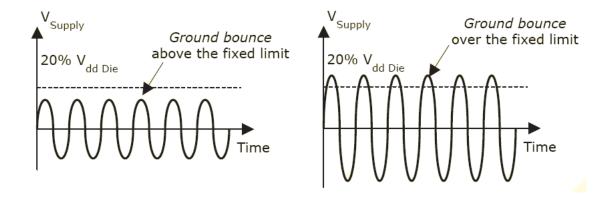

#### Stress of the power supply

In the presence of a RF disturbance, the voltage of the power supply can fluctuate. This fluctuation is called ground bounce when it is observed on the  $V_{ss}$  die, and supply bounce when it results from the  $V_{dd}$  die. Below a certain limit, these effects are tolerated by the active blocks of the circuit and no error is observed. Beyond this limit, the potential difference between the external and internal  $V_{ss}$  references is such that a part of the information from the outside can be badly interpreted by the active parts of the circuit and generate logical faults.

The idea is to perform iterative simulations by varying the frequency characteristics of the aggression voltage. For each frequency, the amplitude of the disturbance is increased until the fluctuation of the internal  $V_{ss}$  reference is higher than or equal to 20% of the nominal power

Figure 2.18. Power supply stress failure criteria

supply voltage. Once the level is reached, the criterion for susceptibility is supposed to be met, as shown in fig. 2.18.

#### Decrease of the power supply voltage

An important failure criterion lies in the decrease of the internal power supply voltage, defined as the difference between the reference voltages  $V_{dd}$  and  $V_{ss}$ . Below a certain margin, which can be defined at 30% of  $V_{dd}$ , the switching of the logical circuits is significantly slowed. This phenomenon originates delays of signal distribution and can lead to the loss of features of logical or analog circuits. [31] presents the switching delays according to the fall of the power supply voltage, in a simulation made for an CMOS inverter designed in 0.25  $\mu$ m technology with typical load conditions. It shows that a decrease of 30% of the power supply voltage (from 2.5 V to 1.75 V) corresponds to an increase of the switching delay of about 60%. A decrease of 50% of the voltage  $V_{dd}$  generates a switching delay 150% higher. Such increase may cause some functional blocks to be no longer correctly operational at component level.

#### Over-consumption of current

A disturbance injection on the power supply network of a printed circuit board can generate parasitic effects on the on-chip power supply network, such as current flow of very strong intensity. These currents possess certain limitations due to the physical elements they cross. The current that can nominally flow through a gold bonding wire can be estimated as:

$$I_{max} = J_{cur}\pi r^2 \tag{2.1}$$

where  $J_{cur}$  is the maximal current density defined in  $[A/m^2]$ , r the conductor radius and  $I_{max}$  the maximal current which can flow before destruction of the conductor. It is important to note that the dependence on temperature is not taken into account, therefore in nominal functioning this maximum current is certainly lower than the proposed value. Consequently, these limits can be exploited to define a new failure criterion within the framework of analog simulations. For instance, an integrated circuit which consumes a nominal current  $I_{nom}$  of about 100 mA is supposed

to be able to stand 500 mA (5 x  $I_{nom}$ ) current peaks. Furthermore, currents whose intensity is higher than 1 A have a very strong probability of destroying the most fragile elements of the chip.

#### 2.5.2 Circuits Models

A realistic and faithful approach consists in building transistor-level models; a physics-based or "white-box" model can be used to simulate circuits susceptibility starting from an accurate description of the DUT. Historically, such model approach has been used first in a study [12] proposing to simulate RF disturbance effects on bipolar transistors using their Ebers-Moll model; it correctly defines parasitic elements and controlled sources in order to describe the non-linear effects due to signal rectification for PN junction. This kind of approach has been successfully applied to studies on circuits such as operational amplifiers and logic gates [4] and more recent research [32, 11] has studied circuit susceptibility modifying model characteristics, such as the operational amplifier model [33] shown in fig 2.19. For CMOS-based technology it is also possible to use the BSIM model for transistors that is easily exploitable by simulators of SPICE type. This model, not originally developed for immunity prediction, is a compact model of third generation and commonly used in microelectronics design; it models with great precision different operating regions due to the presence of many user-defined parameters.

Figure 2.19. Operational amplifier immunity model

More recently the susceptibility simulation of complex circuits has been done using a full transistor-level circuit [27]. These studies are related to circuits built for susceptibility characterization, meaning that there is a direct collaboration with the circuit manufacturer. However this type of modeling is seldom used nowadays because it is not suitable for large circuits due to their huge complexity and long simulation time; a complete simulation of a logic core requires large computational time and therefore it is necessary to develop simplified models to shorten simulation time.

Moreover, for industrial circuits, such modeling approach requires access to confidential information and chip manufacturers often do not provide a complete netlist of their circuit. Therefore new model types have been developed in order to comply with those requirements.

#### 2.5.3 Behavioural Models

The principle of behavioural modeling is to replace all or part of a component by a mathematical model reproducing the circuit behavior when affected by interference. A behavioral model expresses the outputs of a system as a function of its inputs and of several internal "state variables", i.e. by means of mathematical expression, therefore it does not require physical and technological details of the circuit. A behavioral model can then take into account only the most important phenomena required by the application; consequently, there is always a trade-off between simulation speed and accuracy. Those models provide a description of the functional blocks at a level of abstraction higher than the transistor-level model; it proposes to develop a "black box" in which input and output variables are linked by a set of differential equations, non-linear functions or data tables. Development of behavioural models is expanding with the widespread use of standard languages such as MAST, HDL-A, VHDL-AMS and Verilog-AMS, that position themselves as direct competitors of SPICE type circuit simulations. VHDL-AMS (Analog and Mixed-Signal) has many advantages over other languages: it is standardized [34], upward-compatible with VHDL, and modeling and simulation tools are now mature. Several studies have been done about behavioural models; Stievano work [35] consists in behavioural model identification by means of nonlinear dynamic parametric models. In this approach, the parameters of a suitable model are estimated from the voltage and current waveforms measured at the device ports. The modeled device is considered as a black-box, i.e., in principle, no knowledge of the internal structure is required and the modeling information is completely contained in the device external responses. Owing to this feature, parametric models can be effectively estimated from measured transient responses or from simulated responses computed for detailed reference transistor-level models. Besides, since the structure of the parametric models is partially selected by the identification process itself, they automatically include all significant physical effects relating input and output waveforms. It has been demonstrated [36] that this modeling solution is able to address EMC problems and signal integrity.

Another model has been successfully built by Chahine [37] who has proposed to use Artificial Neural Networks (ANN). The modeling procedure consists in building a susceptibility mathematical model based on an inverter susceptibility measurement from a DPI test; indeed, the conducted susceptibility problem can be considered as a non-linear mathematical function such as an ANN that connects inputs and output variables. Depending on the complexity of the function to approximate, training and building a Neural Network could be computationally heavy.

In [38], a new technique to create an accurate immunity model of an analog IC is proposed. The model is based on surrogates, constructed using ANNs, replacing the real netlist and concealing the IP of the manufacturer. Data are collected by means of harmonic balance (HB) simulations, allowing to model both the functional and the noisy behavior of the nonlinear circuit in the frequency domain, making it ideally suited for efficient DPI or BCI immunity simulations. The novel method is validated by means of an industrial case study, being an automotive voltage regulator, clearly showing the capabilities and practical advantages of the technique.

Generally speaking, behavioral models present interesting features for manufacturers since they do not release any confidential information about the internal structure of ICs; however their validity domain is strictly related to the adopted mathematical formulation, which may reduce their effectiveness. In addition, they could display a non physical behaviour since generally no physical constraints are included in the model, apart from input/output data.

#### 2.5.4 Macromodels

By definition, macromodeling aims at replacing a system or part of it with a model in order to reduce computational time during simulation. Therefore macro-modeling consists in constructing an electrical model as simple as possible and able to reproduce with precision the behavior of the system. A macro-model is built with a "gray-box" approach, as it can be composed of a mix of ideal linear elements (passive components and controlled sources), non-linear active components (diode, transistors) and mathematical formulations from measured or simulated data. This class of models has been widely used both in academic and industrial world to build susceptibility model. In an industrial context, a macro-model is preferred if it has compatibility with main circuit simulators (SPICE, VHDL-AMS) and it does not disclose confidential information. For these reasons, the macro-model is viewed as the most appropriate model type; however, unlike EM circuit emission, currently there is no standard for immunity modeling. Research elaborating a susceptibility model is underway in academic contexts. In the following sections several macromodels for IC are described.

#### **IBIS**

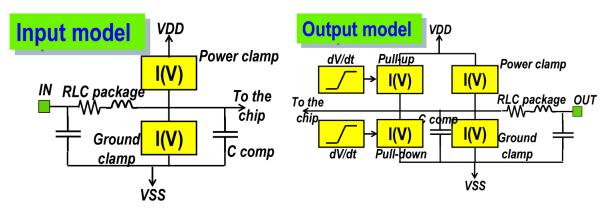

The first important contribution to standard EMC modeling originates from the I/O buffer information specification (IBIS) [39] working group, originally developed by INTEL engineers, that proposed a standard aimed at describing the electrical performance of I/O structures of ICs. IBIS is a standard for describing the analog behavior of a buffer; the specification provides a standard parsed file format consisting of current-voltage (I-V) characteristics, voltage-time (V-t) characteristics, device package parasitics, input capacitance, and timing measurement information for several types of I/O structures. IBIS models provide information that accurately models a buffer's behavior without revealing proprietary information about the circuit's structure or fabrication process. IBIS models are component-centric; the IBIS model describes all pins of the physical component. So, IBIS models are particularly well-suited for interfacing with the component footprints of large PCB databases describing hundreds or thousands of nets. Systems designers use IBIS models to perform board level signal integrity simulations and timing analyses.

Fig. 2.20 presents the structure of input and output described according to the IBIS specification. The most important keywords relating to EMC are listed in Table 2.4.

From a EMC point of view, IBIS does not provide specific information about ICs core noise and considers the power supply as an ideal voltage source, therefore a more advanced model is needed for immunity simulation.

| IBIS feature                  | EMC Application                                     |  |

|-------------------------------|-----------------------------------------------------|--|

| R,L,C Package                 | Used for defining Passive Distribution Network (PDN |  |

| Input protection diodes       | Susceptibility Analysis                             |  |

| Output driver characteristics | I/O driver emission                                 |  |

| Supply structure for each pin | PDN definition                                      |  |

| Pin input capacitance         | Immunity analysis                                   |  |

Table 2.4. Role of IBIS in EMC of ICs

Figure 2.20. IBIS model structure

#### **LECCS**

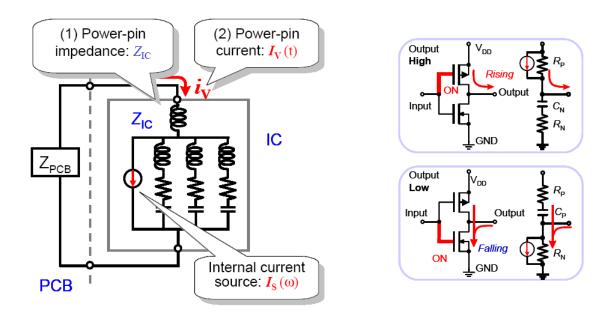

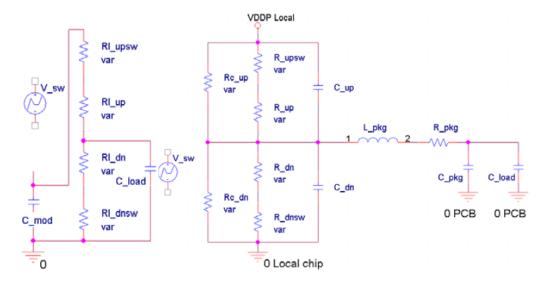

To achieve fast EMI/EMS simulations of digital devices and printed circuit boards, an EMC macro-model for digital ICs/LSIs has been developed that was named Linear Equivalent Circuit and Current Source (LECCS) model. The model was originally proposed to evaluate the RF noise current on a power pin of a core logic circuit. LECCS models consist of linear equivalent circuits (LEC) combined with equivalent current sources (CS) that express the internal noise source caused by the switching operations of the transistors; the switching duration of each transistor is as short as sub-nano seconds, which is short enough when compared to the time constants of the noise current. Therefore, most of the noise characteristics of the device under test can be expressed by linear macro-impedance models such as the one shown in Fig. 2.21, and the macro impedances, including a chip and package, can be evaluated from the outside. So, the equivalent circuit of linear impedance is practically applicable and accurate enough for EMC simulations. Two types of LECCS models have been proposed, the LECCS-core for the internal core logic circuit and the LECCS-I/O for the output buffer circuit. They have been applied to practical ICs to simulate and control RF power current of devices.

The LECCS-core model is composed of a linear equivalent impedance,  $Z_i$ , and an internal equivalent current source,  $I_s$ , The device model provides the RF current in the power pin of an IC as the noise excitation source. The LECCS model for core circuits has the following features:

• All the model parameters can be determined by measurements, so there is no need to consider the internal design parameters. Of course, the parameters can also be derived from a

Figure 2.21. LECCS Core (left) and LECCS I/O (right)

SPICE model of the device.

- The internal current source is determined from the measured current spectrum.

- The model can express RF noise characteristics of the power current of an IC. The effects of decoupling capacitors on a PCB or of on-package and on-chip decoupling capacitors can be evaluated.

The LECCS-core model was applied to simulate EMI from practical PCBs and good agreement between simulations and measurements was achieved [40]. The results include decoupling simulation with on-package and on-board capacitors, and EMI simulation with a powerbus resonance model of a multi-layer PCB.

The LECCS-I/0 model was proposed to express the variation of the RF power current dependent on the external output load of the drivers. Two quasi-static (H or L) states were separately modeled with a set of linear equivalent circuits. When the LECCS-I/0 model is compared with the LECCS-core model, they can be defined as follows: the LECCS-core model describes the electrical characteristics of the internal blocks of an LSI or IC with no global I/0 interconnection, and the LECCS-I/0 model describes the characteristics of blocks having external I/0 interconnections.

The LECCS-core model is also applicable for immunity evaluations; Ichikawa et al. [41] have shown that LECCS model could be used to describe component susceptibility. Indeed the impedance characterization of coupling path and circuit is critical because it allows to simulate interference propagation inside the circuit. The frequency-dependent internal impedance is directly related to its susceptibility as it impacts the power levels of interfering signal.

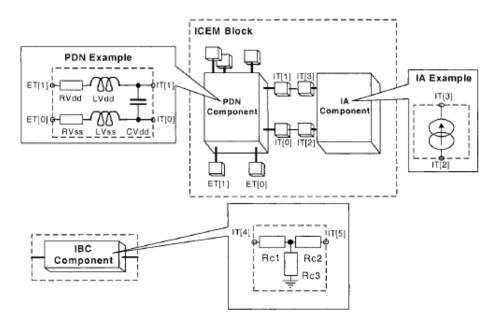

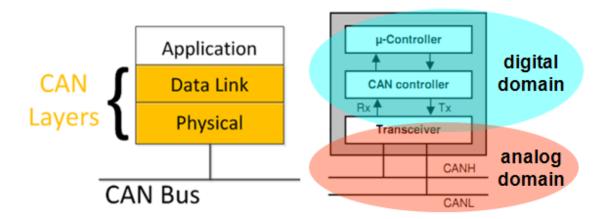

#### **ICEM**

The Integrated Circuit Emission Model (ICEM) [42] has been developed to simulate conducted and radiated emission due to internal circuit activity and input/output commutations, therefore not for simulating susceptibility test. Based on this IC architecture, which describes all the functional blocks and all the internal and external connections, an ICEM model is defined to describe the electrical and electromagnetic behavior of all the internal blocks. An ICEM model is built around a set of ICEM blocks, which are composed of different components, as shown in Fig. 2.22:

- Passive Distribution Network (PDN): The PDN for this analysis describes impedances seen between terminals such as power-supply and I/0.

- Internal Activity (IA): The IA describes the current driven by the internal blocks. It can

be expressed in time or frequency domains. Spice source components such as IPWL and

IPULSE can be used to describe low complexity signals.

- Inter-Block Coupling (IBC): the IBC component describes the connection between two internal terminals such as two different grounds.

With these three ICEM components and a set of block ICEM models, a structural ICEM model can describe a full IC architecture. For example, I/Os can be described using the PDN for the internal and external impedance and the IA for the specific activity of this port.

Figure 2.22. ICEM structure

Since the integrated circuit emission mode used for the simulation of parasitic emissions gave interesting results, a similar development path to set up the immunity model for components is used. The integrated circuit immunity model reused the passive elements of the ICEM model; the

electrical elements of the model are directly linked to the physical dimensions of the component, to the on-chip capacitances and to the power supply network. As immunity simulation is relatively different to parasitic emission simulation, a current generator is no longer necessary. but, from the point of view of the RF generator, the IC core is perceived as a load. Consequently, the current generator is replaced, in a first approximation, by a resistance load. Research done by Baffreau [43, 30] successfully reproduced susceptibility tests when RF interference coupled with power supply; however this model is far less useful when interferences are injected on I/O ports, because non-linear elements protecting IC ports are not modeled in ICEM; adding those circuits as necessary, such as clamp diodes during injection of RF disturbances on a I/O, improved susceptibility prediction significantly.

#### **ICIM**

The development of a model able to predict ICs response to interferences is mandatory in order to improve EM immunity and in a industrial context, a general immunity model of IC functional blocks is needed to deal with this issue in a way as realistic as possible.

Figure 2.23. ICIM structure

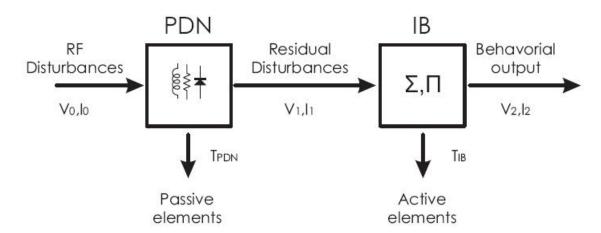

Starting from ICEM model, the first attempts to standardize these approaches were performed through the proposed standard ICIM [44]; the internal structure, shown in Fig. 2.23, is defined by two blocks:

- Passive distribution network: The PDN consists of passive elements for the package, bonding and on-chip interconnections. It represents the input network of the power and signal pins of the chip. It characterizes the coupling path for the RF disturbances, which can undergo filtering and distortion.

- Immunity Behaviour (IB): the IB corresponds to a behavioral block which reproduces functional behavior when disturbances couple with the component. The information output, where immunity criterias are applied, from the IB via one or more observable outputs describes circuit response to a disturbing signal applied to one or more input ports.

A first model has been made by Lafon et al. [45] dedicated to the prediction of immunity behavior for continuous wave (CW) disturbances, in the 1 MHz - 3 GHz frequency range, on a LIN transceiver analyzed with a DPI test; the agreement between measurement and simulation were good when RF interference coupled with power supply.

#### Other models

An interesting model of microcontroller immunity has been described by Steinecke et al. [46]; it presents an approach to simulate the immunity of the microcontroller based on dynamic, nonlinear and passive model. By introducing the dynamic elements, this modelling technique reflects both those dynamic and nonlinear behaviour of ports and cores of the microcontroller. The dynamic model is suitable for time domain simulation, capable of simulating both RF and pulse immunity of the microcontroller.

In order to apply immunity criteria the model should correctly predict the interference arriving at the functional blocks. Impedance is one of the most important properties of the microcontroller that determine the transmission coefficient. The impedance of the I/O, the impedance of the load of the power network and the impedance of the interconnection lines work together to determine how much disturbance will be coupled into the microcontroller and how much of them will reach specific functional blocks. To be able to simulate the immunity properly, the model of the microcontroller should includes all significant impedance components. Those components can be divided into two groups:

- Passive components: package, on-chip PDN and substrate are modeled in a standard manner with basic structures of RLC networks, extracted from the technology profile and layout design of the microcontroller with EDA tools.

- Active components: Cores and I/O.

Cores of microcontrollers have three important electrical properties: they create dynamic current, their impedances are strongly nonlinear with respect to core supply, and finally once core supply is out of operation range, it stops working and the core current becomes very small. Fig. 2.24 shows the immunity model that can correctly simulate the behaviour of the core, composed of  $C_m$ , sum of parasitic and decoupling capacitors of the core, and dynamic voltage dependent resistors, simulating the active part of the core. The upper resistor and lower resistor are switching resistors that charge and discharge the load capacitor  $C_o$ ; when they are in on-state, their resistances depend on both the voltage across them and local  $V_{dd}$ .

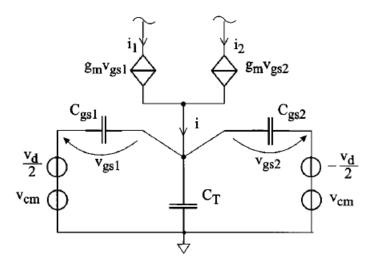

The model of the digital I/O contains a dynamic element simulating the driver/buffer, a pair of voltage controller resistors simulating the power and ground clamp, a pair of capacitors simulating the pad capacitances to power and ground. It is worth to point out the difference between this model and the model generated from IBIS, due to the presence of non-ideal power and ground.

Time domain simulation in HSPICE are run with this model and EM immunity test of micro-controllers can be done, obtaining realistic functional failures when disturbance is injected either on digital I/O or power supply [46].

Figure 2.24. Dynamic core model (left) and model of digital I/O (right)

### 2.6 Chapter Summary

In this chapter, the EMC of integrated circuits was introduced analyzing the technological trend of the last years. The EM emission and susceptibility problems are steadily growing due to the IC physical scaling and the increasing frequencies. The basic EMI effects on ICs and the most common failures are highlighted. Several different experimental techniques are described to measure the impact of RF and transient disturbances on the functional behavior of integrated circuits at component and system level. The designers' need to have immunity models of ICs is highlighted and a review of the different modeling approaches is carried out. In the following chapters a susceptibility characterization and a novel modeling approach are presented for ICs used in communication networks.

# Chapter 3

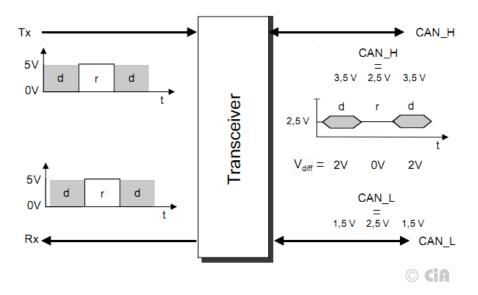

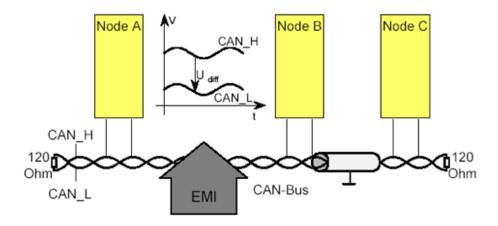

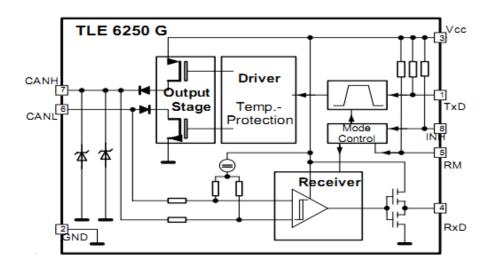

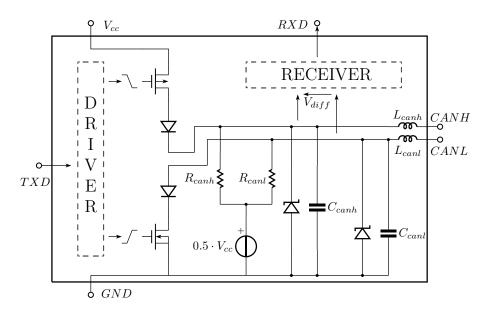

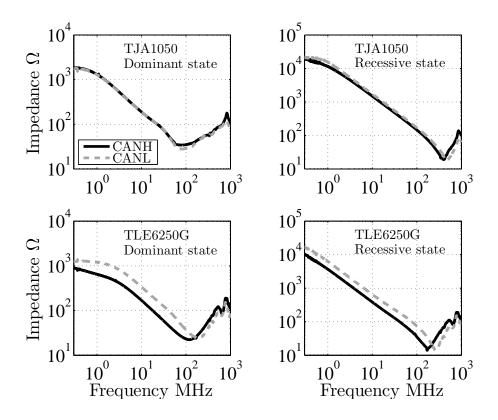

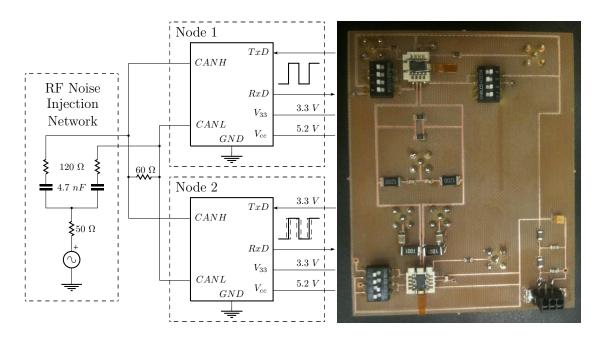

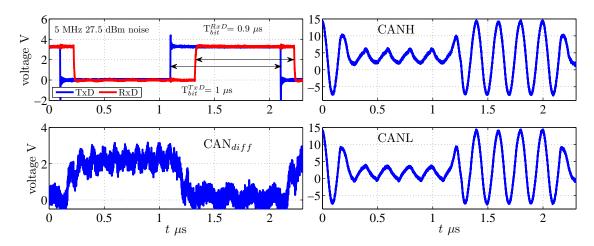

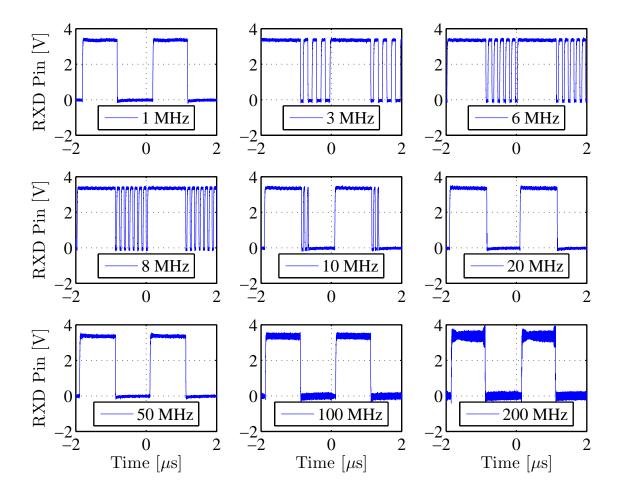

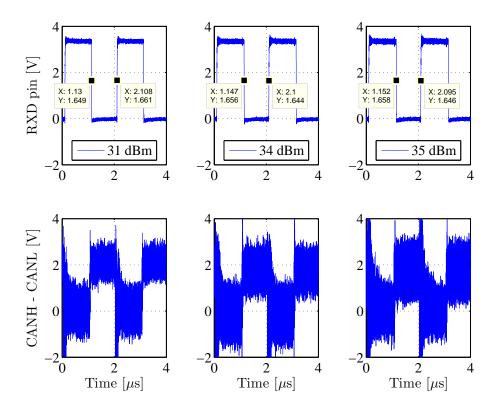

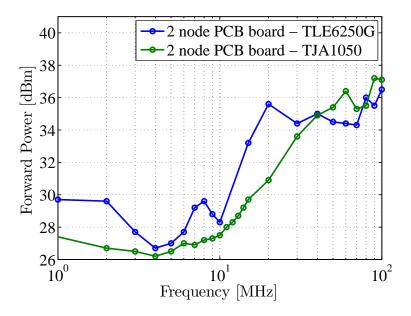

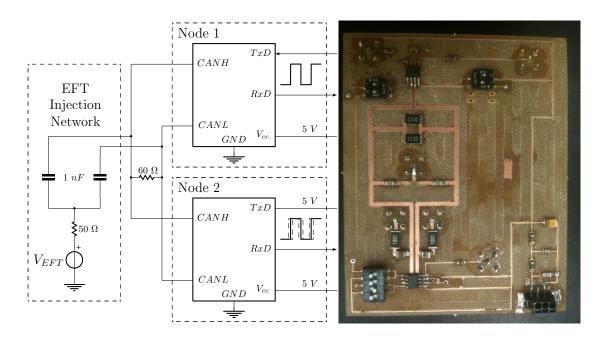

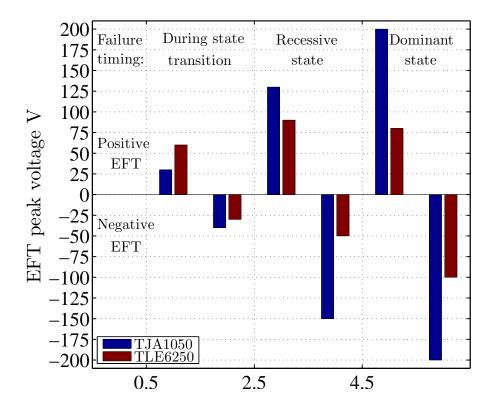

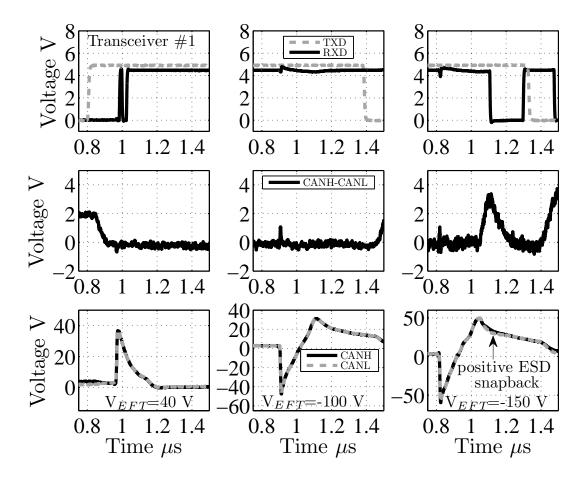

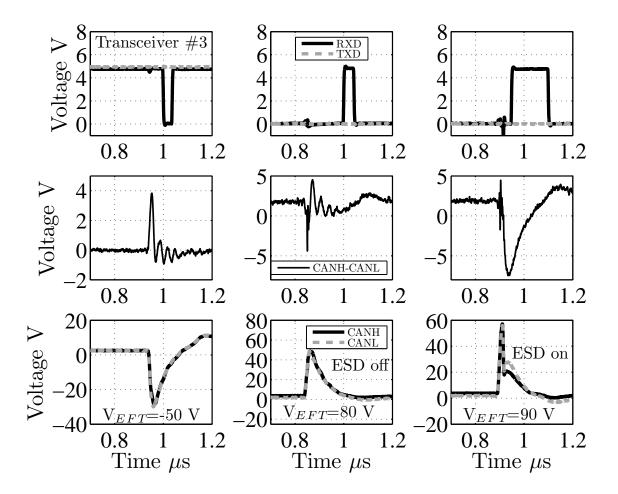

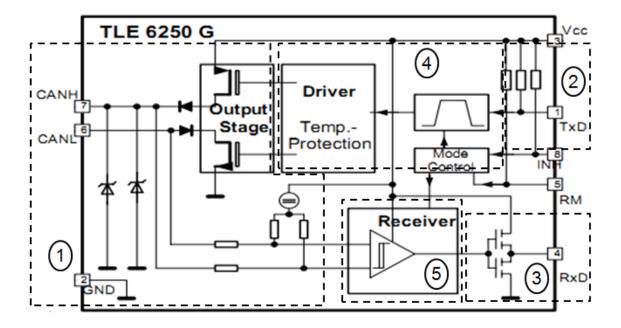

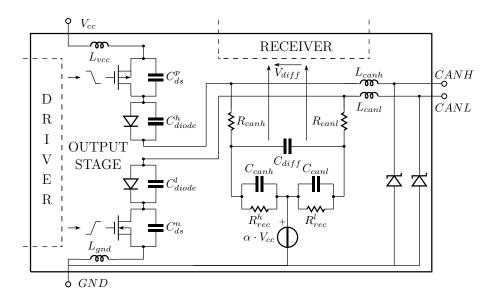

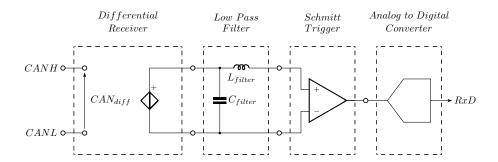

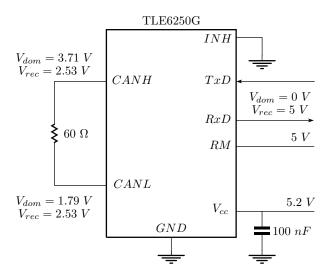

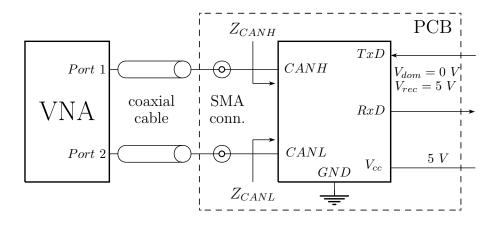

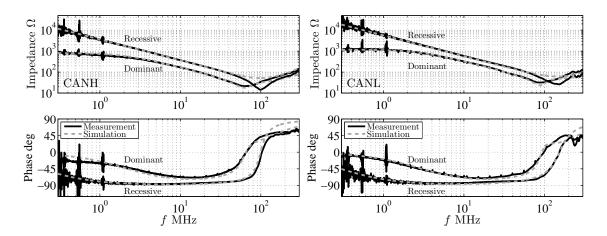

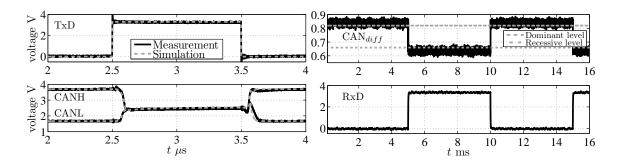

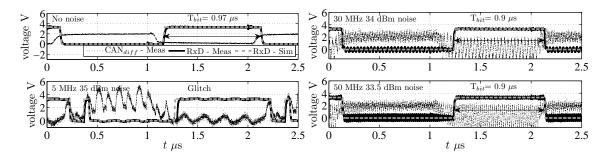

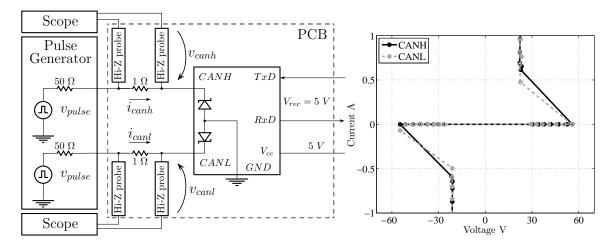

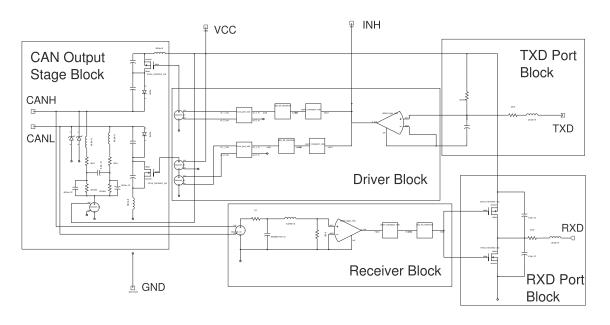

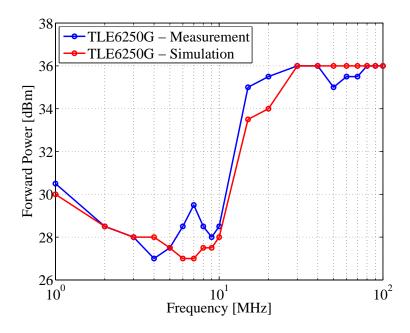

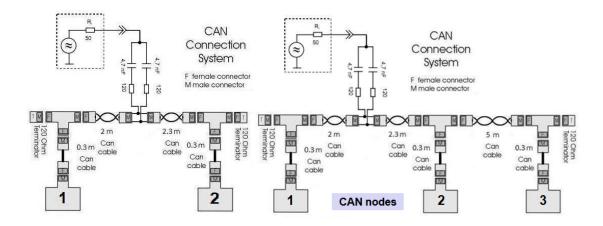

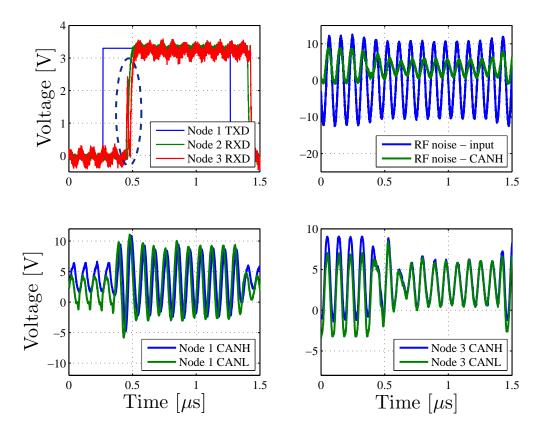

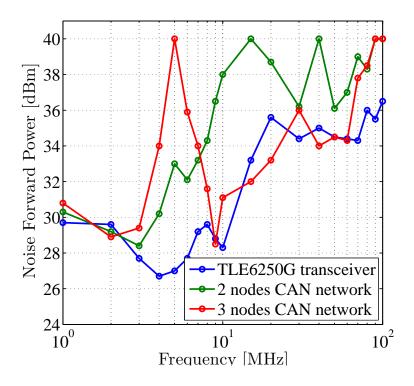

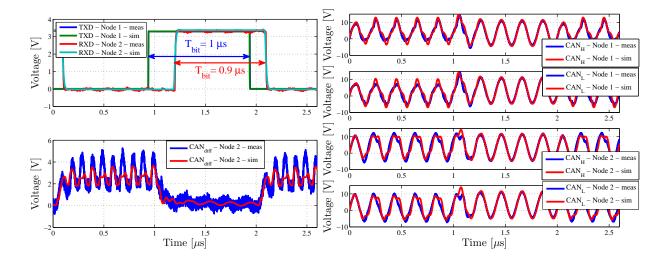

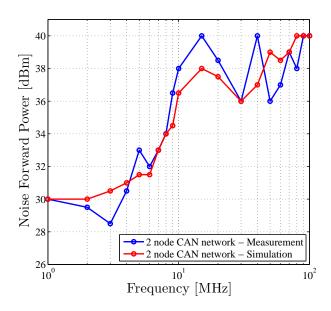

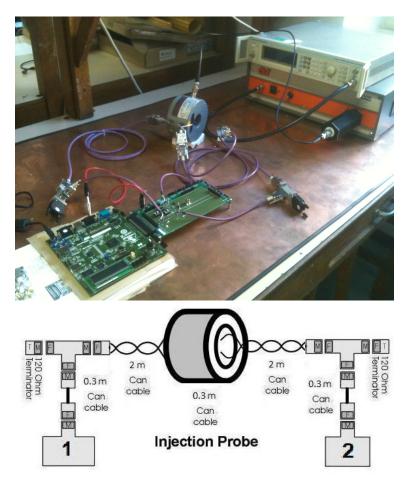

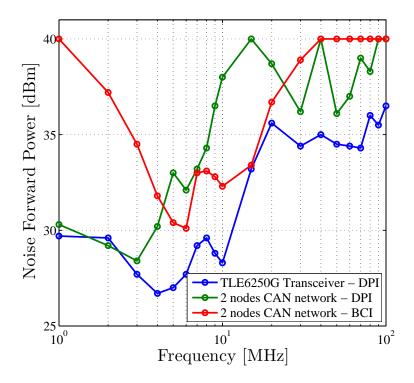

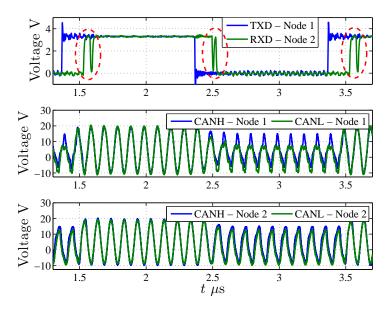

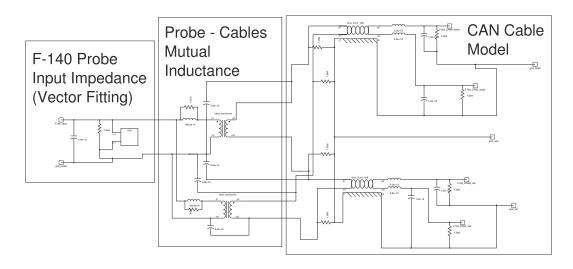

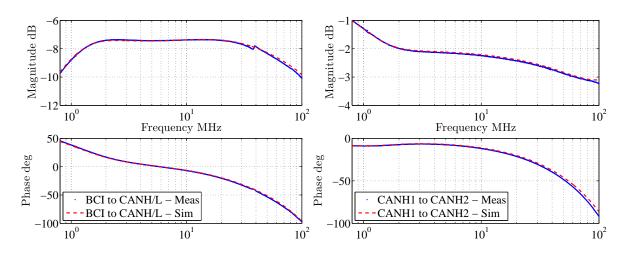

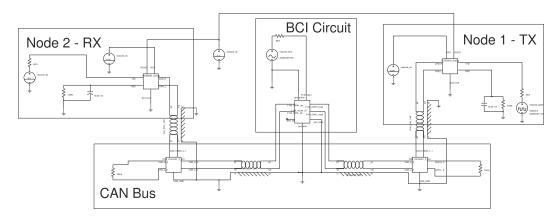

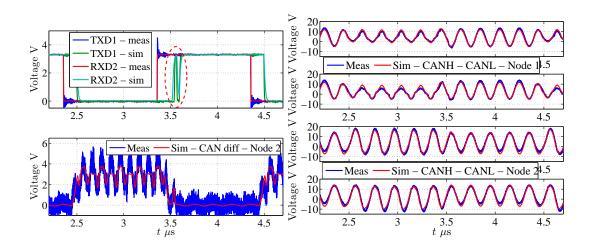

# **Communication Network Immunity Analysis**