## POLITECNICO DI TORINO

DOCTORATE SCHOOL Ph.D. in Computer And Control Engineering – XXV cycle

PhD Thesis

# New Techniques for

# Reliability Characterization of

## **Electronic Circuits**

### Lyl M. Ciganda Brasca

**Advisor** Prof. Paolo Bernardi

February 2013

Lovingly dedicated to my parents, Dominga and Yamandú, continuous source of inspiration, my "sweet rocks".

## Acknowledgements

It is with immense gratitude that I acknowledge the support and help of my advisor, Paolo Bernardi, whom with great patience and sense of opportunity guided my work during these years.

I would also like to thank Professor Matteo Sonza Reorda for his time, encouragement, and expertise throughout this project.

I consider it an honour to have worked with Michelangelo Grosso and Ernesto Sanchez, thank you for the stimulating discussions and creative ideas.

Special thanks go to my fellow lab members at Politecnico di Torino: Alberto, Alessandro, Davide, Fabio, the four Marcos, Mauricio, Niccolò, Salvatore, and all the students who came and go during these years, you all made my work much more fun.

To the staff and students at TIMA Laboratoire RMS group (2012), I am grateful for the chance to visit and be a part of the lab. Thank you for welcoming me as a friend and helping to develop some of the ideas in this thesis.

I am indebted to my many colleagues from Torino, Grenoble and Montevideo, beautiful people and excellent professionals who continuously encouraged me in this path.

This thesis would have remained a dream had it not been for my husband, Pablo Scanniello, whose constant support, selfless generosity and brilliant mind provided me light at all times. The baby-to-be was also a stupendous source of strength and hope for the last mile.

To my siblings, Antonio, Rosario, Yamandú, Carolina, Diego and Verónica, and all my beautiful nephews, thank you for being a never ending source of joy and happiness. And to all my family members, especially the ones who are no longer with me, your lives were truly inspiring.

Last but not least, to all my girlfriends round the globe, from very far away or from around the corner, thank you for your open ears (and hearts) and wise pieces of advice.

## Contents

| 1 Int              | troduc                           | ction                                                                                                                                                                            | 1                          |

|--------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Part I             | Back                             | ground                                                                                                                                                                           | 4                          |

| 2 Re               | liabili                          | ty Characterization                                                                                                                                                              | 5                          |

| 2.1                | Rel                              | iability definition                                                                                                                                                              | 5                          |

| 2                  | 2.1.2                            | Associated standards                                                                                                                                                             | 6                          |

| 2.2                | Cha                              | aracterization methods                                                                                                                                                           | 7                          |

| 2                  | 2.2.1                            | Manufacturing testing                                                                                                                                                            | 9                          |

| 2                  | 2.2.2                            | Online testing                                                                                                                                                                   | 12                         |

| 3 Ch               | aracte                           | erization - Different devices, different strategies                                                                                                                              | 16                         |

| 3.1                | Sys                              | tems-on-a-Chip                                                                                                                                                                   | 16                         |

| 3                  | 3.1.1                            | Microprocessors                                                                                                                                                                  | 17                         |

| 3                  | 3.1.2                            | Memories                                                                                                                                                                         | 19                         |

| 3                  | 3.1.3                            | Mixed-Signal devices                                                                                                                                                             | 21                         |

| 3.2                | Sen                              | isors                                                                                                                                                                            | 21                         |

| Part II            | Contr                            | ibution to the State-of-the-Art                                                                                                                                                  | 24                         |

| 4 Pr               | opose                            | d test programs for SBST of microprocessors                                                                                                                                      | 25                         |

| 4.1                | Pre                              | diction Units                                                                                                                                                                    | 25                         |

| 4                  | ł.1.1                            | Branch Target Buffer-based Prediction Unit Behaviour                                                                                                                             | 27                         |

|                    |                                  |                                                                                                                                                                                  |                            |

| 4                  | ł.1.2                            | BTB-based Prediction Unit Architecture                                                                                                                                           | 29                         |

|                    | ł.1.2<br>ł.1.3                   | BTB-based Prediction Unit Architecture<br>Proposed methodology to test microprocessors' BTB                                                                                      |                            |

| 4                  |                                  |                                                                                                                                                                                  |                            |

| 4                  | ł.1.3                            | Proposed methodology to test microprocessors' BTB                                                                                                                                | 31<br>35                   |

| 4<br>4<br>4        | ł.1.3<br>ł.1.4                   | Proposed methodology to test microprocessors' BTB<br>Test program for the BTB prediction unit                                                                                    | 31<br>35<br>37             |

| 4<br>4<br>4        | 4.1.3<br>4.1.4<br>4.1.5<br>4.1.6 | Proposed methodology to test microprocessors' BTB<br>Test program for the BTB prediction unit<br>BTB SBST experimental results                                                   | 31<br>35<br>37<br>38       |

| 4<br>4<br>4<br>4.2 | 4.1.3<br>4.1.4<br>4.1.5<br>4.1.6 | Proposed methodology to test microprocessors' BTB<br>Test program for the BTB prediction unit<br>BTB SBST experimental results<br>Conclusions about the BTB prediction unit SBST | 31<br>35<br>37<br>38<br>39 |

|   | 4.2.3    | Conclusions about the SBST of the Address Calculation adder $51$ |

|---|----------|------------------------------------------------------------------|

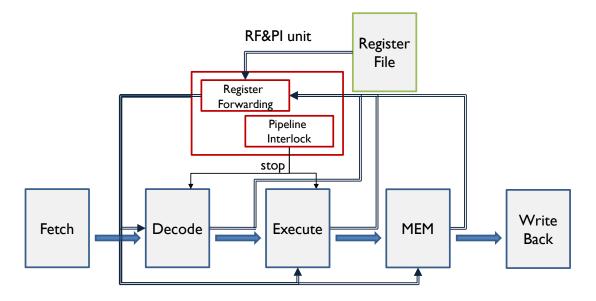

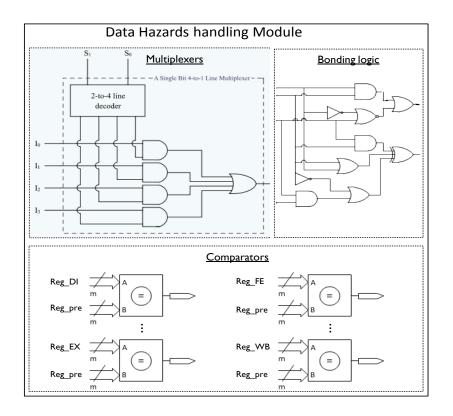

|   | 4.3 Reg  | ister Forwarding and pipeline interlocking unit51                |

|   | 4.3.1    | Data hazards and pipeline interlock mechanisms53                 |

|   | 4.3.2    | Proposed methodology to test the RF&PI unit56                    |

|   | 4.3.3    | RF&PI unit SBST experimental results63                           |

|   | 4.3.4    | Conclusions about the RF&PI unit SBST64                          |

| 5 | Propose  | d Infrastructure-IP to augment self-testing capabilities         |

|   | 5.1 MIH  | IST – A new Hardware-Based Self-Test concept65                   |

|   | 5.2 MIH  | IST – An embedded microprocessor testing strategy68              |

|   | 5.2.1    | Forced instruction sequence                                      |

|   | 5.2.2    | Encoded procedure description71                                  |

|   | 5.2.3    | MIHST unit architecture and behaviour72                          |

|   | 5.2.4    | Encoded instruction generation75                                 |

|   | 5.2.5    | Use of MIHST for on-line testing79                               |

|   | 5.2.6    | Microprocessor MIHST testing experimental results81              |

|   | 5.2.7    | MIHST-based processor testing conclusions                        |

|   | 5.3 MIH  | IST – An embedded memories testing strategy85                    |

|   | 5.3.1    | Why yet a new approach for memory testing?85                     |

|   | 5.3.2    | MIHST approach for embedded memory testing87                     |

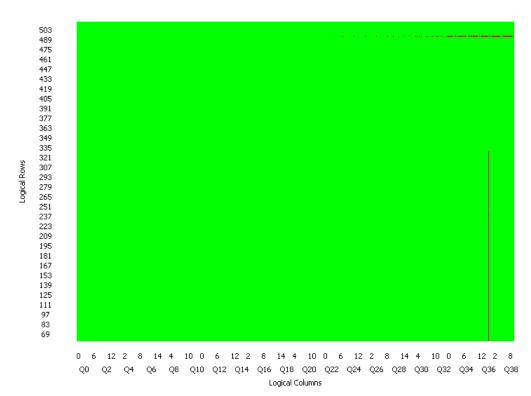

|   | 5.3.3    | Embedded memories MIHST testing experimental results             |

|   | 5.3.4    | Advantages of the MIHST approach97                               |

|   | 5.3.5    | MIHST-based embedded memories testing conclusions98              |

| 6 | Propose  | d enhanced ATE – can we make it better, faster, stronger? 99     |

|   | 6.1 Diag | gnosis of embedded memories99                                    |

|   | 6.1.1    | Embedded memory diagnosis101                                     |

|   | 6.1.2    | Proposed approach for embedded memories diagnosis                |

|   | 6.1.3    | Experimental results for the embedded memories diagnosis124      |

|   | 6.1.4    | Conclusions about embedded memories diagnosis134                 |

|   | 6.2 Cali | bration of MEMS inertial sensors134                              |

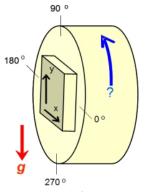

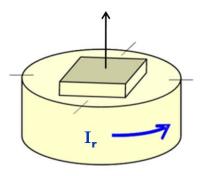

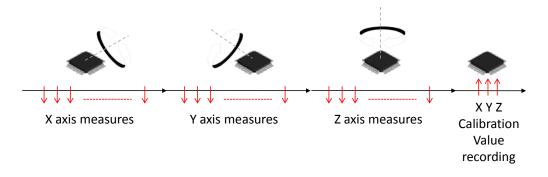

|   | 6.2.1    | Accelerometer and gyroscope MEMS calibration procedure135        |

|   | 6.2.2    | MEMS testing equipment                                           |

|   | 6.2.3    | Proposed methodology for MEMS calibration and test140            |

|     | 6.2.4  | MEMS calibration and testing experimental results | .151 |

|-----|--------|---------------------------------------------------|------|

|     | 6.2.5  | Conclusions about MEMS calibration and testing    | .155 |

| 7 C | onclus | ions                                              | .156 |

## **List of Figures**

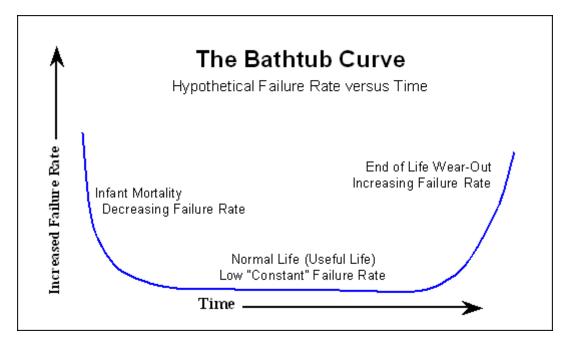

| Figure 2.1 The bathtub curve                                                     | 6   |

|----------------------------------------------------------------------------------|-----|

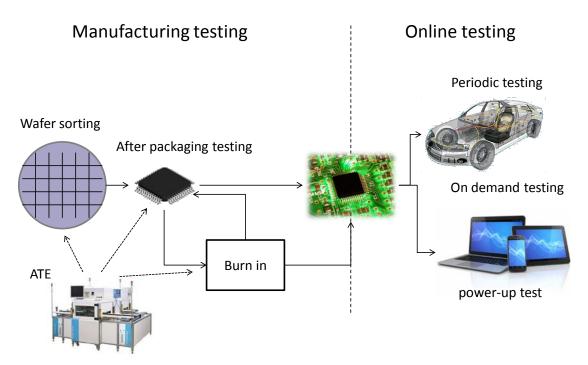

| Figure 2.2 Semiconductors characterization process                               | 8   |

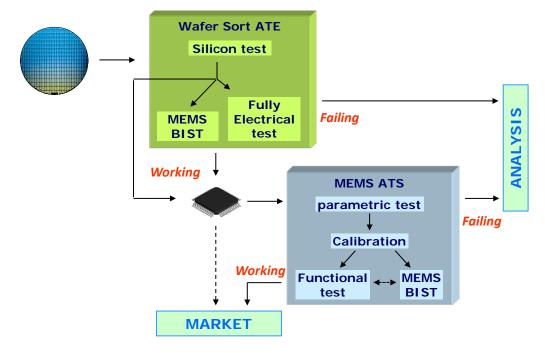

| Figure 3.1 MEMS testing flow                                                     | 22  |

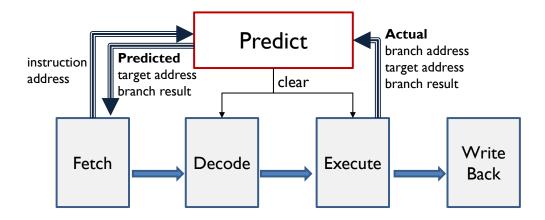

| Figure 4.1 The prediction Unit and its interaction with the processor pipeline   | 28  |

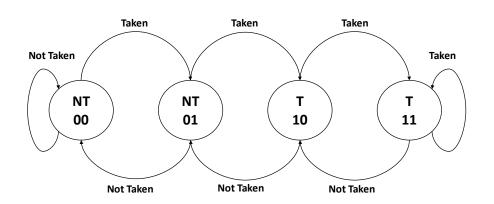

| Figure 4.2 State diagram of the 2-bit saturated counter prediction algorithm     | 29  |

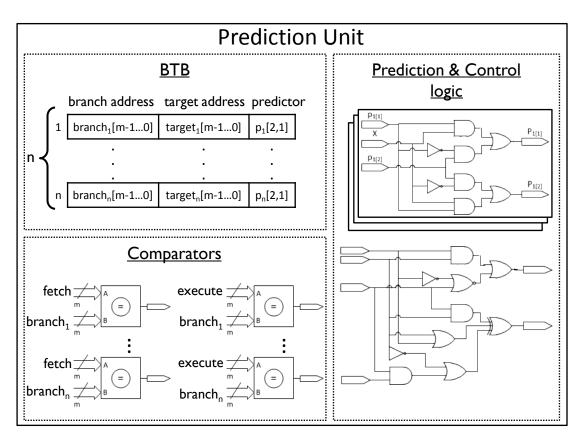

| Figure 4.3 Prediction Unit schema with 3 sub-blocks                              | 30  |

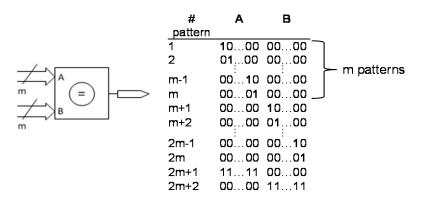

| Figure 4.4 Comparator schema and patterns guaranteeing 100% FC                   | 32  |

| Figure 4.5 Test program for the comparator in a BTB with n=1 and m=7             | 33  |

| Figure 4.6 Pseudo code of the test for the saturated counter prediction logic    | 35  |

| Figure 4.7 General test program schema                                           | 36  |

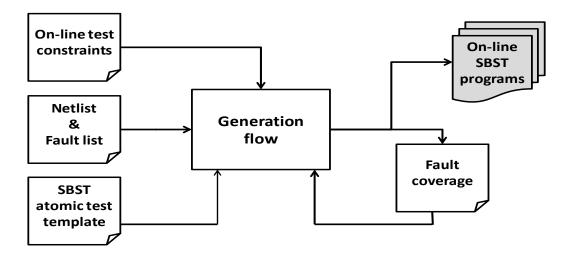

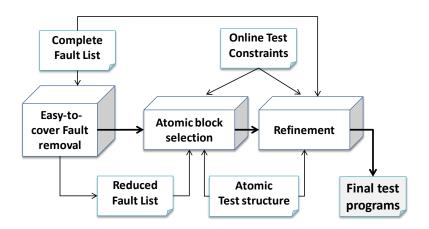

| Figure 4.8 Conceptual view of the proposed generation approach                   | 41  |

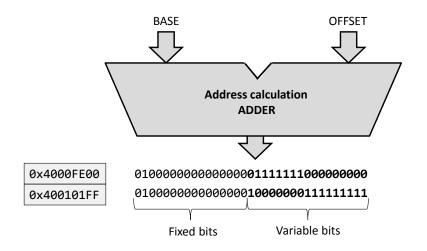

| Figure 4.9 Effect of address range selection for Address Calculation adder test. | .43 |

| Figure 4.10 Atomic block pseudo-code                                             |     |

| Figure 4.11 Proposed framework for on-line testing                               | 46  |

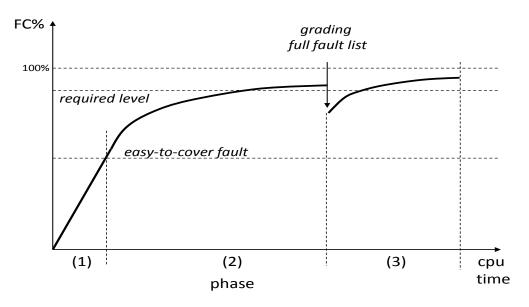

| Figure 4.12 Fault coverage general trend along the generation process            | 47  |

| Figure 4.13 Graph of the possible forwarding paths between pipeline stages       | 54  |

| Figure 4.14 The Register RF&PI unit and its interaction with the proces          |     |

| pipeline and Register File module                                                | 54  |

| Figure 4.15 Data hazards handling module schema with 3 sub-blocks                | 56  |

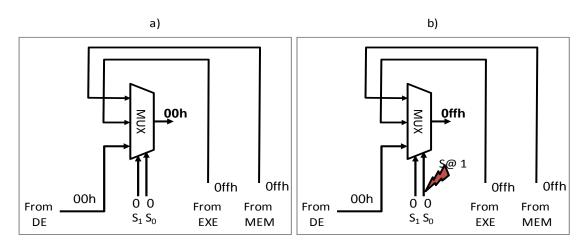

| Figure 4.16 Test program fragment for testing the MUX for the EXE stage          | 59  |

| Figure 4.17 a) Normal and b) Faulty behaviour in one selector                    | 59  |

| Figure 4.18 Test program fragment for testing the CMP in the EXE stage           | 62  |

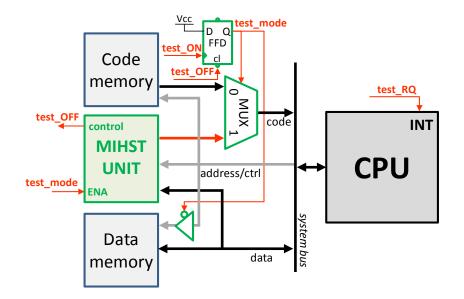

| Figure 5.1 Architecture of a system including the MIHST unit                     | 66  |

| Figure 5.2 Program execution flow in normal and test mode                        | 69  |

| Figure 5.3 PC and IR evolution in mission and MIHST mode                         | 70  |

| Figure 5.4 Program execution flow in normal and test mode                        | 71  |

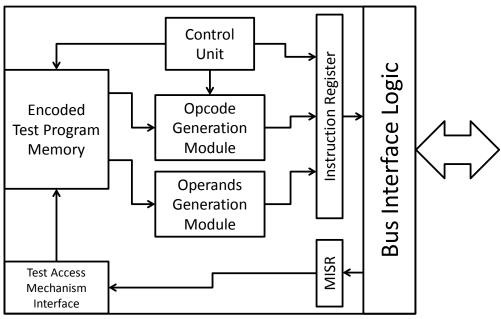

| Figure 5.5 Schematic view of the MIHST unit architecture                         | 73  |

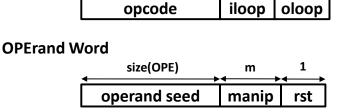

| Figure 5.6 MIHST unit instruction encoding                                       | 75  |

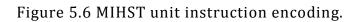

| Figure 5.7 Program manipulation flow.                                            | 76  |

| Figure 5.8 Original Register File module test program                            | 77  |

| Figure 5.9 Unrolled and sifted Register File module test program                 | 77  |

| Figure 5.10 Encoded MIHST-ready Register File module test program                | 78  |

| Figure 5.11 Encoded MIHST-ready BTB test program                                 | 79  |

| Figure 5.12 Schema of the MIHST connections for on-line usage                    | 80  |

| Figure 5.13 Basic SW BIST solution to loops                                         | 90   |

|-------------------------------------------------------------------------------------|------|

| Figure 5.14 Loop unrolled SW BIST to loops.                                         | 90   |

| Figure 5.15 MIHST solution to loops                                                 | 91   |

| Figure 5.16 SW BIST solution to result evaluation                                   | 91   |

| Figure 5.17 Loop unrolled SW BIST to result evaluation                              | 92   |

| Figure 5.18 MIHST solution to result evaluation                                     | 92   |

| Figure 5.19 SW BIST solution to address generation.                                 | 93   |

| Figure 5.20 MIHST solution to address generation                                    | 93   |

| Figure 5.21 4-way folding memory                                                    | 94   |

| Figure 5.22 MIHST solution for the 1 <sup>st</sup> March element of the MATS+       | 94   |

| Figure 5.23 MIHST solution for the 2 <sup>nd</sup> March element of the MATS+       | 95   |

| Figure 5.24 MIHST solution for the 3 <sup>rd</sup> March element of the MATS+       | 96   |

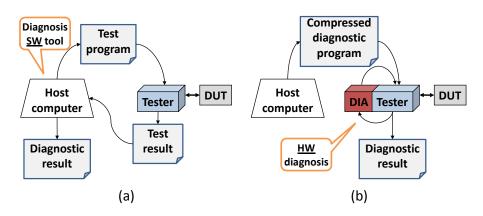

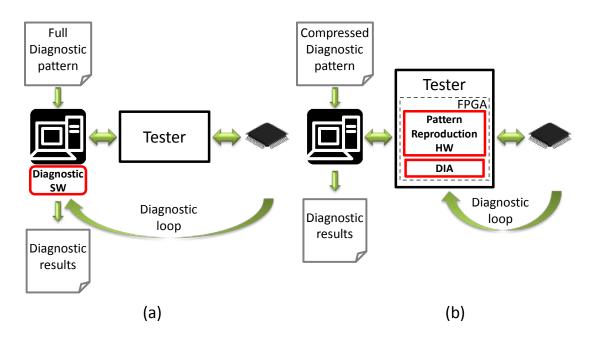

| Figure 6.1 Traditional (a) and proposed (b) memory diagnosis tester architecture    | 100  |

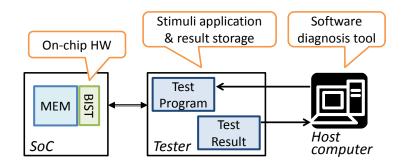

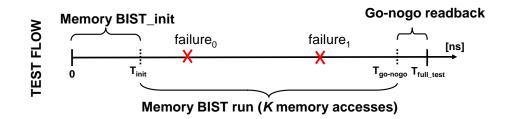

| Figure 6.2 Memory diagnosis environment                                             | 102  |

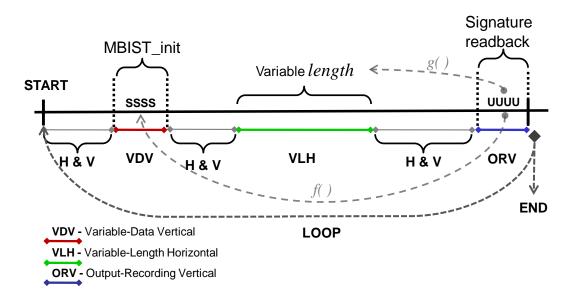

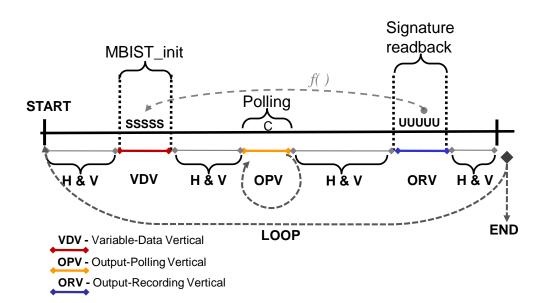

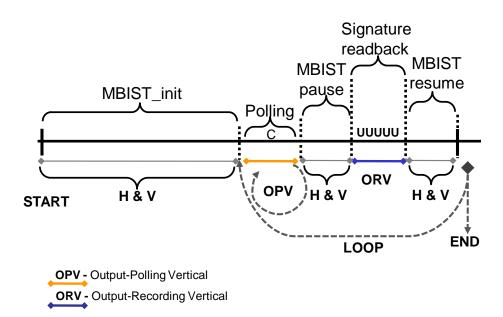

| Figure 6.3 Base memory test execution with its usual phases                         | 102  |

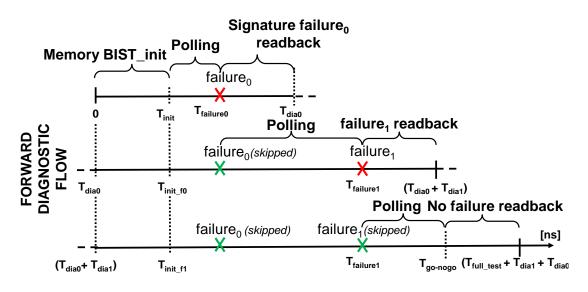

| Figure 6.4 Forward diagnosis flow.                                                  | 103  |

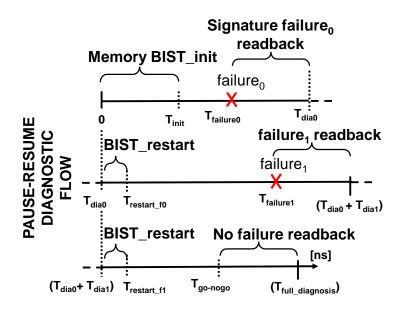

| Figure 6.5 Pause and Resume flow.                                                   | 104  |

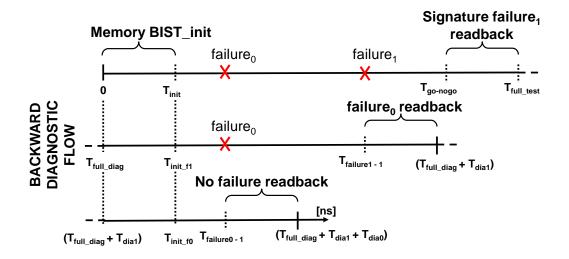

| Figure 6.6 Backward diagnosis flow                                                  | 104  |

| Figure 6.7 Traditional (a) and proposed (b) diagnosis approach                      | 106  |

| Figure 6.8 Methodology flow for embedded memory test and diagnosis                  | 108  |

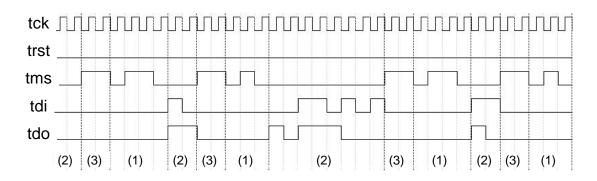

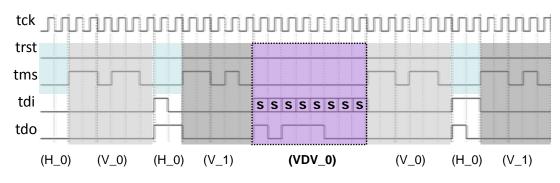

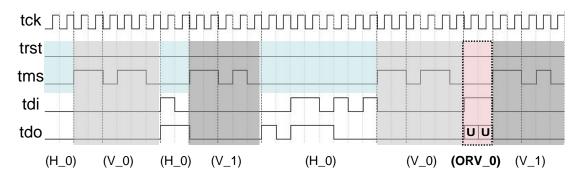

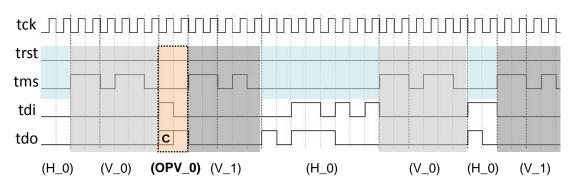

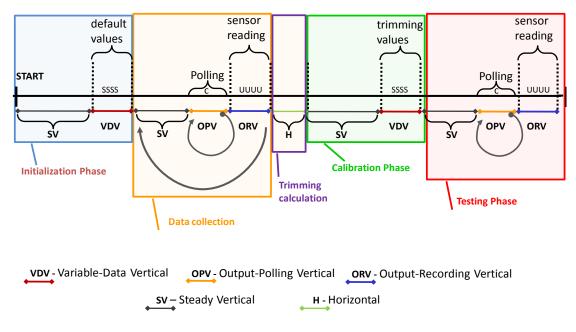

| Figure 6.9 TAP access timing snapshot (zone labels are related to phases)           | 109  |

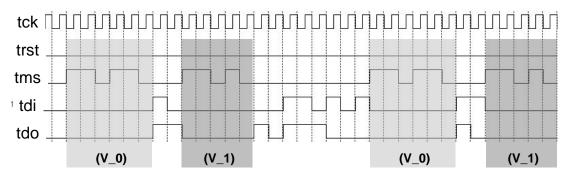

| Figure 6.10 Two vertical occurrences (V_0 and V_1) identified                       | 109  |

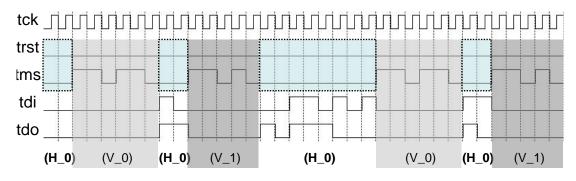

| Figure 6.11 One horizontal occurrence (H_0) identified for the trst and tms signals | s110 |

| Figure 6.12 One variable data vertical occurrence (VDV_0) is identified             | 113  |

| Figure 6.13 One output recording vertical (ORV_0) is identified                     | 113  |

| Figure 6.14 One output polling vertical (OPV_0) is identified                       | 114  |

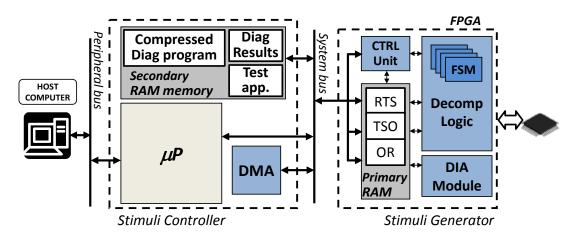

| Figure 6.15 Low-cost tester architecture.                                           | 116  |

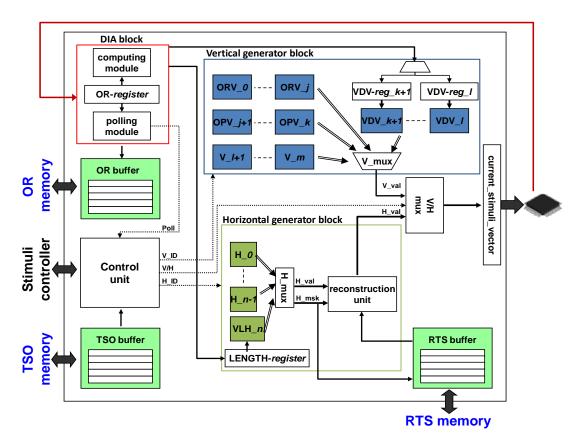

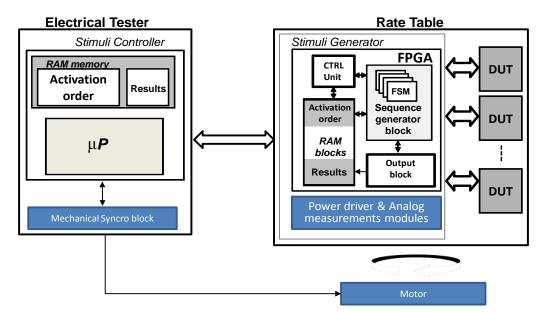

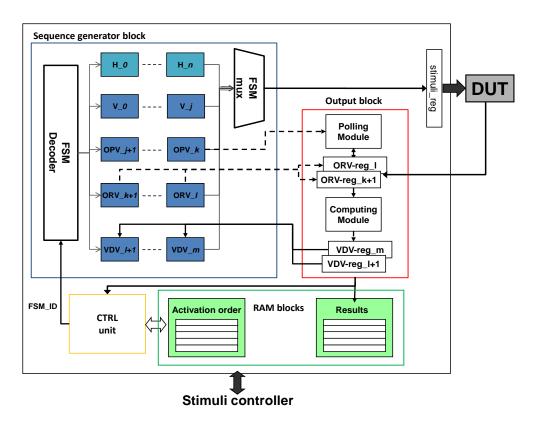

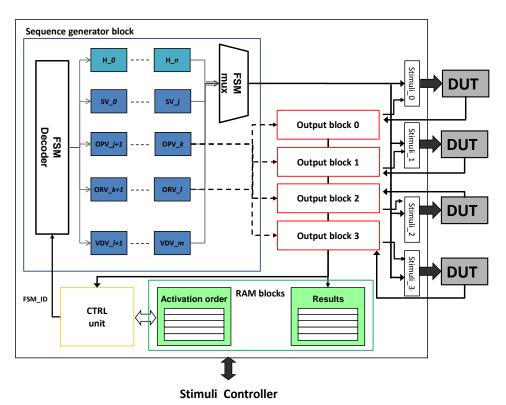

| Figure 6.16 Stimuli Generator conceptual view                                       | 118  |

| Figure 6.17 Backward diagnosis flow diagram.                                        | 121  |

| Figure 6.18 Backward diagnosis iterative process high level description             | 121  |

| Figure 6.19 Forward diagnosis flow diagram                                          | 122  |

| Figure 6.20 Forward diagnosis iterative process high level description              | 122  |

| Figure 6.21 Pause and Resume diagnosis flow diagram                                 | 123  |

| Figure 6.22 Pause and Resume diagnosis process high level description               | 123  |

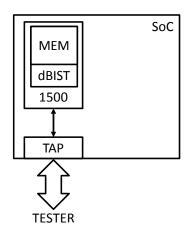

| Figure 6.23 Embedded memory test infrastructure in the case study SoC               | 124  |

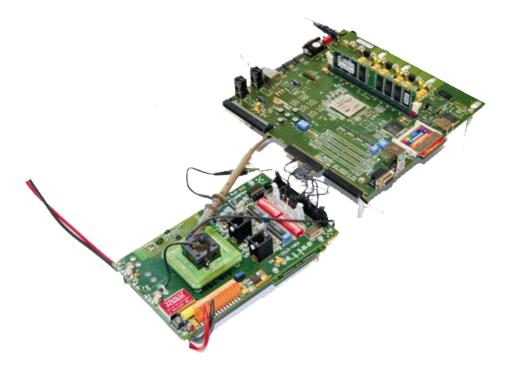

| Figure 6.24 Experimental setup of the tester.                                       | 126  |

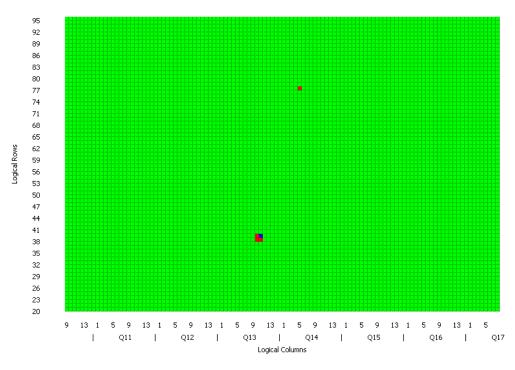

| Figure 6.25 Faulty scenario 1: cluster + spot fail                                  | 129  |

| Figure 6.26 Faulty scenario 2: partial column + partial jeopardized row             | 130  |

| Figure 6.27 Four-point tumble schema for accelerometer calibration                  | 136  |

| Figure 6.28 Rate table schema for gyroscope calibration                             | 136  |

| Figure 6.29 Accelerometers and gyroscope calibration flow.                          | 137  |

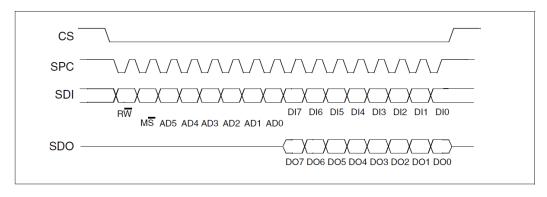

| Figure 6.30 Four-wire SPI protocol, 16 bits implementation                          | 138  |

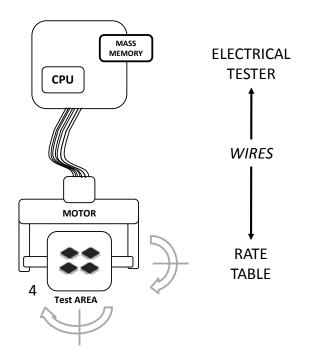

| Figure 6.31 MEMS testing equipment conceptual schema                               |

|------------------------------------------------------------------------------------|

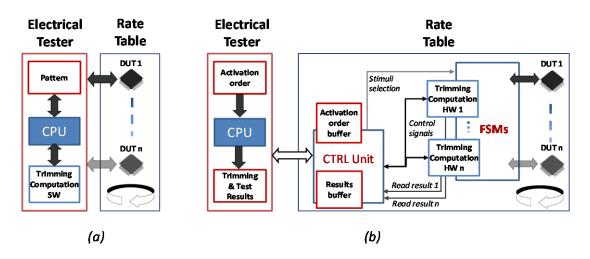

| Figure 6.32 Traditional (a) and proposed (b) MEMS tester architecture141           |

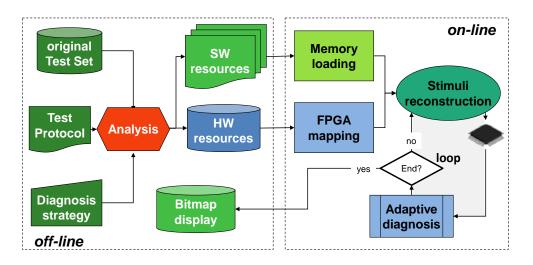

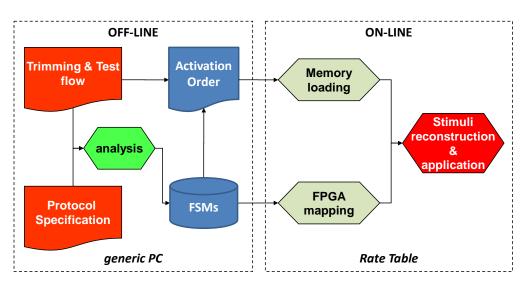

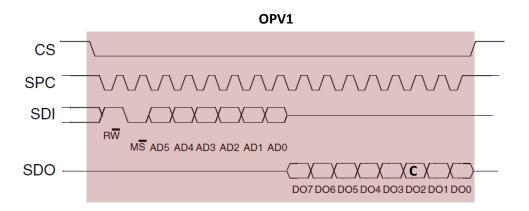

| Figure 6.33 Off-line analysis and on-line stimuli reconstruction                   |

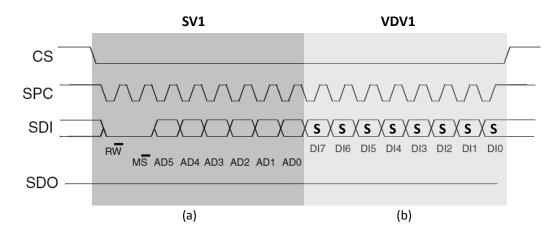

| Figure 6.34 Write cycle with two consecutive occurrences: SV (a) and VDV (b).144   |

| Figure 6.35 Read cycle with two consecutive occurrences: SV (a) and ORV (b).144    |

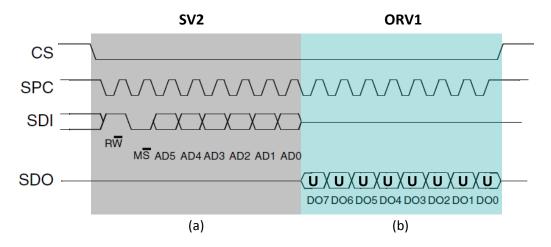

| Figure 6.36 Read cycle implementing a polling operation with an OPV occurrence 145 |

| Figure 6.37 Calibration and testing flow implementation by means of FSMs 147       |

| Figure 6.38 Proposed tester architecture, including the two main modules 148       |

| Figure 6.39 Stimuli Generator module schema149                                     |

| Figure 6.40 Four chips parallel MEMS calibration and testing architecture151       |

## List of Tables

| TABLE I PREDICTION UNIT FAULT COVERAGE                                        | 88 |

|-------------------------------------------------------------------------------|----|

| TABLE II STUCK-AT FAULT COVERAGE [%] OBTAINED ALONG THE FLOW       5          | 50 |

| TABLE III STUCK-AT FAULT COVERAGE FOR DIFFERENT CONFIGURATIONS CASE STUDY 2 5 | 51 |

| TABLE IV TEST VECTORS FOR A 8-TO-1 MUX5                                       | 57 |

| TABLE V INPUT VALUES FOR THE 4-TO-1 MUX FEEDING THE FIRST OPERAND INPUT OF TH | ΗE |

| EXE STAGE IN A PIPELINED PROCESSOR                                            | 58 |

| TABLE VI CHARACTERISTICS OF THE TEST PROGRAM FOR THE RF&PI UNIT6              | 53 |

| TABLE VII ADDER MODULE RESULTS                                                | 31 |

| TABLE VIII REGISTER FILE MODULE RESULTS                                       | 32 |

| TABLE IX BRANCH TARGET BUFFER RESULTS                                         | 32 |

| TABLE X MINIMIPS OVERALL RESULTS                                              | 33 |

| TABLE XI MIHST AREA OVERHEAD                                                  | 34 |

| TABLE XII TEST TIME AND PROGRAM SIZE COMPARISON FOR TESTING A SAMPLE MEMOR    | RY |

| WITH MINIMIPS PROCESSOR                                                       | 96 |

| TABLE XIII TESTER ARCHITECTURE FPGA OCCUPATION12                              | 26 |

| TABLE XIV FAULTY SCENARIO 1 DIAGNOSIS CLOCK CYCLE COUNT AND TIME12            | 29 |

| TABLE XV FAULTY SCENARIO 2 DIAGNOSIS CLOCK CYCLE COUNT AND TIME               | 30 |

| TABLE XVI TIME OVERHEAD COMPARISON    13                                      | 31 |

| TABLE XVII COMPLETE TIME COMPARISON    13                                     | 32 |

| TABLE XVIII FPGA REQUIREMENTS OF THE DEVELOPED ARCHITECTURE                   | 53 |

| TABLE XIX COMPARISON OF THE PATTERN MEMORY OCCUPATION BETWEEN PROPOSE         | ED |

| (new) AND TRADITIONAL (old) TESTING/CALIBRATION METHODS                       | 54 |

| TABLE XX NUMBER OF WIRES AND TRIMMING COMPUTATION TIME COMPARISON BETWEE      | EN |

| TRADITIONAL (OLD) AND PROPOSED (NEW) WITH DIFFERENT PARALLELISM RATES         | 55 |

## Chapter 1 Introduction

Integrated electronic systems are increasingly used in an wide number of applications and environments, ranging from critical missions to low cost consumer products. Information processing has been thoroughly integrated into everyday objects and activities, in the so-called ubiquitous computing paradigm. This wide distribution is caused mainly by the miniaturization of semiconductor devices (transistor channel length scaling from 180 nm in 1999 to 22 nm in 2012), which allows integrating a complete system on a single chip (SoC). However, there are many difficult challenges associated with continued cost reduction, size reduction, improved performance and improved power efficiency.

One of these challenges is the reliability of these electronic systems. Important research efforts are aimed at improving the reliability of semiconductors. Manufacturing processes, intrinsic aging phenomena of components and environmental stress may cause internal defects and damages during the lifetime of a system, possibly causing misbehaviours or failures. In order to guarantee product quality and consumer satisfaction, it is necessary not only to discover faults as soon as possible in the manufacturing process, but also to continuously check for their absence throughout a product lifetime.

Today's modern systems have become increasingly complex to design and build, while the demand for reliability and cost effective development continues. Reliability is one of the most important attributes in all these systems, including aerospace applications, real-time control, medical care, defence equipment, transportation, communication, entertainment products, agriculture, energy and environmental systems. Growing international competition has increased the need for all designers, managers, practitioners, scientists and engineers to ensure a high level of reliability of their product before release and during mission time, at the lowest cost. The interest in reliability has been growing in recent years and this trend will continue during the next decade and beyond.

With testers being expensive pieces of equipment and the cost of transistors continuously decreasing, it make sense to use some of these low-cost transistors to replace the costly test tools, whenever possible.

The first low cost approach we can think about is using the devices themselves to implement their own test. This is the underlying motivation of functional Software-Based Self-Test (SBST): a fast, powerful microprocessor, which has lots of resources, could certainty help in its testing procedure. Having the outstanding advantages of enabling at-speed testing, zero area overhead and actually testing the device's operation, this approach also has some drawbacks. Even if SBST is essentially suitable for online testing (and sometimes it is the only possible approach), it requires some dedicated system memory for the functional testing data, which can reach very big sizes. Also some faults happen to be functionally untestable; i.e., you cannot detect them exclusively by running proper software routines. For this reason a combination of both functional and structural test approaches is common practise.

A second natural approach to low cost testing is design for test (DfT). Add some extra (cheap) area on-chip specifically in charge of performing and managing tests. The DfT path started long ago, but it is still a key element in 2012 International Technology Roadmap for Semiconductors (ITRS)[1] test roadmap. Different sorts of DfT enable the use of low cost testers, contributing to the full checking of a device, and may also be reused for online testing purposes. Logic and Memory Built-In Self Test (BIST) schemas are usual practises. Analogue DfT, even if it is not as advances as digital one, is also an interesting strategy, especially when the analogue or mixed-signal device is integrated in a wider digital system like a SoC

Finally, there are some fields where the use of external (and generally expensive) testers is mandatory. Diagnosis is one of the cases in which an Automatic Test Equipment (ATE) is needed to store the huge amount of retrieved data and to drive the cyclic characteristic of the diagnosis procedure. In particular, even if memories are commonly tested making use of internal BIST structures, their diagnosis demands the use of a tester. Another interesting and blooming field is that of the mixed energy-domain devices as Micro Electro Mechanical Systems (MEMS). MEMS require unique testing apparatus applying both electrical and physical stimuli: movement, pressure, magnetic fields. Additionally, they not only need to be exhaustively tested but in most of the cases also calibrated.

The work described in this thesis falls in low cost testing domain. Strategies for new and/or improved SBST, DfT and ATE mechanisms are proposed, implemented and evaluated. The strategies deal mainly with memories, processor and mixed-signal devices (analogue-to-digital converters is our target device) embedded in Systems-on-a-Chip, where standard communication protocols and wrappers are used to communicate with the device under test. The thesis is organized as follows: Chapter 2, "Reliability Characterization" gives some basic concepts and general background information. Different kinds of testing methodologies are described, including the equipments, tools and methods they used, and the results that can be obtained with each. Also some competent international standards are presented.

Chapter 3, "Characterization - Different devices, different strategies" describes characteristics and limitations in the testing of some specific electronic circuits and introduces different approaches available in the state of the art. In particular we describe the solutions for embedded microprocessors, memories, mixed signal devices and MEMS sensors.

Chapter 4, "Proposed test programs for Software-Based Self-Test of microprocessors" presents SBST approaches for three not-easy to test units within a microprocessor: Prediction unit, Address Adder unit and Data Forwarding & Pipeline Interlock unit. First, the behaviour and architecture of each module is described. Then, we discuss the methodology for generating SBST patterns. Finally, a complete test program is explained, implemented and experimented in academic and industrial case studies for all three units. Obtained results support the proposed strategies.

Chapter 5, "Proposed Infrastructure-IPs to enhance self-testing capabilities of digital devices" introduces a new in-chip testing concept, which enables faster and cheaper testing of embedded memories and microprocessors. Two digital designs implementations are described, both of which are particularly suitable for online testing. Experimental results on real case studies are reported for the two presented designs.

Chapter 6, "Proposed enhanced Automatic Test Equipment – can we make it better, faster, stronger?" displays a methodology and suitable hardware implementation of a digital low cost tester. The approach benefits from FPGAs flexibility and is presented both for SoC embedded memories diagnosis and MEMS inertial sensor testing and calibration. Background on both fields is provided. Results obtained in real case experiments are shown.

Chapter 7, "Conclusions" draws some conclusive remarks.

# Part I BACKGROUND

## Chapter 2 Reliability Characterization

Reliability is the aptitude of a product or system to perform as intended (i.e., without failure) within its specified performance limits, for a specified time and in its life-cycle environment. Reliability characterization refers in general to all methods and procedures to measure how reliable a device is.

### 2.1 Reliability definition

The IEEE defines reliability as: "The ability of a system or component to perform its required functions under stated conditions for a specified period of time" [2].

Mathematically, reliability is the probability of a system to works correctly up to time *t*. One simple, commonly used model, is the exponential distribution. In this model the failure rate  $\lambda$  is a constant and the reliability R(*t*) at time *t* is given in eq. (2.1).

$$R(t) = e^{-\lambda t}, \lambda =$$

failure rate (2.1)

Reliability theory and reliability engineering make extensive use of the exponential distribution because of its *memoryless* property. This property is well-suited to model constant hazard rate components or systems. Memoryless means "the past has no bearing on the future behaviour". The probability that a component fails in the near future is always the same and doesn't depend on its current age. Every instant is like the beginning of a new random period, which has the same distribution regardless of how much time has already elapsed. Exponential distribution is also very convenient because it is easy to combine failure rates of independent components to find a reliability model of a complex system.

However, the exponential distribution is not appropriate to model the overall lifetime of organisms or technical devices, because their "failure rates" are not constant: more failures occur for very young and for very old systems.

The life cycle of a population of semiconductor devices, and of any living organism, can be graphically represented with a curve called "bathtub curve" (Figure 2.1), which models the cradle to grave instantaneous failure rate vs. time. While the origins of the curve are still uncertain; we can find studies from as far

as 1693 [**3**] showing human beings life expectancy having this kind of bathtub curve behaviour. The curve consists of three periods: infancy, useful life and wear-out. The earliest period, with steepest part of the curve, has the highest but decreasing failure rate, known as infant mortality,. Alternatively, the flat part of the curve, known as useful life (normal life) or random failure, depicts the lowest failure rate, relatively constant over an extended period of time, here is where the exponential distribution makes sense. The rightmost part of the graph, where the curve goes up again, represents the increasing failure rate when reaching the end of life, due to intrinsic material issues and accumulative electrical or mechanical stresses.

Figure 2.1 The bathtub curve

### 2.1.2 Associated standards

The International Electrotechnical Commission (IEC) develops and maintains international standards that provide systematic methods and tools for dependability assessment and management of equipment, services, and systems throughout their life cycles [4]. The commission defines dependability as "the collective term used to describe the availability performance and its influencing factors : reliability performance, maintainability performance and maintenance support performance" [5]. Consequently, in systems engineering, reliability is one of the performance characteristics contributing to asses a system's dependability.

Reliability engineering is related to safety engineering and system safety: they use similar methods for their analysis and may require mutual feedback. While reliability engineering focuses mainly on costs of failure; the focus of safety engineering is normally not on cost, but on preserving life and nature. High reliability levels are usually necessary to obtain high safety levels.

Functional safety ensures adequate protection against each significant hazard affecting any system, and is a concept applicable across all industry sectors. It is crucial to enable the use of complex technology for safety-related systems. It assures that the systems offers the necessary risk reduction required to achieve a proper safety level for an equipment. IEC 61508 [6] defines appropriate means for achieving functional safety in electrical/electronic/programmable electronic safety-related systems.

As the use of electronic components responsible for safety and mission-critical parts raises the necessity for high-dependability systems, different application fields have determined their own standards, defining and providing guidelines in the managing of components and systems reliability and safety.

In particular, car manufacturers are adopting the ISO 26262 standard [7], which is an adaptation of the IEC 61508 for Automotive electric and/or electronic (E/E) Systems in series production passenger cars. ISO 26262 addresses possible hazards caused by malfunctioning behaviour of E/E safety-related systems and their interactions. It demands a number of auditing processes during the whole product's lifecycle, to insure high reliability and mission safety throughout the system useful life. Remarkably, in mission testing for error detection demands the adoption of on-line self-test technique as an essential test process in critical E/E vehicle parts.

Another example of a domain-dependant standard dealing with Reliability, Availability, Maintainability and Safety (RAMS) issues is CENELEC EN pr50126 [8], (still under ratification process). In particular in its part 4 [9] gives guidelines for their specification and demonstration in electrical/electronic railway equipment and programmable electronic systems.

### 2.2 Characterization methods

Various methodologies aiming at assessing systems reliability have been the subject of scientific and industrial research. They are overall called *testing*, generally meaning measuring the output response to specific signals (usually called test patterns or test vectors) applied to the inputs, and comparing them with the known good response (golden solution) obtained by simulations. There exist different testing strategies, and they are also applied at different moments of a semiconductor device lifetime, in order to characterize its reliability.

Tests may be structural or functional. The first category includes all testing techniques that take advantage of deep knowledge of the internal structure of the Device Under Test (DUT). This kind of test checks that each element of the device is working as expected. The stimulus to be applied are simpler, because they target one element, so they can highly benefit from automation. However, this kind of test lacks overall view of the device and also it is difficult to assess a device's performance with this kind of techniques.

Tests belonging to the latter category do not need any information about the internal architecture, they use the functional specification of the device. They control that the DUT behaves as expected, and are useful to measure performances, though determining the proper stimuli to perform a functional test is usually a job requiring a lot of expertise that relies on the test engineer.

Another possible classification is according to the lifetime phase in which they are applied, roughly in two categories:

- Manufacturing testing

- On-line testing

Figure 2.2 shows an overview of the semiconductors characterization process, with all the testing steps a single digital device may suffer along his lifetime. In the next sections we will concisely describe the characteristics of each methodology, the equipments, tools and methods used, and the results that can be obtained.

Figure 2.2 Semiconductors characterization process

### 2.2.1 Manufacturing testing

Manufacturing testing allows the evaluation of the performances of the target device at production time.

Semiconductor devices are very sensitive to impurities and particles. To manufacture these devices it is necessary to manage many processes while accurately controlling the level of impurities and particles. Consequently, even if the device's design was verified to be correct, there is no guarantee that the manufactured device is compliant with the design requirements. Therefore, manufacturing testing comes into role.

A methodology and equipments that can verify that each manufactured chip behaves as the reliable designed circuit and has no defects, at least immediately after manufacturing process. The manufacturing test main goal is to classify good from bad devices. Additionally, it can help in determining if there is any phase of the fabrication process that is systematically introducing a defect in the produced chips, by performing some kind of diagnosis.

In general, manufacturing test consists in applying a test pattern to a device under test by means of an external Automatic Test Equipment (ATE), sometimes profiting from a Design-for-Test (DfT) feature present on the devices itself, collecting the responses from the DUT and determining if the device is good or not. Eventually some extra data can be collected to perform a diagnosis of the found faults and aide in improving the fabrication and/or design process.

#### 2.2.1.a Wafer Sort & After Packaging Final Test

Chip fabrication is a very complex process, performed in various steps. Tests are executed in various stages, in order to prevent expending money, time and efforts in finishing a non-working device.

When a wafer is ready, *wafer test* (a.k.a. *wafer sort*) is performed to all dies present on the wafer, looking for functional defects, by applying special test patterns to them. Faulty dies are marked, so only *known good dies* will be packaged; also repairing may be a possibility in next manufacturing steps; or eventually, if the number of faulty individual integrated circuits is greater than a certain threshold, the whole wafer may be discarded.

Once the *known good dies* have been packaged, a final test is needed to verify the packaging process itself didn't affect the devices, and also that the pin connections were correctly wired.

#### 2.2.1.b Burn-in

In general, manufacturers want to avoid introducing to the market chips that will fail in an early stage (left-most part of the bathtub curve). If the application is critical, the justification is obvious; but even for non-critical applications, early failing chips may degrade the company's image and this is never an objective. To detect these common cases known as infantile mortality, a special procedure, called *burn-in*, is applied to them. Burn-in consists in subjecting the devices to particularly stressing conditions, in general determined by extreme temperatures and supply voltage, for a specified period of time. These stressing conditions work as a time machine for the chips (unluckily, only fast forward option is available). After the burn-in period, the final test is performed again to the devices. In this way, chips that were subject to infant mortality, won't make it into the market.

In order to characterize the bathtub curve, the complete burn-in process, that is covering all three stages of a device lifecycle, is to be performed on a statistical sample of products.

#### 2.2.1.c Automatic Test Equipment

For all the manufacturing tests previously described an apparatus is in charge of applying the tests to the DUTs. Using automation, the Automatic Test Equipment (ATE), is able to perform the testing process. Basic component of the system are:

A *computer* in charge of controlling the process and the different instruments that will be connected to the DUT.

A variable number of *instruments*, which performed the desired measures, applying stimulus and collecting results.

A *fixture* that is the physical place holder for the DUT, where it connects to the ATE.

Eventually, a *handler* to place the packaged chips in the fixture; or *probes* that connect directly to the DUT when wafer testing.

It can be from as simple as computer controlling a multimeter, to a complex equipment, performing many different analogue and digital measurements.

#### 2.2.1.d Design for Test

With more than 1 billion transistors in a 22 nm technology microprocessor, and Moore's law **[10]** yet to be denied, the complexity of the devices under test is correctly expected to continue to increase. Considering this, the minimum number of test vectors is also increasingly impossible **[11]**, even with the most

fast and efficient ATE. In a Very Large Scale Integration (VLSI) integrated circuit (IC) it may take thousands of years to fully excite all possible states of a DUT. Of course, nobody can afford such a long process. Moreover, due to complexity, not all possible states may be reachable just manipulating the primary inputs of a device.

This testing problem can be avoided and its solution is called Design for Test (DfT). Circuits are designed in a way that make them efficiently testable; in particular using the sequential parts of them. This design modifications help the circuits to be tested with an acceptable fault coverage and in an acceptable time and, furthermore, to overcome the problem of test access.

The added special features can allow the control and observation of deeply embedded nodes to verify circuit functionality and detect fabrication defects. Performance loss due to their inclusion must be minimal in normal (non-test) operating mode. DfT may also help in making the process of application and observation of test vectors particularly suitable to automation.

The most popular DfT techniques are structured scan-based approaches (e.g., scan chains [12], boundary scan [13]), but there are also other useful ad-hoc techniques to be applied at the design stage (e.g., test point insertion [14], partitioning [15]).

#### 2.2.1.e Test pattern generation

We already stated that in order to test a device a set of test patterns are applied to it, usually by means of an ATE. However, a very time consuming and important part of the characterization process is the generation of these test patterns. Essentially, test patterns are the stimuli to be applied at the inputs of a device in order to obtain an expected output. If we want to thoroughly test a component, the stimuli should be chosen carefully, extended enough so all the device's parts are excited; but also minimum, so as to minimize the test application time and the memory needed to store the patterns.

Often, generation effort and time of the patterns are an issue in themselves; Automatic Test Pattern Generation (ATPG) profits from the Design for Testability features included in-chip in order to generate at minimum cost a set of complete and efficient patterns. This kind of patterns and their possible optimization (compaction, compression, etc.) suit well for scan-chain based testing.

However, depending on the DUT or on the type of test, scan-chains may not be a possibility, or at least not an optimal one. For example, mixed-signal devices or on line testing of digital devices can hardly benefit from scan-chains. In these cases, carefully crafted input test patterns may be manually designed by the test

engineer in order to properly excite the circuit under test; being this a usually onerous task.

#### 2.2.1.f Test Results

Once the patterns are applied, the responses from the DUT shall be compared onthe-fly with the golden model; i.e., the expected good response; or collected to be compared in a latter phase. In order to minimize data to be processed (and/or stored), different compression schemes were identified. Usually, one or more signatures will be generated from all the answers the DUT gave to all the applied patterns, and it is only these signatures that will be compared with the expected ones. The go/nogo verdict for the device will be decided basing on this. These comparisons can be made off chip by the ATE applying the stimuli; or eventually the outputs from the signature analyzer can be checked by a built-in checking circuit.

#### 2.2.1.g Diagnosis

Chip diagnosis is usually a process performed once testing is over, it usually implies the collection of more than the go/nogo response from test phase. This data will be processes, more or less automatically, in order to provide the diagnosis engineer with as much information as possible, so he/she can individualize a possible problem in the production chain.

#### 2.2.1.h Built-In Self-Test

A further step in aiding manufacturing testing is generating patterns and evaluating results on-chip, this approach is called Built-In Self-Test [16]. This technique requires some dedicated logic to have pattern generation, response analyzer and test application controller implemented in the hardware itself [17].

The generation can be from just a ROM storing the patterns to a Linear-Feedback Shift Register (LFSR) generating pseudorandom patterns on the fly, and also different implementations of counters.

A modified Linear-Feedback Shift Register (LFSR), called Multiple-Input Shift Register (MISR) [**18**], is a well-known technique widely used to implement the signature analyzer.

Besides, some methodologies were proposed so that the BIST added to the chip can also be used, complete or in part, during online testing **[19] [20]**.

#### 2.2.2 Online testing

Online testing are a group of techniques aimed at detecting the occurrence of a fault during the product mission time and to correct possible misbehaviours.

Reliability of semiconductor devices may also depend on assembly, use, and environmental conditions. Stress factors affecting device reliability include gas, dust, contamination, voltage, current density, temperature, humidity, mechanical stress, vibration, shock, radiation, pressure, and intensity of magnetic and electrical fields. If we want to guarantee a system or component reliability throughout time, the manufacturing test is not enough. Other tests need to be performed during its useful lifetime. There are different methodologies for online testing with different levels of confidence and consequences for the application.

Start-up testing, when a system is booting, before putting it to actual service, testing of some or all of its components can be performed. This implies no consequence for the application, as it is not yet running, it is useful for systems that are consistently restarted throughout their mission time, like the Power-On Self-Test (POST) of a computer memory.

Non-concurrent online testing is another strategy consisting in testing the system while the application is running, but with some constrains. This is, performing the test in one component of the system or in one part of the component that is not being used for the main application while tested. For example, testing one peripheral that is not being used; or testing a part of the memory chip after properly saving its content to a region not under test; and restoring the content after performing the test. This strategy is less intrusive than the start-up test, in the sense that it allows the application to run, but anyway it somehow prevents the complete free behaviour of the application. This kind of testing can be applied at periodic intervals, or its execution can be triggered by a particular situation present at the DUT. Some safety standards required this kind of periodic testing for critical systems as a car electronic control unit.

The third strategy is concurrent online testing, it consists in testing the device or system while the application is fully executed in the device under test. This is, of course, the less intrusive strategy from the point of view of the user application. However, it is not easy to find the proper stimuli and results collecting and analysis methodology. One example of this kind of online testing is the concurrent error detection (CED) mechanisms, for memories and processors, where an output characteristics predictor and a checker, can detect errors while the application is running.

#### 2.2.2.a Software-Based Self-Test

The principle of software-based self-test (SBST) is to run functional test patterns, based on the processor instruction set; i.e., exploiting processor resources to test the processor itself and the components around it **[21]**.

SBST consists in forcing the embedded processor(s) to execute a carefully crafted test program, i.e., a sequence of instructions capable of thoroughly exciting possible device faults and propagating the fault effects to some observable point(s). The test program can either be stored in a non-volatile memory, or uploaded in a RAM immediately before the test execution. SBST does not require circuit modifications (therefore making it particularly suitable for the test of third-parties cores, which can hardly be modified) and may offer good defect coverage, since it is executed at the same speed of the normal applications. Moreover, it can be performed both at the end of the production process, and during the operational phase (e.g., for periodical on-line testing); when the functional approach is used for on-line test, the results are typically checked by the system itself.

This strategies is firmly included in the manufacturing flow of microprocessors. Industrial experiences, such as **[22]** and **[23]** have confirmed the suitability of the methodology. In **[24]** an interesting case targeting a multi-core processor is presented. In that experience functional patterns are loaded in cache and applied to each of the 8 Processing Units belonging to a 4 GHz multi-core server in order to perform partial-good device binning.

SBST is also an appealing alternative for identifying faults during normal operation of the product, by performing on-line testing **[25]**. Several reasons push this choice: SBST does not require external test equipment, it has very little intrusiveness into system design and it minimizes power consumption and hardware cost with respect to other on-line techniques based on circuit redundancy. It also allows at-speed testing, a feature required to deal with some defects prompted by deep submicron technology advent.

However, some additional aspects have to be taken into account when dealing with test program generation for on-line purposes. The test program must first be able to properly excite the considered processor modules, and then, once the results have been produced, it must turn them observable from the outside in a transparent way that does not affect the normal operation of the mission application. The most important constraints for on-line testing include:

• *Preserving the processor status*: the status of the interrupted mission (i.e., the processor status register content) has to be saved and restored at the end of the test.

- *Execution time*: duration must be as short as possible complying with the requirements stated in the adopted safety standard [7].

- *Memory content*: it is crucial to prevent mission software and test programs from overriding information belonging to other processes. Code and data memory belonging to the test procedures must be clearly defined and limited considering the system memory map of the device.

- *Code Memory footprint*: the code memory space required by the test programs should not be excessive, and it must conform to the established memory limits.

- *Data Memory footprint*: the data memory space must also be as short as possible. However, the data memory placement can play a significant role with respect to the effectiveness of the generation process.

In the next chapter particularities and constraints in the testing of different electronic devices will be detailed.

# Chapter 3 Characterization - Different devices, different strategies

### 3.1 Systems-on-a-Chip

With the advent of SoC, the low-cost concept has become a common denominator among test generation and test application.

In fact, in the SoC terminology, the term low cost is commonly used to classify a set of strategies and equipment that exploit DfT features included on a chip to reduce test costs without impacting its effectiveness **[26][27][28][29]**.

The costs of SoC test procedure involve many factors, that are primarily test pin count, application frequency and tester memory depth for pattern and data storage. Many efforts have been done to blow it down in recent years **[30]**.

Low-cost scan-based test approaches rely on design techniques that allow the minimization of the number of tester channels [**31**] and the tester frequency requirements [**32**]. In addition to (or in substitution of) traditional scan cells, these techniques adopt suitable DfT features such as decoders and phase-locked loop (PLL)-based circuitries; the former addresses pin count minimization, and the latter permits moving deterministic patterns in the chip at reduced speed, thus applying them at higher frequency. The introduction of test access protocols, as [**33**] and [**13**], to transport information inside the SoC architecture mainly addresses pin count reduction, often at the expense of the bandwidth [**34**]. Conversely, self-test procedures address frequency requirement mitigation, since it normally exploits internal or independent clock supply resources that do not request any external intervention.

Low-cost self-test approaches may be based on infrastructure intellectual property (I-IP) **[35]** or may employ functional parts of the DUT itself. The key point is that, once launched, a self-test procedure is autonomously applied until it ends. A further sub-classification for low-cost self-test approaches may include software-based self-test (SBST) **[36]** and BIST strategies **[37][38]**. Test procedures exploiting both SBST and BIST principles consist of at least three

parts: 1) a preliminary initialization phase aimed at loading at low-frequency the test microcode and/or setting parameters; 2) a self-test execution at high frequency; and 3) result download at low frequency.

Another strategy aimed at saving test costs is pattern compression. Such technique is intended to reduce the overall size of the test vectors to be applied to the DUT, thus reducing the test time. In the data compression techniques presented in [**39**] and [**40**], the process is performed by suitable software tools and consists in encoding the test vectors using as few bits as possible. Compressed data are then reconstructed, or decompressed, by ad hoc hardware decoders/decompressors placed on a chip or on the tester. In the specific field of embedded memory diagnosis, some approaches have been proposed to compress the results of the memory algorithm, finally providing a signature that synthesizes the amount of diagnostic data [**41**]; the drawback of this strategy is a potential loss in the diagnostic resolution.

Testing costs are stigmatized when the objective is diagnosis. In the case of volume diagnosis, the low cost is a must. Not only an increased quantity of information has to be downloaded but also diagnosis time may explode because diagnostic procedures frequently encompass many test iterations.

#### 3.1.1 Microprocessors

Testing embedded microprocessors is one of the most challenging tasks to be performed at the end of the SoC production cycle [42]. Exhaustive testing is hardly a solution, since executing all the possible instructions, in all their feasible addressing modes, with all the potential data combinations, in all possible orders, starting from all the reachable initial states, may take extremely long testing times, and no one can afford waiting that long. Conventionally, testing strategies are largely based on the introduction of additional Design for Testability (DfT) hardware devoted to perform structural testing; scan chains [12] and Built-In Self-Test (BIST) [43] are well known and very popular solutions. Functional methods, such as Software-Based Self-Test (SBST) [21], are today increasingly used. Actually, hardware- and software-based techniques appear to be complementary and are often exploited in a more general testing plan including both of them [44].

There are various aspects to be taken into account when implementing a testing strategy for microprocessors: fault coverage, ability of the test to be executed at maximum speed, acceptable test time, guarantee of independence and Intellectual Property of the different cores to be tested in the system, area overhead introduced by the DfT module.

Moreover, when designing an on-line test strategy other issues must likewise be considered: preservation of the previous microprocessor state, ability to provide the diagnostic information and the fulfilling of the timing constraints considering that generally the time slice assigned to test execution is shorter than the test program itself, among others.

Today, SBST and other microprocessor functional testing approaches are gaining again popularity after many years in which scan-based approaches have been largely preferred. This is due to many reasons: the latest technologies show timing-related faulty behaviours that can be investigated in a more accurate manner using SBST [45], while avoiding over-testing and over-consumption; SBST techniques are cost and time effective, since they request few tester channels and limited memory amount on the tester; the self-test program can be stored in a non-volatile memory and activated also during the component lifetime to perform on-line testing. In the automotive and other safety-critical fields, emerging standards [7] and regulations mandate high fault coverage figures and usually require in-field testing (e.g., periodic on-line testing, power-up testing) that can be more easily implemented through SBST.

Many efforts have been invested in the past 30 years on the functional and SBST topic. Academy **[46] [47] [36]** and industry **[48][49]** have proposed many techniques solving general test problems and giving solutions to functionally reach the highest possible fault coverage.

Current state-of-the-art techniques include different strategies able to generate test programs resorting to manual and automatic approaches; generally, the proposed methodologies are generic enough to be easily adapted to various processors. New grading techniques to rapidly characterize test programs have also been proposed [**50**]. However, reducing costs related to both test program fault grading and test application is still an open issue.

Some interesting approaches tried to merge SBST principles with smart architectural solutions. In **[22]** a solution was proposed to generate suitable instruction sequences for testing, which are stored in the processor cache for sake of efficiency. In **[51]** a hybrid SBST technique was introduced that merges pseudo random pattern generation and functional processor behaviour knowledge.

Recently, the some specific issues raised by the on-line test of specific processor modules have been discussed and partly solved in **[52**].

Today, the problem of test is especially critical in the case of embedded processor cores. Their wide diffusion is increasing the challenges in the test arena. Modern designs include complex architectures that further increase test complexity, as pipelined and superscalar designs. Single sub-components in a microprocessor may be autonomously tested by accessing their inputs and outputs through specific test buses built in the chip, and by applying specific test patterns, or resorting to integrated hardware, such as with Logic Built-In Self-Test (LBIST) [53]. Within this framework, a critical issue is the system integration test, where the whole processor and the interconnection between different modules have to be checked. At this level, one suitable possibility is to let the processor execute carefully crafted test programs.

#### 3.1.2 Memories

#### 3.1.2.a Memory SW BIST

We use the term SW BIST to denote a test solution targeting memories embedded in a SoC, based on performing the test through a suitable program executed by a processor inside the SoC: the program is in charge of executing the sequence of accesses to memory (for both read and write purpose) mandated by a given test algorithm (e.g., corresponding to a March algorithm).

Several published works, including those from industry (e.g., [54][55][56]), underline the fact that various memory defects existing in new technologies require the test accesses to be performed at the maximum speed (or at least at-speed) in order to be detected; this constraint is called Back-to-Back (or BtB) execution. The authors of [57] and [58] performed a careful analysis to understand how to match the BtB constraint when implementing test programs for CISC and RISC processors, respectively. Clearly, access to memory is performed through suitable instructions (i.e., LOAD and STORE in RISC architectures). However, implementing a March element in any assembly language requires addressing some critical issues:

- Loops

- Read result evaluation

- Memory address generation.

In the following we will detail each issue and summarize the limitations preventing the traditional SW BIST implementations to fully satisfy the BtB constraint.

#### Loops

When a March Element of a memory test is implemented in software, some instructions should be devoted to manage the loop in charge of repeating the required LOAD/STORE instructions for each memory word in the given order. Managing the loop requires introducing some index variable, which is updated and tested at each iteration; a conditional branch also needs to be executed.

During the execution of these instructions the memory is not accessed, thus, violating the Back-to-Back (BtB) constraint required for the detection of speed-related faults.

A possible solution relies on loop unrolling. However, this is a partial solution as we cannot infinitely unroll the loop in order to satisfy the BtB requirement for all memory access as mandated by a March Element. Moreover, even solving the problem partially leads to a significant increase in the code size (requiring larger memory).

#### Read result evaluation

March algorithms include read and verify instructions that require the read value from memory to be compared with the expected one. Usually, the check operation is interposed between the memory access ones, thus preventing the BtB constraint to be satisfied.

#### Memory address generation

March algorithms typically require to access all words in the target block in a given order. When BIST is implemented in hardware, address generation represents a major component of the required circuitry (in some cases up to 30% of the BIST, as reported by Mentor Graphics and others [59][60][61]). When SW BIST is considered, updating the memory address from one memory access to the following may require additional instructions, hence violating the BtB requirement. This issue becomes even more critical when the memory physical addresses do not match the logical ones, due for example to scrambling, mirroring and folding. In these cases scanning the memory words in the desired order may require complex pieces of code to be added, in charge of computing the physical address for every memory access. In [58] it is shown that some of these scanning sequences (e.g., fast-row) cannot be implemented when the assembly language of specific RISC processors is considered. Moreover, implementing memory tests usually require the use of multiple Data Background (DB) values. Once more, preparing the right DB value for each instruction may require additional assembly instructions, thus violating the BtB requirement.

Finally, it should be noted that the adoption of the SW BIST requires storing the code implementing the test somewhere in memory; in this way, not only the total amount of required memory increases, but we also somehow perturb the memory footprint with respect to the one required by the "pure" application.

#### 3.1.3 Mixed-Signal devices

#### 3.1.3.a Analogue-to-Digital Converters (ADC)

The dynamic performances of an analogue-to-digital converter (ADC) reflect the noise and the distortion introduced by the ADC in its signal path [**62**][**63**]. They are typically measured by injecting a single-tone sine-wave signal at the input of the ADC and computing a Fast Fourier Transform (FFT) of the output [**62**][**63**]. In the context of a Built-In Self-Test (BIST) technique aimed at computing the dynamic performances on-chip [**64**], it is required to replace the computationally intensive FFT algorithm with an alternative algorithm that can be implemented efficiently using digital resources. A well-known algorithm for doing this is the sine-wave fitting algorithm [**65**][**66**][**67**]. A variant of this algorithm with reduced complexity and, thereby, more efficient digital implementation, is proposed in [**64**] for the case of a BIST technique for a stereo switch-capacitor (SC)  $\Sigma \Delta$  ADC. Another variant of this algorithm that is even less complex is proposed in [**68**] and makes use of the COordinate Rotation DIgital Computer (CORDIC) algorithm [**69**].

### 3.2 Sensors

#### 3.2.1.a Micro-Electromechanical Systems (MEMS) Inertial Sensors

Micromachined inertial sensors, commonly known as accelerometers and gyroscopes MEMS (Micro-ElectroMechanical Systems), are one of the most important types of silicon-based sensors; indeed they reached 25% of the MEMS market in 2008 according to market analysis reports [**70**] and their market is forecasted to continue to grow. In fact, MEMS inertial sensors are widely used in automotive and aeronautics applications and are becoming extremely popular (21% expected annual growth) in a wide range of consumer electronics products, encompassing smart phones, 3D game consoles, personal media players, aided navigation systems, and camcorders stabilization systems. High volume production coping with the huge market demand is a crucial issue for the industry. Of course, the cost of testing is a major one within the MEMS manufacturing process; therefore, relevant efforts are currently being spent to speed up the test process by achieving high parallelism rates at a low cost and without losing screening effectiveness [**71**].

MEMS come from the integration of mechanical elements, sensors, actuators and electronics on a common silicon substrate through micro-fabrication technology. Their complex nature makes the testing issues even more challenging than for conventional semiconductor integrated circuits; advanced CAD and mechanical tools are needed to enable testing of a MEMS device in all stages of its production. Final test flow encompasses many actions to be performed at different realization steps, as it is graphically shown in Figure 3.1.

Figure 3.1 MEMS testing flow.

First, silicon parts of MEMS are tested at the wafer level by means of electrical wafer sort using an ATE (Automatic Test Equipment), possibly exploiting Design for Testability circuitries included on-chip, such as scan chains and self-test engines, similarly to common integrated circuits. This test phase only partially proves MEMS goodness; devices passing this preliminary stage are packaged and have to undergo a second test step that aims at checking their overall functional behaviour. Since MEMS are designed to respond to physical stimulation (i.e., movements, hits, sounds) with electrical signals, such a testing phase requires the application of physical stimuli beyond the electrical ones. After the parametric testing, aimed to assure the conformance of the accelerometer to the mechanical and electrical requirements, two consecutive operations are performed: *Calibration* (or Trimming) and *Functional Testing*.

Calibration is compulsorily performed on every single MEMS sensor before proper usage. It suits to find out some inherent constants (or trimming values) related to the device working principle [72][73][74]; trimming values change from chip to chip and are stored inside the Device Under Test (DUT) in a proper manner, such as using trimmed resistors, fuse transistors, ad-hoc registers or some kind of non-volatile memory, like a flash memory. Following calibration, functional testing of a MEMS component consists in applying a known physical stimulation and reading the device's output; if the measured value differs from the expected one the component is rejected, otherwise it is shipped to market.

Detailed descriptions of infrastructures (often known as Automatic Test Stations, or ATS) and methodologies for inertial MEMS calibration and testing can be found for accelerometers in [75] and for gyroscopes in [76][77]. Such equipment may be capable of performing the calibration and test process for many devices in parallel.

Many commercial MEMS implement self-test techniques [78][79][80][81][82], often based on BIST modules able to test the mechanical system through electrical stimuli. However, typically none of the preceding MEMS BIST techniques can be used to replace the traditional manufacturing test. The reason comes from the fact that considering the fabrication variations, the electrostatic force has to be calibrated first for each individual MEMS device before the device operates in self-test mode, and the calibration process requires the device to be thoroughly tested using external test equipment [83]. No matter the fact that BIST approaches are widely used for in-field, offline or online testing, they cannot perform sensor calibration if the BIST itself isn't calibrated firstly. Thus, calibration needs to be performed on each device by means of an ATS at some point in time before releasing it to the market.

Some efforts have also been done to devise a fully electrical method to estimate the sensitivity of capacitive MEMS accelerometers in batch fabrication without the need of mechanical test equipment [84]. This approach proved to be useful in reducing the dispersion of the sensors sensitivity, with an improvement that could be enough, typically for low-cost accelerometers. However, functional test, needing mechanical test equipment, is still required at least on a sample batch of sensors, for each sensor model that is being calibrated; finally, it is important to note that functional test cannot exploit parallelism, since the tester has to calculate the trimming values for each DUT.

The second part of the thesis describes the contributions made to the state of the art in three different testing areas: SBST, BIST and ATE.

# Part II CONTRIBUTION TO THE STATE-OF-THE-ART

## Chapter 4 Proposed test programs for SBST of microprocessors

A widespread strategy to perform online testing of microprocessors is Software-Based Self-Test (SBST). The next sections describe SBST programs generation strategies for three very critical units of pipelined microprocessors: Prediction units, Register Forwarding & Pipeline Interlocking units and Address Adder units. In particular for the Address Adder unit the online constrains are carefully taken into account and a suitable strategy is proposed.

### 4.1 Prediction Units

A Prediction Unit is a mechanism to support speculative execution in order to overcome the performance penalty caused by branch instructions in pipelined microprocessors. Being an intrinsically fault tolerant unit, it is hard to achieve a good fault coverage resorting to plain functional testing methods. In this chapter we analyze the causes for low functional testability and propose some techniques able to effectively face these issues. In particular, we describe a strategy to perform SBST on an specific type of prediction units: fully associative Branch Target Buffer (BTB) units. The unit's general structure is analyzed, a suitable test program is proposed and the strategy to observe the test responses is explained. Feasibility and effectiveness of the proposed approach are shown on a MIPS-like processor.

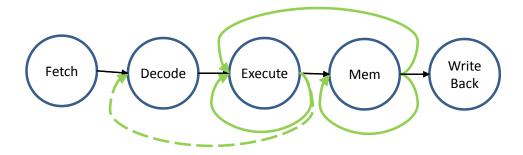

Speculative execution has long been used as a way to overcome performance penalties derived from branches present in the instruction stream of pipelined microprocessors. A typical pipelined architecture has at least Fetch, Decode and Execute stages; one instruction per clock cycle is fetched, but it is not identified as a branch instruction until it reaches the *DECODE stage*; moreover, the branch is normally not resolved (i.e., the computation to know whether the branch should be taken or not-taken and to get the target address of the branch are not performed) until the Execution step. So, once a branch instruction is fetched, in order not to stall the pipeline, the microprocessor must fetch the next instruction, with no deterministic information if it is the correct one. If the wrong next instruction is fetched, some clock cycles, depending on the processor branch delay slot, are lost since the processor pipeline is flushed and new instructions

are fetched instead. Here is where branch prediction comes into play. Many strategies have been proposed to tackle this problem; from static always taken or always not-taken approaches to more complex dynamics ones, such as the Branch Target Buffer (BTB) mechanism, based on statistical principles.

Prediction accuracy of BTB mechanisms varies according to the different prediction algorithms, reaching up to 98.1% [85], when applying combined approaches.

All branch prediction execution strategies are error resilient by nature, because ultimately, in the Execution step, the correct next instruction is known for sure. If an incorrect decision was predicted, the pipelined will be flushed and the processor will fetch the correct stream of instructions. This behaviour does not lead to any functional error but at most to a performance penalty of two or more clock cycles, depending on the architecture. However, the faults present in the prediction unit may have a negative impact on the processor performance.

In order to detect these faults, a suitable test strategy is needed. The use of structural approaches, such as scan test or BIST, is not always possible; moreover, some of them are not suitable for at-speed testing, require an expensive external tester, or may not be adopted by designers because they put at risk the IP protection; finally, they may not represent the optimal solution (they have some area overhead, may lead to extra power consumption and often do over-testing). For these reasons, sometimes functional approaches, like Software-based Self-Test (SBST), are preferred [21]. SBST consists in uploading to the processor memory a sequence of assembly instructions, the so called test program, and then forcing the embedded processor to execute them. The test program should be capable of thoroughly exciting possible device faults and propagating the fault effects to some observable points. This technique does not request any circuit modification, therefore making it suitable for the test of thirdparties cores. Moreover, this kind of test is, by definition, performed at-speed. Finally, test programs generated following the SBST approach are well-suited to be used for on-line testing.