### POLITECNICO DI TORINO

### SCUOLA DI DOTTORATO

Dottorato in Ingegneria Elettronica e delle Comunicazioni – XXV ciclo

Tesi di Dottorato

## Emerging Technologies -NanoMagnets Logic (NML)

Marco Vacca

**Tutore** prof. Mariagrazia Graziano

Coordinatore del corso di dottorato prof. Ivo Montrosset

April 2013

### Summary

In the last decades CMOS technology has ruled the electronic scenario thanks to the constant scaling of transistor sizes. With the reduction of transistor sizes circuit area decreases, clock frequency increases and power consumption decreases accordingly. However CMOS scaling is now approaching its physical limits and many believe that CMOS technology will not be able to reach the end of the Roadmap. This is mainly due to increasing difficulties in the fabrication process, that is becoming very expensive, and to the unavoidable impact of leakage losses, particularly thanks to gate tunnel current.

In this scenario many alternative technologies are studied to overcome the limitations of CMOS transistors. Among these possibilities, magnetic based technologies, like NanoMagnet Logic (NML) are among the most interesting. The reason of this interest lies in their magnetic nature, that opens up entire new possibilities in the design of logic circuits, like the possibility to mix logic and memory in the same device. Moreover they have no standby power consumption and potentially a much lower power consumption of CMOS transistors.

In literature NML logic is well studied and theoretical and experimental proofs of concept were already found. However two important points are not enough considered in the analysis approach followed by most of the work in literature. First of all, no complex circuits are analyzed. NML logic is very different from CMOS technologies, so to completely understand the potential of this technology it is mandatory to investigate complex architectures. Secondly, most of the solutions proposed do not take into account the constraints derived from fabrication process, making them unrealistic and difficult to be fabricated experimentally.

This thesis focuses therefore on NML logic keeping into account these two important limitations in the research approach followed in literature. The aim is to obtain a complete and accurate overview of NML logic, finding realistic circuital solutions and trying to improve at the same time their performance. After a brief and complete introduction (Chapter 1), the thesis is divided in two parts, which cover the two fundamental points followed in this three years of research: A circuits architecture analysis and a technological analysis.

In the architecture analysis first an innovative VHDL model is described in Chapter 2. This model is extensively used in the analysis because it allows fast simulation of complex circuits, with, at the same time, the possibility to estimate circuit performance, like area and power consumption. In Chapter 3 the problem of signals synchronization in complex NML circuits is analyzed and solved, using as benchmark a simple but complete NML microprocessor. Different solutions based on asynchronous logic are studied and a new asynchronous solution, specifically designed to exploit the potential of NML logic, is developed. In Chapter 4 the layout of NML circuits is studied on a more physical level, considering the limitations of fabrication processes. The layout of NML circuits is therefore changed accordingly to these constraints. Secondly CMOS circuits architectures are compared to more simple architectures, evaluating therefore which one is more suited for NML logic. Finally the problem of interconnections in NML technology is analyzed and solutions to improve it are found. In Chapter 5 the problem of feedback signals in heavy pipelined technologies, like NML, is studied. Solutions to improve performances and synchronize signals are developed. Systolic arrays are then analyzed as possible candidate to exploit NML potential. Finally in Chapter 6 ToPoliNano, a simulator dedicated to NML and other emerging technologies, that we are developing, is described. This simulator allows to follow the same top-down approach followed for CMOS technology. The layout generator and the simulation engine are detailed described.

In the first chapter of the technological analysis (Chapter 7), the performance of NML logic is explored throughout low level simulations. The aim is to understand if these circuits can be fabricated with optical lithography, allowing therefore the commercial development of NML logic. Basic logic gates and the clock system are there analyzed from a low level perspective. In Chapter 8 an innovative electric clock system for NML technology is shown and the first experimental results are reported. This clock system allows to achieve true low power for NML technology, obtaining a reduction of power consumption of 20 times considering the best CMOS transistors available. This power consumption takes into account all the losses, also the clock system losses. Moreover the solution presented can be fabricated with current technological processes.

The research work behind this thesis represents an important breakthrough in NML logic. The solutions here presented allow the design and fabrication of complex NML circuits, considering the particular characteristics of this technology and considerably improving the performance. Moreover the technological solutions here presented allow the design and fabrication of circuits with available fabrication process with a considerable advantage over CMOS in terms of power consumption. This thesis represents therefore a considerable step froward in the study and development of NML technology.

## Contents

| Sι | ımm  | ary                                                | II       |

|----|------|----------------------------------------------------|----------|

| 1  | Inti | roduction                                          | 1        |

|    | 1.1  | Quantum dot Cellular Automata (QCA)                | 1        |

|    | 1.2  | Magnetic QCA or NanoMagnetic Logic (NML)           | 5        |

|    |      | 1.2.1 Logic Gates                                  | 7        |

|    |      | 1.2.2 Clock                                        | 8        |

|    |      | 1.2.3 NML logic subtypes                           | 9        |

|    |      | 1.2.4 3-phase overlapped Snake clock               | 10       |

|    |      | 1.2.5 Border crosstalk                             | 14       |

|    | 1.3  | Two phases clock                                   | 16       |

|    | 1.4  | Problems                                           | 16       |

|    |      | 1.4.1 Layout=Timing                                | 16       |

|    |      | 1.4.2 Feedback signals                             | 17       |

|    | 1.5  | NCL logic                                          | 18       |

|    | 1.6  | Integrated design methodology for nanotechnologies | 20       |

|    |      |                                                    |          |

| Ι  | Aı   | chitecture Analysis                                | 22       |

| 2  | NM   | IL VHDL modeling                                   | 23       |

|    | 2.1  | e e e e e e e e e e e e e e e e e e e              | 23       |

|    | 2.2  | Power modeling                                     | 24       |

|    |      | 2.2.1 Power consumption components                 | 25       |

|    |      | 2.2.2 Model                                        | 25       |

| 3  | NIV  | IL architecture level analysis                     | 35       |

| J  | 3.1  | 4 bit microprocessor                               | 35       |

|    | 0.1  | 3.1.1 Full NCL logic                               |          |

|    |      | 3.1.2 NCL-Boolean logic                            | 48       |

|    |      | 3.1.2 Full Roolean Logic                           | 40<br>53 |

| 4 | Imp            | roved  | Circuits Layout                                      | 59           |

|---|----------------|--------|------------------------------------------------------|--------------|

|   | 4.1            | Enhar  | nced clock zones layout                              | 59           |

|   | 4.2            | Comb   | inational logic circuit structure                    | 60           |

|   | 4.3            |        | cation of CMOS architectures to NML logic            |              |

|   |                | 4.3.1  | Pentium 4 adder                                      |              |

|   |                | 4.3.2  | 32 bit Ripple Carry Adder                            | 64           |

|   |                | 4.3.3  | Comparison                                           |              |

|   | 4.4            | NML    | interconnections improvement                         |              |

|   |                | 4.4.1  | Input and output interfaces                          |              |

|   |                | 4.4.2  | Electric interconnections                            |              |

|   |                | 4.4.3  | Applications                                         | 73           |

|   |                | 4.4.4  | Full magnetic interconnections                       |              |

| 5 | Arc            | hitect | ure improvements                                     | 75           |

|   | 5.1            |        | ack signals                                          | 75           |

|   |                | 5.1.1  | Throughput reduction                                 |              |

|   |                | 5.1.2  | Throughput maximization: Data Interleaving           |              |

|   |                | 5.1.3  | Loops length reduction                               |              |

|   |                | 5.1.4  | Signals synchronization with feedbacks               |              |

|   |                | 5.1.5  | Loop Unrolling                                       |              |

|   | 5.2            |        | lic arrays                                           |              |

|   | ٠٠_            | 5.2.1  | Programmable Systolic Array                          |              |

|   |                |        |                                                      |              |

| 6 | <b>Tol</b> 6.1 |        | no: a synthesis and simulation tool for NML circuits | <b>86</b> 86 |

|   | 6.2            |        |                                                      |              |

|   | 6.2            |        | ral structure                                        |              |

|   | 6.4            | _      | Synthesizer                                          |              |

|   | 6.4            |        | L Parser                                             |              |

|   |                |        | al circuits description                              |              |

|   | 6.6            |        | & Route                                              |              |

|   |                |        | Graph elaboration                                    |              |

|   | c 7            | 6.6.2  | Physical Mapping                                     |              |

|   | 6.7            | Simula |                                                      |              |

|   |                | 6.7.1  | Swich model                                          |              |

|   |                | 6.7.2  | Clock generation                                     |              |

|   |                | 6.7.3  | Input generation and simulation data structure       |              |

|   |                | 6.7.4  | The simulation controller                            |              |

|   |                | 6.7.5  | Simulation algorithm                                 |              |

|   |                | 6.7.6  | Matrix exploration                                   |              |

|   |                | 6.7.7  | Magnetization calculation algorithm                  | 114          |

|   |                | 678    | Exception handling                                   | 115          |

|    |              | 6.7.9    | Output generation                              | 118 |

|----|--------------|----------|------------------------------------------------|-----|

| II | $\mathbf{T}$ | echno    | ological analysis                              | 120 |

| 7  | NM           | L phy    | sic level analysis                             | 121 |

|    | 7.1          | Real c   | elock signal waveform                          | 121 |

|    | 7.2          |          | y considerations                               |     |

|    |              | 7.2.1    | Nanomagnets switching energy                   | 122 |

|    | 7.3          | Errors   | s in signal propagation due to misaligned dots |     |

|    | 7.4          |          | ity voter analysis                             |     |

|    |              | 7.4.1    | Majority voter characterization                |     |

|    |              | 7.4.2    | Impact of process variation                    | 128 |

|    |              | 7.4.3    | NMAG automatic C framework                     |     |

|    |              | 7.4.4    | Timing analysis                                | 131 |

|    |              | 7.4.5    | Energy analysis                                | 134 |

|    |              | 7.4.6    | Majority voter input extension                 | 137 |

|    | 7.5          | Invert   | er                                             | 140 |

|    | 7.6          | Globa    | l clock system                                 | 142 |

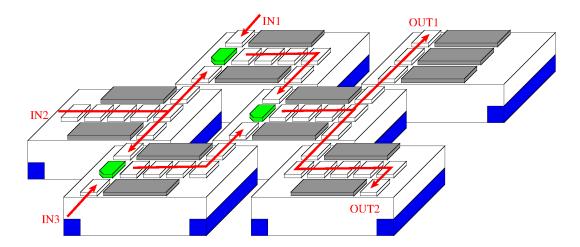

| 8  | Mag          | gnetoe   | lastic clock                                   | 147 |

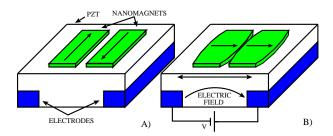

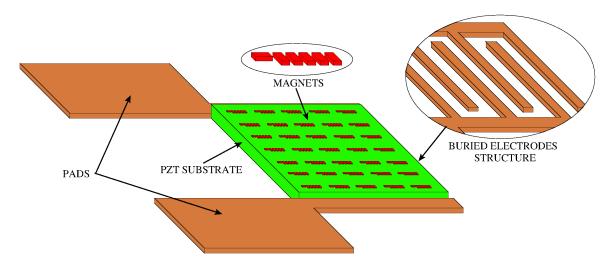

|    | 8.1          | Magne    | etoelastic clock system                        | 147 |

|    |              | 8.1.1    | Clock structure                                | 149 |

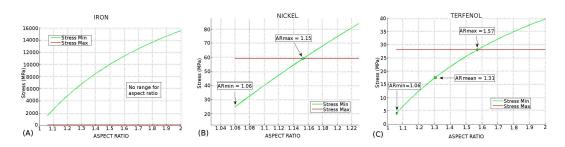

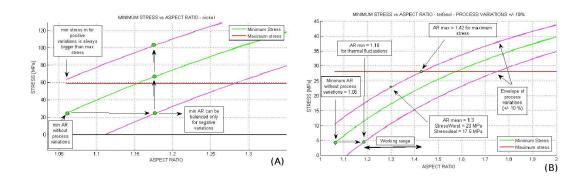

|    |              | 8.1.2    | Choice of magnetic material and magnet sizes   | 150 |

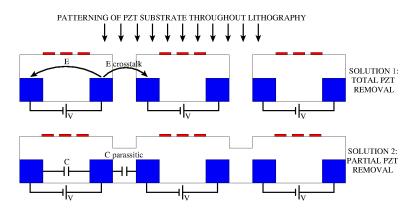

|    |              | 8.1.3    | Circuit Layout                                 | 153 |

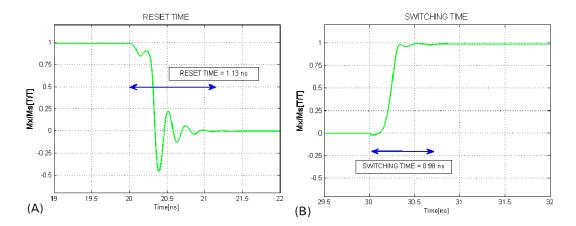

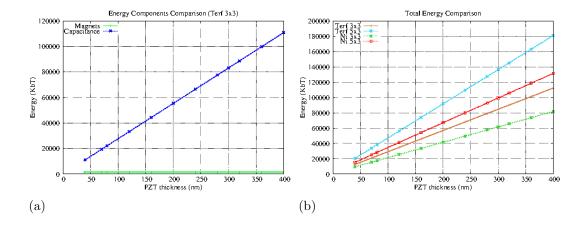

|    |              | 8.1.4    | Performance analysis                           | 156 |

|    | 8.2          | Magne    | etoelastic clock system fabrication            | 160 |

|    |              | 8.2.1    | Electrodes                                     | 161 |

|    |              | 8.2.2    | PZT substrate                                  | 162 |

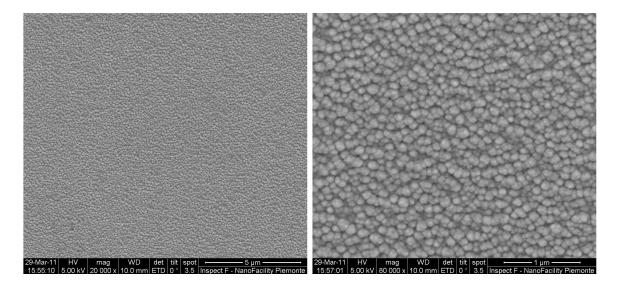

|    |              | 8.2.3    | Magnetic materials                             | 162 |

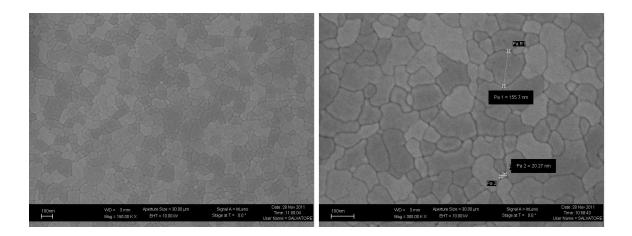

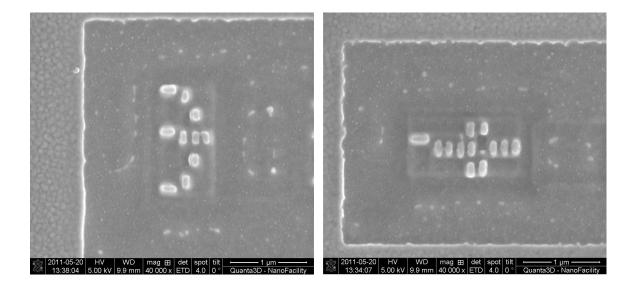

|    |              | 8.2.4    | Magnetic dots                                  |     |

|    | 8.3          | Ackno    | wledgment                                      | 166 |

| II | ${f I}$ $A$  | Appe     | ndix                                           | 167 |

|    | ъ.           | 1        |                                                | 100 |

| A  |              | olicatio |                                                | 168 |

|    |              |          | rences                                         |     |

|    |              |          |                                                |     |

|    | $A \cdot 3$  | Books    | and books' chapters                            | 170 |

| ${f B}$      | How   | to wr   | ite an article - Simple guidelines on how                                     | to | write | you | r   |

|--------------|-------|---------|-------------------------------------------------------------------------------|----|-------|-----|-----|

|              | first | article |                                                                               |    |       |     | 171 |

|              | B.1   | Article | General Organization                                                          |    |       |     | 171 |

|              | B.2   |         | Sections                                                                      |    |       |     |     |

|              |       | B.2.1   | Title                                                                         |    |       |     | 171 |

|              |       | B.2.2   | Authors List                                                                  |    |       |     | 172 |

|              |       | B.2.3   | Abstract                                                                      |    |       |     | 172 |

|              |       | B.2.4   | Keywords                                                                      |    |       |     | 174 |

|              |       | B.2.5   | $Introduction \dots \dots \dots \dots \dots \dots \dots \dots$                |    |       |     | 175 |

|              |       | B.2.6   | Basic Concepts Description                                                    |    |       |     | 177 |

|              |       | B.2.7   | Work Description                                                              |    |       |     | 178 |

|              |       | B.2.8   | Conclusions and Future Work $\ .\ .\ .\ .\ .$                                 |    |       |     | 178 |

|              |       | B.2.9   | Acknowledgments                                                               |    |       |     | 179 |

|              |       | B.2.10  | Bibliography                                                                  |    |       |     | 179 |

|              | B.3   | Hints & | z Tips                                                                        |    |       |     | 180 |

|              |       | B.3.1   | Article Structure                                                             |    |       |     | 180 |

|              |       | B.3.2   | Writing Order                                                                 |    |       |     | 180 |

|              |       | B.3.3   | Language style                                                                |    |       |     | 181 |

|              |       | B.3.4   | $\label{eq:conferences} \mbox{Journals, Conferences, Letters, Book Chapters}$ |    |       |     |     |

|              |       | B.3.5   | Figures                                                                       |    |       |     | 184 |

|              |       | B.3.6   | Latex or Word?                                                                |    |       |     | 184 |

| $\mathbf{C}$ | Prog  | ram fo  | or NMAG automatic parametric analysis                                         |    |       |     | 186 |

| _            | C.1   | _       |                                                                               |    |       |     |     |

|              | C.2   |         | try creation file                                                             |    |       |     |     |

|              | C.3   |         | tion file                                                                     |    |       |     |     |

|              | C.4   |         | creation file                                                                 |    |       |     |     |

|              | C.5   |         | file                                                                          |    |       |     |     |

|              | C.6   |         | ile                                                                           |    |       |     |     |

|              | O.0   | THUIS I |                                                                               |    |       |     | 100 |

| Bi           | bliog | raphy   |                                                                               |    |       |     | 195 |

## List of Tables

| 1.1 | NCL dual-rail coding                                                    | 18 |

|-----|-------------------------------------------------------------------------|----|

| 1.2 | NCL logic gates.                                                        | 19 |

| 2.1 | Parameters and constant defined in the VHDL package used in the         |    |

|     | NML power model. M. Vacca et al. "Nanomagnetic Logic Microproces-       |    |

|     | sor: Hierarchical Power Model", IEEE Transaction on VLSI systems,       |    |

|     | 2012                                                                    | 34 |

| 3.1 | NCL Microprocessor performances. M. Vacca et al. "Asynchronous So-      |    |

|     | lutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging       |    |

|     | Technologies in Computing Systems, 2011                                 | 48 |

| 3.2 | Mixed logic microprocessor performances. M. Vacca et al. "Asynchronous  |    |

|     | Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerg-       |    |

|     | ing Technologies in Computing Systems, 2011                             | 53 |

| 3.3 | Microprocessor types comparison. M. Vacca et al. "Asynchronous So-      |    |

|     | lutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging       |    |

|     | Technologies in Computing Systems, 2011                                 | 58 |

| 6.1 | Results of Fan-out Tolerance Duplication for different thresholds [1] . | 96 |

| 6.2 | Results of ISCAS85 samples [1]                                          | 08 |

| 8.1 | Power comparison among the main NML implementations 1                   | 59 |

# List of Figures

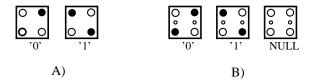

| 1.1 | Quantum dot Cellular Automata (QCA) cells. A) Four dots cells. B) Six dots cells                                                                                                                                                                                                                                                               | 1 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

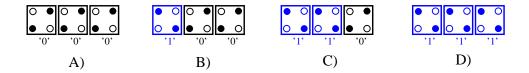

| 1.2 | Quantum dot Cellular Automata (QCA) wire. A) Starting condition. B) Input cell is forced to 1. C) Second cell switches to 1, due to the electrostatic interaction. D) Third cell switches to 1                                                                                                                                                 | 2 |

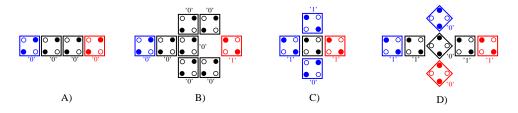

| 1.3 | Quantum dot Cellular Automata (QCA) basic blocks. A) Wire. B) Inverter. C) Majority gate. D) Crosswire                                                                                                                                                                                                                                         | 2 |

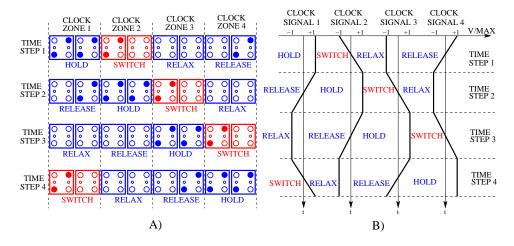

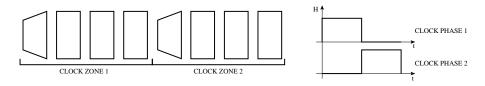

| 1.4 | Clock mechanism. A) Clock zones. B) Clock signals                                                                                                                                                                                                                                                                                              | 3 |

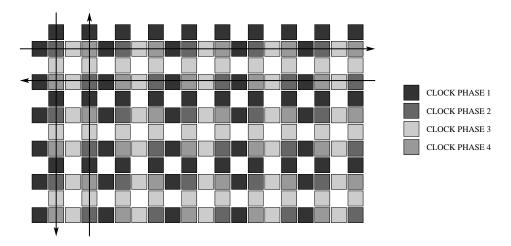

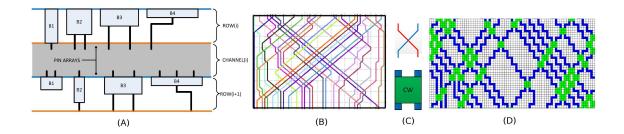

| 1.5 | Example of complex QCA clock zones layout. M. Graziano, M. Vacca et al. "Magnetic QCA Design: Modeling, Simulation and Circuits", Cellular Automata Innovative Modelling For Science And Engineering, Intechweb.org, 2011                                                                                                                      | 4 |

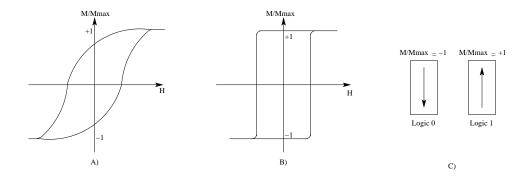

| 1.6 | A) Multidomain magnetic material hysteresis cycle. B) Single domain magnetic material hysteresis cycle. C) Magnetic Quantum dot Cellular Automata (MQCA) cells. M. Graziano, M. Vacca et al. "Magnetic QCA Design: Modeling, Simulation and Circuits", Cellular Automata Innovative Modelling For Science And Engineering, Intechweb.org, 2011 | 6 |

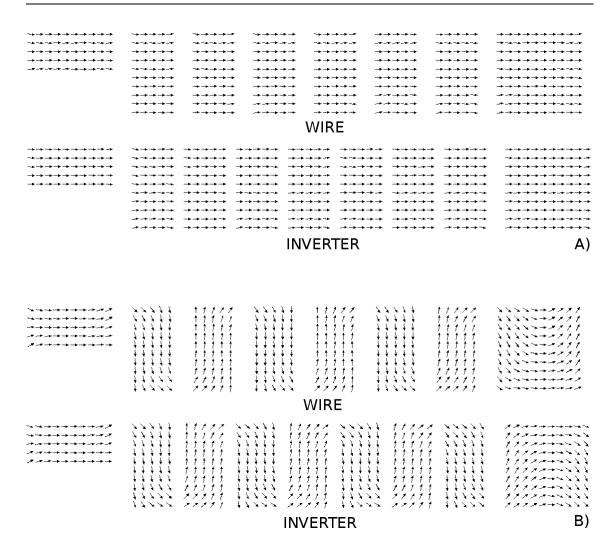

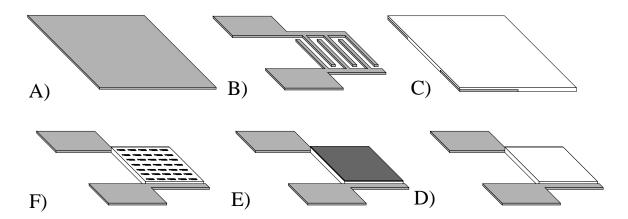

| 1.7 | NML logic gates. A) Horizontal Wire. B) Inverter. C) Vertical Wire. D) Majority Voter. E) AND. F) OR. G) Crosswire                                                                                                                                                                                                                             | 7 |

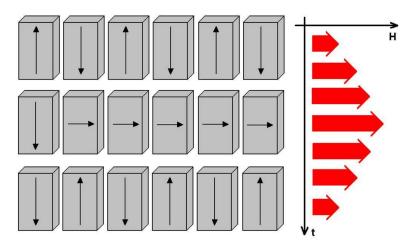

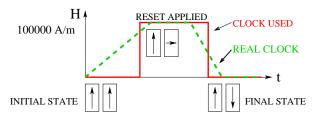

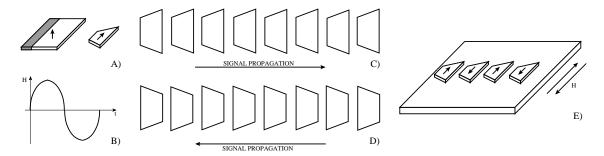

| 1.8 | NML clock system. Magnets are forced in an intermediate state with an external magnetic field. When the field is removed magnets realign themselves following the input magnet. M. Vacca et al. "Nanomagnetic Logic Microprocessor: Hierarchical Power Model", IEEE Transaction on VLSI systems, 2012                                          | 8 |

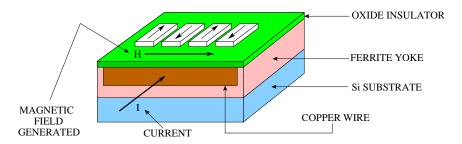

| 1.9 | Magnetic field generation for MQCA circuits. The magnetic field is generated by a current which flows through a wire placed under the magnets plane. M. Vacca et al. "Nanomagnetic Logic Microprocessor:                                                                                                                                       | • |

|     | Hierarchical Power Model", IEEE Transaction on VLSI systems, 2012                                                                                                                                                                                                                                                                              | 9 |

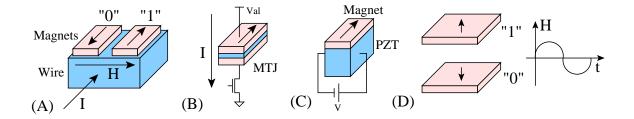

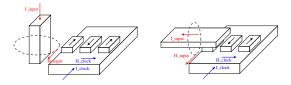

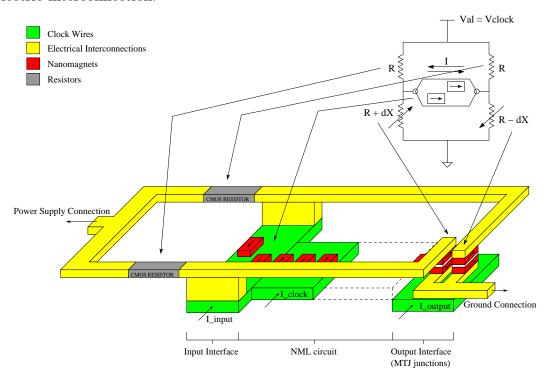

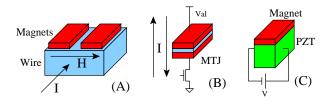

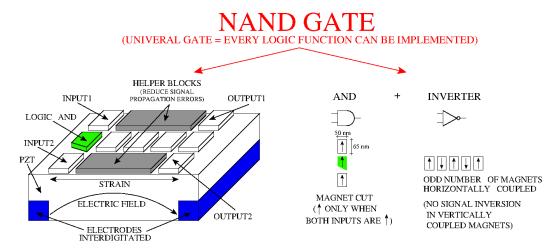

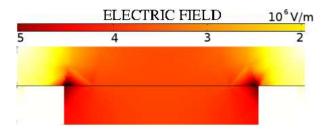

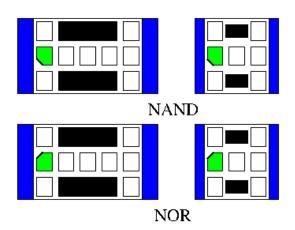

| 1.10 | NML logic subtypes. A) In-plane NML (iNML) with current generated magnetic field. B) Multilayered NML (M-NML) based on Mag- |

|------|-----------------------------------------------------------------------------------------------------------------------------|

|      | neto Tunnel Junctions (MTJ) as basic element. Clock is based on a                                                           |

|      | current flowing through the wire. C) Multiferroic NML. Magnets are                                                          |

|      | multilayered structures made with a layer of piezoelectric material                                                         |

|      | and a layer of ferromagnetic material. Clock should be theoretically                                                        |

|      | generated by an applied electric field. D) Out-of-plane NML (oNML).                                                         |

|      | , , , , , , , , , , , , , , , , , , , ,                                                                                     |

|      | Magnets are multilayered structures made by Cobalt and Platinum,                                                            |

| 1 11 | while clock is an external oscillating magnetic field                                                                       |

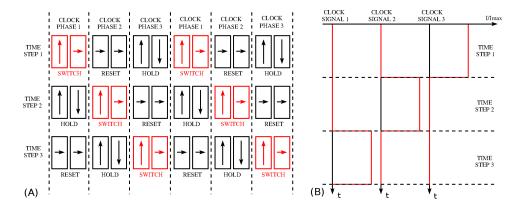

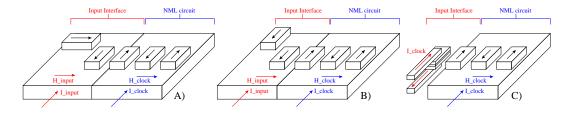

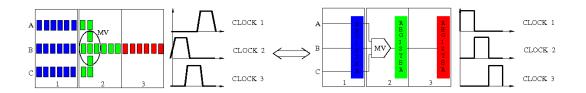

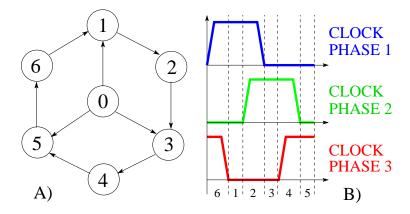

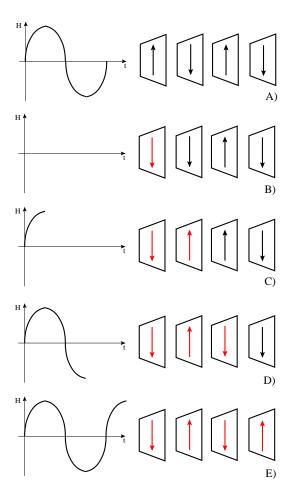

| 1.11 | (A) Left: logic organization of nanomagnets in time and space follow-                                                       |

|      | ing the clock signal sequence (Reset, Switch, and Hold). (B) Right:                                                         |

|      | clock signal on three phases delivered to three different zones in space                                                    |

|      | and repeated in time following the Reset, Switch, and Hold sequence.                                                        |

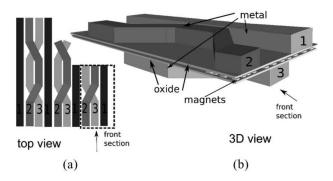

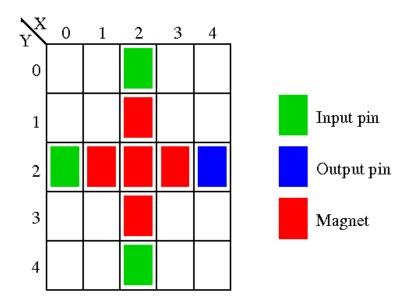

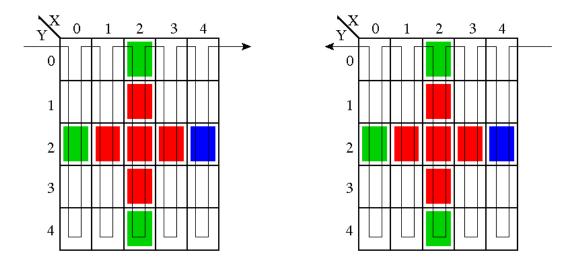

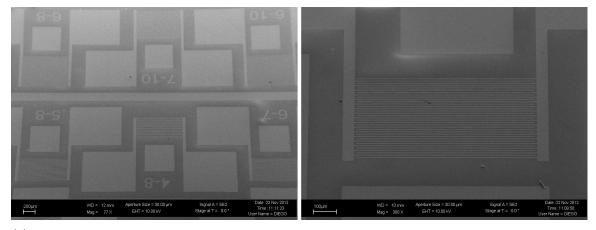

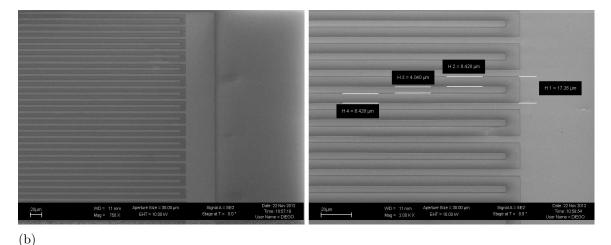

| 1.12 | Snake-clock. (A) Top view. (B) 3-D view. The 3-D view front sec-                                                            |

|      | tion corresponds to the 2-D detail evidenced by the dotted rectangle.                                                       |

|      | Phase 1 is delivered through a straight line on upper plane. Phases 2                                                       |

|      | and 3 are twisted, but are routed on different planes: phase 2 is on the                                                    |

|      | same plane of phase 1; phase 3 is below the lower plane. Nanomagnets                                                        |

|      | are visible in the section between the two planes. Magnets cannot be                                                        |

|      | placed where wires 2 and 3 are twisted. M. Graziano, M. Vacca et                                                            |

|      | al. "An NCL-HDL Snake-Clock-Based Magnetic QCA Architecture",                                                               |

|      | IEEE Transaction on Nanotechnology, 2011                                                                                    |

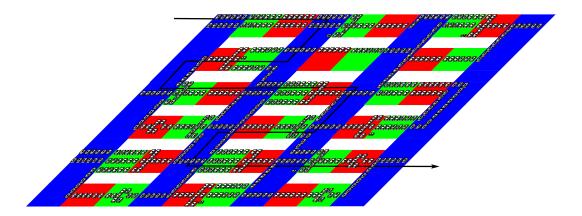

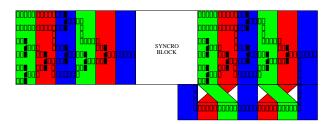

| 1.13 | An example of circuit based on the "snake-clock" scheme. Differ-                                                            |

|      | ent colors of rectangles refer to different clock zone. In white zones                                                      |

|      | no magnets are present because that is the region where two wires are                                                       |

|      | twisted, according to layout in Figure 1.12. M. Vacca et al. "Asynchronous                                                  |

|      | Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerg-                                                           |

|      | ing Technologies in Computing Systems, 2011                                                                                 |

| 1.14 | Reset field showing a realistic slope. (a) Non-overlapping phases. (b)                                                      |

|      | Overlapping phases, preferred for a correct information propagation.                                                        |

|      | M. Graziano, M. Vacca et al. "An NCL-HDL Snake-Clock-Based Mag-                                                             |

|      | netic QCA Architecture", IEEE Transaction on Nanotechnology, 2011 13                                                        |

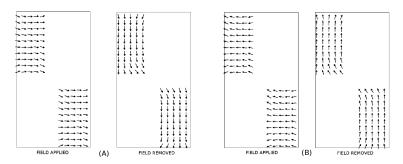

| 1.15 | Nanomagnet wire information propagation: three phases partially                                                             |

|      | over- lapped. (a) Reset on first zone. (b) Reset on first and second                                                        |

|      | zones. (c) Reset on second zone. (d) Reset on second and third zones.                                                       |

|      | (e) Reset on third zone. M. Graziano, M. Vacca et al. "An NCL-HDL                                                           |

|      | Snake-Clock-Based Magnetic QCA Architecture", IEEE Transaction                                                              |

|      | on Nanotechnology, 2011                                                                                                     |

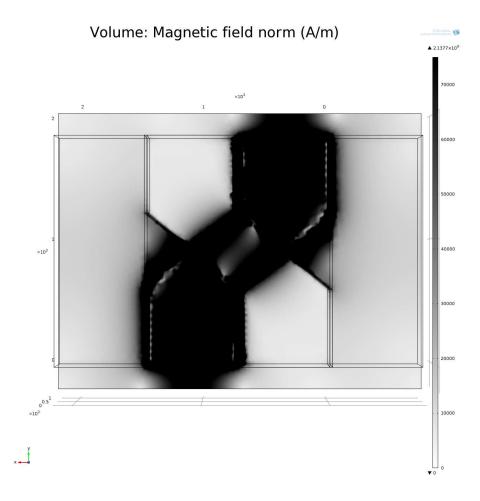

| 1.16 | Comsol simulation of the twisted clock wires for the Snake-clock                                                            |

|      | scheme. M. Vacca et al. "Nanomagnetic Logic Microprocessor: Hier-                                                           |

|      | archical Power Model", IEEE Transaction on VLSI systems, 2012 15                                                            |

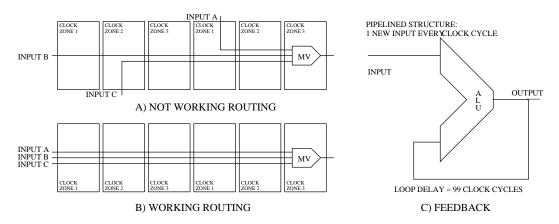

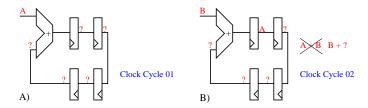

| 1.17 | B) represent the problem of signal synchronization at layout level.  A) Shows a case where the circuit will not work properly because the input wires pass through a different number of clock zones. B) Shows a working case with input signals correctly synchronized. C) Schematic representation of the problem of feedback signals. M. Vacca et al. "Asynchronous Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging Technologies in Computing Systems, 2011                                                                                     | 17 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

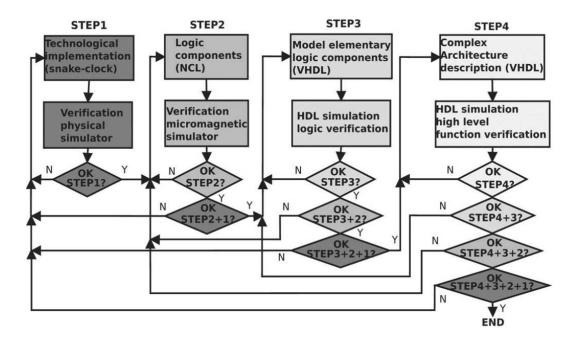

| 1.18 | NCL circuit example: full adder. Every signal is coded using two bits. Logic gates are TH23 (symbol 2) and TH34w2 (symbol 3) M. Graziano, M. Vacca et al. "Magnetic QCA Design: Modeling, Simulation and Circuits", Cellular Automata Innovative Modelling For Science And Engineering, Intechweb.org, 2011                                                                                                                                                                                                                                                            | 20 |

| 1.19 | Flow diagram of the proposed methodology organized in four steps: (1) technological implementation, (2) logic components definition, (3) HDL model of logic components, (4) architectural HDL description. Each step requires a validation through a proper simulator. Progress from one step to the next is subject to this validation and may require a feedback not only to decision on current step, but on previous ones as well. M. Graziano, M. Vacca et al. "An NCL-HDL Snake-Clock-Based Magnetic QCA Architecture", IEEE Transaction on Nanotechnology, 2011 | 21 |

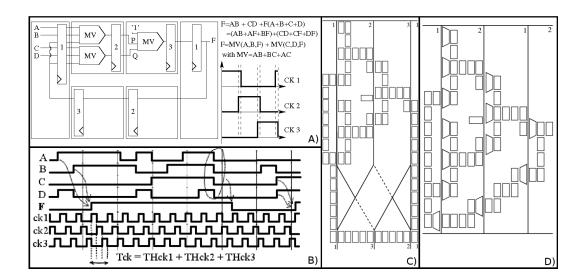

| 2.1  | A) THxor0 VHDL behavioral model. Logic functions of the gate and the majority voter (MV) are shown in the upper-right detail while the bottom-right detail shows the clock signals applied to each register. B) THxor0 simulation results. It is possible to observe the transition of the gate from F=0 to F=1 when the logic equation is satisfied. C) THxor0 3-phases NML implementation. D) THxor0 2-phases implementation. M. Vacca et al. "Nanomagnetic Logic Microprocessor: Hierarchical Power Model", IEEE Transaction on VLSI systems, 2012                  | 24 |

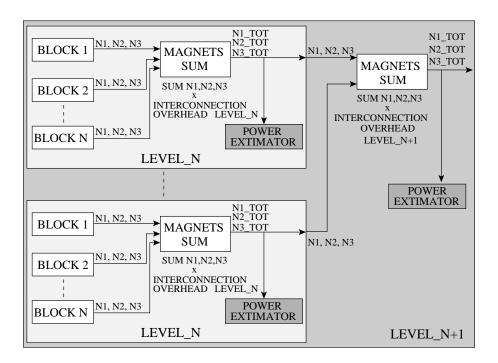

| 2.2  | Model for the estimation of nanomagnets number in a NML circuit and for the evaluation of power dissipation due to nanomagnets and clock wires. N1, N2, N3 represents the number of magnets (for each clock zone) of each lower level logic block. N1_TOT, N2_TOT, N3_TOT are instead the total number of magnets of the logic level considered. M. Vacca et al. "Nanomagnetic Logic Microprocessor: Hierarchical Power Model", IEEE Transaction on VLSI systems, 2012.                                                                                                | 26 |

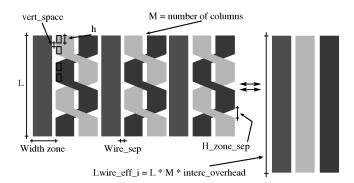

| 2.3  | Wire length calculation. Wires of same color are connected serially, so they can be approximated as one straight wire. A factor Wire_curves is used to takes into account wire angles overhead. M. Vacca et al. "Nanon Logic Microprocessor: Hierarchical Power Model", IEEE Transaction                             | nagnetic   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | on VLSI systems, 2012                                                                                                                                                                                                                                                                                                | 31         |

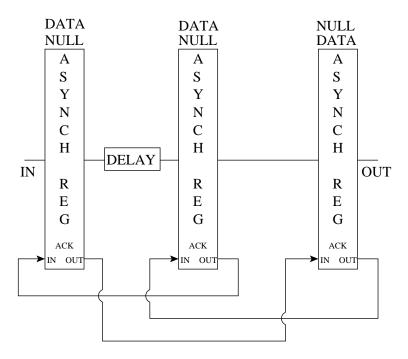

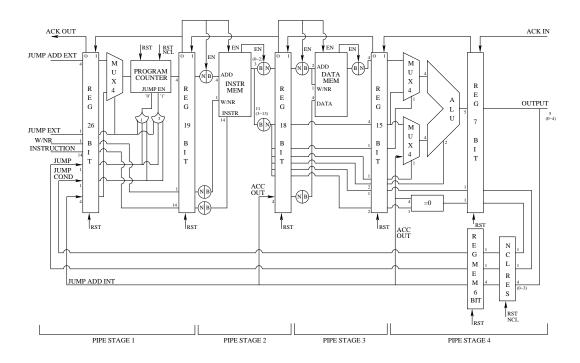

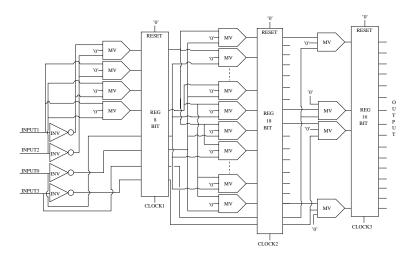

| 3.1  | NCL Microprocessor architecture                                                                                                                                                                                                                                                                                      | 36         |

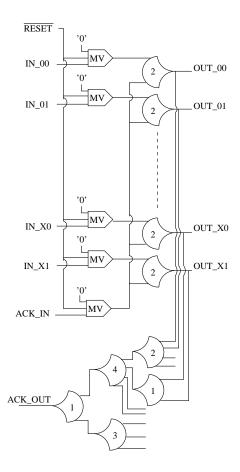

| 3.2  | Generic asynchronous register architecture                                                                                                                                                                                                                                                                           | 38         |

| 3.3  | NCL feedbacks structure                                                                                                                                                                                                                                                                                              | 39         |

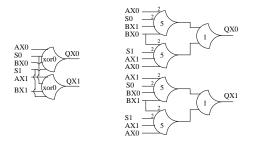

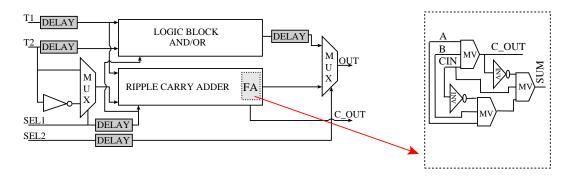

| 3.4  | NCL magnetic QCA arithmetic/logic unit architecture. M. Graziano, M. Vacca et al. "Magnetic QCA Design: Modeling, Simulation and Circuits", Cellular Automata Innovative Modelling For Science And Engineering, Intechweb.org, 2011                                                                                  | 40         |

| 3.5  | NCL mux architecture. M. Graziano, M. Vacca et al. "Magnetic QCA Design: Modeling, Simulation and Circuits", Cellular Automata Innovative Modelling For Science And Engineering, Intechweb.org, 2011                                                                                                                 | 40         |

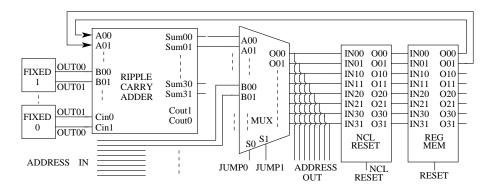

| 3.6  | NCL magnetic QCA program counter architecture                                                                                                                                                                                                                                                                        | 41         |

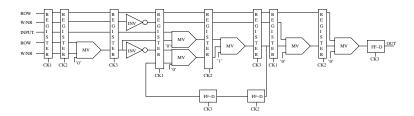

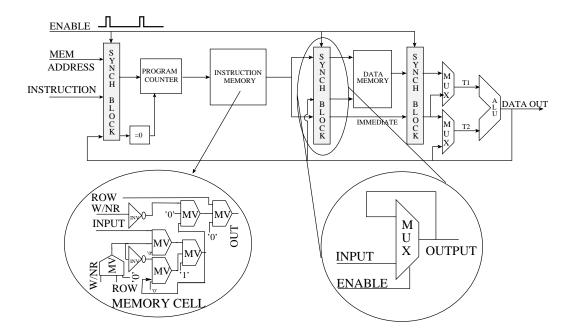

| 3.7  | NCL parallel memory architecture                                                                                                                                                                                                                                                                                     | 42         |

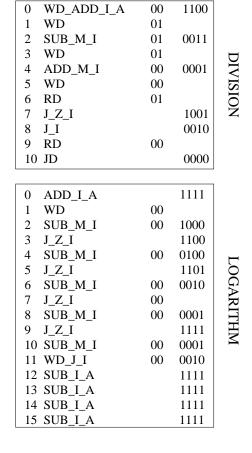

| 3.8  | Microprocessor instruction set                                                                                                                                                                                                                                                                                       | 43         |

| 3.9  | Division and logarithm program code                                                                                                                                                                                                                                                                                  | 44         |

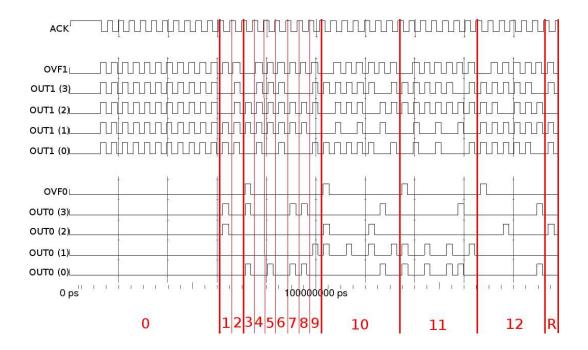

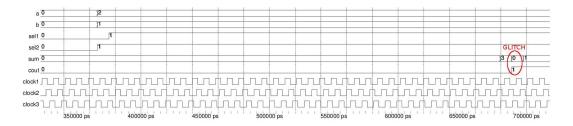

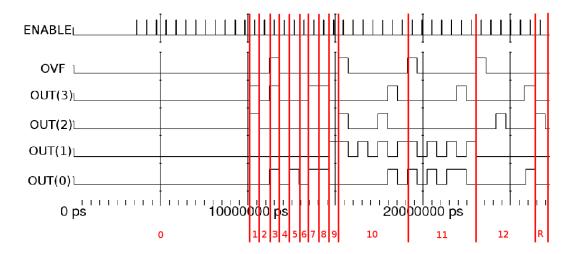

| 3.10 | Simulation results of the division algorithm executed on the pure NCL microprocessor. In the mixed case waveforms are identical, but the time of the execution is reduced. M. Vacca et al. "Asynchronous Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging Technologies in Computing Systems, 2011 | 45         |

| 3.11 | Logarithm algorithm simulation results (starts from step 2 for space reason as step 1 concerns just initialization)                                                                                                                                                                                                  | 46         |

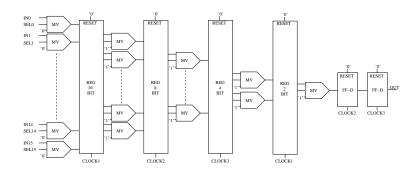

| 3.12 | Mixed logic microprocessor architecture. Memories are designed using boolean logic, interfaces are therefore required                                                                                                                                                                                                | 49         |

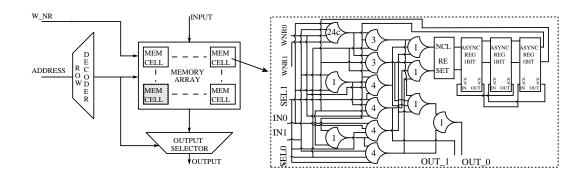

| 3.13 | Boolean memory cell                                                                                                                                                                                                                                                                                                  | 49         |

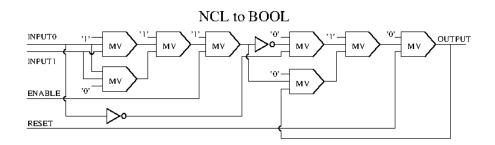

| 3.14 | Boolean-NCL interface. M. Vacca et al. "Asynchronous Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging Technolo-                                                                                                                                                                                   | <b>~</b> 0 |

| 0.45 | gies in Computing Systems, 2011                                                                                                                                                                                                                                                                                      | 50         |

| 3.15 | NCL-Boolean interface. M. Vacca et al. "Asynchronous Solutions for<br>Nanomagnetic Logic Circuits", ACM Journal on Emerging Technolo-                                                                                                                                                                                |            |

| 0.10 | gies in Computing Systems, 2011                                                                                                                                                                                                                                                                                      | 50         |

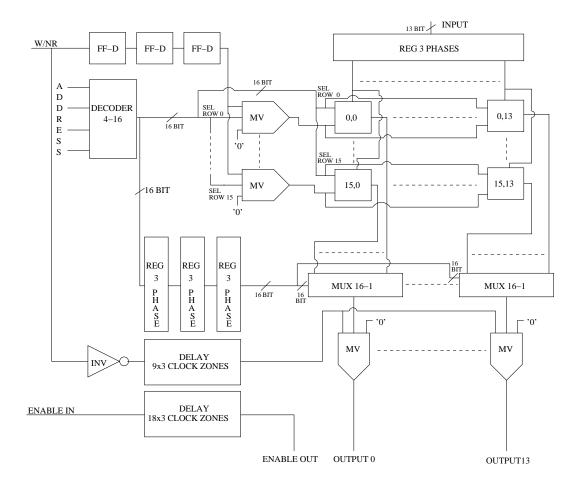

|      | Boolean memory architecture                                                                                                                                                                                                                                                                                          | 51         |

|      | A 4 to 16 decoder made using boolean logic                                                                                                                                                                                                                                                                           | 52         |

| 3.18 | A 16 to 1 multiplexer used to select the correct memory output                                                                                                                                                                                                                                                       | 52         |

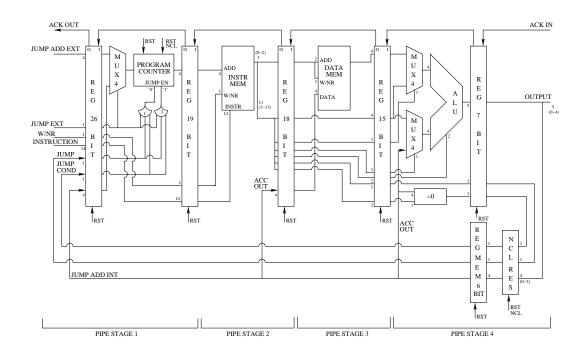

| Boolean microprocessor architecture. Asynchronous registers are substituted with synchronization blocks (bottom right inset) that realize an asynchronous-like structure. In bottom left detail the boolean memory cell is shown, used in the mixed Boolean-NCL and in the fully Boolean versions of the microprocessor. M. Vacca et al. "Asynchronous Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging Technologies in Computing Systems, 2011                                                                                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

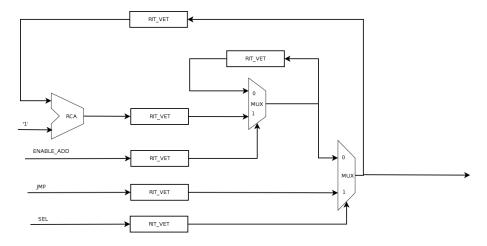

| Boolean program counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Boolean alu. M. Graziano, M. Vacca et al. "Asynchrony in Quantum-<br>Dot Cellular Automata Nanocomputation: Elixir or Poison?", IEEE<br>Design & Test of Computers, 2011                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example of glitch generated during alu operations due to bad synchronization. M. Graziano, M. Vacca et al. "Asynchrony in Quantum-Dot Cellular Automata Nanocomputation: Elixir or Poison?", IEEE Design & Test of Computers, 2011                                                                                                                                                                                                                                                                                                                           | 56                                                                                                                                                                                                                                                                                                                                                                                                                       |

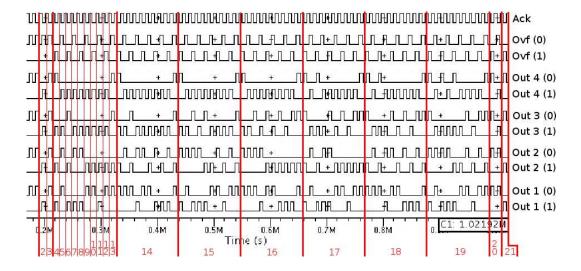

| Simulation results of the division algorithm executed on the pure Boolean microprocessor. M. Vacca et al. "Asynchronous Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging Technologies in Computing Systems, 2011                                                                                                                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                       |

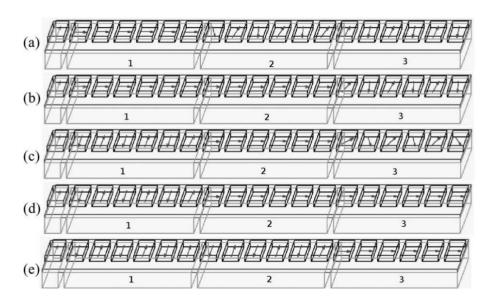

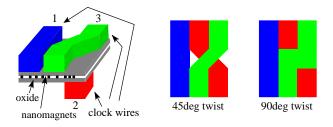

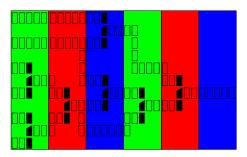

| Snake clock. Wire twisting can be at 45 degrees or 90 degrees, but this can be difficult to fabricate                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Improved circuit layout. Combinational and sequential parts of the circuit are separated. Wire twisting is limited only to feedback signals.                                                                                                                                                                                                                                                                                                                                                                                                                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                       |

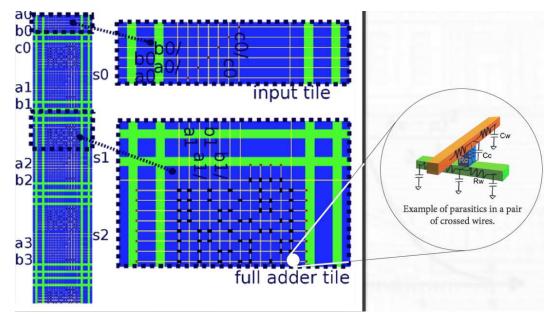

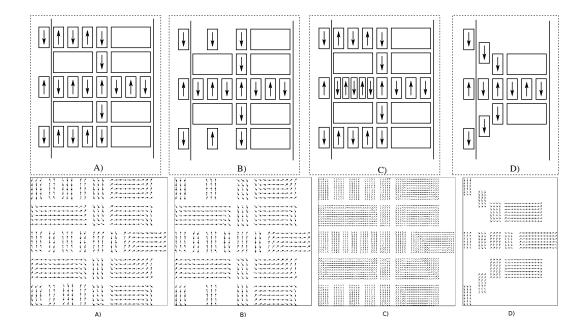

| NML Combinational circuits layout. This layout is technologically feasible and particularly adapted to dataflow logic                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                       |

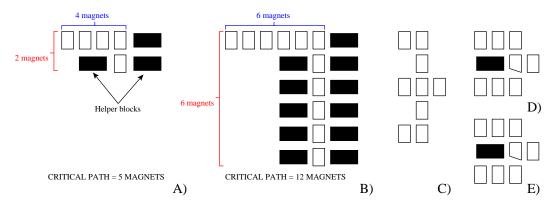

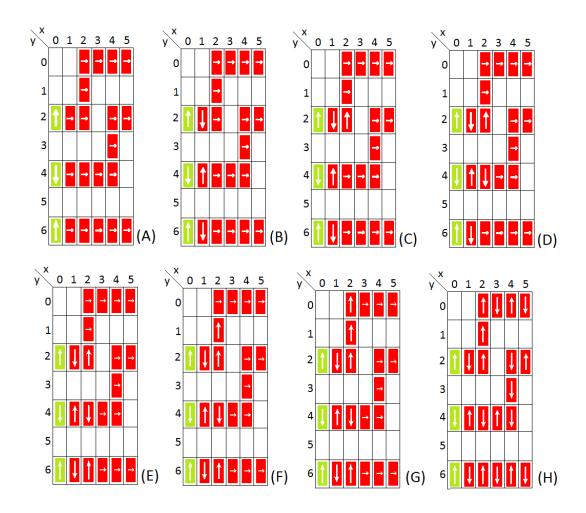

| Constraints related to the clock zones layout. Helper blocks are used to help signal propagation in vertical direction. A) More constraining case: Critical path of 5 magnets. B) Relaxing of some constraints: Critical path of 12 magnets. C) Modified majority voter. D) AND                                                                                                                                                                                                                                                                              | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                      |

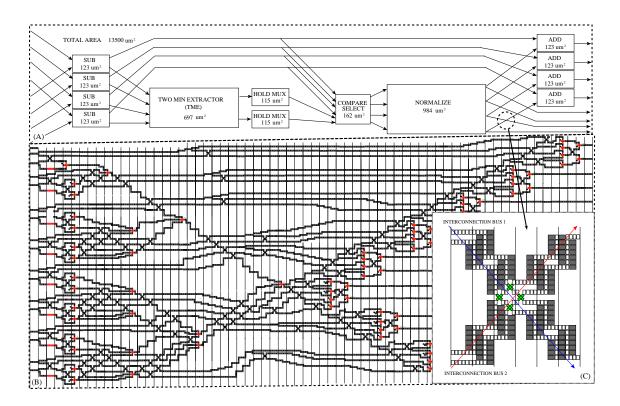

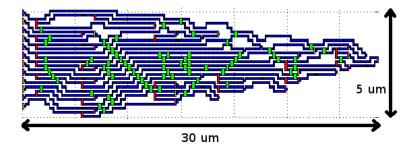

| A LDPC decoder for wireless applications. The layout is based on straight wires for the generation of the clock field. This layout was theoretically and experimentally demonstrated for Magnetic QCA [2]. B) CMP block layout. C) A detail on vertical interconnection wires. Due to the layout limitations vertical signals follow a "stairs-like" propagation. Stabilizer blocks are used to improve the reliability in vertical signal propagation [3]. M.Awais et al. "Quantum dot Cellular Automata Check Node Implementation for LDPC Decoders", IEEE | 61                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | stituted with synchronization blocks (bottom right inset) that realize an asynchronous-like structure. In bottom left detail the boolean memory cell is shown, used in the mixed Boolean-NCL and in the fully Boolean versions of the microprocessor. M. Vacca et al. "Asynchronous Solutions for Nanomagnetic Logic Circuits", ACM Journal on Emerging Technologies in Computing Systems, 2011  Boolean program counter |

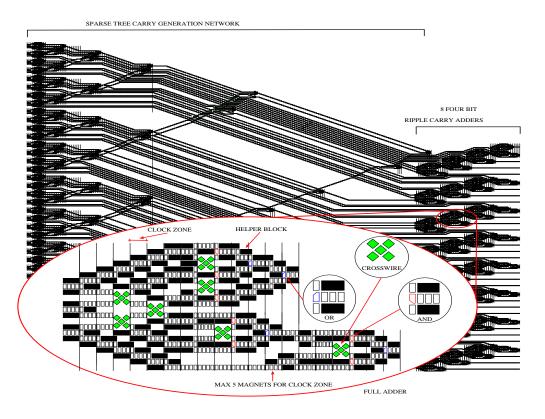

| 4.6  | NML 32 bits pentium 4 adder. A sparse tree carry generation network is coupled with eight 4 bit ripple carry adder. M. Vacca et al. "ToPoliNano: A synthesis and simulation tool for NML circuits", International Conference on Nanotechnology, 2012                                                                                                                          | 64 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

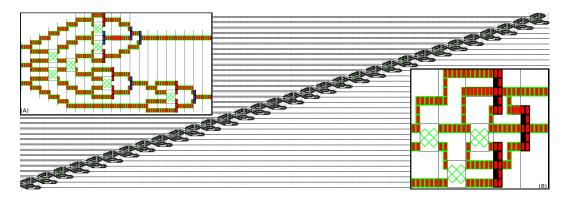

| 4.7  | 32 bits ripple carry adder. Two different types of fulladders are shown, one which uses AND/OR gates and a clock zone with a width of 4 nanomagnets, a second one which uses Majority Voters [4] and a clock zone with a width of 6 magnets. M. Vacca et al. "ToPoliNano: A synthesis and simulation tool for NML circuits", International Conference on Nanotechnology, 2012 | 65 |

| 4.8  | Comparison between the P4 adder and the ripple carry adder. The ripple carry adder area is only slightly higher than the P4 adder. With this clock zones layout the simplest architectures are favored                                                                                                                                                                        | 66 |

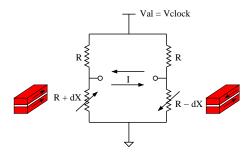

| 4.9  | Current flowing through wires can be used to generate a magnetic field used to influence an input magnet                                                                                                                                                                                                                                                                      | 68 |

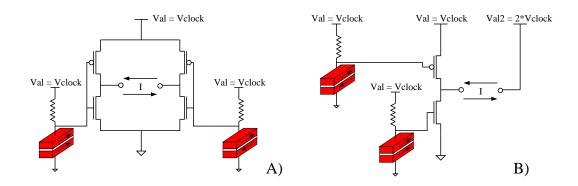

| 4.10 | A) Classic input interface. B) Improved input interface. C) MTJ input interface                                                                                                                                                                                                                                                                                               | 68 |

| 4.11 | A) Low level simulation of input '0'. B) Low level simulation of input '1'                                                                                                                                                                                                                                                                                                    | 69 |

| 4.12 | Simplest example of electric interconnection, a resistive H Bridge is used to read the value of MTJ and to drive another magnet                                                                                                                                                                                                                                               | 70 |

| 4.13 | Example of complete electric interconnection system used for a feedback signal                                                                                                                                                                                                                                                                                                | 71 |

| 4.14 | Alternative electric interconnection circuits. A) Full bridge. B) Half bridge                                                                                                                                                                                                                                                                                                 | 72 |

| 4.15 | Magnetic Wires. A) Nanomagnet wires. B) Domain wall wires                                                                                                                                                                                                                                                                                                                     | 74 |

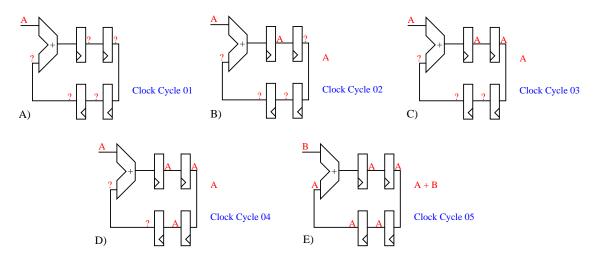

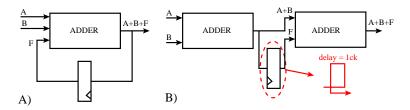

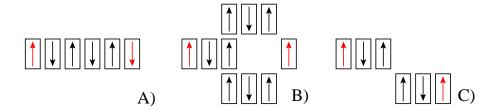

| 5.1  | Effect of loops in intrinsic pipelined technologies. A) Sending a data and B) immediately after a clock cycle sending a new data, lead to the wrong result, because the previous result had not time to propagate back                                                                                                                                                        | 76 |

| 5.2  | Effect of loops in intrinsic pipelined technologies. A) Sending a data and B) C) D) keeping the input constant for N clock cycles, E) allows to obtain the correct result, because the data had time to propagate back.                                                                                                                                                       | 76 |

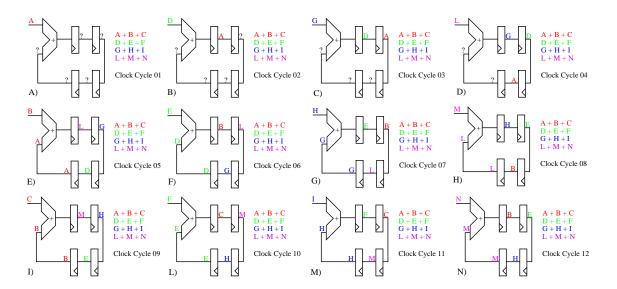

| 5.3  | Data interleaving. N operations are executed in parallel. Every clock cycle a data of a different operation is sent, achieving perfect synchronization and maximum throughput.                                                                                                                                                                                                | 78 |

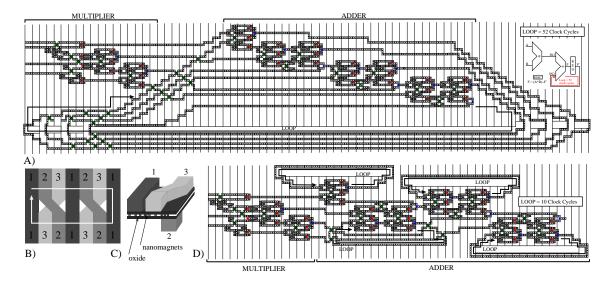

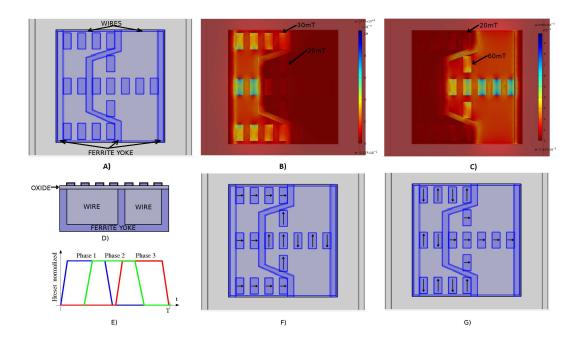

| 5.4  | MAC detailed layout. The layout uses clock zones made by parallel wires [2], while for feedback it is adopted the solution proposed in [5]. |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|

|      | Circuits are made using AND/OR gates [6] that best suit this kind of                                                                        |

|      | clock zones layout. A) Direct mapping of the circuit schematics. The                                                                        |

|      | longest loop has a delay of 52 clock cycles. B) Top view of the clock                                                                       |

|      | zones layout to allow feedback signals propagation. C) 3D view of                                                                           |

|      | the clock wires where the current must flow to generate the magnetic                                                                        |

|      | field [5] [2]. D) Circuit layout with loops optimization. The delay of                                                                      |

|      | the loop is reduced to 10 clock cycles                                                                                                      |

| 5.5  | Nested Loops. To synchronize signals their length must be exactly                                                                           |

|      | the same                                                                                                                                    |

| 5.6  | Complex signals synchronization. If a loop is present inside the cir-                                                                       |

|      | cuit, every additional register, which is not present in all the input                                                                      |

|      | paths, must have an equivalent delay equal to the delay of the loop 80                                                                      |

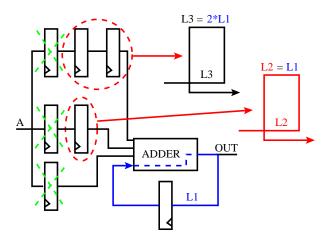

| 5.7  | Loop unrolling to completely remove loop inside the circuit 8                                                                               |

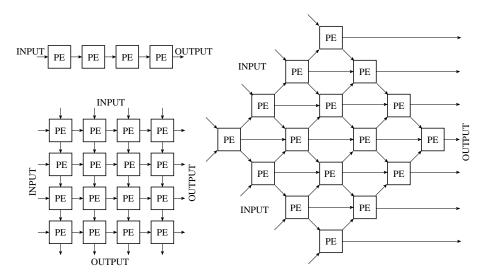

| 5.8  | Different possibilities for systolic arrays                                                                                                 |

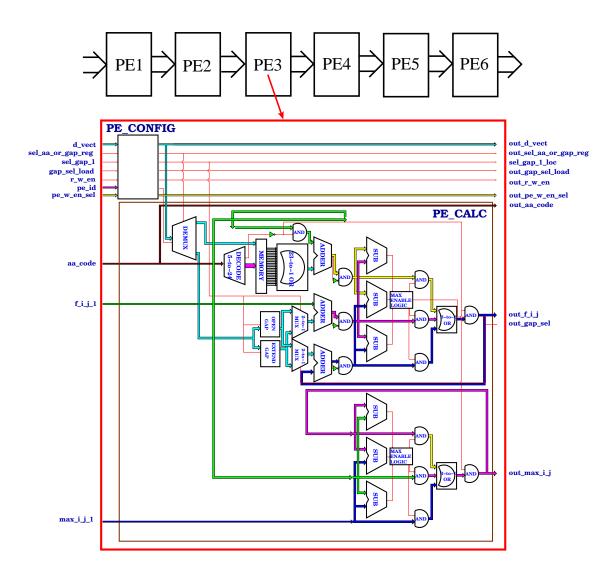

| 5.9  | Processing Element of the Smith-Waterman implemented in NML                                                                                 |

|      | with a systolic array architecture [7]                                                                                                      |

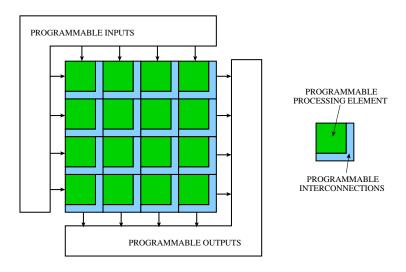

| 5.10 | Programmable systolic array structure                                                                                                       |

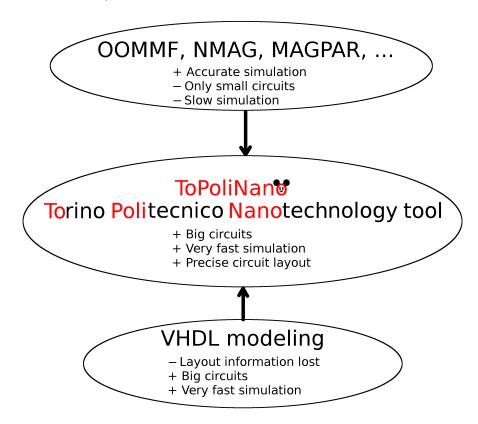

| 6.1  | Vhdl modeling                                                                                                                               |

| 6.2  | NML simulation                                                                                                                              |

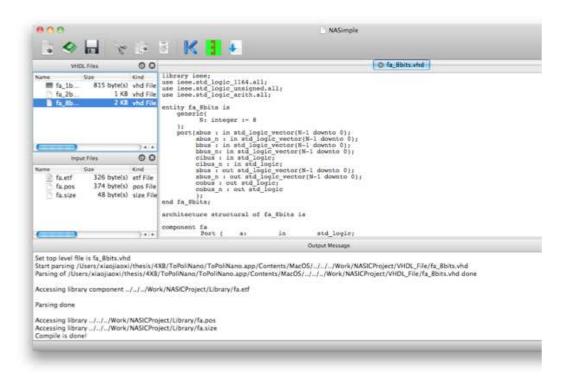

| 6.3  | ToPoliNano GUI                                                                                                                              |

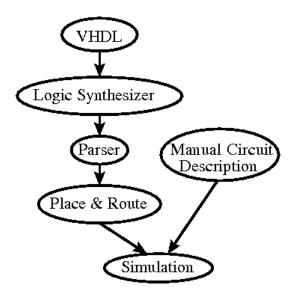

| 6.4  | ToPoliNano design flow. M. Vacca et al. "ToPoliNano: A synthesis                                                                            |

|      | and simulation tool for NML circuits", International Conference on                                                                          |

|      | Nanotechnology, 2012                                                                                                                        |

| 6.5  | Silicon Nanowire NanoPLA full adder. S. Frache et al. "ToPoliNano:                                                                          |

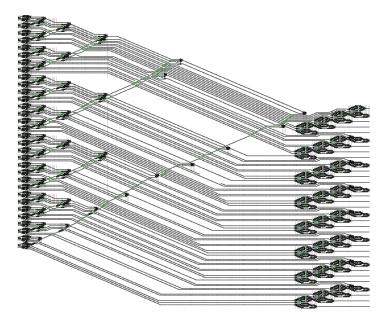

|      | Nanoarchitectures Design Made Real", Nanoarch, 2012 90                                                                                      |

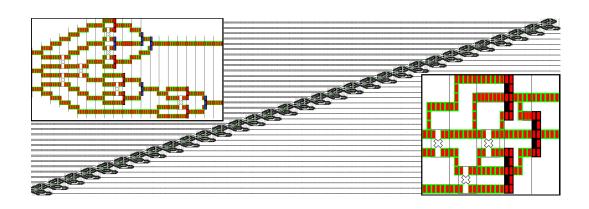

| 6.6  | NML layout example: A 32 bit ripple carry adder. In the left detail                                                                         |

|      | a full adder made using AND/OR gates is shown, while in the right                                                                           |

|      | detail there is a full adder made with majority voters. M. Vacca et                                                                         |

|      | al. "ToPoliNano: A synthesis and simulation tool for NML circuits",                                                                         |

|      | International Conference on Nanotechnology, 2012                                                                                            |

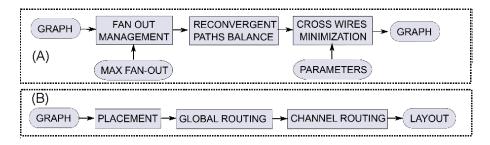

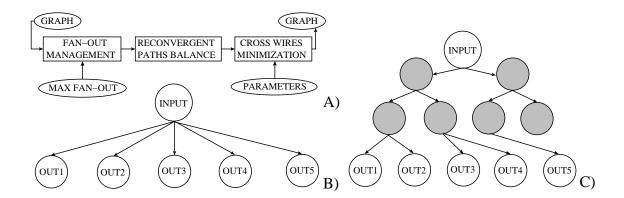

| 6.7  | A) Graph elaboration flow diagram. C) Physical Mapping flow chart. 92                                                                       |

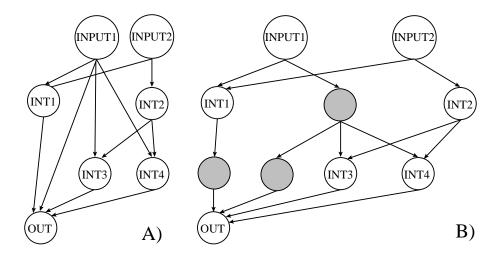

| 6.8  | A) Graph before Fan-out Limitation is applied. B) Graph after Fan-                                                                          |

| c o  | out Limitation                                                                                                                              |

| 6.9  | Reconvergent Paths Balance. A) Graph before leveling. B) Graph                                                                              |

| C 10 | after wire block insertion and wire block sharing                                                                                           |

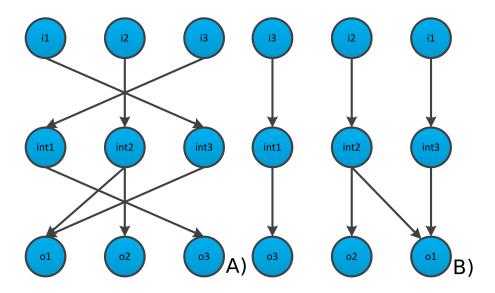

| 6.10 | Graph before (A) and after (B) Barycenter application [1] 90                                                                                |

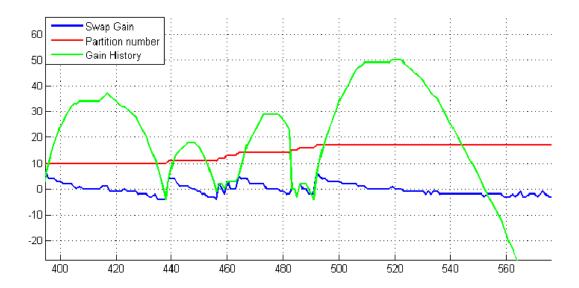

|      | KL algorithm applied to NML circuits                                                                                                        |

| 0.12 | Gain history for the entire set of partitions [1]                                                                                           |

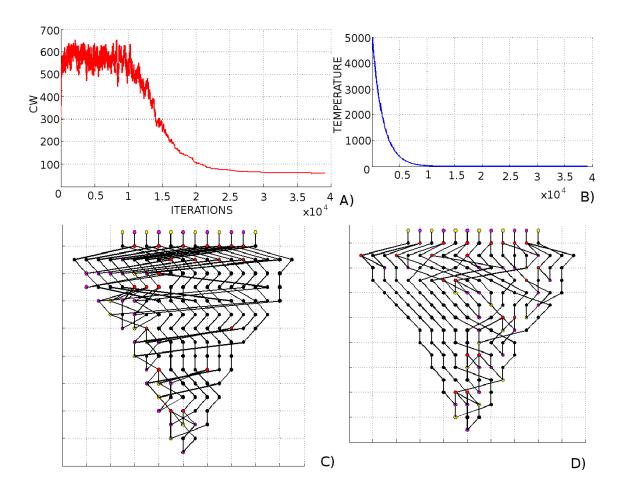

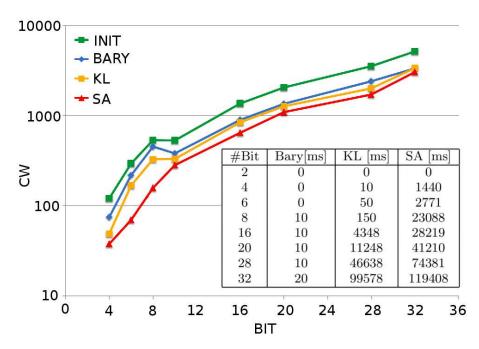

| 6.13 | A) B) Simulated Annealing applied to a 6 bit RCA. C) D) Graph processing through SA, PT=29.8 s [1]                                                                                                                 | 102 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.14 | Wire cross reduction comparison of different algorithms. A multi bit adder is used as benchmark. Inset with table: Execution time for wire cross minimization algorithms applied to a variable bit number          |     |

|      | Ripple Carry Adder [1]                                                                                                                                                                                             | 104 |

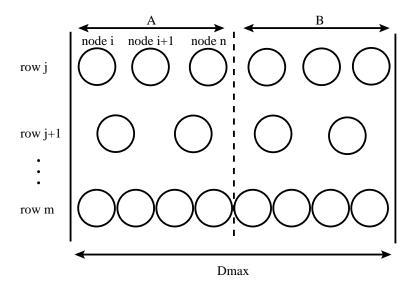

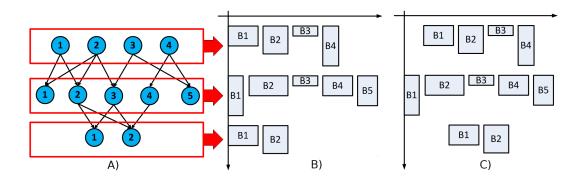

| 6.15 | A-B) Seed row placement for maximum width evaluation. C) Barycen-                                                                                                                                                  |     |

|      | tered placement [1]                                                                                                                                                                                                | 105 |

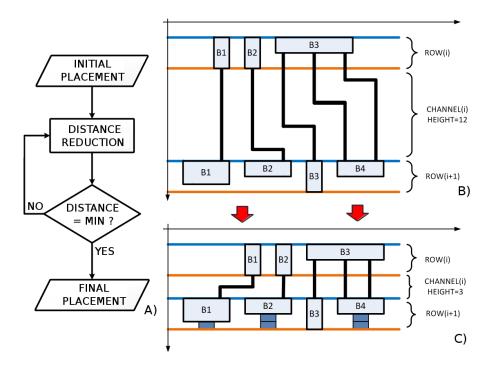

| 6.16 | A) Global Routing flow diagram. B) Unoptimized placement. C) Optimized placement. [1]                                                                                                                              | 107 |

| 6.17 | A) Pins for channel definition. B) Mini Swap model for channel routing. C) Crosswire mapping. D) Physical mapping of interconnections.                                                                             | 4.0 |

|      |                                                                                                                                                                                                                    |     |

|      | Layout of a 6 bit Ripple Carry Adder [1]                                                                                                                                                                           | 108 |

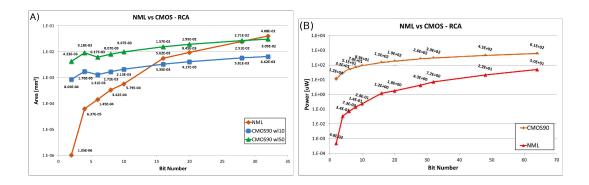

| 6.19 | A) Comparison for RCA between NML and CMOS 90 nm in terms of area (two wireload models). B) Comparison for RCA between NML and CMOS 90 nm in terms of power dissipation. [1]                                       | 109 |

| 6.20 | Topolinano switch model. M. Vacca et al. "ToPoliNano: A synthesis and simulation tool for NML circuits", International Conference on                                                                               | 110 |

| C 01 | Nanotechnology, 2012                                                                                                                                                                                               | 110 |

| 6.21 | A) Finite state machine used for the state calculation B) Three phase overlapped clock and the 6 states that characterize it                                                                                       | 111 |

| 6.22 | ToPoliNano simulation matrix                                                                                                                                                                                       | 112 |

| 6.23 | Details on matrix exploration                                                                                                                                                                                      | 114 |

| 6.24 | Magnet state calculation. Only the 8 neighbor cells are considered.<br>M. Vacca et al. "ToPoliNano: A synthesis and simulation tool for NML circuits", International Conference on Nanotechnology, 2012            | 115 |

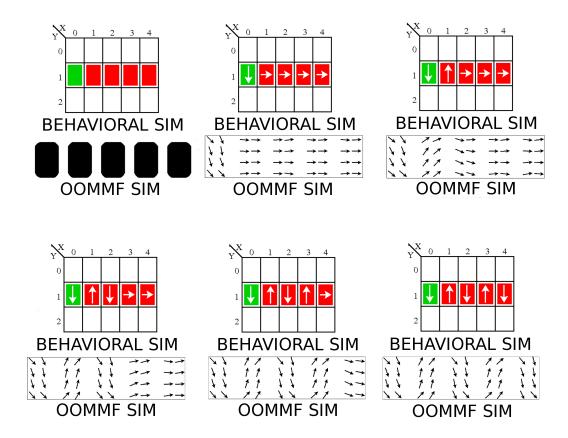

| 6.25 | Step by step simulation of an array of three wires. M. Vacca et al. "ToPoliNano: A synthesis and simulation tool for NML circuits",                                                                                |     |

|      | International Conference on Nanotechnology, 2012                                                                                                                                                                   |     |

| 6.26 | Step by step simulation of the majority voter                                                                                                                                                                      | 117 |

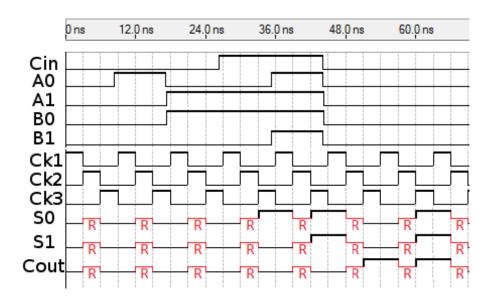

| 6.27 | Example of a simulation waveforms of a 2 bit ripple carry adder, obtained using the full adders shown in Figure 6.6 right detail. <i>M. Vacca et al.</i> "ToPoliNano: A synthesis and simulation tool for NML cir- |     |

|      | cuits", International Conference on Nanotechnology, 2012                                                                                                                                                           | 118 |

| 7.1  | Real clock signal waveform and ideal clock signal waveforms. M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic                                                                            |     |

|      | Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                | 121 |

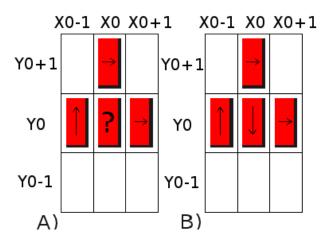

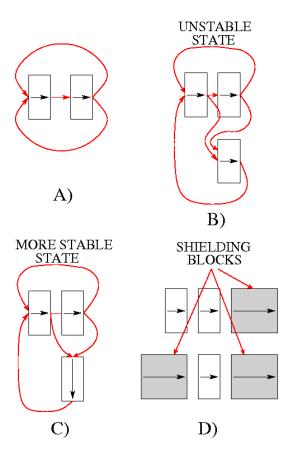

| 7.2 | Reset problem. A) Perfectly aligned magnets. Magnets maintain the (unstable) RESET state due to the perfect alignment of the neighbors magnets. The red lines (magnetic flux) are perfectly symmetric. B) Misaligned magnets. Magnets are not in the minimum energy state. C) The misaligned element turn down due to the influence of the neighbor magnets in the RESET state. Magnetic flux lines are shorter therefore in this situation the total energy of the system is lower. D) Shielding block used to keep the misaligned elements in the RESET state, until the neighbor magnets go in a stable state. M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012              | 124 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

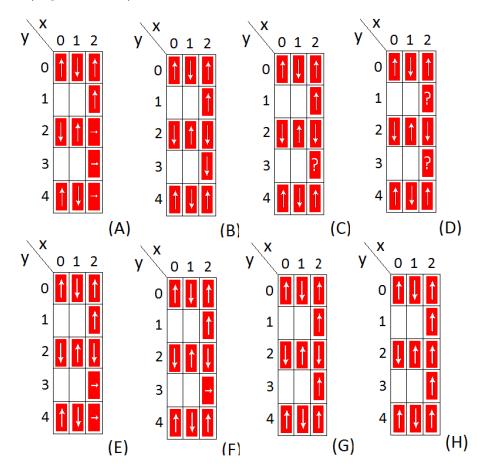

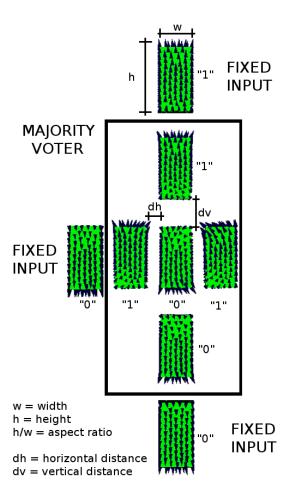

| 7.3 | Majority Voter configuration. Fixed magnets are used as inputs for the Majority Voter. Horizontal and vertical distances and aspect ratio are changed to verify the majority voter operating area. $M.Vacca$ et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                                                                                                                                                                                                                                                                            | 126 |

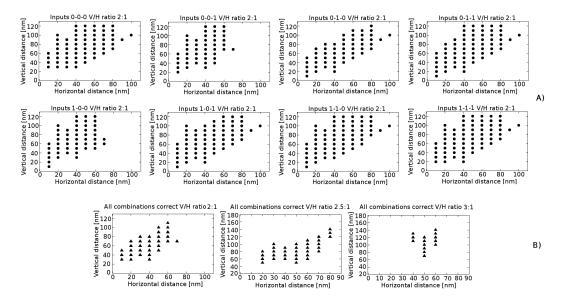

| 7.4 | Majority voter working area with the variation of the horizontal and vertical distance. A) Working area for every inputs configuration. B) Complete working area with magnets with an aspect ratio of 2, 2.5 and 3. M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                                                                                                                                                                                                                                                            | 127 |

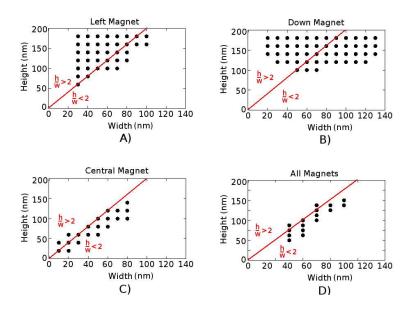

| 7.5 | Majority voter working area considering process variations. Red line represent the aspect ratio 2. A) Sizes variation of the left magnet. B) Sizes variation of the down magnet. C) Sizes variation of the central magnet. D) Sizes variation of all the magnets together. M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                                                                                                                                                                                                     | 130 |

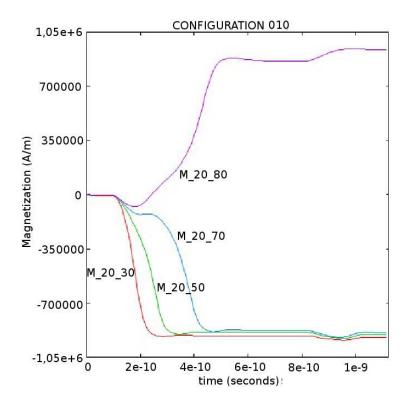

| 7.6 | Timing variation of the central magnet magnetization in a few cases of vertical and horizontal distance for the input configuration of 010. The different waveforms identify different values of horizontal and vertical distance. The first number represents the horizontal distance while the second number identifies the vertical distance. Different waveforms are presented: In the first three the gate works properly, and in the last one the behavior of the gate is wrong as magnetization is expected to go to a negative value (which represents logic 0) but goes to a positive value (which represents logic 1). M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits" IEEE Transaction on Nanotechnology 2012 | 139 |

| 7.7  | Timing variation with three values of vertical distance for the each input configuration, considering an horizontal distance of 20 nm. <i>M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits"</i> , <i>IEEE Transaction on Nanotechnology</i> , 2012                                                                                                                                                                                                                                                                                                                                                                | . 133 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

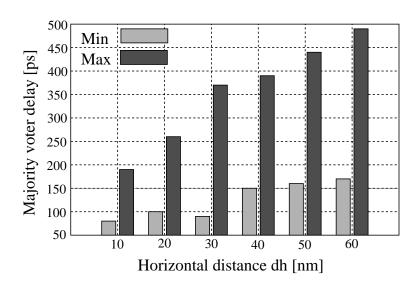

| 7.8  | Timing variation of the gate. For each value of horizontal distance the minimum and maximum values of delay, measured among all the input configurations and all the vertical distance, are reported. M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                                                                                                                                                                 | . 133 |

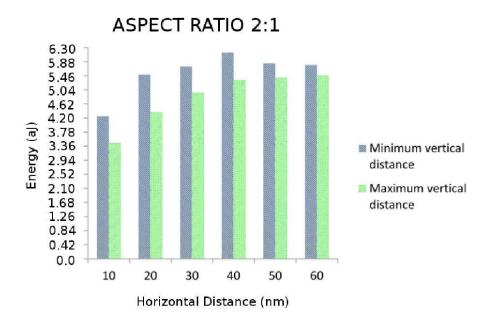

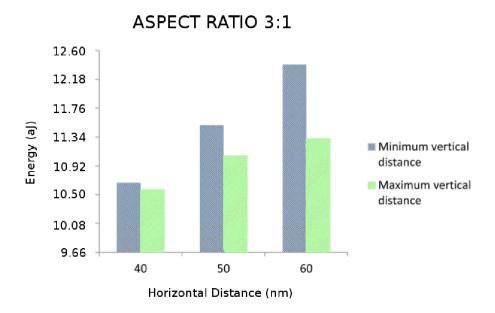

| 7.9  | Power analysis with all the possible inputs configurations, for all the vertical and horizontal distance values with an aspect ratio of 2. M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                                                                                                                                                                                                                            | . 135 |

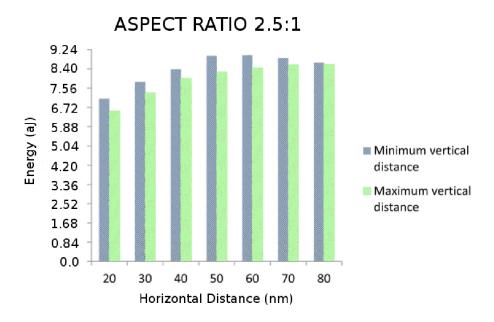

| 7.10 | Power analysis with all the possible inputs configurations, for all the vertical and horizontal distance values with an aspect ratio of 2.5.<br>M. Vacca et al. "Majority Voter Full Characterization for Nanomagnet Logic Circuits", IEEE Transaction on Nanotechnology, 2012                                                                                                                                                                                                                                                                                                                                                                       | . 136 |