# POLITECNICO DI TORINO

#### SCUOLA DI DOTTORATO

Dottorato in Ingegneria Elettronica e Comunicazioni – XXIV ciclo

### Tesi di Dottorato

# Digital Signal Processing on FPGA for Short-Range Optical Communications Systems over Plastic Optical Fiber

Experimental investigations to increase the POF channel capacity

Julio César Ramírez Molina

**Tutore**Prof. Roberto Gaudino

Coordinatore del corso di dottorato Prof. Ivo Montrosset

Marzo 2012

$\begin{array}{c} A\ Malui,\\ a\ H\'{e}ctor,\ a\ Mami\ y\ al\ Viejo \end{array}$

# Summary

Nowadays bandwidth requirements are increasing vertiginously. As new ways and concepts of how to share information emerge, new ways of how to access the web enter the market. Computers and mobile devices are only the beginning, the spectrum of web products and services such as IPTV, VoIP, on-line gaming, etc has been augmented by the possibility to share, store data, interact and work on the Cloud.

The rush for bandwidth has led researchers from all over the world to enquire themselves on how to achieve higher data rates, and it is thanks to their efforts, that both long-haul and short-range communications systems have experienced a huge development during the last few years. However, as the demand for higher information throughput increases traditional short-range solutions reach their limits. As a result, optical solutions are now migrating from long-haul to short-range communication systems. As part of this trend, plastic optical fiber (POF) systems have arisen as promising candidates for applications where traditional glass optical fibers (GOF) are unsuitable.

POF systems feature a series of characteristics that make them very suitable for the market requirements. More in detail, these systems are low cost, robust, easy to handle and to install, flexible and yet tolerant to bendings. Nonetheless, these features come at the expense of a considerable higher bandwidth limitation when compared to GOF systems.

This thesis is aimed to the investigate the use of digital signal processing (DSP) algorithms to overcome the bandwidth limitation in short-range optical communications system based on POF. In particular, this dissertation presents the design and development of DSP algorithms on field programmable gate arrays (FPGAs) with the ultimate purpose of implementing a fully engineered 1Gbit/s Ethernet Media Converter capable of establishing data links over 50+ meters of PMMA-SI POF using an RC-LED as transmitter.

# Contents

| Sı | ımm  | ary                                                                  | ]          |

|----|------|----------------------------------------------------------------------|------------|

| 1  | Inti | coduction                                                            | 1          |

|    | 1.1  | Fiber-to-the-Home                                                    | 2          |

|    | 1.2  | Fiber-in-the-Home                                                    | 5          |

|    | 1.3  | Intensive Broadband Networking for Optical Interconnect Applications | 5          |

|    | 1.4  | The EU POF-PLUS Project                                              | 7          |

|    | 1.5  | The scope of this Thesis                                             |            |

| 2  | PO   | F Short-Range Communication System                                   | 12         |

|    | 2.1  | PMMA-SI POF                                                          | 12         |

|    | 2.2  | Optoelectronic Transmitter                                           | 14         |

|    | 2.3  | Optoelectronic Receiver                                              | 16         |

|    | 2.4  | Investigation of Modulation Formats and Equalizing Algorithms        | 17         |

|    | 2.5  | Summary                                                              | 24         |

| 3  | Me   | dia Converter Prototype: 1Gb/s over 50+ m                            | <b>2</b> 5 |

|    | 3.1  | Design Specifications                                                | 25         |

|    | 3.2  | Implementation Methodology                                           | 27         |

|    | 3.3  | Physical Coding Sublayer PCS                                         | 28         |

|    | 3.4  | Physical Medium Attachment PMA                                       | 29         |

|    |      | 3.4.1 Decision Feedback Equalization                                 | 32         |

|    |      | 3.4.2 DSP Implementation of an Adaptive and Blind Decision Feed-     |            |

|    |      | back Equalizer                                                       | 38         |

|    | 3.5  | Summary                                                              | 59         |

| 4  | Me   | 1                                                                    | <b>6</b> 0 |

|    | 4.1  | Experimental Set Up                                                  | 60         |

|    | 4.2  | Optical Power Margin, BER and PER measurements                       |            |

|    | 4.3  | PCS Validation                                                       | 63         |

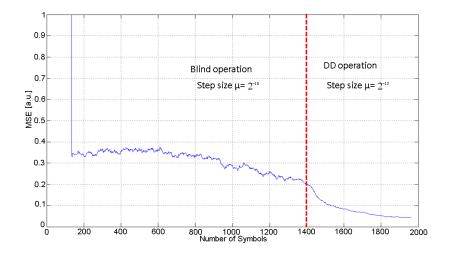

|    | 4.4  | Convergence time of the DLMS Algorithm                               | 64         |

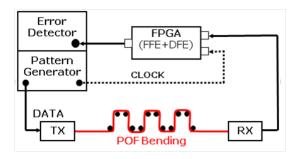

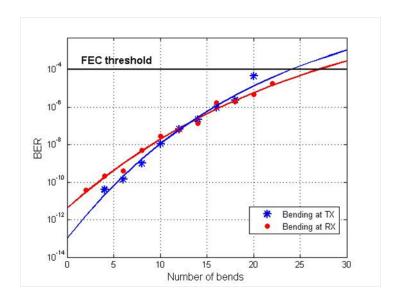

|    | 4.5   | Media Converter Tolerance to Fiber Bendings             | 65 |

|----|-------|---------------------------------------------------------|----|

|    | 4.6   | FPGA Logic and Area Utilization                         | 66 |

|    | 4.7   | Summary                                                 | 67 |

| 5  | Clo   | ck Recovery System                                      | 68 |

|    | 5.1   | Clock Synchronizers                                     | 68 |

|    |       | 5.1.1 Feedforward Synchronizer                          | 69 |

|    | 5.2   | Feedback Synchronizer                                   |    |

|    | 5.3   | Hybrid Implementation of an Error Tracking Synchronizer |    |

|    |       | 5.3.1 Mueller and Muller TED                            |    |

|    |       | 5.3.2 Loop Filter                                       |    |

|    |       | 5.3.3 $\Delta - \Sigma$ Modulator                       |    |

|    | 5.4   | Summary                                                 |    |

| 6  | Med   | dia Converter: DFE+CR Experimental Results              | 81 |

|    | 6.1   | Firecomms 650nm Receiver                                | 81 |

|    | 6.2   | Testing the Clock Recovery System                       |    |

|    | 6.3   | 1Gbit/s Full Duplex Media Converter                     |    |

| 7  | Cor   | aclusions and Recommendations                           | 87 |

| Bi | bliog | graphy                                                  | 94 |

# List of Figures

| 1.1<br>1.2   | Economies with the highest penetration of FTTH/Building+LAN [2]                    | 2               |

|--------------|------------------------------------------------------------------------------------|-----------------|

| 1.2          | Interest in futuristic web services of current FTTH users over 55 years of age [3] | 3               |

| 1.3          | Interest in futuristic web services of current FTTH users over 40 years            |                 |

|              | of age [3]                                                                         | 4               |

| 1.4          | Future Broadband In-Building Networks [6]                                          | 6               |

| 1.5          | Attenuation Spectrum for different fibers                                          | 8               |

| 1.6          | OSI/ETHERNET Layers implemented by the 1Gbit/s Media Converter                     | 9               |

| 1.7          | Envisioned Full Duplex Gigabit Ethernet Media Converter                            | 10              |

| 2.1          | SI PMMA POF (taken from [11])                                                      | 13              |

| 2.2          | Attenuation Spectrum of SI PMMA POF (taken from [11])                              | 13              |

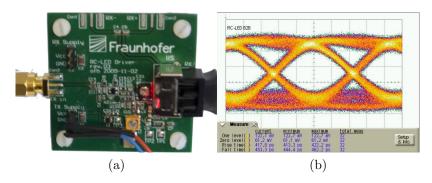

| 2.3          | (a) Firecomms 650nm RC-LED (b) Eye Diagram @1.25GHz                                | 15              |

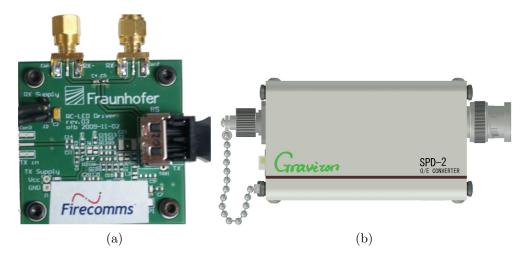

| 2.4          | 650nm (a) Firecomms Receiver (b) Graviton SPD-2                                    | 16              |

| 2.5          | POF Transmission Channel                                                           | 18              |

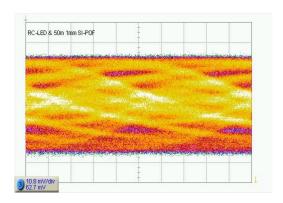

| 2.6          | 2-PAM Eye Diagram after 50 m of PMMA-SI POF                                        | 19              |

| 2.7          | Frequency Response of the POF System                                               | 19              |

| 2.8          | Impulse Response of the POF System                                                 | 20              |

| 2.9          | DFE Architecture                                                                   | 20              |

| 2.10         | Received signal for (a) 2-PAM transmission over 50 m (b) 4-PAM                     |                 |

|              | transmission over 50 m (taken from [13])                                           | 21              |

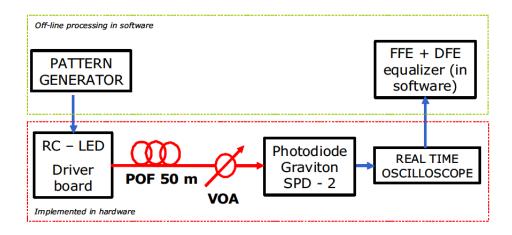

| 2.11         | Experimental Set up for off line processing                                        | 22              |

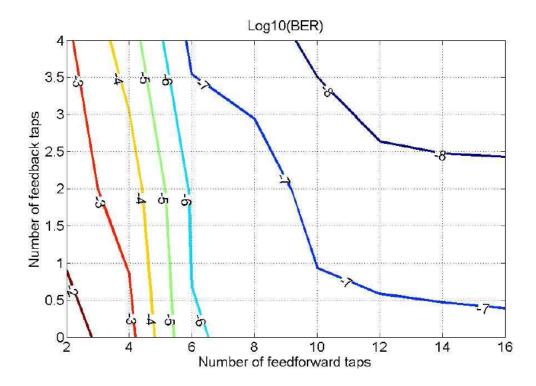

| 2.12         | BER as a function of the number of taps of the FF and FB stages of the DFE         | 23              |

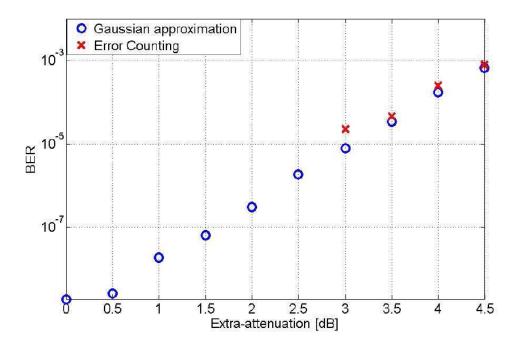

| 2.13         | Measured BER vs extra-attenuation at the receiver                                  | $\frac{23}{24}$ |

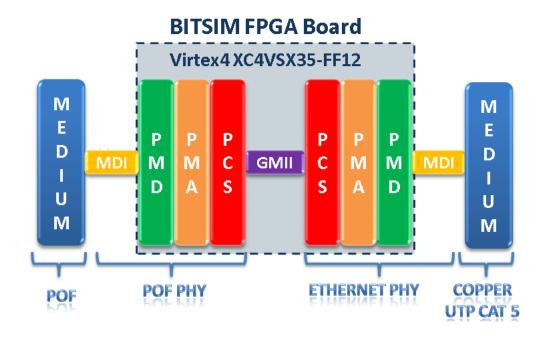

| 3.1          | Ethernet Layer Scheme of the Media Converter                                       | 26              |

| 3.2          | Implementation Methodology Diagram                                                 | 28              |

| 3.3          | Ethernet Layers                                                                    | 29              |

| 3.4          | PCS transmitter                                                                    | 29              |

| 3.5          | PCS receiver                                                                       | 30              |

| 3.6          | General Diagram of the PMA                                                         | 31              |

| $\mathbf{o}$ | - COLICION 12100=10011 OF 0110 1 101/1 + + + + + + + + + + + + + + + + + +         |                 |

| 3.7  | General Diagram of the POF Channel                                         | 1  |

|------|----------------------------------------------------------------------------|----|

| 3.8  | Linear FIR Filter                                                          | 3  |

| 3.9  | Block Diagram of DFE                                                       | 5  |

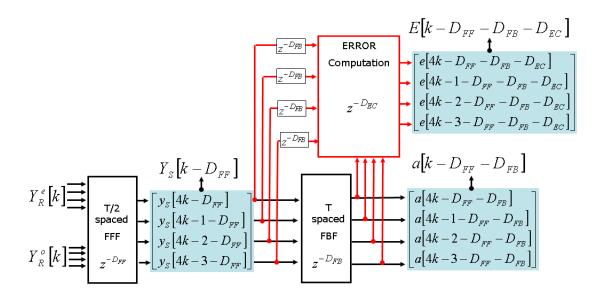

| 3.10 | PMA Top Level Implementation Diagram                                       | 8  |

| 3.11 | Samples Arrangement at the ADC output                                      | 9  |

| 3.12 | FSE First Level Implementation Diagram                                     | 0  |

|      | FSE Fourth Level Implementation Diagram 4                                  | 2  |

| 3.14 | FSE Third Level Implementation Diagram 4                                   | .3 |

|      | FSE Second Level Implementation Diagram 4                                  | 4  |

|      | FSE Implementation                                                         | 5  |

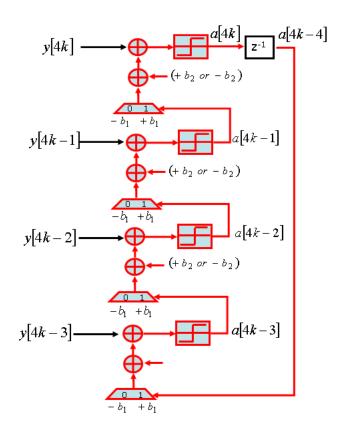

| 3.17 | Feedback Conventional Serial Architecture                                  | 6  |

| 3.18 | Multiplier MUX based implementation 4                                      | 7  |

| 3.19 | Feedback Conventional Serial Architecture                                  | 8  |

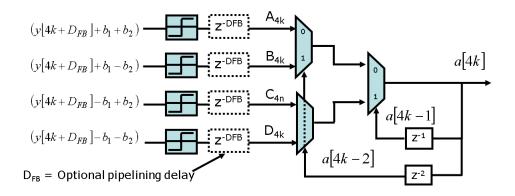

| 3.20 | Reformulated DFE                                                           | 9  |

| 3.21 | 4-stage look ahead pipelining of a 4-to-1 multiplexer loop 5               | 2  |

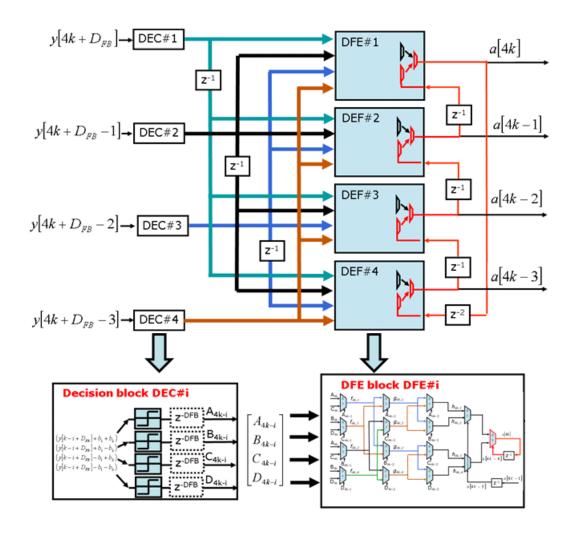

| 3.22 | 4-Parallel DFE Architecture                                                | 3  |

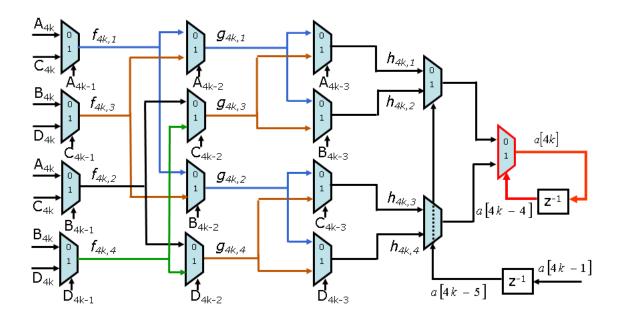

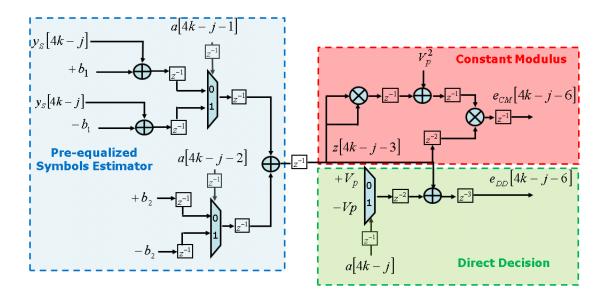

| 3.23 | DFE Block Diagram                                                          | 4  |

| 3.24 | $j^{th}$ parallel stage of the Error Estimation Block                      | 5  |

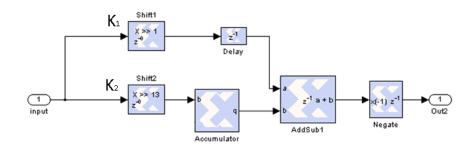

| 3.25 | Implementation diagram of the DLMS Tap Estimation (I) 5                    | 7  |

| 3.26 | Implementation diagram of the DLMS Tap Estimation (II) 5                   | 8  |

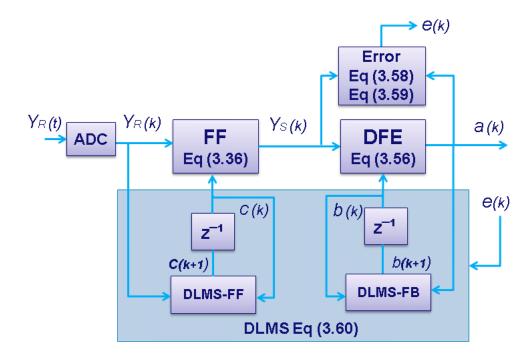

| 3.27 | Summarized Block Diagram of the Adaptive and Blind DFE $\ .\ .\ .\ .\ .$ 5 | 9  |

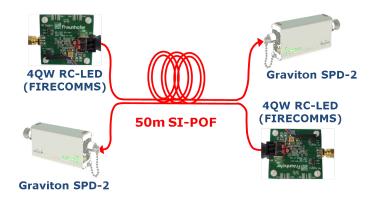

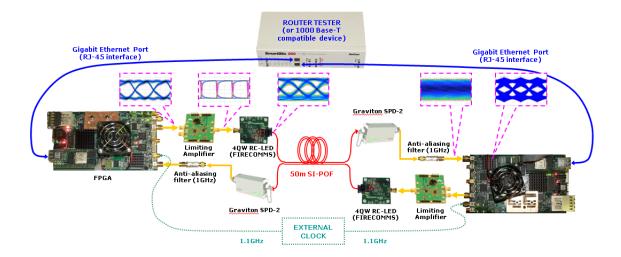

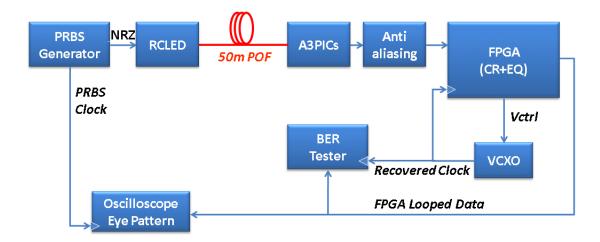

| 4.1  | Experimental Set Up for evaluating the 1Gbit/s Media Converter 6           | 1  |

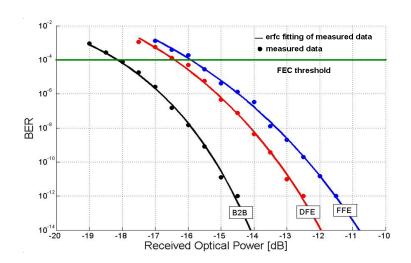

| 4.2  | BER curves for FF and DFE after 50m of PMMA-SI POF 6                       | 2  |

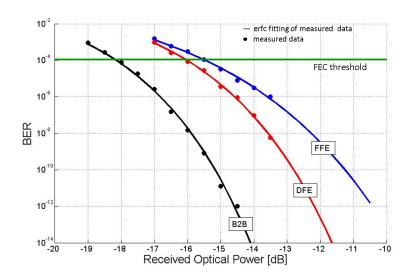

| 4.3  | BER curves for FF and DFE after 75m of PMMA-SI POF 6                       | 2  |

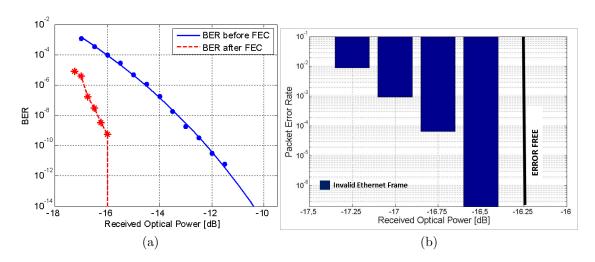

| 4.4  | (a) BER and (b) PER vs Received Optical Power 6                            | 3  |

| 4.5  | Experimental measurement of the MSE 6                                      | 4  |

| 4.6  | Experimental Set Up for evaluating the system tolerance to Fiber           |    |

|      | Bendings                                                                   | 5  |

| 4.7  | BER versus Number of Fiber Bendings 6                                      | 6  |

| 5.1  | Feedforward Synchronizer Architecture 6                                    | 9  |

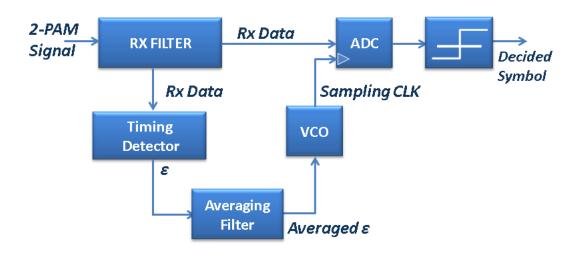

| 5.2  | Feedback Synchronizer Architecture                                         |    |

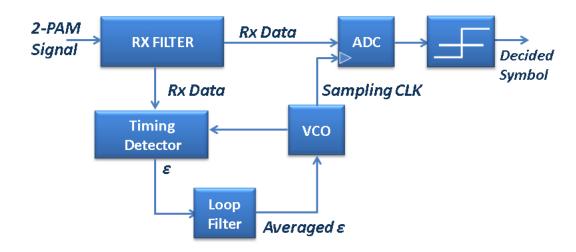

| 5.3  | Digital Feedback Synchronizer Architecture                                 | 1  |

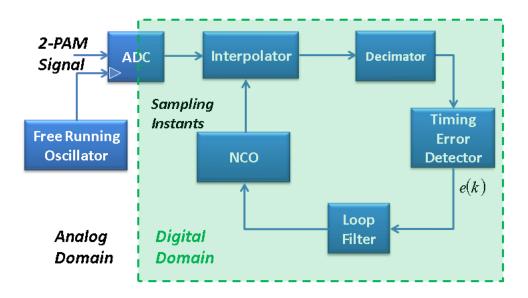

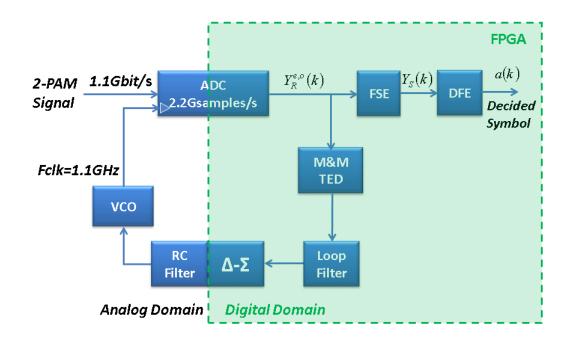

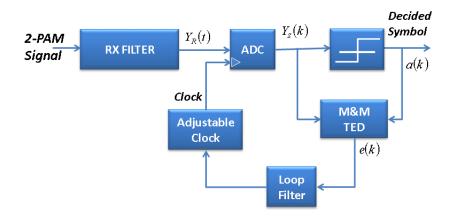

| 5.4  | Hybrid Clock Recovery Architecture                                         | 2  |

| 5.5  |                                                                            | '3 |

| 5.6  |                                                                            | 3  |

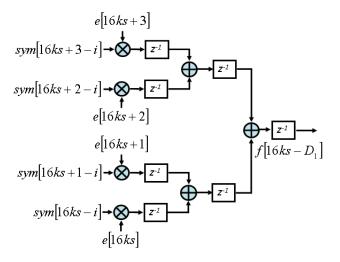

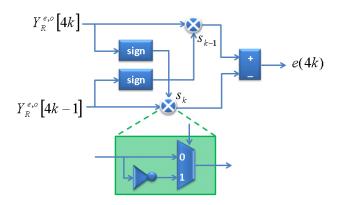

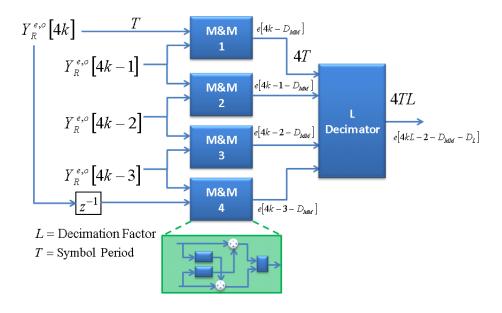

| 5.7  | M&M Parallel Implementation                                                |    |

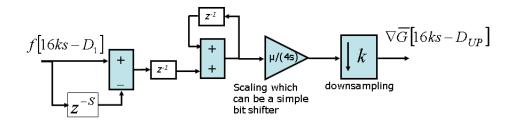

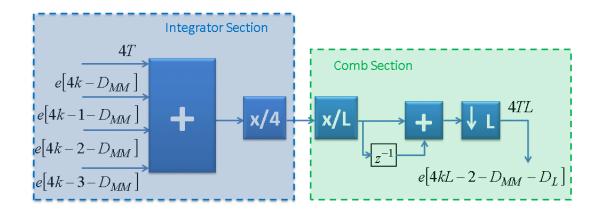

| 5.8  | Decimator Parallel Implementation                                          |    |

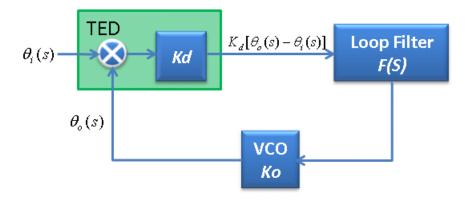

| 5.9  | PLL Diagram                                                                |    |

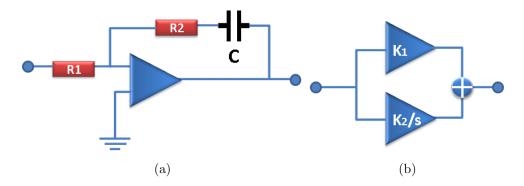

| 5.10 | Loop Filter Implementation as (a) an Active Filter (b) equivalent      |    |

|------|------------------------------------------------------------------------|----|

|      | s-domain Diagram                                                       | 76 |

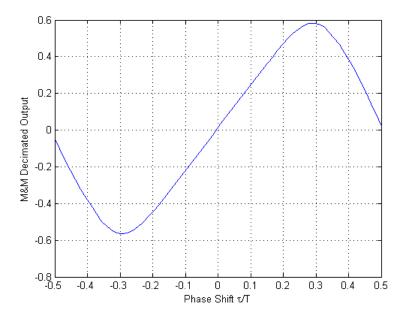

| 5.11 | S-curve of the M&M TED                                                 | 78 |

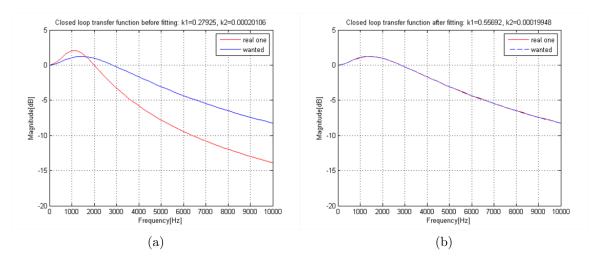

| 5.12 | Loop Filter Frequency response (a) before and (b) after compensating   |    |

|      | the effects of the digital arithmetic                                  | 79 |

| 5.13 | Loop Filter Final Implementation Diagram                               | 79 |

| 5.14 | $\Delta - \Sigma$ modulator Top level implementation diagram           | 80 |

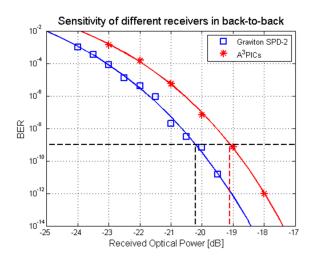

| 6.1  | Back-to-Back Sensitivity Comparison between the Graviton-SPD2          |    |

|      | and the Firecomms Receiver                                             | 82 |

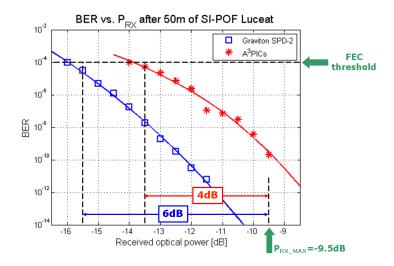

| 6.2  | Power Margin Comparison between the Graviton-SPD2 and the              |    |

|      | Firecomms Receiver for transmission over $50\mathrm{m}$ of PMMA-SI POF | 82 |

| 6.3  | Clock Recovery Experimental Set Up                                     | 83 |

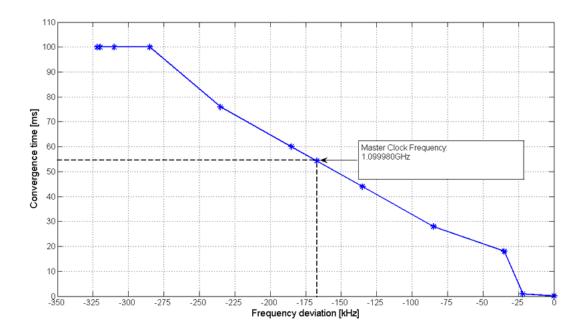

| 6.4  | Convergence Time of the Clock Recovery System                          | 84 |

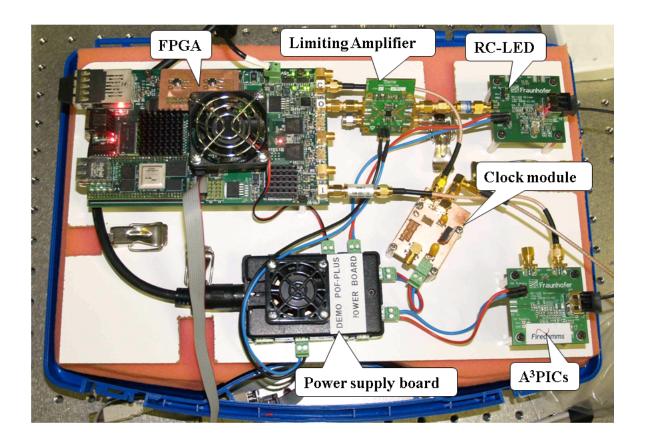

| 6.5  | Fully Engineered 1Gbit/s Media Converter                               | 85 |

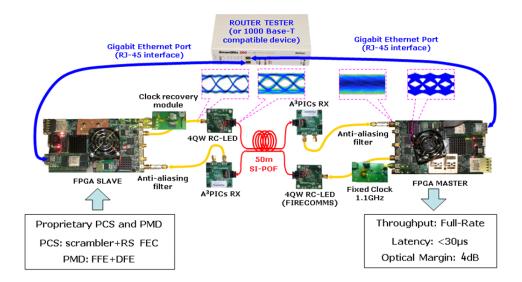

| 6.6  | Experimental Set Up for validate the Fully Engineered 1Gbit/s Media    |    |

|      | Converter                                                              | 86 |

| 6.7  | BER vs Received Optical Power the Fully Engineered 1Gbit/s Media       |    |

|      | Converter                                                              | 86 |

# List of Tables

| 2.1 | Main Properties of PMMA-SI POF                                   | 14 |

|-----|------------------------------------------------------------------|----|

| 2.2 | Summarized Features of Firecomms RC-LED                          | 15 |

| 2.3 | Summarized Features of the Graviton SPD-2 and the Firecomms RX   | 17 |

| 2.4 | BER measured in offline processing after 50 meter of PMMA-SI POF | 22 |

| 3.1 | Required Features for the Media Converter                        | 27 |

| 4.1 | Performance Results for 50m and 75m of PMMA-SI POF               | 63 |

| 4.2 | FPGA Resources and Area Utilization                              | 66 |

| 6.1 | Holding Window and Jitter Measurements                           | 83 |

# Chapter 1

## Introduction

Nowadays bandwidth hunger is increasing vertiginously. In this precise moment new on-line based applications are being developed, users are finding new ways of sharing information, new ways to get in touch. Social networks have arisen as worldwide platforms capable, in terms of software, of handling a vast range of information from tweets, to high definition videos, from music to e-books. As new ways and concepts of how to share information emerge, new ways of how to access the web enter the market. Computers and mobile devices are only the beginning. The spectrum of web products and services such as IPTV, VoIP, on-line gaming, etc has been augmented by the possibility to share, store data, interact and work on the Cloud.

The rush for bandwidth has led researchers from all over the world to enquire themselves on how to achieve higher data rates. And it is thanks to their efforts, that both long-haul and short-range communications systems have experienced a huge development during the last few years. In this respect, important contributions were made in the last mile of the network towards the user, defined formally as the access network. Among these valuable contributions, technologies such as Asymmetric Digital Subscriber Line (ADSL), Very high bit rate Digital Subscriber Line (VDSL) and Power Line Communications (PLC) provide communication links at speeds that range from tens of Mbps up to 100Mbps. However, as the demand for higher information throughput increases, these copper based solutions have begun to reach their limits. It is in this scenario that long-haul optical based solutions began migrating into short-range communications systems, giving place to the Fiber to the Home (FTTH) solutions.

### 1.1 Fiber-to-the-Home

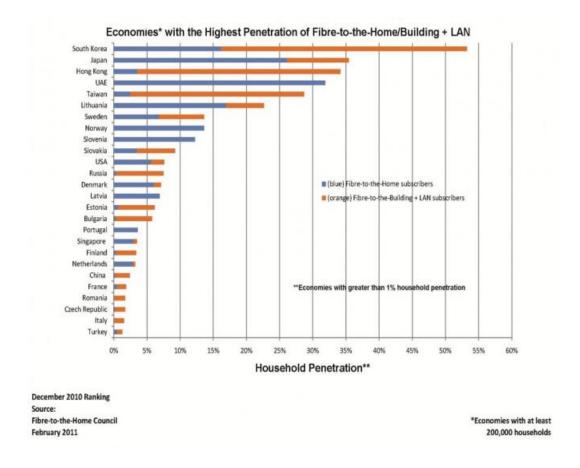

Statistics released by the FTTH Council in the year 2010 indicated that approximately 50.2 million users worldwide were already connected by optical fiber, the large majority of which were from the Asia Pacific Region with 38.9 million, followed by North America with 7.9 million, and last Europe with 3.4 million users [1]. Further analysis made by the same organization, established that the widespread deployment of high speed connections to the door step of the end user, together with the increasing presence inside premises of interconnected devices supporting and sharing different types of data (e.g. High Definition Video, mp3, etc) had shifted the network bottleneck to the short range networks inside the home. Earlier this year, and in order to support this position, they presented updated statistics confirming the FTTH penetration rate reported in 2010, see Fig. 1.1.

Figure 1.1: Economies with the highest penetration of FTTH/Building+LAN [2]

Fig. 1.1 shows the countries with the highest penetration rate of FTTH and FTTB (Fiber to the Building) plus Local Access Networks (LANs). Also, but in a collateral way, this figure shows a potential market for short-range optical fiber systems. According to the graph, subscribers categorized as FTTB+LAN, have access to fiber connections by means of LANs. Hence, the market opportunity here lies in implementing these connections using optical fiber. LANs can strongly benefit from its overall better performance, when compared with its eventual counterparts, in delivering information at high bit rates. In particular, optical fiber provides symmetrical access and larger bandwidth. It does not use electricity to transmit information, therefore it is immune to electromagnetic interference (EMI), so that it could be deployed through, let's say, power supply ducts. On the other hand, it is precisely the intrinsic roughness of such in-building/in-home installation environments what makes difficult to use the common and widely spread Glass Optical fibers (GOFs). Mainly because its deployment require specialized equipment and trained personnel, which in the end, implies more expenses and therefore a higher cost for Telecom Operators (Telcos).

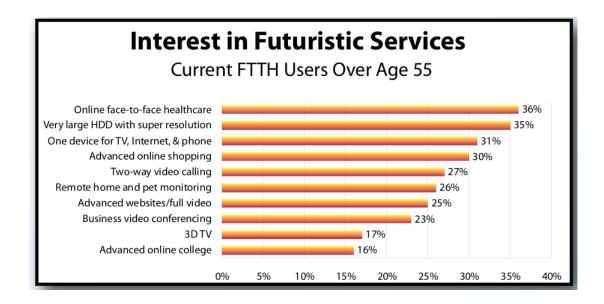

Figure 1.2: Interest in futuristic web services of current FTTH users over 55 years of age [3]

Alongside the above mentioned study, the FTTH council also presented an interesting study of how high bit rate access networks impacted the future expectations of its current users. In particular, the study analyzes the interests in futuristic web

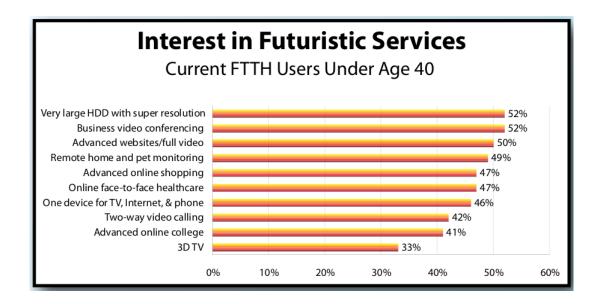

services of users categorized by age group. Figures 1.2 and 1.3 summarize the results by ranking the expectation stated by the members of each group in relation with future web services. These results show that people, depending on their age, relate in different ways with the web. Despite the differences there seems to be a constant factor shown by the fact that an important number of envisioned services will require real-time data streaming. Requirement that would imply by default, a high quality of service in order to guarantee a high quality of experience for the client; which means in other terms that any future broadband in-home network must provide: large bandwidth, low latency and low bit error rates (BER).

Figure 1.3: Interest in futuristic web services of current FTTH users over 40 years of age [3]

Regarding private networks within user's homes, technologies such as wireless fidelity (WiFi), power line communications (PLC) and solutions based on coaxial and UTP CAT cables have fulfilled today requirements. In doing so, they have demonstrated both advantages and disadvantages, WiFi for instance, is very attractive because of its easy deployment and configuration. However, its future improvements are challenged by an already saturated spectrum that makes difficult the allocation of new services, and also by access issues related to its distribution within a building, task that very often requires cabling between floors or to reach an isolated area. Hence, future broadband access networks have to deal with this reality and consider not only improving current technologies and creating new ones but also try to integrate them properly. In this sense and as an alternative to improve bandwidth limitations due to in-building cabling, novel systems based on both perfluorinated plastic optical fiber (PF-POF) and silica based multi-mode fiber (MMF) have been studied and demonstrated [4]. Recently, also optical wireless has been investigated as an option to WiFi, so that these systems combined together may become in the near future a very promising solution for LANs. Nonetheless, there are still challenges to overcome, even if these fiber cabling solutions were proven feasible, they still need to be deployed by expert personnel, and therefore the challenge still lies in finding a solution that allows safe and easy "do-it-yourself" installation. Under these circumstances and for these requirements, solutions based on POF are being investigated. The next sections will show the future envisioned for POF as part of the Fiber-in-the-Home (FITH) concept.

### 1.2 Fiber-in-the-Home

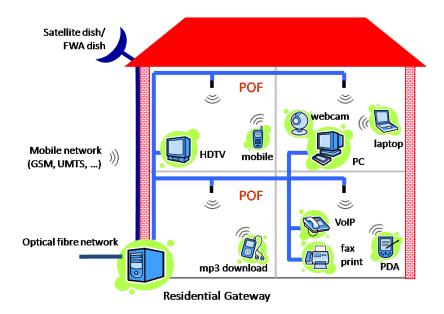

FITH is the term given for the foreseen future broadband in-home/in-building networks. A network in which the service provider will ensure high bit rate transmission service inside the user's house. Fig. 1.4 illustrates the envisaged POF based backbone for future residential networking. Furthermore and with the purpose of providing service to the vast and continuously increasing number of mobile devices, microwave and baseband network services were recently studied and demonstrated as part of the proposed FITH architecture [5].

# 1.3 Intensive Broadband Networking for Optical Interconnect Applications

Social Networking, web searching engines, working, storing and exchanging information on the Cloud have dramatically increased the amount of power computation, and therefore, of speed at which the vast range of algorithms involved in providing these services must be executed [7].

Currently, data centers are big warehouses where thousands of computer nodes are interconnected between them to form clusters, which are connected as well to operate as High Performance Computers (HPCs). Links for composing these grids span from very short distances of around <30cm for intra-computer node connection up to 10m for inter-rack connections. The link requirements include large bandwidth capacity (>20GHz), support of both bursting and non-interrupted data transfers, and as the data centers become larger, power consumption issues must be addressed in order to guarantee low cost green solutions [8]. It is in

Figure 1.4: Future Broadband In-Building Networks [6]

this scenario that optical interconnects communications systems based on large bandwidth PF-POF and MMF (BW around 13GHz) arise as potential solutions for HPC Systems in Data Centers (DC).

### 1.4 The EU POF-PLUS Project

Due to all the above mentioned reasons, during the last few years European Telecom Operators together with the European Union have been actively working and creating policies to bring broadband access to the European continent. As part of their effort the European Seventh Framework Program 7 (FP7) hosted the POF-PLUS Project [9], an initiative aimed to promote research and development of short-range optical communication solutions based on Plastic Optical Fiber (POF) to provide wired and wireless services for in-building/in-home networks and to investigate the feasibility of optical interconnects applications.

As mentioned, the intrinsic roughness of in-building/in-home environments makes difficult the deployment of conventional GOFs. Therefore, POF-PLUS proposed 1mm polymethyl methacrylate step index (PMMA-SI) POF as an alternative solution. More commonly referred as standard SI POF, this fiber is robust, ductile and tolerates extreme bending, thus it is the perfect candidate for installation in rough and less accessible locations. Moreover, its large core diameter (up to 1 mm) enables the relaxation of connector requirements without compromising optical coupling, which simplifies the design of connectors and allows the use of low cost materials for their manufacturing. As a result, do-it-yourself installation is possible and system costs are reduced, thus increasing the appealing of POF solutions for Telecom Operators.

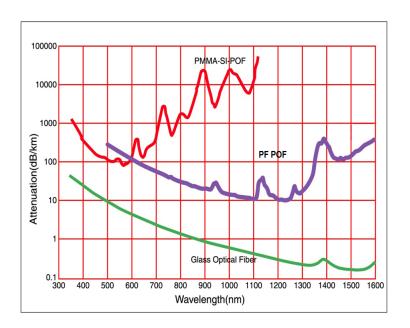

POFs outperform GOFs in terms of robustness. However, their advantages come at the expense of a considerable higher attenuation and bandwidth limitation. As seen in Fig. 1.5, both PMMA-SI POF and PF-POFs present higher attenuation values than GOFs, and accordingly, the lowest bandwidth is presented by PMMA-SI POF whilst the highest by GOFs. A full account concerning the different types of POF, their attributes and applications, is beyond the scope of the present document. More details in this respect can be consulted in [10].

In order to overcome the effect of the mentioned impairments, a list of objectives was defined within POF-PLUS. All of them aimed at the development of devices capable of transmitting and receiving data at >1Gbit/s over several tens of meters of POFs for applications such as multimedia device connections, in-building/in-home networks and optical interconnects in DCs. In particular, the fundamental activities of the project were defined as:

Design and implementation of a fully engineered real-time transceiver capable of establishing 1Gbit/s links over 50 meters of PMMA-SI POF using Light Emitting Diode (LED).

Figure 1.5: Attenuation Spectrum for different fibers

- Design, implementation and optimization of multi-Gbit/s optoelectronic transceivers to improve linearity, bandwidth and reliability.

- Optimization of transmission techniques for Multi-Gbit/s over tens of meters of non-standard novel large-core POFs using multi-core and/or multi-fiber ribbons.

- Reliable transmission of radio-over-fiber (RoF) systems over PMMA-SI POF.

### 1.5 The scope of this Thesis

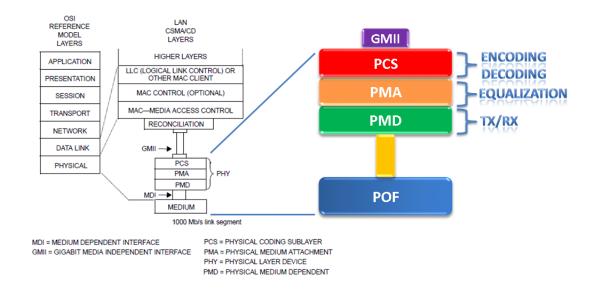

POF-PLUS was aimed, at least for which respect to the partnership POLITO-ISMB, to implement a fully engineered 1Gbit/s Ethernet Media Converter capable of establishing data links over 50+ meters of PMMA-SI POF using a LED as transmitter. Furthermore, the resulting system had to comply with the IEEE 802.3 Gigabit Ethernet Standard, which depending on its version defines transmission protocols for different physical layers (or transmission core materials). In this particular case the main version used was the 1000Base-X<sup>1</sup>, which defines operation with optical fiber at 1Gbit/s. Now getting into details, Fig. 1.6 shows the Ethernet layers as established by the Gigabit Ethernet Protocol (GEP) and their relation to the OSI reference model. This figure also shows the PMD, PMA and PCS sub-layers, that conform the Ethernet Physical Layer implemented by the Media Converter. Finally it also includes a summarized description in terms of their intended function within the Ethernet Media Converter for the POF system.

Figure 1.6: OSI/ETHERNET Layers implemented by the 1Gbit/s Media Converter

The scope of this thesis is the design, development, and implementation of the required equalizing algorithms. In particular, this dissertation presents their design and implementation by means of digital signal processing (DSP) on field programmable gate arrays (FPGAs). More in general, the final system for which all efforts within this thesis were made is illustrated by Fig. 1.7, in which two Ethernet Media Converters operate between a UTP CAT 5 cable and 50m of POF providing

$<sup>^{1}10\</sup>mathrm{Gbit}$  Ethernet in its version  $10\mathrm{Gbase}$ -R was also used as a reference to tackle specific tasks

1Gbit/s full duplex communication.

# 50m SI-POF Cable UTP CAT 5

## 1Gbit/s Ethernet Media Converter

Figure 1.7: Envisioned Full Duplex Gigabit Ethernet Media Converter

This thesis is organized as follows. Chapter 2 presents first a detailed description of the POF transmission channel (medium+PMD) by introducing its impairments and the challenges implied in transmitting through it, this is followed by a brief account concerning modulation formats and equalizing architectures that lead to the main requirements for implementing the Media Converter.

Chapter 3 focuses on the design and implementation of the PMA and PCS layers. In particular, the equalizing algorithms are first mathematically formulated and then adapted or redefined in order to implement them on the FPGA. Next is Chapter 4, which presents the experimental results that concern the first 1Gbit/s Media Converter prototype capable of establishing Full Duplex communication over 50+[m] of PMMA-SI POF.

Chapter 5 presents the design and development of a hybrid analog-digital clock recovery system. More in detail, its analysis and formulation, based in the theory of Phase Looked Loops (PLL), is presented. Then, this is followed by the description of its hardware implementation, giving particular attention first to the Timing Error Detector block which implements the Mueller and Muller algorithm, and later to the design and hardware implementation of the Loop Filter. Chapter 6

presents the results obtained with the fully engineered 1 Gbit/s Media Converter for transmission over 50  $[\rm m]$  of PMMA-SI POF.

Chapter 7 presents the conclusions derived from the above mentioned activities together with some comments and recommendations regarding future work.

# Chapter 2

# POF Short-Range Communication System

This chapter introduces the POF system and makes evident the inherent challenges that must be faced to run 1Gbit/s over it. In order to set the premises on which the work carried out by the author is based, experimental and simulative results obtained by the ISMB researchers before his involvement in POF-PLUS are presented. The author contributions to the project are detailed in next chapters. For which respects to the present discussion, it is organized as follows: a first part is dedicated to present the main features of the PMMA-SI POF, followed by a second part describing the optoelectronic components, i.e. light sources and photo detectors. Then, the main features and impairments of the complete POF transmission channel are presented, and finally the chapter ends presenting the results of an study of possible modulation formats and equalizing architectures for the Media Converter.

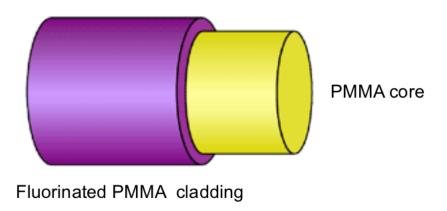

### 2.1 PMMA-SI POF

As aforesaid it was defined within POF-PLUS that the Media Converter had to be implemented using PMMA-SI POF. Also referred as standard SI POF, this fiber has a large core and a thin cladding (see Fig. 2.1) that present typical refraction indexes of 1.49 and 1.40, respectively. These characteristics lead to a large numerical aperture (NA) of  $\sim 0.5$  and an acceptance angle of  $\sim 30^{\circ}$ , which provide standard SI POF with the required handling robustness and tolerance to misalignments. Properties that in the end translate into lower costs by allowing the use of inexpensive splicing tools and connectors.

Nonetheless PMMA-SI POF qualities come at the expense of low bandwidth

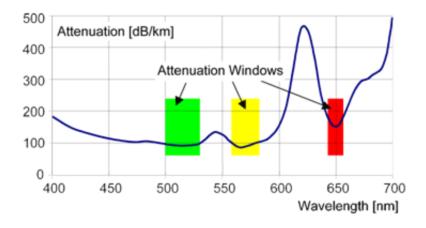

Figure 2.1: SI PMMA POF (taken from [11])

and high attenuation. Concerning the latter, Fig. 2.2 illustrates the attenuation spectrum of PMMA-SI POF. As seen, there are three relatively low attenuation regions (or windows) for which transmission is considered feasible. Incidentally these transmission windows are located within the visible spectrum, specifically on wavelengths around 520nm (green), 570nm (yellow), and 650nm (red), which results to be very convenient for the system, because the location of the transmission windows together with the fact that the Media Converter should operate with a LED (instead of a laser) mean that the system can be verified with a nude eye without incurring in any risk. So that, it not only improves safety but also enables do-it yourself installation and as an overall consequence reduces even further the cost.

Figure 2.2: Attenuation Spectrum of SI PMMA POF (taken from [11])

As shown in Table 2.1, PMMA-SI POF has a very limited bandwidth. condition that results from its high multi modal dispersion and that usually constitutes the main limiting factor in POF systems. Moreover, the POF channel (including the optoelectronic devices), acts upon the signal as if it were transmitted through an electrical low pass filter, which makes possible, for theoretical and analytic purposes, to approximate the frequency response of the channel (in the electrical domain) as a gaussian low pass filter. Later on, this property will be corroborated by experimental measurements obtained by means of a Vector Network Analyzer. Further information in this respect alongside with techniques to measure the bandwidth of different fibers can be consulted in [10].

| 1mm Standard SI-POF   |                    |  |  |

|-----------------------|--------------------|--|--|

| Core Diameter         | $1000[\mu { m m}]$ |  |  |

| Numerical Aperture    | $0.48 \pm 0.02$    |  |  |

| Bandwidth             | 40[MHz]·100[m]     |  |  |

| Attenuation @ 650[nm] | 160-180[dB]/[Km]   |  |  |

| Attenuation @ 520[nm] | 90[dB]/[Km]]       |  |  |

Table 2.1: Main Properties of PMMA-SI POF

Moreover, in Chapter 2 of this same source, it is stated that most of the time knowledge of the bandwidth alone does not suffice for a definitive analysis of the total capacity of a link involving further elements, simply because POFs behave differently depending on the properties of the other components of the set up, i.e. spectral width of the light source, its launching conditions, etc. In the light of this information, next sections will introduce the properties of the optoelectronic components that, once integrated with the fiber, will give place to the complete transmission channel.

## 2.2 Optoelectronic Transmitter

A key factor to achieve low cost, easy and safety deployment of POF technology, is the utilization of light emitting diodes (LEDs) instead of more complex and expensive lasers. Conventional LEDs are accessible and easy to use, they can be driven with CMOS technology, they present good thermal stability and they are more robust and have longer life time than lasers. For many years, red (650nm) LEDs have been used as optical sources in POF applications. Consequently, the POF-PLUS project included the development of a 650nm Resonant Cavity LED, which is a high

speed variant of a LED.

Figure 2.3: (a) Firecomms 650nm RC-LED (b) Eye Diagram @1.25GHz

| RC-LED                       | Units |       |

|------------------------------|-------|-------|

| Wavelength                   | 650   | [nm]  |

| Optical Output Power         | -1.5  | [dBm] |

| Optical Modulation Amplitude | -3.3  | [dBm] |

| Extinction Ratio             | 3     | [dB]  |

| Falling Time                 | 453   | [ps]  |

| Rising Time                  | 411   | [ps]  |

Table 2.2: Summarized Features of Firecomms RC-LED

RC-LEDs were first proposed in 1992 [12], since then companies such as Firecomms (former partner of the POF-PLUS project) have developed commercial RC-LED sources for high speed applications as for instance Fast Ethernet. During the last few years, Firecomms together with Fraunhofer Institute (another former partner) developed a 650nm RC-LED capable of giving an open eye diagram up to 1.25Gbit/s (see Fig. 2.3) thanks to the optimization of the electronic driver circuitry. Moreover it is integrated within an optolock, which is a Firecomms plug device specially tailored for POF applications whose specific purposes are making POF connection easier and more efficient by minimizing eventual misalignments between the fiber and the LED. The main features of the RC-LED are summarized in Table 2.2.

### 2.3 Optoelectronic Receiver

At the beginning of the POF-PLUS project and as part of its objectives, the development and optimization of a 650nm optoelectronic (O/E) converter was required. To this end, Firecomms working in collaboration with Fraunhofer delivered, after 18 months, an optical receiver that integrated a A<sup>3</sup>PICs photodiode with a Firecomms optolock in a Fraunhofer driving board (see Fig. 2.4 (a)). During its implementation, the set up for developing the Media Converter was integrated using an O/E converter Graviton SPD-2 (see Fig. 2.4 (b)). Given its high cost and dimensions (see Table 2.3), such a device is far from being considered a suitable candidate for a low cost POF solution, but it made possible to prototype the first the Media Converter.

Figure 2.4: 650nm (a) Firecomms Receiver (b) Graviton SPD-2

Later in the project, and after achieving some positive results, the Graviton SPD-2 was substituted by the Firecomms Receiver; even if this new component arose some new considerations for the system in terms of sensitivity, gain and, as will be shown later, power margin, it didn't invalidate the premises on which the development of the Media Converter was based. Therefore and for the purposes of this dissertation, the POF system that will lead us to the first version of the Media Converter will have the Graviton as a receiver.

|                  | Graviton SPD-2 | Firecomms RX | Units              |

|------------------|----------------|--------------|--------------------|

| Acceptable       | <1000          | <1000        | $[\mu \mathrm{m}]$ |

| Core Diameter    |                |              |                    |

| O/E Device       | $\phi 0.4$     | $\phi 0.4$   | [mm]               |

| Active Area      |                |              |                    |

| Sensitivity      | 25             | 24           | [dBm]              |

| Peak Sensitivity | 760            | 660          | [nm]               |

| Wavelength       |                |              |                    |

| Wavelength       | 380~1000       | 410~850      | [nm]               |

| Range            |                |              |                    |

| Variable         | NO             | YES          |                    |

| Gain Amplifier   |                |              |                    |

| Connector        | SMA            | Optolock     |                    |

| Interface        |                |              |                    |

| Frequency        | DC~1.2         | DC~1.25      | [GHz]              |

| Bandwidth        |                |              |                    |

| Noise Equivalent | -27.3          |              | [dBm]              |

| Power            |                |              |                    |

| Supply Voltage   | DC±15          | DC 5         | [V]                |

| Supply Current   | +150/-50       | 120/110      | [mA]               |

| Physical         | 103 x 44 x 21  |              | [mm]               |

| Dimension        |                |              |                    |

| Weight           | 130            |              | [g]                |

Table 2.3: Summarized Features of the Graviton SPD-2 and the Firecomms RX

# 2.4 Investigation of Modulation Formats and Equalizing Algorithms

At the beginning of POF-PLUS M-PAM modulation formats and post-equalization schemes for the implementation of the Gigabit Ethernet Media Converter were investigated. For this purpose a Matlab/Simulink set up was modeled based on either the measured frequency response of each element or, if not available, on ideal assumptions regarding its operation. For instance, the POF was modeled by means of its experimentally measured frequency response while the O/E transmitter was considered to be ideal, thus neglecting eventual nonlinearities. There were also assumptions related to the nature of the noise sources, the bandwidth of the overall channel, etc. For a detailed explanation, a full account of this investigation can be consulted in [13]. For the purposes of this dissertation the attention will be

focused on the main conclusions derived from this intensive simulation campaign, which were that 2-PAM and 4-PAM signals together with adaptive equalization at the receiver side in the form of a Decision Feedback Equalizer (DFE) are suitable solutions for implementing the Media Converter. More in detail, this section will present the off line processing analysis carried out in order to corroborate, with the actual system, the results obtained with the above mentioned simulations.

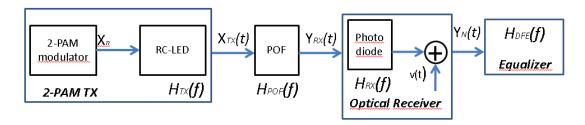

Figure 2.5: POF Transmission Channel

Accordingly, an FPGA development board was configured to generate 2-PAM and 4-PAM signals at 1.25GHz and at 0.625Gbauds, having thus in both cases a total throughput<sup>1</sup> of 1.25Gbit/s. Then, the Graviton SPD-2, 50m of PMMA-SI POF and the 650nm RC-LED were put together to conform the POF transmission channel shown in Fig. 2.5.

At this point, the effects of transmitting through this channel were evaluated by measuring the signal at the output of the Graviton SPD-2. The resulting eye diagram from 2-PAM transmission is reported in Fig. 2.6, showing that the signal is completely distorted and thus the eye is totally shut, condition that make evident the need of some sort of equalization in order to recover the original sequence.

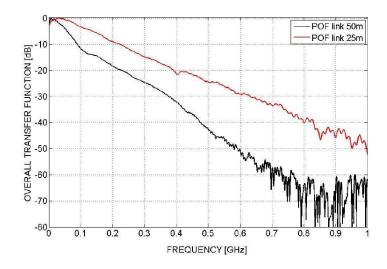

Consequently and in order to better understand the channel impairments, the following measurements consisted on obtaining the electrical-to-electrical frequency and impulse responses of the POF transmission channel by means of a Vector Network Analyzer (VNA), the results for 25 and 50 meters of POF are shown by

<sup>&</sup>lt;sup>1</sup>this value corresponds to the desired bit rate 1Gbit/s plus the overhead due to synchronizing and Forward Error Correction (FEC) codes as defined by the IEEE 802.3 Gigabit Ethernet Standard in its optical version 1000Base-X

Figure 2.6: 2-PAM Eye Diagram after 50 m of PMMA-SI POF

Figure 2.7: Frequency Response of the POF System

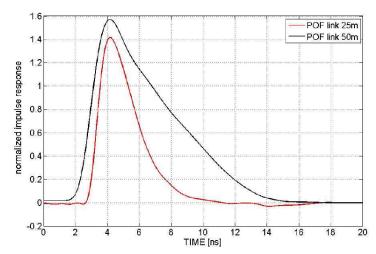

Figures 2.7 and 2.8.

As it may be noticed in Fig. 2.7 , the cut frequency for the POF transmission channel is around 150MHz for 25 meters of fiber, and 75MHz for 50 meters. These values are estimated as the limits for optical 3dB bandwidth which, since the electrical power is proportional to the square of the optical power, becomes 6dB for the transfer functions obtained with the VNA. For either case, it is clear that some kind of compensation should be done in order to be able to transmit at high data rates.

Considering now the impulse responses shown in Fig. 2.8, it is evident, due to the

Figure 2-3: Overall impulse response h(t).

Figure 2.8: Impulse Response of the POF System

broadening of the impulses, that the POF channel induces a very strong intersymbol interference (ISI) on the signal. ISI is the result of overlapping between the current symbol with previous and subsequent symbols and usually is caused by the limited bandwidth of the transmission channel and/or by multipath propagation. For the present case, ISI is evidenced by the fact that while each transmitted symbol has a duration of  $\sim 0.8$  [ns]<sup>2</sup>, the actual impulse response after the fiber spans 7ns for 25 meters of fiber, and 12ns for 50 meters. In other words, for the prototype target distance (50m) the pulse broadens more than 12 times its actual duration. Thus, proving once again that equalization is a must for recovering the transmitted signal.

Figure 2.9: DFE Architecture

$<sup>^2</sup>$ this corresponds to the inverse of the signal frequency 1.25GHz

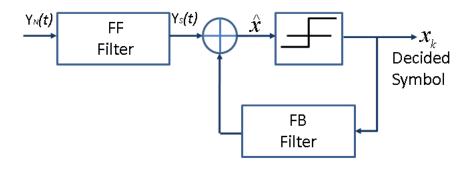

After the above quantitative characterization of the POF transmission channel, all efforts were directed to overcome its negative effects on the transmitted signal. Therefore, the acquired data were equalized (in off-line processing) by a DFE based on a Feed Forward (FF) and (FB) filters (see Fig. 2.9). More in detail, both filters i.e. FF and FB were implemented within the Matlab/Simulink<sup>TM</sup>environment using Finite Impulse Response (FIR) Filters and their taps coefficients were adapted with a gradient-based least mean square (LMS) algorithm. A detailed description of the equalizing and adapting algorithms applied during this study, as well as their hardware implementation within the Media Converter, is given in Chapter 3. Next the most relevant results of this experimental campaing are presented, for a full account the reader is referred to [13].

Figure 2.10: Received signal for (a) 2-PAM transmission over 50 m (b) 4-PAM transmission over 50 m (taken from [13])

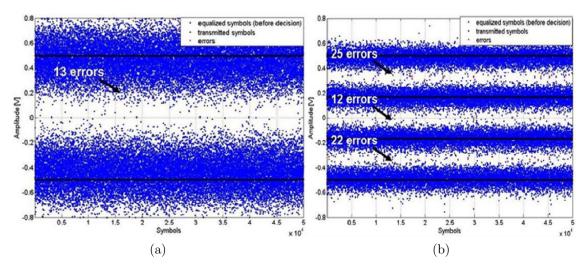

Fig. 2.10 shows the samples resulting at the output of the DFE from both 2-PAM and 4-PAM transmissions. As seen, the 4-PAM signal presents, after equalization, a non-homogeneous distribution of the errors that lead to a higher number of them in the external levels. This could indicate the presence of non-linearities on the optoelectronic devices. The overall effect of this condition is made evident by the measured BERs reported in Table 2.4. In the end, given the available set up, the main conclusion is that multilevel amplitude modulation, although it demands less bandwidth, presents a worse performance than conventional 2-PAM. Moreover, from a digital signal processing point of view 4-PAM implies, in terms of DC-balancing, equalizing hardware architectures and clock recovery, more complex implementations for both the transmitter and the receiver. All of which led to the decision to

implement the Gigabit Ethernet Media Converter using 2-PAM transmission.

| Transmitted Signal | BER                 |

|--------------------|---------------------|

| 2-PAM              | $2 \cdot 10^{-4}$   |

| 4-PAM              | $1.2 \cdot 10^{-3}$ |

Table 2.4: BER measured in offline processing after 50 meter of PMMA-SI POF

Once 2-PAM was chosen for implementing the Media Converter, an analysis regarding the performance of the system as a function of the DFE architecture was carried out. In particular, the system was evaluated in terms of the BER, the number of coefficients of the DFE and the optical power margin before FEC<sup>3</sup>. The set up for this study is shown in Fig. 2.11. As seen, it included: first a Pattern Generator in which a real Ethernet traffic stream was pre-stored, so that the effects of actual data on the system could be evaluated; second the 50 meters of PMMA-SI POF; third a Variable Optical Amplifier (VOA) used to vary the magnitude of the received optical power; and finally the off-line processing model for the DFE.

Figure 2.11: Experimental Set up for off line processing

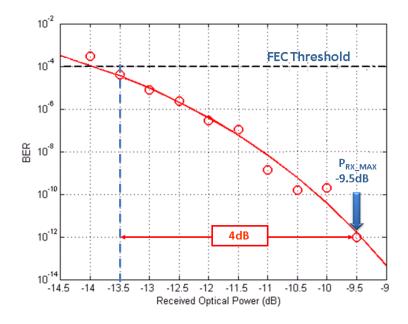

The first experiment consisted on measuring the BER of the system while varying the number of coefficients of both DFE stages, i.e. FF and FB. The received optical power was measured as -9.5dB (after the fiber) and it was maintained constant

$<sup>^3\</sup>mathrm{Here}$  the assumption is a FEC capable of correcting errors on a signal that presents a BER lower than  $10^{-3}$

throughout the test. The results are summarized by the contour graph shown in Fig. 2.12.

Figure 2.12: BER as a function of the number of taps of the FF and FB stages of the DFE

The second experiment consisted on measuring the BER for a fixed number of coefficients while varying the magnitude of the received optical power. At this point, an analysis based on the evaluation of the power margin obtained as a function of the number of taps coefficients of each stage together with the feasibility of an eventual implementation of the DFE, led to the conclusion that 16 FF and 2 FB taps coefficients guaranteed an acceptable power margin and were at the same time realizable. In this respect, Fig. 2.13 shows a power margin before FEC of 4.5dB for a DFE with the mentioned characteristics.

Figure 2.13: Measured BER vs extra-attenuation at the receiver.

### 2.5 Summary

This Chapter introduced the main properties of the PMMA-SI POF and of the optoelectronic devices that together constitute the POF channel. More in detail, the distortion and attenuation observed on the received signal evidenced that the POF channel is strongly limited in terms of bandwidth. Moreover, it was shown that the bandwidth limitation is mostly due to the PMMA-SI POF and that in order to retrieve the transmitted information, it is necessary to equalize the signal at the receiver.

In this sense, the results of an off-line processing experimental campaign were presented. In particular, it was concluded that a system based on 2-PAM transmission over 50 meters of PMMA-SI POF with adaptive and blind equalization at the receiver in the form of a 16 FF tap coefficients followed by a 2 DFE tap coefficients guarantee 4.5 dB of optical power margin before FEC.

Chapter 3 presents formally the mathematical model for both the equalizing as well as the adaptation algorithms that were used for the above mentioned analysis. Also a detailed account explaining how they were implemented on FPGA is given.

# Chapter 3

# Media Converter Prototype: 1Gb/s over 50+ m

This chapter presents the design and implementation of the Gigabit Ethernet Media Converter. The discussion is organized as follows: at first the requirements for the system are summarized and the methodology followed for prototyping the system is presented. Subsequently, the Media Converter is described in terms of the Ethernet Layers as they are defined by the 802.3 Gigabit Ethernet Standard, particular attention is given to the PMA sublayer in which the equalizing schemes required for achieving transmission over the PMMA-SI POF are implemented. Accordingly, section 3.4.1 presents the theoretical model of the equalizing and adapting algorithms followed by an analysis that redefines them to allow their implementation on FPGA.

### 3.1 Design Specifications

The general requirements for the Media Converter implementation are:

- To achieve complete compatibility with IEEE 802.3 Gigabit Ethernet Standard.

- To reduce the effects of POF limited bandwidth.

- To develop a very efficient full-custom PHY tailored for POF applications that minimizes the transmitted in-line bit rate.

More in detail, compliance with the IEEE 802.3 Gigabit Ethernet Standard means that the system must provide a throughput of 1Gbit/s, which implies testing and validating the prototype with traffic at gigabit data rates. For this reason the media conversion is performed between 50 meters of SI-PMMA POF and a

link based on an UTP CAT-5 copper cable. In this sense and according with the Ethernet layers defined by Gigabit Ethernet Standard the complete system results in the scheme illustrated in Fig. 3.1.

Figure 3.1: Ethernet Layer Scheme of the Media Converter

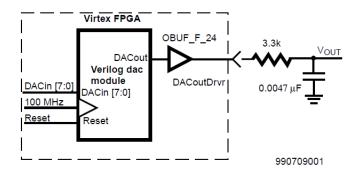

As seen, the Media Converter implements not only the physical layer required by the optical POF link, but also the one corresponding to the analog transceiver for ethernet communication over the UTP cable. Regarding POF bandwidth limitation and in-line bit rate minimization, the PCS and the PMA sublayers (in the POF PHY) are specially designed to address these requirements. In particular, the PMA implements the pertinent equalizing algorithms while the PCS is in charge of synchronizing and correcting the eventual errors still present after treating the signal. Moreover, this diagram shows that the Media Converter is mostly implemented as an embedded system within an FPGA Virtex4 XC4VS35-FF12 that is mounted together with other electronic peripheral devices on a BITSIM Ultra High-Speed Acquisition Board (UHAB). Among these peripherals, there is the BMC5461 Gigabit transceiver, which is a commercial device that implements the Ethernet PHY layer and provides the GMII interface, thus allowing to connect directly any design implemented on the FPGA. Throughout this document, the most relevant features of this board and its components will be presented. For further and more detailed information regarding this device, the reader is referred to [14].

In the following sections, the design and/or implementation of all the above mentioned sub-layers towards the POF will be described, but before proceeding the reader should acknowledge and be aware of the required and actual characteristics of the Media Converter as summarized on Table 3.1.

| Media Converter Characteristics |             |          |                   |  |  |

|---------------------------------|-------------|----------|-------------------|--|--|

| PARAMETER                       | VALUE       | Units    | NOTES             |  |  |

| Throughput                      | 1           | [Gbit/s] | 1000Base-X        |  |  |

| Transmission Mode               | Full Duplex |          |                   |  |  |

| FEC                             | RS(237,255) |          | Reed Solomon      |  |  |

| Coding Scheme                   | 64B/65B     |          | 10G Ethernet      |  |  |

| Modulation Format               | 2-PAM NRZ   |          |                   |  |  |

| Line Baud Rate                  | 1.0991      | [Gbit/s] | includes overhead |  |  |

| Target Distance                 | 50          | [m]      |                   |  |  |

| Maximum BER                     | $10^{-3}$   |          | Before FEC        |  |  |

| Transmitted Optical Power       | -1.5        | [dBm]    | Modulated         |  |  |

| POF bandwidth                   | 40(@100m)   | [MHz]    |                   |  |  |

| POF attenuation @650nm          | 160-180     | [dB/Km]  |                   |  |  |

| Received Optical Power          | -9.5        | [dB]     | After 50m of POF  |  |  |

| Power Margin                    | 4.5         | [dB]     |                   |  |  |

Table 3.1: Required Features for the Media Converter

## 3.2 Implementation Methodology

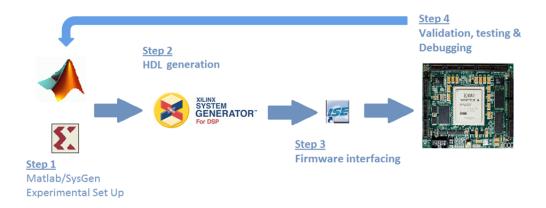

The methodology followed for implementing the Media Converter is illustrated by Fig. 3.2. As the reader can see, the first step involved designing and simulating the system using Matlab/Simulink. More in detail, the Xilinx System Generator Toolbox was used to implement the required DSP algorithms. Once these systems were validated through simulation a translation tool generated the VHDL code (step 2) together with all the files needed for the instantiation within the BITSIM firmware (step 3). Only then, the VHDL project was compiled using the ISE software from Xilinx and then the FPGA was configured (step 4). The iterative nature of this process was concretized when bugs or new problems were identified during experimentation with the complete set up, so that re-designing at simulation level was needed. For further information regarding the implementation of DSP

systems using the Xilinx System Generator Toolbox the reader is referred to [15].

Figure 3.2: Implementation Methodology Diagram

After having described the tools and methods applied for delivering the prototype, next section begins its description by introducing the reader to the implementation of the PCS sublayer.

# 3.3 Physical Coding Sublayer PCS

According to the IEEE 802.3 Gigabit Ethernet Standard, the PCS sub-layer defines the way in which a datastream is arranged in code words before being transmitted over a physical link. This operation may imply words synchronizing and signaling, error correction algorithms and DC-balancing considerations. Recalling the structure of the Ethernet Physical Layer (see Fig. 3.3), the PCS operates between the GMII interface and the low sublayers towards the transmission medium, i.e. PMA and PMD.

As mentioned for this project the version 1000Base-X of the Ethernet Standard was used as reference. Basically, the 1000Base-X defines the same PCS/PMA architectures for different physical layers depending on the type of fiber and transmission wavelength used. In other words, it relies mainly on the features of the transmission channel (fiber+optoelectronics) to achieve error free transmission. However, the standard 1000Base-X PHY is not enough for overcoming the impairments introduced by the POFs, so that for the present case it was necessary to add more computation power and complexity at a higher level.

Figure 3.3: Ethernet Layers

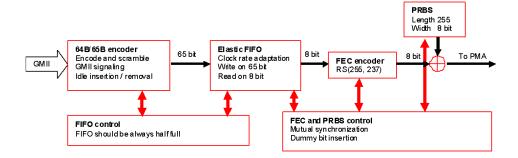

Figure 3.4: PCS transmitter

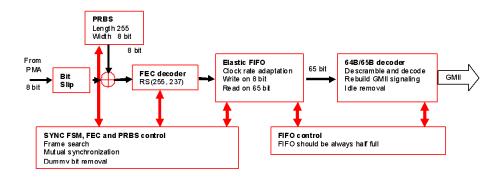

Therefore in order to address bandwidth limitation a 64/65B coding scheme from the 10Gbit Ethernet version 10Gbase-R was used instead of the 8B/10B coding specified by Gigabit Ethernet version 1000Base-X. This decision allowed an important bandwidth overhead reduction. Moreover, its implementation together with FEC encoding based on a Reed Solomon (RS) code (255,237) resulted in a serial line rate of 1.0991GBit/s instead of the 1.25GBit/s (without FEC) defined by the more common 1000Base-X. Figures 3.4 and 3.5 show respectively the transmitter and receiver sides of the implemented PCS. For further details on this matter, the reader is referred to [16]. Next the PMA will be described.

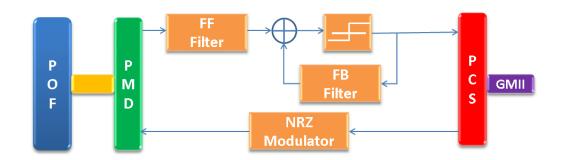

## 3.4 Physical Medium Attachment PMA

This section describes the design and implementation of the PMA layer. In particular, the mathematical formulation for both the received signal as well as the equalizing and adaptive algorithms are introduced. The description of the system begins by showing in Fig. 3.6 the general block diagram of the PMA as part of the

#### POF PHY Layer.

As seen, it is composed, in transmission, by a Not Return to Zero (NRZ) modulator that acts upon the serial bits arriving from the PCS while, in reception, it presents the DFE in charge of processing the incoming distorted symbols. As mentioned in section 2.4, the equalizer is formed by a Feed Forward (FF) and a Feedback (FB) filters together with the logic to adapt their coefficients. The system is adaptive and blind, which means that the channel is not known a priori so that the DFE is adapted to match it, and in doing so, no training sequence is used. In the following a description of their design will be given, for a more detailed analysis the reader can consult Chapter 8 of [17], in which many of the equations and considerations that are presented throughout this document were studied.

The first step of the design process consist on obtaining an expression to model the impairments inflicted by the POF channel on the received signal. Accordingly, the analysis starts by proposing the block digram shown in Fig. 3.7, from which, considering that the overall frequency response of the channel comprehends the individual transfer function of each of its components, an expression for the POF channel can be derived as

$$p(t) = (h_{TX}(t) * h_{POF}(t) * h_{RX}(t)) = \mathcal{F}^{-1}[H_{TX}(f) \cdot H_{POF}(f) \cdot H_{RX}(f)]$$

(3.1)

where  $H_{POF}(f)$  is modeled as a linear time invariant (LTI) low pass filter, while  $H_{TX}(f)$  and  $H_{RX}(f)$  correspond to the theoretical transfer functions of the 2-PAM TX + RC-LED and the Graviton SPD-2, respectively. Once the channel is modeled,

Figure 3.5: PCS receiver

Figure 3.6: General Diagram of the PMA

Figure 3.7: General Diagram of the POF Channel

the signal at the output of the optoelectronic receiver can be expressed as

$$Y_R(t) = \sum_{n = -\infty}^{n = \infty} x_n p(t - nT) + v(t)$$

(3.2)

where  $x_n$  denotes the 2-PAM symbols transmitted, T is the bit duration and v(t) is the inherent additive colored Gaussian noise introduced during the optoelectronic conversion. Moreover, given that the equalizer is implemented in the digital domain, the signal expressed by 3.2 is sampled so that supposing periodic sampling times of t = kT, it becomes

$$Y_R(kT) = x_k p(0) + \sum_{n \neq k} x_n p(kT - nT) + v(kT)$$

(3.3)

or, equivalently

$$Y_R(k) = x_k p_0 + \sum_{n \neq k} x_n p_{k-n} + v_k$$

(3.4)

The first term on the right-hand side (RHS) of 3.4 corresponds to the transmitted symbol while the second term correspond to the ISI. As aforementioned, ISI is

a form of signal distortion in which one symbol is affected by the interference of subsequent and previous symbols. It is caused by the limited frequency response and the amplitude attenuation of the transmission channel. Moreover, its presence implies synchronizing difficulties and noise margin reduction, that together produce errors at the receiver. Thence, the need to eliminate it from the received signal. In this respect, the equalizer architecture that is been proposed is specially tailored for this purpose.

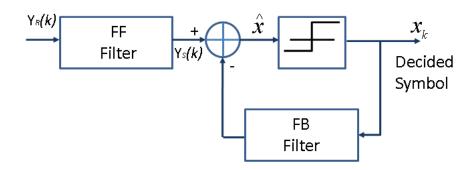

#### 3.4.1 Decision Feedback Equalization

Decision Feedback Equalization makes use of previous decisions in attempting to estimate the current symbol. Any intersymbol interference caused by previous symbols is reconstructed and then subtracted from the current estimated symbol [18]. According to its block diagram (see Fig. 3.6), its configuration includes a FF filter for shaping the channel output signal followed by a FB filter that subtracts the ISI. Due to the presence of a decision device within the feedback loop, the DFE is inherently a nonlinear receiver. However, it can be analyzed using linear techniques by assuming all previous decisions as correct [19]. In practice, this may not be true, and can significantly affect the overall performance of the equalizer. Nonetheless, including errors in the decision feedback section would complicate its analysis. In general, the most efficient way to specify the effect of feedback errors is via measurement. The analysis of the DFE begins by analyzing its FF filter.

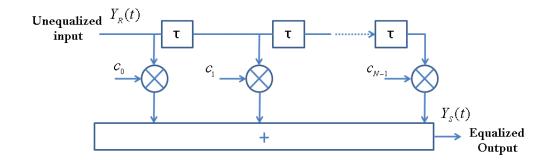

#### Feed Forward Filter

FF filters are generally implemented in the form of linear equalizers by means of FIR filters with tap coefficients  $c_n$ , as illustrated in Fig. 3.8. As seen, the time delay  $\tau$  between taps may be chosen equal to the symbol period T, in which case the filter is referred to as symbol spaced equalizer and its input corresponds to the sequence given by 3.4. On the contrary, if the time delay  $\tau$  is chosen such that  $\tau < T$  then the equalizer has fractionally spaced taps and hence it is called fractionally spaced equalizer (FSE) [20].

The impulse response of the FIR equalizer is

$$h(t) = \sum_{n=0}^{N-1} c_n \delta(t - n\tau)$$

(3.5)

where  $c_n$  are the N equalizer coefficients, where N must be large enough so that the equalizer spans in time as much as the ISI and thus it can attempt to compensate

Figure 3.8: Linear FIR Filter

this spurious effect by means of the convolution between its tap coefficients and the samples of the input signal. This may be mathematically expressed by recalling Eq. (3.2) and defining its output as

$$Y_S(t) = \sum_{n=0}^{N-1} c_n Y_R(t - n\tau)$$

(3.6)

considering that the FSE input is sampled at times t = kT

$$Y_S(kT) = \sum_{n=0}^{N-1} c_n Y_R(kT - n\tau)$$

(3.7)

Now that we have an expression for the FSE output, we may proceed to derive an expression for adapting the FSE taps coefficients and thus match the frequency response of the FSE to the transmission channel. In order to do this, the mean square error (MSE) between the desire symbol  $x_k$  and the equalizer output  $Y_S(kT)$ is computed

$$MSE = E[Y_S(kT) - x_k]^2$$

$$= E\left[\sum_{n=0}^{N-1} c_n Y_R(kT - n\tau) - x_k\right]^2$$

$$= \sum_{n=0}^{N-1} \sum_{m=0}^{N-1} c_n c_k R_Y(n-m) - 2\sum_{k=0}^{N-1} c_k R_{XY}(m) + E[x_k^2]$$

(3.8)

where

$$R_Y(n-m) = E[Y_S(kT - n\tau)Y_S(kT - m\tau)] R_{XY}(m) = E[Y_S(kT - m\tau)x_k]$$

(3.9)

then by differentiating Eq. (3.8) with respect to the taps coefficients  $c_n$ , we obtain an expression from which the optimum set of taps can be derived

$$\sum_{n=0}^{N-1} c_n R_Y(n-m) = R_{XY}(m), \text{ where } m = 0,1,2,\dots,N$$

(3.10)

equivalently, this may be expressed as a matrix

$$\mathbf{R}_{\mathbf{Y}} \cdot \mathbf{C} = \mathbf{R}_{\mathbf{XY}} \Rightarrow \mathbf{C}_{\mathbf{opt}} = \mathbf{R}_{\mathbf{Y}}^{-1} \cdot \mathbf{R}_{\mathbf{XY}}$$

(3.11)

Normally, if the system does not require to be blindly adapted,  $C_{opt}$  can be estimated by transmitting a training sequence and obtaining  $R_Y$  and  $R_{XY}$  by means of the following estimators

$$\mathbf{R}_{\mathbf{Y}} = \{\mathbf{Y}_{\mathbf{S}}\mathbf{Y}_{\mathbf{S}}^*\} \approx \widehat{R}_Y(n-m) = \frac{1}{K} \sum_{k=1}^K Y_S(kT - n\tau) Y_S(kT)$$

$$\mathbf{R}_{\mathbf{XY}} = \{\mathbf{Y}_{\mathbf{S}}\mathbf{x}_{\mathbf{k}}^*\} \approx \widehat{R}_{XY}(m) = \frac{1}{K} \sum_{k=1}^K Y_S(kT - n\tau) x_k$$

(3.12)

On the contrary when the system has to be adapted blindly, as in the present case, an stochastic gradient algorithm known as Least Mean Square (LMS) can be applied, so that the tap coefficients are optimized according to the following expression

$$\widehat{\mathbf{C}}_{k+1} = \widehat{\mathbf{C}}_k + \mu \varepsilon_k \mathbf{Y}_{\mathbf{S}_k} \tag{3.13}$$

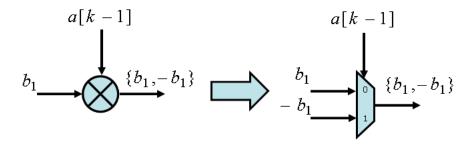

where  $\widehat{\mathbf{C}}_k$  is a vector with the set of taps at the  $k^{th}$  iteration,  $\mathbf{Y}_{\mathbf{S}k}$  corresponds to the received signal at the FSE input,  $\mu$  is the step-size parameter (scales the correction) and  $\varepsilon_k$  denotes the error, which is defined as the difference between the desired output from the FSE at  $k^{th}$  iteration and the actual transmitted symbol. Later, after completing the description of both equalizing stages, the algorithms used to compute the error signal  $\varepsilon_k$  will be presented. In the meantime, the mathematical model and architecture of the Feedback Filter will be presented.

#### Feedback Filter

The linear equalizer described in the previous section is effective on channels where ISI is not severe. The severity of the ISI depends strongly on the spectral characteristics of the channel. For instance, when a channel presents a strong attenuation or even a spectral null the equalizer tries to compensate it by introducing a large gain in its frequency response, which as a result leads to

noise enhancement and thus affects the equalizer performance. A solution to this problem is to implement a DFE [19] by adding a feedback filter as shown in Fig. 3.9.

Figure 3.9: Block Diagram of DFE

The feedback filter may also be implemented as an FIR filter with symbol-spaced taps. As seen, it receives the previously decided symbols and generates a signal that is subtracted from the output of the FF section. This operation is mathematically expressed as

$$\widehat{x}_k = Y_S(kT) - \sum_{n=1}^{N_b} b_n x_{k-n}$$

(3.14)

substituting Eq. (3.7) in Eq. (3.14), we have

$$\widehat{x}_k = \sum_{n=0}^{N_f - 1} c_n Y_R(kT - n\tau) - \sum_{n=0}^{N_b - 1} b_n x_{k-n}$$

(3.15)

where  $c_n$  and  $b_n$  are the tap coefficients of the feed-forward and feedback filters, respectively, while  $N_f$  and  $N_b$  correspond to the filters length, finally  $x_{k-n}$  are the previously decided symbols. Equivalently, Eq. (3.15) may also be expressed as a matrix

$$\widehat{\mathbf{X}}_k = \mathbf{C}^T \mathbf{Y}_R - \mathbf{B}^T \mathbf{X}_{k-n} \tag{3.16}$$

In order to simplify Eq. (3.16), it is convenient to define an augmented vector for the tap coefficients

$$\widetilde{\mathbf{C}} = \begin{bmatrix} \mathbf{C} \\ \mathbf{B} \end{bmatrix} \tag{3.17}$$

and also for the DFE inputs

$$\widetilde{\mathbf{Y}}_k = \begin{bmatrix} \mathbf{Y}_k \\ \mathbf{X}_{k-n} \end{bmatrix} \tag{3.18}$$

so that Eq. (3.16) becomes

$$\widehat{\mathbf{X}}_k = \widetilde{\mathbf{C}}^T \widetilde{\mathbf{Y}}_k \tag{3.19}$$

where T denotes the transpose operator.

Once the DFE output has been derived including the effects of both FF and FB stages, we can re-define Eq. (3.13) as

$$\widetilde{\mathbf{C}}_{k+1} = \widetilde{\mathbf{C}}_k + \mu \varepsilon_k \widetilde{\mathbf{Y}}_k \tag{3.20}$$

where  $\mu$  corresponds again to the step-size parameter (scales the correction) while  $\varepsilon_k$  denotes the error, which is defined depending on the adapting method that is chosen to optimize the equalizer.

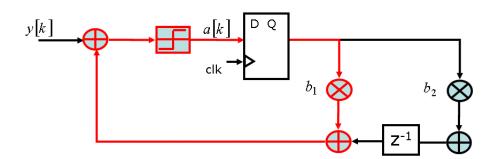

As aforementioned, the equalizer has to be adapted blindly, which means that the system cannot be optimized by means of a training sequence. In this sense, traditional adaptive DFEs are adapted using the Decision Directed (DD) algorithm which defines the error as

$$\varepsilon_k = \hat{x}_k - x_k \tag{3.21}$$

where  $\hat{x}_k$  corresponds to the signal just before the slicer and  $x_k$  to the decided symbol at its output. However, it is known that DD presents convergence problems such as gradient attraction to undesired local minima, which according to [21], occurs because of the finite length of the equalizer filter and the poor selection of cost functions, i.e. the function that defines the criterion to be minimized whose surface may present more than one minima. As a consequence, it was decided to adjust the system estimating  $\varepsilon_k$  by means of the Constant Modulus Algorithm (CMA)[19], which as reported in [22] constitutes a more robust method than DD for converging to global optimums. More in detail, the CMA assumes the constant modularity of the signal as the desired property to equalize, therefore the incoming sequence is considered as a modulated signal with constant amplitude, so that any amplitude deviation at the receiver constitutes a distortion introduced by the channel, for the present case this is expressed as

$$\varepsilon_k = Y_{Sk} \cdot (|Y_{Sk}|^2 - \gamma^2) \tag{3.22}$$

where  $Y_{Sk}$  corresponds to the FF output signal while  $\gamma$  is the CMA dispersion constant defined as

$$\gamma = \frac{E\{Y_{Rk}^4\}}{E\{Y_{Rk}^2\}} \tag{3.23}$$

where  $Y_{Rk}$  corresponds to the input signal of the FF filter.

Nonetheless, since the CMA is based on high order statistics, it suffers from slow convergence rate and high residual noise [19]. Therefore, after achieving convergence using the CMA, it was decided to add a further adaptation stage in which the system is adapted by means of the more precise DD method [23]. More in detail, during the first part of the adapting procedure the FB filter is disabled and therefore only the FF filter is adapted, meanwhile, the MSE is monitored so that once it reaches a certain low value indicating an state of CMA convergence, the equalizer switches to decision-directed (DD) mode and enables also the FB section.

So far, this chapter has theoretically formulated the equalizing and adapting algorithms as they are normally presented in literature [18], [20], [19], and accordingly as they are usually modeled as part of off-line processing experimental set ups. However, these models do not necessarily suffice the requirements of an FPGA based implementation, mainly because depending on the required throughput and on the on-board peripheral devices the system may need to be implemented by means of parallel and pipelined hardware architectures. In this sense, next section presents the analysis and resulting set of redefined equations that fit the features of our chosen development platform, the BITSIM FPGA board.

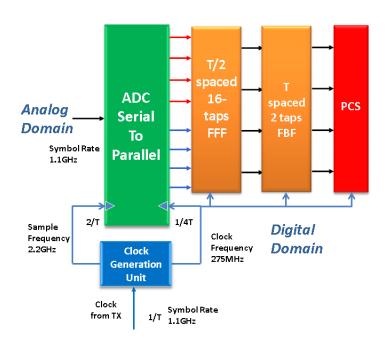

# 3.4.2 DSP Implementation of an Adaptive and Blind Decision Feedback Equalizer

In our work, the DFE is based on DSP techniques and is entirely implemented in the digital domain as an embedded system on an FPGA. As aforementioned, an Ultra High-speed Acquisition Board (UHAB) from BITSIM was selected for prototyping the Media Converter. In order to draft the possible hardware architectures to implement the DFE, it is first necessary to know the available on board clock domains. In this sense the most relevant on board component to define the chosen FPGA clocks are the analog to digital (ADC) and Digital to Analog (DAC) converters, because both devices together with the FPGA clock determine the parallelizing requirements, clock domains and also constrain the possible designing schemes for implementing the DFE. In the following, it will be explained how the DFE presented in section 3.4.1 is implemented using a highly parallel strategy.

Figure 3.10: PMA Top Level Implementation Diagram

For the present case, Fig. 3.10 shows the top-level<sup>1</sup> implementation diagram of the receiver side of the PMA as part of the Media Converter. As seen, the ADC

<sup>&</sup>lt;sup>1</sup>Henceforth, the description of the system will lead us to lower hardware levels, which will be referred by a cardinal number, i.e top level, first level, second level and so on, this is a common practice for among hardware designer

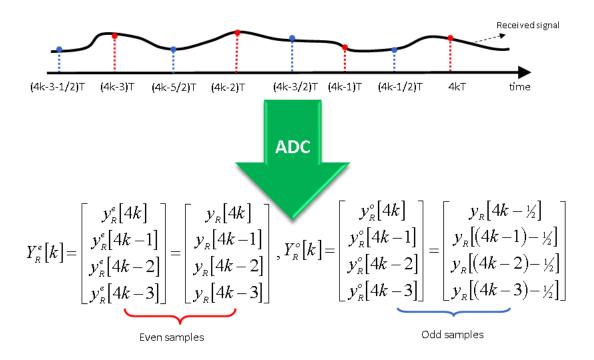

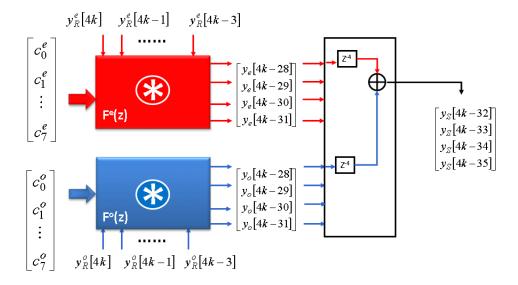

mounted on the BITSIM board provides the FPGA with 8 parallel samples each clock cycle. This means that the ratio between the sampling frequency and the FPGA clock frequency corresponds to one-eight, therefore considering that the input signal is transmitted at 1.1Gbit/s, the ADC clock frequency was fixed at 2.2GHz (the limit of the Nyquist Rate for two samples per bit) and thus the FPGA clock frequency at 275MHz. Moreover, Fig. 3.11 shows how the samples provided by the ADC are first categorized as odd or even samples and then arranged in two groups constituted by four samples each so that they can be processed in parallel inside the FPGA. This categorizations is performed because it facilitates implementing the FF filter. More in detail, the fact that the data is provided in two groups at the same data rate as the incoming signal allows the implementation of the FF filter as a Fractionally Spaced Equalizer conformed by two parallel baud spaced filters. On the other hand it should be noticed that this system outputs only 4 parallel data streams, which corresponds to the minimum number of samples required by the on board DAC in order to be able to maintain the signal throughput, in other terms, 4 data lines at 275Mbps give place, after being serialized, to a single line at a data rate of 1.1Gbps. Further details in this regard are given later, next the implementation of the FF filter in the form of a FSE equalizer is presented.

Figure 3.11: Samples Arrangement at the ADC output

#### Fractionally Spaced Equalizer

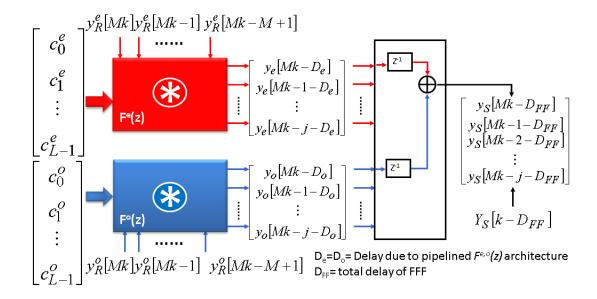

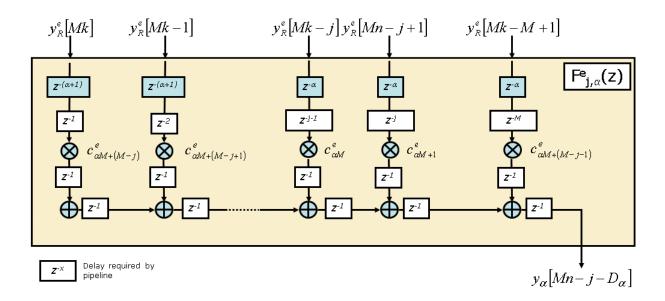

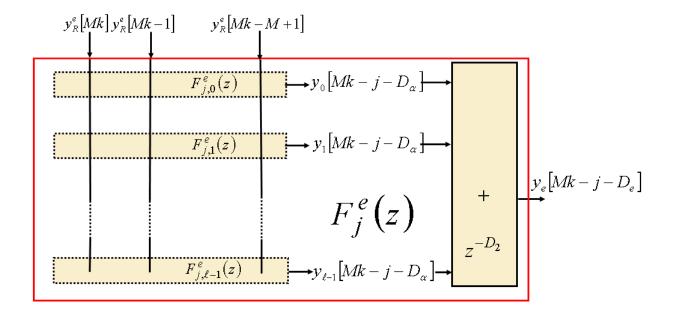

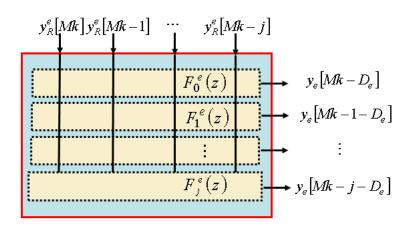

The fractionally spaced equalizer shown in Fig. 3.12 follows the above mentioned sample categorization. As seen, it is composed by two parallel filters that compute the convolution between the tap coefficients  $(c^o, c^e)$  and the samples  $(Y_R^e, Y_R^o)$  provided by the ADC. More in detail, this figure shows how the ADC samples are grouped in two sets formed by M odd (blue) and M even (red) samples, where M is the generic parallelizing factor, while in the same matter, the coefficients of each parallel baud space filter are grouped in two sets formed by L odd and L even tap coefficients. In particular and in correspondence with the sample sets shown in Fig. 3.11 the generic parallelizing factor M is equal to 4, while in correspondence to the off-line processing analysis presented in section 2.4, the L number of taps coefficients for each parallel filter is equal to 8, i.e 8 odd and 8 even taps that add together to the required 16 FF taps. In the following, the mathematical model of the DFE that was presented in section 3.4.1 will be adapted and as a result a set of equations describing the DFE hardware architecture in terms of the above mentioned generic factors will be given.

Figure 3.12: FSE First Level Implementation Diagram

Let us begin by deriving a first expression for the  $j^{th}$  row of the FSE output signal  $y_S$

$$y_S[Mk - j] = y_e[Mk - j] + y_o[Mk - j]$$

(3.24)

where  $y_e$  and  $y_o$  correspond to the outputs of the even  $F^e(z)$  and odd  $F^o(z)$  filters, which are defined as

$$y_e[Mk - j] = \sum_{i=0}^{L_f - 1} c_i^e Y_R^e[Mk - i - j]$$

(3.25)

and

$$y_o[Mk - j] = \sum_{i=0}^{L_f - 1} c_i^o Y_R^o[Mk - i - j]$$

(3.26)

where  $L_f$  denotes the length of the filters, c corresponds to the taps coefficients and  $Y_R$  are the samples of the incoming signal provided by the ADC.