### POLITECNICO DI TORINO Repository ISTITUZIONALE

Influence of parasitic capacitance variations on 65 nm and 32 nm predictive technology model SRAM core-cells

| Original Influence of parasitic capacitance variations on 65 nm and 32 nm predictive technology model SRAM core-cells / DI CARLO, Stefano; Prinetto, Paolo Ernesto; Savino, Alessandro; Scionti, A STAMPA (2008), pp. 411-416. (Intervento presentato al convegno IEEE 17th Asian Test Symposium (ATS) tenutosi a Sapporo, JP nel 24-27 Nov. 2008) [10.1109/ATS.2008.13]. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/1845210 since: 2016-09-16T17:16:00Z                                                                                                                                                                                                                                                                                     |

| Publisher: IEEE Computer Society                                                                                                                                                                                                                                                                                                                                          |

| Published DOI:10.1109/ATS.2008.13                                                                                                                                                                                                                                                                                                                                         |

| Terms of use:                                                                                                                                                                                                                                                                                                                                                             |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                           |

| Publisher copyright                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                           |

(Article begins on next page)

# Influence of parasitic capacitance variations on 65 nm and 32 nm predictive technology model SRAM core-cells

Authors: Di Carlo S., Prinetto P., Savino A., Scionti A.,

Published in the Proceedings of the IEEE 17th Asian Test Symposium (ATS), 24-27 Nov. 2008, Sapporo, JP.

N.B. This is a copy of the ACCEPTED version of the manuscript. The final PUBLISHED manuscript is available on IEEE Xplore®:

URL: <a href="http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=4711625">http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=4711625</a>

DOI: 10.1109/ATS.2008.13

© 2000 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

## Influence of Parasitic Capacitance Variations on 65 nm and 32 nm Predictive Technology Model SRAM Core-Cells

Alberto Scionti, Alessandro Savino, Stefano Di Carlo, Paolo Prinetto

\*Politecnico di Torino\*

\*Dipartimento di Automatica e Informatica

\*Torino, Italy\*

Email: {alberto.scionti, alessandro.savino, stefano.dicarlo, paolo.prinetto }@polito.it

#### **Abstract**

The continuos improving of CMOS technology allows the realization of digital circuits and in particular Static Random Access Memories that, compared with previous technologies, contain an impressive number of transistors. The use of new production processes introduces a set of parasitic effects that gain more and more importance with the scaling down of the technology. In particular, even small variations of parasitic capacitances in CMOS devices are expected to become an additional source of fective behaviors in future technologies. This paper analyzes and compares the effect of parasitic capacitance variations in a SRAM memory circuit realized with 65 nm and 32 nm predictive technology models.

#### 1. Introduction

Semiconductor memories are the predominant majority of semiconductor devices production. The Semiconductor Industry Association (SIA) forecasts that in the next 15 years up to 95% of the entire chip area will be used create memory blocks. Memories will therefore represent one of the most critical elements to guarantee the success of next generation digital devices [1].

Memories have been used for a long time to push the state-of-the-art in the semiconductor industry. While new technologies allow a significant improvement in terms of performance and capacity, the continuous scaling and the high integration density make memories highly sensitive to physical defects and process variations. Precise fault modeling and efficient test design are therefore mandatory to guarantee high quality products.

Memory testing is historically based on the definition of Functional Fault Models (FFM) together with

very efficient test algorithms such as march tests [2]. Functional fault models are independent of the specific memory technology and allow the definition of test sequences not tight to a specific architecture. Several publications propose an extensive set of memory fault models together with the corresponding march tests for their detection. Classical fault models include static faults, i.e., faults that require a single memory operation to be sensitized [3], [4], [5], [6], [7] as well as more complex dynamic faults, i.e., faults that require more than one memory operation to be sensitized [5], [8]. Dynamic faults are one of the main manifestations of the negative effects Very Deep Sub Micron (VDSM) technologies have on memory devices. Their complexity strongly reduces the efficiency of traditional test algorithms requiring complex at-speed test sequences to be detected.

Recent publications analyzing the effect of VDSM technologies on memory devices, mainly focused on studying the effect of resistive defects in static random access memories by injecting these defects into an electrical model of the memory, and by performing electrical simulations [9], [10], [11], [12], [13], [14], [15], [16], [6]. Nevertheless, recent works also show that, as the device size is down-scaled into nanometer range, the transistor characteristics are liable to various changes due to shift of underlying device physics and in particular new parasitic capacitances become increasingly serious [17], [18], [19].

This paper analyzes the influence of parasitic capacitance variations on 6-transistors SRAM memory cells implemented using VDSM technologies. In particular, the paper proposes a comparative analysis among two memory technologies with feature sizes of 65 nm and 32 nm respectively. The analysis is performed by considering different defect locations, and defect sizes. The fault analysis is based on a set of SPICE simulations of a defective memory model with the support

of an automatic fault model extraction algorithm for an efficient exploration of the space of possible faulty behaviors. Experimental results show that capacitive defects may introduce dynamic faulty behaviors that need to be considered and tested in future memory devices.

The paper is organized as follows: Section 2 details the main characteristics of the proposed experimental design while Section 3 proposes a preliminary defect analysis on the memory behavior in terms of identified faulty behaviors and relationship with the technology process used to build the memory. Finally Section 4 summarizes the main contributions of the work and concludes the paper.

#### 2. Experimental design

This section introduces the characteristics of the proposed experimental design.

The core of the experiment is a set of electrical simulations performed on a SPICE model of a Static Random Access Memory (SRAM) block. Our reference architecture includes a cell array organized as a 512x512 matrix including, the pre-charge circuits for bit and word lines, the sense amplifier the write circuitry, and the address decoder in order to keep the simulation time into a real pable level, due to the amount of required simulations, we considered a simplified memory architecture including a limited number of memory cells.

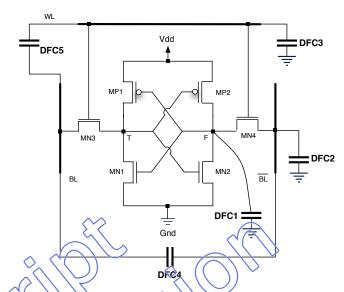

Figure 1 shows the architecture of a core memory cell realized with a standard transistors structure. Figure 1 also includes a set of five candidate defect locations considered during the fault analysis. The proposed analysis is limited to single defects only, not considering the effect of multiple defects.

The set of proposed defects does not include all possible locations. The number of candidate locations has been recently by considering the internal circuit symmetry. In particular, we considered the right part of the circuit for defects  $DFC_1$  and  $DFC_2$ , the left part of the circuit for defect  $DFC_5$ , while defects  $DFC_3$  and  $DFC_4$  are not asymmetric.

The defects introduced in Figure 1 try to model a set of physical parasitic effects gaining importance with technology down scaling. Crystallographic defects in the interface between the oxide layer and the substrate of a mosfet transistor may produce an electron trap effect that acts as a capacitance, which can be modeled as an alteration of the capacitive load of the transistor. This effect leads to an alteration of the capacitive load of the CMOS inverter in the self refreshment loop of the memory cell (see Figure 1) identified

Figure 3. 6 transistors memory cell with candidate defects

by  $DFC_1$ . The capacitive parasitic effects due to the metallization substrate coupling and the capacitive coupling between two lines are also additional sources of defects. They are modeled by defects  $DFC_2$ ,  $DFC_3$ ,  $DFC_4$ , and  $DFC_5$ .

This paper analyzes and compares the effect of the proposed list of defects on SRAMs considering two different technologies from Predictive Technology Model [20], with transistor feature size of 65 nm and 32 nm respectively. To allow a correct comparison, all experiments have been performed in similar working conditions, i.e., same operational temperature 27° C, process type typical, and timing with a clock period of 1.5 ns (666MHz clock frequency). The only different parameter passing from one technology to the other one is the supply voltage that requires to be scaled to adapt the memory behavior to the specific technology. Table 1 summarizes the main parameters applied during simulations.

We considered defect values in the range of a few fF to hundreds of fF in order to extensively analyze the memory behavior and to obtain a clear view of the observed phenomena.

All the experiments have been conducted by running electrical simulations using HSPICE. In particular the main goal of the analysis is the identification of dynamic faulty behaviors caused by the insertion of the proposed defects.

From preliminary analyses and simulations, and looking at the results of previous studies on the effect of resistive defects in static random access memories [16] we observed that in many situations dynamic

Table 1. Experimental conditions

|                | 65 nm technology | 32 nm technology |

|----------------|------------------|------------------|

| Process corner | Typical          | Typical          |

| Supply voltage | 1.1 V            | 0.9 V            |

| Temperature    | 27° C            | 27° C            |

| Timing         | 1.5 ns           | 1.5 ns           |

| Mode           | Active           | Active           |

faults are generated in very specific conditions usually identified by a specific value (or a very thin interval of values) of the target defect representing a cut point between the fault free domain and the static faults domain. The experimental approach used during our analysis mainly focuses on the identification of this cut point, if present.

For each defect, to reduce the number of simulations to perform, we applied a binary search procedure. The analysis starts with two defect values, one big enough to generate a static faulty behavior, while the second one small enough to be not influent on the memory behavior. These two values represent the starting search space for the analysis.

With this initial range, we split the interval in two parts and we simulate the middle point analyzing the effect on the memory. We can first three situations:

- The middle point identifies a dynamic behavior. In this case we reached the cut point and the search is concluded;

- The middle point falls in the no fault domain. In this case we need to restrict the search space to the upper half of the initial range;

- The middle point falls in the static faults domain.

In this case we need to restrict the search to the lower half of the initial range.

This procedure is repeated until either we find the cut point i.e., we identify a dynamic behavior) or we reach a shar transition from the no fault domain to the static faults domain (i.e., the defect do not lead to a dynamic fault). Obviously once the cut point is identified, additional simulations around its value are performed to precisely characterize the behavior of the memory in this defect area.

Concerning the test sequences applied during the analysis, since we mainly focus on the identification of dynamic faulty behaviors in the memory, we look for activation sequences longer than one operation. Possibly, two, three or more operations should be analyzed. In this context exploring all possible activation sequences is unfeasible due to the extended search space and simulation time. We thus resorted to an automation algorithm able to efficiently target those

sequences that most likely lead to faulty behaviors. This algorithm actually analyzes the simulation results of a good memory model and a faulty memory model and based on this comparison, and applying opportune heuristics, generates test sequences to simulate.

This automatic simulation approach allows us to explore a wider set of test sequences thus increasing the meaningfulness of the proposed analysis.

#### 3. Fault Analysis

This section analyzes the results obtained during the experiments proposed in Section 2.

Table 2 and Table 3 summarize the results obtained observing the simulations. For each table the first committeeports the target defect, the second column the echnology used to build the SRAM circuit, the third column the minimum defect value able to introduce the corresponding faulty behavior, while the last column shows the faulty behavior expressed in terms either of fault primitives or fault models.

All the identified faulty behaviors belong to the following functional faults categories:

- **Transition Faults (TFs):** a memory cell fails to perform an up transition  $(0 \rightarrow 1)$  or a down transition  $(1 \rightarrow 0)$  after a write operation;

- Incorrect Read Fault (IRF): a cell stores a correct logic value but the output read circuitry returns an incorrect value after a read operation;

- dynamic Transition Fault (dTF): a cell is unable to perform an up/down transition after a write operation which immediately follows another operation on the same cell (i.e., read or write operation).

Moreover, by observing the results of Table 2 we had the confirmation that for this technology the range of values that lead to dynamic faulty behaviors is actually reduced to a single cut point.

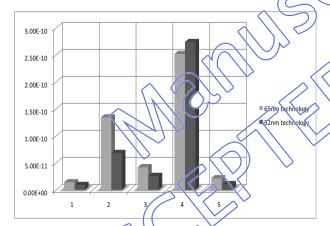

Figure 4 summarizes the sensitivity of the memory to the target defects based on the technology. It shows, for each defect, the minimum value required to introduce a faulty behavior.

As expected 32 nm technology is more sensitive to parasitic capacitance variations. In general, with 32 nm technology, faulty behaviors arise with a smaller defect value w.r.t. 65 nm technology. The only exception concerns DFC<sub>4</sub>. For this defect 65 nm technology becomes more sensitive even if the experimental data show that the faulty behavior emerge only for a defect size of the order of a hundred fF.

This behavior is connected with the reduced ability of the  $65\,\mathrm{nm}$  memory to work at high frequencies, and to the relative bigger size of the  $65\,\mathrm{nm}$  cell w.r.t. the

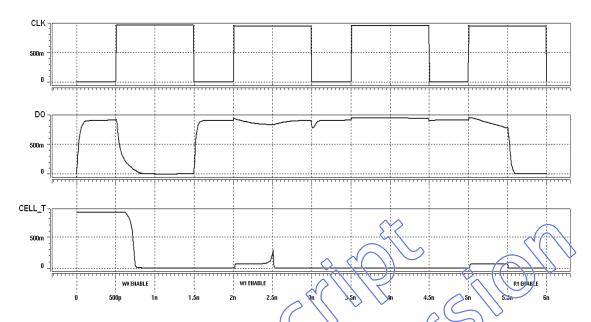

Figure 2. Dynamic faulty behavior for DFC2 in the 32 nm technology based memory

32 nm one. Moreover we have to remark that each technology uses a different supply voltage that may contribute to this result.

Table 2. Dynamic fault behaviors

|         | \               |                  | $-\langle \wedge \rangle$                    |

|---------|-----------------|------------------|----------------------------------------------|

| #DFC    | Technology      | Min. defect size | Fault primitive                              |

| $DFC_1$ | 65 nm           | 14.20 fF         | $\langle 1w_0w_1/0/2\rangle$                 |

|         | 32 nm           | - (( )           | <u> </u>                                     |

| $DFC_2$ | 65 nm           | - /              | >                                            |

|         | 32 nm           | 68.40 fF         | $\langle 1w_0w_1/0/- \rangle$                |

| $DFC_3$ | 65 nm           | >//              | -                                            |

|         | 32 nm           | -                | -                                            |

| $DFC_4$ | 65 nm           | 252,00 fF        | $\langle 0 \text{ Any } w_1 / 0 / - \rangle$ |

|         | $32\mathrm{nm}$ | 274.00 fF        | $\langle 0 \text{ Any } w_1 / 0 / - \rangle$ |

| $DFC_5$ | 65 n            | 21.68 fF         | $\langle 1 \text{ Any } w_0 / 1 / - \rangle$ |

|         | 32 nm           | -                | -                                            |

| -       |                 |                  |                                              |

Looking into more details at the causes of the different faulty behaviors,  $DFC_1$  introduces a transition fault in the cell. The capacitive parasitic effect introduces a delay in the propagation of the signal from the output of the inverter 2 (i.e., the inverter composed of MN2 and MP2 transistors) and the input of inverter 1 (i.e., the inverter composed of MN1 and MP1 transistors). The inverter 1 does not have enough time to reach the correct threshold for the cell switching. Depending on the technology, the defect may lead to a simple static fault or to a more complex dynamic faulty behavior.

Table 3. Static faulty behaviors

| #DFC    | Technology | Min. defect size    | Fault type |

|---------|------------|---------------------|------------|

| $DFC_1$ | 65 nm      | 14.21 fF            | TF         |

|         | 32 nm (\   | $9.30\mathrm{fF}$   | TF         |

| $DFC_2$ | 65 mm      | 134.34 fF           | TF         |

|         | 32 nm      | 68.41 fF            | TF         |

| $DFC_3$ | 65 nm      | 42.08 fF            | TF         |

|         | 32 mm      | $25.93\mathrm{fF}$  | TF         |

| $DFC_4$ | 65 nm      | $252.10\mathrm{fF}$ | TF         |

|         | 32 nm      | $274.10\mathrm{fF}$ | TF         |

| $DFC_5$ | 65 nm      | 21.69 fF            | TF         |

|         | 32 nm      | 10.70 fF            | IRF        |

$DFC_2$  introduces an alteration of the parasitic capacitance associated to the metallization of  $\overline{BL}$ . This type of alteration induces an extra amount of charges in the bit line capacitance which is not completely discharged during the fault sensitizing operations (see Figure 2). This defect leads to a dynamic faulty behavior in the  $32\,\mathrm{nm}$  cell, while in  $65\,\mathrm{nm}$  memory the behavior is static.

Defect  $DFC_3$  is connected to a capacitive coupling between the polysilicon word line and the substrate of the cell that produces a delay in the word line activation signals (i.e. MN3 and MN4). This defect always leads to a static fault both in  $32 \, \mathrm{nm}$  and  $65 \, \mathrm{nm}$  technology.

Finally  $DFC_4$  and  $DFC_5$  are coupling effects be-

tween the two bit lines, and between the bit line BL and the word line WL, respectively. It is interesting to note that in both cases the faulty behavior can be ascribed to the crosstalk effect between the two involved lines. In particular in case of  $DFC_5$  there is a signal transfer between the word line and the bit line, even if the cell continues to store the correct logic value.

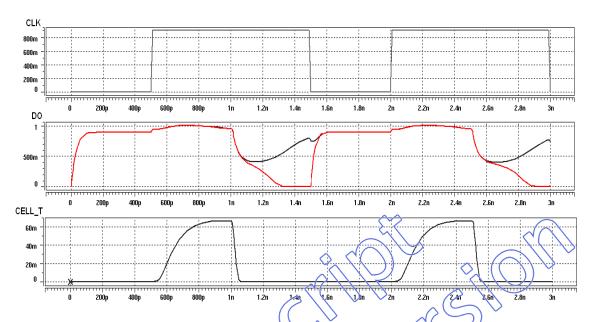

One interesting phenomena we observed during our experiments is that, by repeating the same experiments several times, we obtained small variations in the simulations results (especially when working with 32 nm technology). Figure 3 shows an example of this situation. The 32 nm based core cell continues to store the correct value even if the output signal shows two different behaviors. In the first case (i.e., the dark line), the output signal tries to drop down but after 0.2 ns it is forced again to an high value, while in the second case (i.e., the red line) the output signal reaches the 0 V value after 0.31 ns. This confirms the high sensitivity to this type of defects.

Figure 4. Graphic expression of the minimal capacitive value that produce a fault behavior

#### 4. Conclusion

This paper proposed a preliminary analysis on the influence of parasitic capacitance variations on 6-transistors SRAM memory cells implemented using VDSM technologies. In particular, the paper proposes a comparative analysis among two memory technologies with feature sizes of 65 nm and 32 nm respectively. The analysis is performed by considering different defect locations, and defect sizes.

The experimental results show that for some defect locations the technology downscaling increases the probability of faulty behaviors connected to these physical defects. Moreover for some conditions these faulty behaviors can be classified as dynamic faults, thus requiring more complex test sequences to be detected.

A more complete and extensive analysis of the effects of these defects on different memory architecture is under development to better understand the test requirements of future memory technologies.

#### References

- [1] International technology roadmap for semiconductors. [Online]. Available: http://www.itrs.net/

- [2] A. J. van de Goor, Testing Semiconductor Memories: theory and practice. John Wiley and Sons, Inc, September 1991

- 43 R. Dekker, F. Beenker, and J. Thijssen, Fault modeling and test algorithm development for static random access memories," in *IEEE International Test Conference (ITC* 1988), September, 12 4 1988, pp. 343–352.

- [4] A. J. van be Goor, "Using march tests to test srams," *IEEE Des Vest. Comput.*, vol. 10, no. 1, pp. 8–14, Mar. 2004.

- faults: A formal notation and a taxonomy," in *Proc.* 18th IEEE VLSI Test Symposium (VTS'00), Montreal, Canada, Apr.30-May3, 2000, pp. 281–289.

- [6] S. Hamdioui, Z. Al-Ars, and A. van de Goor, "Opens and delay faults in cmos ram address decoders," *IEEE Trans. Comput.*, vol. 55, no. 12, pp. 1630–1639, Dec 2606.

- [7] S. Hamdioui, Z. Al-Ars, A. van de Goor, and M. Rodgers, "Linked faults in random access memories: concept, fault models, test algorithms, and industrial results," *IEEE J. Technol. Comput. Aided Design*, vol. 23, no. 5, pp. 737–757, May 2004.

- [8] S. Hamdioui, Z. Al-Ars, and A. van de Goor, "Testing static and dynamic faults in random access memories," in *Proceedings 20th IEEE VLSI Test Symposium*, 2002. (VTS 2002)., 2002.

- [9] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, and M. Bastian Hage-Hassan, "Resistive-open defect influence in sram pre-charge circuits: analysis and characterization," in *IEEE European Test Symposium* (ETS 2005), I. Press, Ed., May, 22-25 2005, pp. 116– 121.

- [10] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, and M. Bastian, "March pre: an efficient test for resistive-open defects in the sram pre-charge circuit," in *IEEE Design and Diagnostics of Electronic Circuits* and systems, I. Press, Ed., April, 18–21 2006, pp. 254– 259.

Figure 3. Simulation of the output signal in the 32 nm core cell based with the DFC<sub>5</sub> with two different behaviors

- [11] L. Dilillo, P. Girard, S. Pravossondovitch, A. irazel, and S. Borri, "Comparison of open and resistive-open defect test conditions in sram address decoders," in 12th IEEE Asian Test Symposium (AS 2903), I. Press, Ed., November 16–9 2003, pp. 250–255.

- [12] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, S. Borri, and M. Hage-Hassan, "Resistive open defects in embedded-sram core cells: analysis and march test solution," in *IEEE 13th Asign Test Symposium (ATS 2004)*, November 15–17 2004, pp. 266–271.

- [13] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, and S. Borri, March ic-: an improved version of march c- for anofs detection, in 22nd IEEE VLSI Test Symposium (VTS 2007), I. Press, Ed., April, 25–29 2004, pp. 129–134.

- [14] L. Dilill, P. Girard, S. Pravossoudovitch, A. Virazel, and M. Hage-Hassan, "Data retention fault in sram memories: analysis and detection procedures," in 23rd IEEE VLSI Test Symposium (VTS 2005), May, 1–5 2005, pp. 183–188.

- [15] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, S. Borri, and M. Hage-Hassan, "Dynamic read destructive fault in embedded-srams: analysis and march test solution," in *Ninth IEEE European Test Symposium* (ETS 2004), I. Press, Ed., May, 23–26 2004, pp. 140– 145.

- [16] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, and M. Bastian, "Resistive-open defect injection in sram core-cell: analysis and comparison between 0.13μm and 90nm technologies," in *Proceedings 42nd*

- Design Automation Conference, DAC'05, IEEE/ACM, Ed., 2005.

- [17] K. Natori, "Prospective characteristics of nanoscale mosfets," in 8th International Conference on Solid-State and Integrated Circuit Technology, 2006. ICSICT '06., Oct. 2006, pp. 47–50.

- [18] S. Handioui Z. Al-Ars, G. Gaydadjiev, and A. van de Goor, "An investigation on capacitive coupling in ram address decoders," in 2nd International Design and Test Workshop, 2007, 16-18 Dec. 2007, pp. 9–14.

- S. Kundu, S. Sengupta, and R. Galivanche, "Test challenges in nanometer technologies," in *Proceedings. IEEE European Test Workshop*, 2000., 2000, pp. 83–90.

- [20] P. T. M. (PTM). http://www.eas.asu.edu/ ptm.