### POLITECNICO DI TORINO Repository ISTITUZIONALE

### Design of Analog Integrated Circuits Immune to RFI

| Original Design of Analog Integrated Circuits Immune to RFI / Crovetti, Paolo Stefano (2004).                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/1513633 since: Publisher:                                                             |

| Published<br>DOI:                                                                                                                       |

| Terms of use:                                                                                                                           |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright thesis                                                                                                              |

| Da definire                                                                                                                             |

|                                                                                                                                         |

|                                                                                                                                         |

(Article begins on next page)

## POLITECNICO DI TORINO

### SCUOLA DI DOTTORATO Dottorato in Ing. Elettronica e delle Comunicazioni – XVI ciclo

### Tesi di Dottorato

## Design of Analog Integrated Circuits Robust to RF Interference

#### Paolo Stefano Crovetti

Tutore prof. Vincenzo Pozzolo

Coordinatore del corso di dottorato prof. Ivo Montrosset

Febbraio 2004

Έὰν μὴ ἔλπηται, ἀνέλπιστον οὐκ ἐξευρήσει Ἡράκλειτος

## Summary

This work is aimed to provide analysis tools and criteria which can be employed in the design of analog integrated circuits robust to Electromagnetic Interference (EMI). To this purpose, the nonlinear effects which are induced by EMI in the operation of analog circuits are investigated and related to design parameters and parasitic elements.

In particular, the effects of Radio-Frequency interference (RFI) which is superimposed onto the input voltages and/or onto the power supply rails of opamp-based analog circuits are considered. To this purpose, a two-input Volterra series model, which is suitable to the prediction of distortion induced by RFI superimposed onto the input terminals of opamp-based circuit, and a three-input Volterra series model, which is suitable to the prediction of the effects of RFI superimposed both onto the opamp input voltages and onto the power supply rails, are proposed. Furthermore, a numerical large-signal model which has been proposed in the literature by Fiori is extended in order to provide closed-form prediction of the RFI-induced phenomena in opamp circuits under large-signal EMI excitation.

On the basis of these analysis tools, the relation between opamp configuration, opamp parameters, parasitic elements and susceptibility to EMI is highlighted and the main issues in the design of opamp circuits robust to EMI are discussed. Moreover, an opamp input stage which is intrinsically robust to EMI is presented and its operation principle is discussed on the basis of the models of RFI-induced distortion phenomena in opamp circuits which have been proposed.

## Acknowledgments

A special thank to Franco Fiori, both for his valuable contribution to the research activities which have been carried out within the Microelectronics EMC Group during my PhD course and for his constant advice and support.

I would also thank all the colleagues and friends of the Politecnico di Torino and, in particular, of the Microelectronics EMC Group, who shared with me both the delights and the troubles of the last three years.

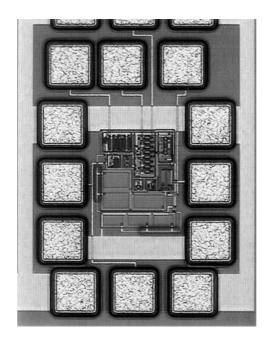

Finally, I would acknowledge the support of STMicroelectronics (Castelletto Site), which has made possible the physical realization of the integrated circuits presented in this work.

# Table of contents

| $\mathbf{S}\iota$ | Summary                                                   |         |                                                   |    |  |  |  |

|-------------------|-----------------------------------------------------------|---------|---------------------------------------------------|----|--|--|--|

| A                 | cknov                                                     | wledgm  | nents                                             | V  |  |  |  |

| 1                 | Introduction                                              |         |                                                   |    |  |  |  |

|                   | 1.1                                                       | RFI in  | Analog Integrated Circuits                        | 2  |  |  |  |

|                   | 1.2                                                       |         |                                                   |    |  |  |  |

| <b>2</b>          | Non                                                       | llinear | Effects of RFI in Analog Integrated Circuits      | 11 |  |  |  |

|                   | 2.1                                                       | Suscep  | tibility to RFI and Harmonic Distortion           | 12 |  |  |  |

|                   |                                                           | 2.1.1   | Classification and Effects of Harmonic Distortion | 13 |  |  |  |

|                   | 2.2                                                       | Nonlin  | near Circuit Analysis                             | 16 |  |  |  |

|                   |                                                           | 2.2.1   | Time-Domain Nonlinear Analysis Techniques         | 16 |  |  |  |

|                   |                                                           | 2.2.2   | Frequency-Domain Steady-State Techniques          | 19 |  |  |  |

| 3                 | Prediction of Operational Amplifier Susceptibility to RFI |         |                                                   |    |  |  |  |

|                   | 3.1                                                       | Nonlin  | near Effects of RF Interference in Opamps         | 28 |  |  |  |

|                   |                                                           | 3.1.1   | Signal Propagation within Operational Amplifiers  | 28 |  |  |  |

|                   |                                                           | 3.1.2   | An RFI-Oriented Opamp Circuit Model               | 30 |  |  |  |

|                   |                                                           | 3.1.3   | Differential Pair Nonlinear Operation             | 32 |  |  |  |

|                   |                                                           | 3.1.4   | Physical Origin of Differential Pair Parasitics   | 34 |  |  |  |

|                   | 3.2                                                       | A Two   | p-Input Volterra Series Opamp Model               | 39 |  |  |  |

|                   |                                                           | 3.2.1   | Two-Input Volterra Series Model Derivation        | 39 |  |  |  |

|                   |                                                           | 3.2.2   | Prediction of RFI-Induced Offset Voltage          | 46 |  |  |  |

|                   |                                                           | 3.2.3   | Model Validation                                  | 48 |  |  |  |

|                   |                                                           | 3.2.4   | Conclusions                                       | 55 |  |  |  |

|                   | 3.3                                                       | A Thr   | ee-Input Volterra Series Opamp Model              | 56 |  |  |  |

|                   |                                                           | 3.3.1   | Effects of EMI on the Opamp Power Supply Rails    | 56 |  |  |  |

|                   |                                                           | 3.3.2   | Model Derivation                                  | 57 |  |  |  |

|                   |                                                           | 3.3.3   | Demodulation of RFI in Feedback Opamps            | 65 |  |  |  |

|                   |                                                           | 3.3.4   | Model Validation                                  | 68 |  |  |  |

|              | 3.4            | 3.3.5<br>Large-S<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6 | Conclusions                                           |  | 78<br>79<br>82<br>86<br>88<br>89 |  |  |  |

|--------------|----------------|------------------------------------------------------------------------|-------------------------------------------------------|--|----------------------------------|--|--|--|

| 4            | EMI            | EMI-Aware Operational Amplifier Circuit Design 101                     |                                                       |  |                                  |  |  |  |

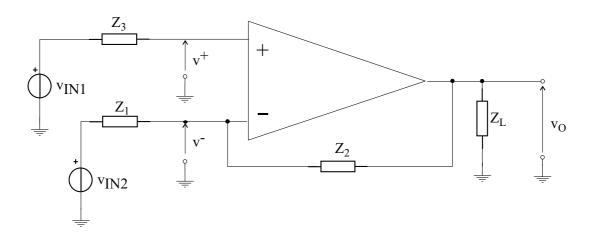

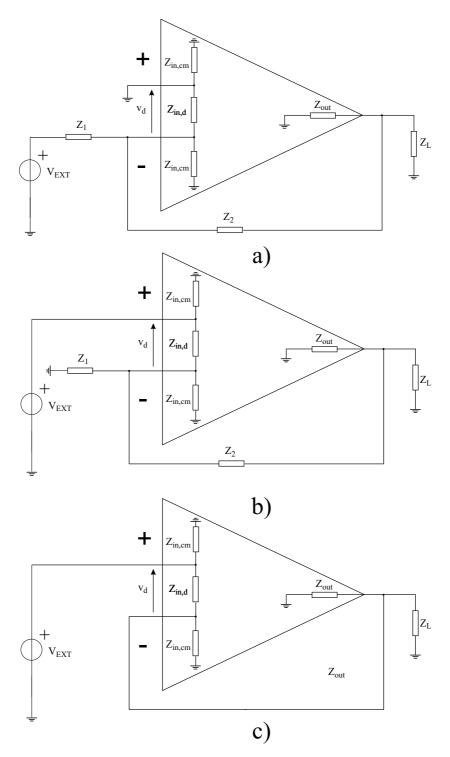

|              | 4.1            |                                                                        | Feedback Opamp Circuits                               |  | 102                              |  |  |  |

|              |                | 4.1.1                                                                  | Input-Referred RFI-Induced Distortion                 |  |                                  |  |  |  |

|              |                | 4.1.2                                                                  | Comparison of Feedback Opamp Configurations           |  |                                  |  |  |  |

|              | 4.2            | High In                                                                | mmunity Opamp Design Criteria                         |  | 108                              |  |  |  |

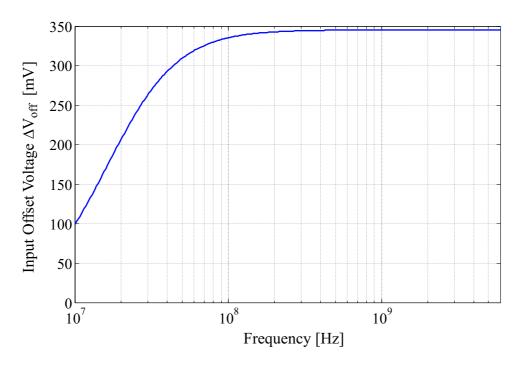

|              |                | 4.2.1                                                                  | Opamp Susceptibility Vs. CW RFI Amplitude             |  | 109                              |  |  |  |

|              |                | 4.2.2                                                                  | Opamp Susceptibility Vs. CW RFI Frequency             |  |                                  |  |  |  |

|              |                | 4.2.3                                                                  | Opamp Susceptibility Vs. Design Parameters and        |  |                                  |  |  |  |

|              |                |                                                                        | Parasitic Elements                                    |  | 113                              |  |  |  |

|              | 4.3            | High In                                                                | mmunity Opamp Design Tradeoffs                        |  |                                  |  |  |  |

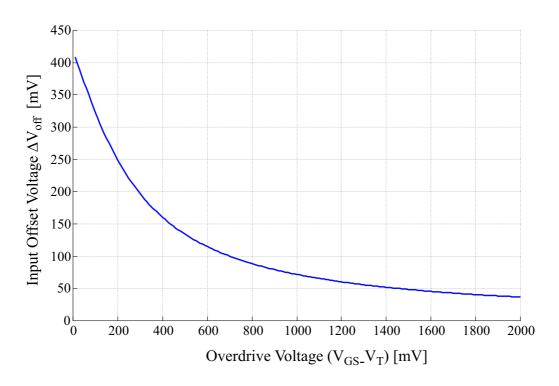

|              |                | 4.3.1                                                                  | Differential Pair Transconductance                    |  | 121                              |  |  |  |

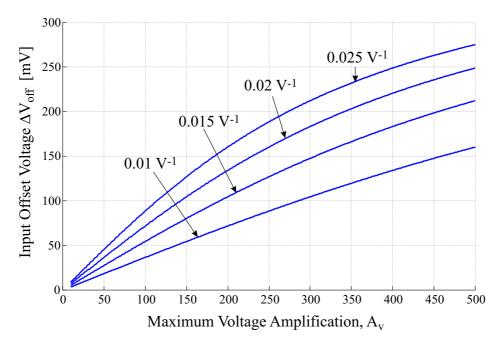

|              |                | 4.3.2                                                                  | Differential Pair Maximum Voltage Amplification       |  |                                  |  |  |  |

|              |                | 4.3.3                                                                  | Common-Mode Voltage Input Range                       |  |                                  |  |  |  |

|              |                | 4.3.4                                                                  | Static DC Offset Voltage                              |  |                                  |  |  |  |

|              |                | 4.3.5                                                                  | Slew Rate Limitation                                  |  |                                  |  |  |  |

|              |                | 4.3.6                                                                  | Opamp Bandwidth                                       |  |                                  |  |  |  |

|              |                | 4.3.7                                                                  | Conclusions                                           |  |                                  |  |  |  |

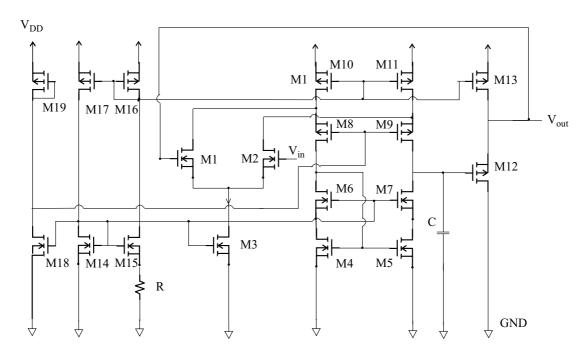

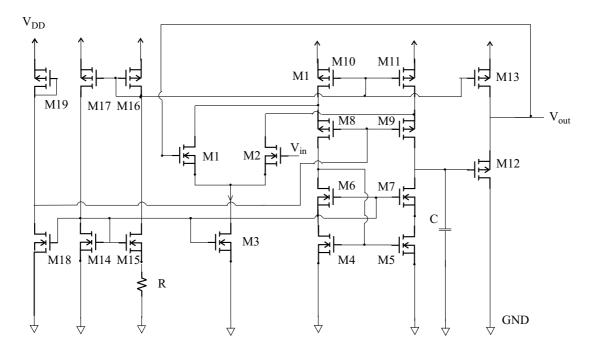

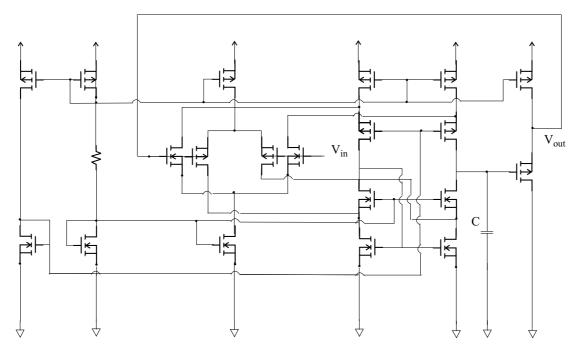

|              | 4.4            |                                                                        | amp Input Stage Robust to EMI                         |  |                                  |  |  |  |

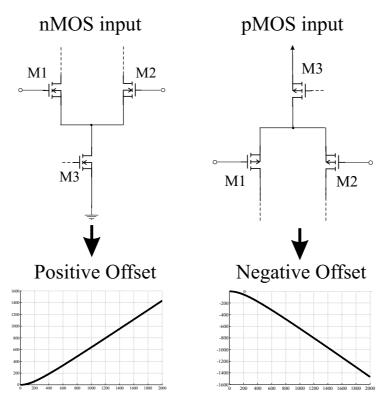

|              |                | 4.4.1                                                                  | Distortion Compensation                               |  |                                  |  |  |  |

|              |                | 4.4.2                                                                  | Complementary Differential Pair                       |  |                                  |  |  |  |

|              |                | 4.4.3<br>4.4.4                                                         | Complementary Differential Pair Susceptibility to EMI |  |                                  |  |  |  |

|              |                |                                                                        | Complementary Differential Pair Design                |  |                                  |  |  |  |

|              |                | 4.4.5 $4.4.6$                                                          | A High Immunity Operational Amplifier                 |  |                                  |  |  |  |

|              | 4.5            |                                                                        | ware Design of Analog Circuits                        |  |                                  |  |  |  |

| 5            | Cone           | clusion                                                                |                                                       |  | 147                              |  |  |  |

| o Conclusion |                |                                                                        |                                                       |  |                                  |  |  |  |

| Bi           | Bibliography 1 |                                                                        |                                                       |  |                                  |  |  |  |

## Chapter 1

## Introduction

The most recent achievements of silicon CMOS technology in terms of geometrical scaling and versatility have paved the way to the low cost integration of high performance electronic systems on a single chip (System on a Chip, SoC) and have brought about new challenges in present day microelectronic design.

The fully integration on a single chip of complex systems which include digital, analog, power and RF sections, however, requires a completely new approach in integrated circuit (IC) design [1, 2, 3, 4]. In fact, while traditional IC design is mainly addressed to the optimization in terms of performance of each single function, SoC design should be firstly aware of the overall system integration and of the final application environment. To this purpose, new requirements and new design tradeoffs arise.

The aspects related to chip-level Electromagnetic Compatibility (EMC) [5], i.e. with the adverse effects which may be induced by the unintentional generation, propagation and reception of electromagnetic energy within an integrated circuit, deserve a special attention in complex SoC design. These aspects cover both the adverse effects which are induced in IC operation by electromagnetic energy collected from the external environment (inter-EMC, susceptibility), the adverse effects which may by induced in the external environment by IC operation (inter-EMC, emission) and the adverse effects which are induced by IC operation in different sections within the same IC (intra-EMC).

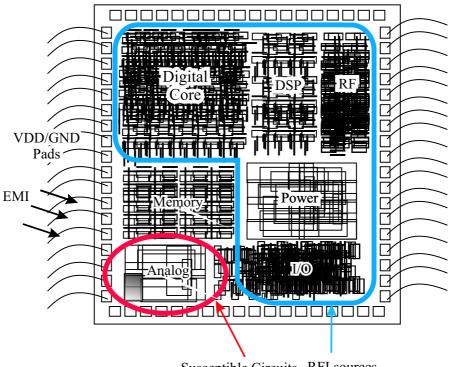

The susceptibility of IC cells to Radio-Frequency Interference (RFI), in particular, has proven to be among the major threats to SoC reliable operation in both intra-EMC and inter-EMC aspects. In fact, with reference to the typical SoC configuration shown in Fig.1.1, it can be observed that potential sources of interference as high-frequency synchronous digital circuits, RF power amplifiers and switching power supplies are located very close to susceptible circuitry and RF disturbances can easily couple with nominal signal paths through on-chip metal interconnections, I/O pads or via the silicon substrate.

Furthermore, due to the widespread diffusion of wireless integrated systems, which is fostered by the availability of low cost RF systems on silicon, the level of environmental electromagnetic pollution is always increasing. As a consequence, an always increasing level of Electromagnetic Interference (EMI) is collected by wiring structures (cables, PCB traces, bondwires, etc...) in electronic systems from the outside environment and it is translated into RF voltages and currents superimposed onto SoC nominal signals. For instance, an RF incident field with a frequency of 900MHz and a peak amplitude of 10V/m, which is a common value in the proximity of a cell phone antenna, can induce on a PCB trace of 10cm, which acts as an electrical dipole, an RF voltage as high as 1Vpk.

Finally, the threats related to the susceptibility to RFI become more and more severe in low voltage design. In fact, the reduction of IC power supply voltages which is imposed by geometrical scaling and by low power constraints makes the amplitude of RF interference very often comparable with the amplitude of ICs nominal signals or even larger, thus strongly reducing the Signal-to-Noise Ratio (SNR) within a chip.

In conclusion, in order to be suitable to present day SoC challenges, an IC must be designed to operate properly even in the presence of RF interference with a magnitude comparable with nominal signals. In this work, the fulfilment of this requirement with reference to analog ICs, which should provide accurate continuous time, continuous amplitude waveforms, is addressed.

### 1.1 RFI in Analog Integrated Circuits

Analog integrated circuits, in which the information is carried by continuous time, continuous amplitude voltage or current waveforms, have proven to be very susceptible to RFI. In fact, the RF disturbances which are superimposed onto nominal voltages and currents of an analog circuit are demodulated by the nonlinear characteristics of the active devices (MOS and BJT transistors) which are included in it, the demodulated RFI is added to the nominal output waveforms and their original information content is corrupted [6, 7, 8]. Demodulation of RFI is particularly hazardous because it converts out-of-band high frequency interference into in-band low frequency interference, which cannot be separated from nominal signals through linear filtering. In particular, in the presence of continuous wave (CW) RFI, the output voltage of analog circuits is affected by a DC offset.

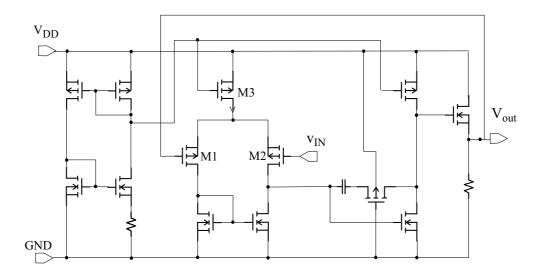

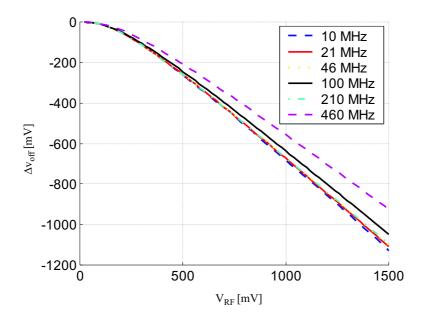

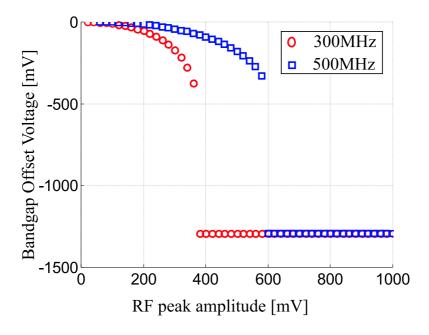

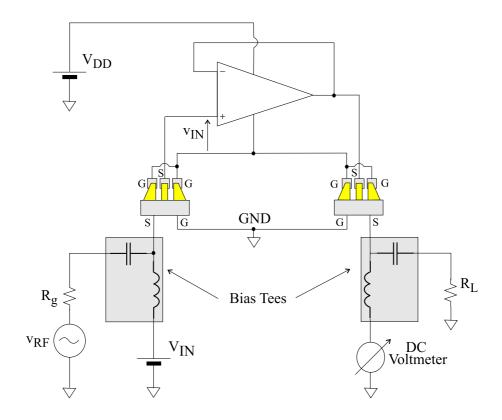

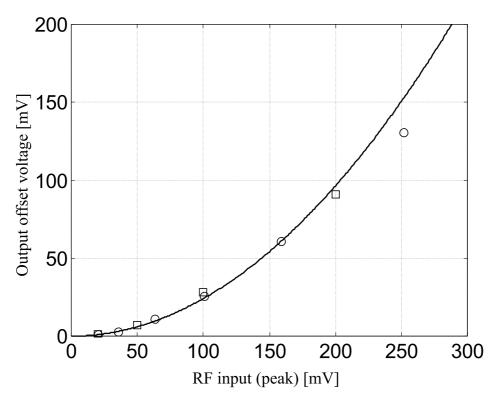

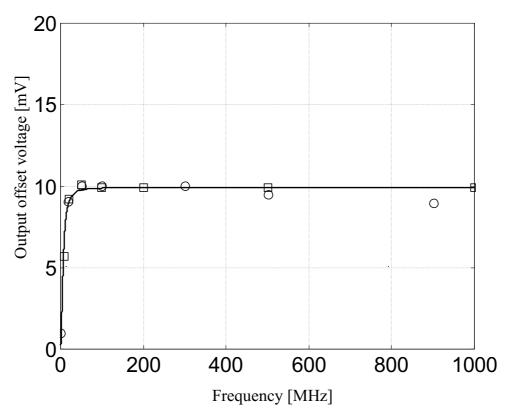

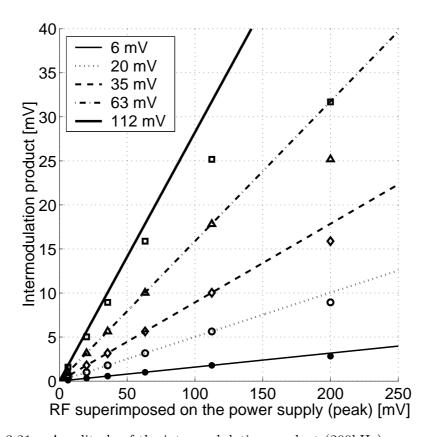

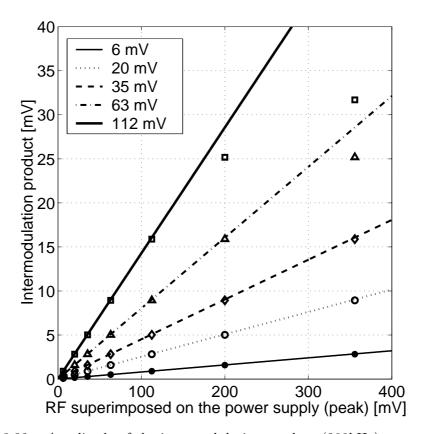

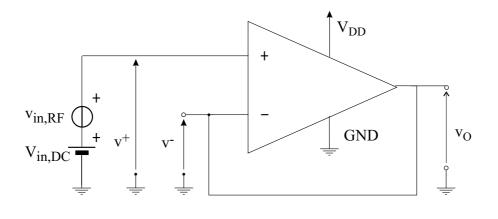

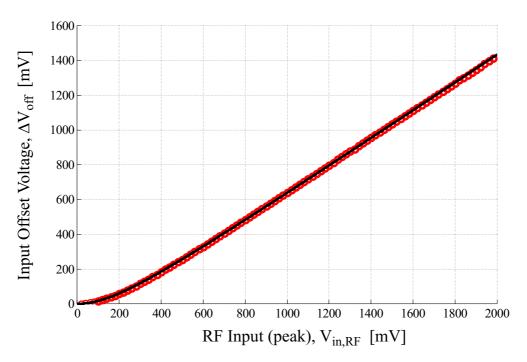

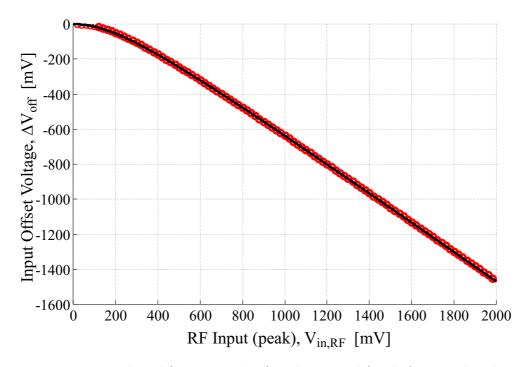

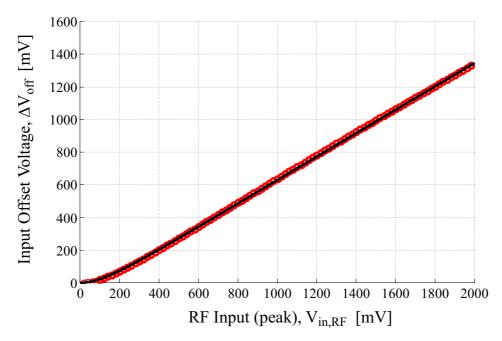

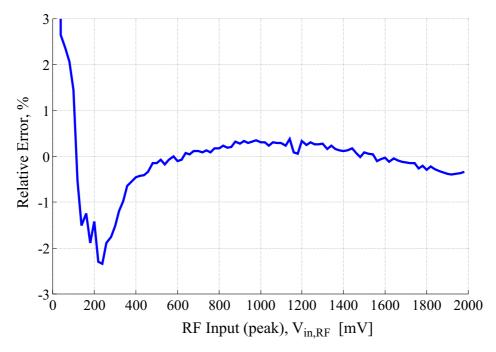

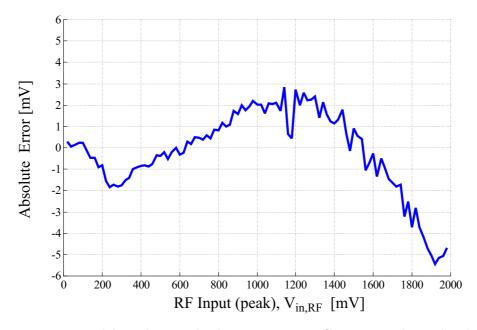

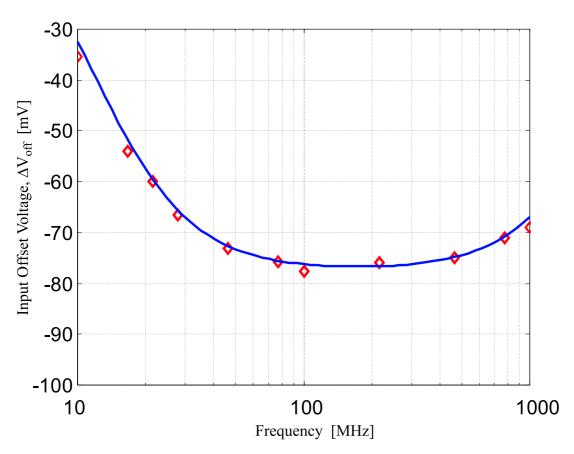

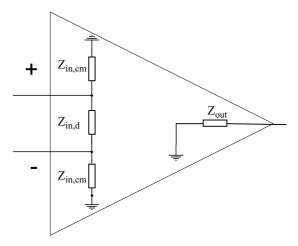

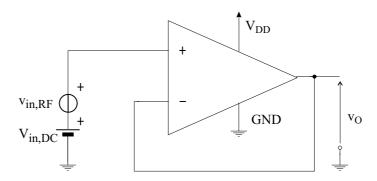

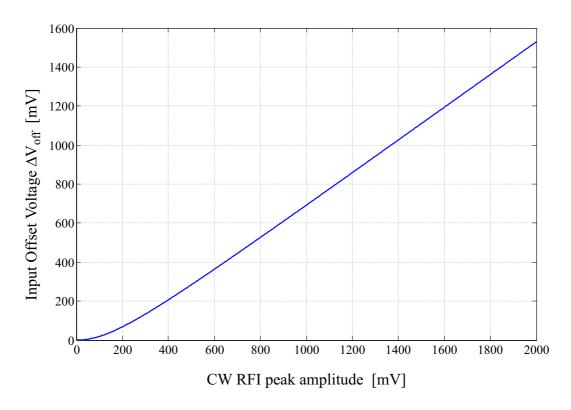

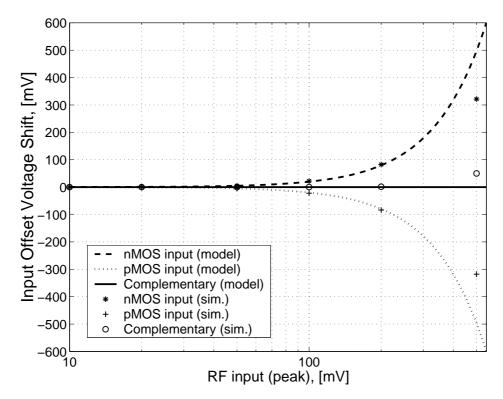

In standard analog circuits, the amount of in-band error which is due to the demodulation of out-of-band RFI is very often much higher than the nominal level of accuracy of these circuits. With reference to the widely employed CMOS Miller Opamp circuit connected in the voltage follower configuration shown in Fig.1.2, which operates from a 5V power supply, the amount of the measured RFI-induced DC offset voltage shift is plotted in Fig.1.3 versus the peak amplitude of CW RFI

superimposed onto the input voltage for different RFI frequencies. It can be observed that the RFI-induced offset voltage is comparable with the peak amplitude of CW RFI, therefore, even for relatively small levels of RFI (e.g. 10mVpk), the RFI-induced offset voltage is higher than the typical offset voltage due to transistor mismatch which is usually below 1mV for this circuit topology.

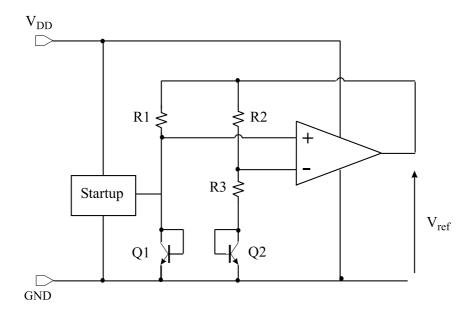

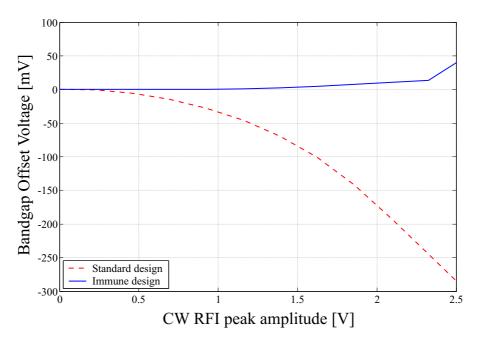

In Fig.1.4 the schematic of a Kujik bandgap voltage reference, which operates from a 5V power supply, is presented. This circuit, that is another widely employed analog building block, is designed to provide a very accurate temperature-independent voltage reference of about 1.2V. The required accuracy of the reference voltage over temperature is very often better than 1mV of residual thermal drift in a temperature range between  $-40^{\circ}$ C and  $+120^{\circ}$ C, i.e. few part per million per degree. In Fig.1.5 it can be observed how RFI can severely impair the performance of this circuit. In particular, it can be observed that CW RFI with a frequency of 300MHz and with a peak amplitude of about 10mV superimposed onto the power supply voltage of this circuit is sufficient to induce an error in the output voltage that is significatively higher than the required accuracy over temperature. Furthermore, it can be observed that a CW RFI with a peak amplitude of about 300mV is enough to induce a complete failure in the bandgap voltage reference operation.

The above examples show that analog integrated circuits can be particularly susceptible to RFI and their performance in terms of accuracy can be completely impaired by RFI with a relatively small peak amplitude. Because of the higher and higher degree of interdependence in complex integrated systems, a failure in analog circuit operations can induce an overall system failure which may be destructive. It follows that conventional analog cells are not suitable to present day SoC design and the analog IC design flow should be properly revised in order to achieve immunity to RFI.

## System on a Chip

Susceptible Circuits RFI sources

Figure 1.1. Sources of RFI in a present-day System on a Chip (SoC) typical architecture.

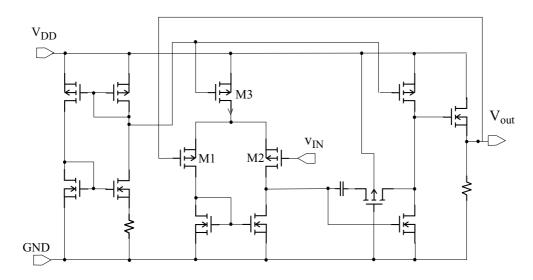

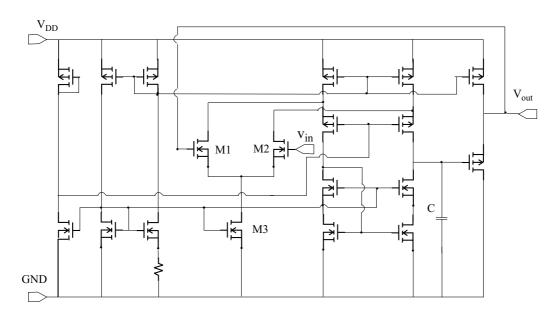

Figure 1.2. CMOS Miller Opamp.

Figure 1.3. CMOS Miller Opamp Susceptibility to EMI.

Figure 1.4. Kujik bandgap voltage reference.

Figure 1.5. Kujik bandgap voltage reference susceptibility to EMI.

### 1.2 RFI Aspects in Analog IC Design Flow

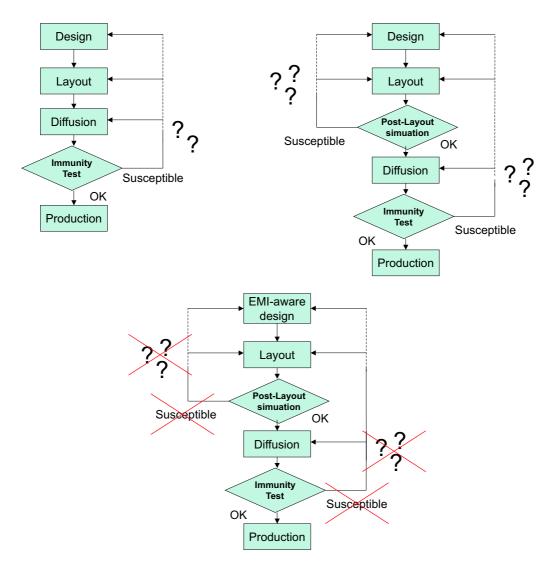

The susceptibility to RFI is not considered in a standard analog IC design flow. According to a standard design flow (Fig. 1.6a), in fact, an IC is first designed and simulated to achieve a target performance, then it is laid out in order to reduce the occupancy of silicon area and finally it is diffused on silicon. The aspects which are related to the susceptibility to RFI are only considered when the chip or, more often, the overall system in which it operates, fails either in EMI susceptibility compliance tests or in the field. At this point, the problem could only be addressed adding expensive external and/or on-chip shielding and filtering structures which may also adversely affect system performance.

In the last years, EMI immunity aspects have been taken into account earlier in the design flow by post-layout computer simulations which may predict the susceptibility to EMI of a chip before it is actually integrated on silicon (Fig. 1.6b). To this purpose, RFI-oriented models of nonlinear active devices [6, 7, 8], analog circuit macromodels [9, 10, 11, 12, 13, 14, 15, 16, 17, 18] and parasitic extraction tools [19] have been proposed in the literature and implemented in the last years.

These computer-aided techniques let to modify an analog IC design in the first stages in order to enhance its immunity to EMI, nonetheless, they do not provide any tool to design integrated circuits immune to EMI as they only provide information on the susceptibility of a particular design and do not give insight on the origin of the susceptibility to EMI which could be translated into design criteria to enhance the immunity of an analog IC.

In order to face the problems related to the susceptibility to EMI of analog circuits in an effective way, a new, EMI-susceptibility aware design flow is required (Fig. 1.6c). To this purpose, in particular, it is essential to know how the susceptibility to EMI is related to design parameters and parasitics. On the basis of this information, it is possible to take into account the immunity to EMI as an IC specification which can be traded off with other system requirements in the early stage of design.

An EMI-aware analog IC design requires some analysis and design tools: to this purpose, in particular, the behavior of analog integrated circuits in the presence of RF interference should be predicted by an analytical model, which relates in a simple way the susceptibility to RFI to design parameters and parasitic elements. The insight in the operation of analog IC in the presence of RFI which can be gained from such a model, in fact, can be exploited in order to derive design criteria to improve the immunity to RFI of standard analog cells and to design new high-immunity building blocks for specific analog functionalities.

Figure 1.6. RFI Aspects in Analog IC Design Flows.

This work is aimed to provide some of the tools which are required in the design of analog integrated circuits robust to EMI. In Chapter II, in particular, the aspects related to the nonlinear effects of RFI in analog ICs are generally considered and the main techniques which are employed in the analysis of nonlinear electronic circuits and systems are shortly revised in order to highlight the advantages and the drawbacks of these techniques in the investigation of the effects of EMI in analog circuits.

In Chapter III the analytical modelling of the susceptibility to EMI of operational amplifiers is dealt with. In particular, two Volterra series analytical models which are suitable to predict the behavior of integrated opamp circuits in the presence of RFI superimposed onto nominal signals and/or onto the power supply voltages are proposed and these models are validated by experimental tests. Furthermore, the numerical model which has been proposed by Fiori in [20] for the prediction of the RFI-induced offset voltage in opamp circuits under large-signal excitation is extended. In particular, a closed-form expression of the RFI-induced offset voltage is derived and the dependence on RFI frequency of the RFI-induced offset is highlighted.

In Chapter IV, the analytical tools which have been proposed are employed in order to derive design criteria to enhance the immunity to EMI of opamp circuits. To this purpose, the influence of the feedback configuration in the susceptibility to EMI of opamp circuits is discussed, the dependence of the intrinsic susceptibility to EMI of IC opamps on design parameters and parasitic elements is highlighted and the design tradeoffs which should be considered in order to enhance the immunity to EMI are discussed. Furthermore, in Chapter IV a new opamp topology which has been designed to achieve a high immunity to EMI is presented and its operation principle is discussed. Moreover, the extension of the high immunity design criteria, which have been proposed, to analog circuits and subsystems is considered.

Finally, in Chapter V, the main results which have been obtained in this research are summarized, the topics which deserve further investigations are focused and some concluding remarks are drawn.

## Chapter 2

# Nonlinear Effects of RFI in Analog Integrated Circuits

A good insight in the mechanisms, which are responsible of the EMI-induced failures in analog ICs, and the availability of analysis tools, which could effectively and efficiently predict the behavior of analog ICs in the presence of EMI, are key issues in EMI-aware analog circuit design.

The main task of EMI-aware analog circuit analysis, in particular, is to highlight how out-of-band interference affects the in-band operation of analog integrated circuits. To this purpose, it should be observed that linear time invariant (LTI) systems cannot transfer the power of their input signals from one region of the spectrum to another as, in the most general case, any output of a linear system is given by a complex, frequency-dependent, linear combination of the input signals. As a consequence, the adverse effects which are induced by RFI in analog IC operation are necessarily related to high-frequency nonlinear phenomena therefore, RFI-oriented analog circuit modelling requires a proper modelling of nonlinear phenomena.

This Chapter is aimed to provide the basic concepts of nonlinear circuit theory and the fundamental insight in nonlinear circuit analysis techniques which are suitable to the investigation of the nonlinear effects of RFI in analog integrated circuits. In particular, the potential advantages and limitations of each nonlinear analysis technique with reference to the above mentioned investigations will be highlighted.

The general concepts and results which are presented in this Chapter are derived from [21, 22, 23], where a comprehensive presentation of nonlinear circuit theory and analysis can be found.

### 2.1 Susceptibility to RFI and Harmonic Distortion

The phenomena which are responsible of the susceptibility to RFI of analog circuits are strictly related to harmonic distortion, i.e. with the parasitic nonlinear effects that occur in electronic circuits which are designed to be linear. The term harmonic distortion refers to the effect of nonlinearity in the frequency-domain analysis of dynamical systems: while in non-autonomous LTI systems the harmonic content of input signals is conserved (i.e., the spectrum of any output signal includes the same harmonic components included in the input signals and the LTI system only affects the amplitude and phase of each spectral component), nonlinear systems may generate spectral components which are not included in the input signals.

In particular the term harmonic distortion refers to the generation of distortion terms at frequencies which are expressed by an integer linear combination of the frequencies of input signals, i.e., if the input signals include harmonic components with frequencies  $\omega_1, \omega_2, \ldots, \omega_i$ , an output signal may include, in the most general case, spectral components at any frequency

$$\omega = k_1 \omega_1 + k_2 \omega_2 + \ldots + k_i \omega_i,$$

where  $k_1, \ldots, k_i \in \mathbf{Z}$ . Spectral components in which there is only one nonzero  $k_i$  coefficient are referred to as *harmonics* of the input signals, while spectral components in which there are two or more nonzero  $k_i$  coefficients are referred to as *intermodulation products*.

Nonlinear systems whose operation can be completely described in terms of harmonic distortion are referred to as weakly nonlinear systems, while the remaining nonlinear systems are referred to as strongly nonlinear systems. Strongly nonlinear systems, in particular, may show nonlinear phenomena as sub-harmonic generation, sensible dependence on initial conditions, multiple steady-state behavior and chaotic behavior [22]. In these systems, the output spectrum may include sub-harmonics (i.e. harmonics of fractional order) of the input signals or can be apparently not related to the input signal spectrum at all.

The nonlinear effects which are induced by RFI in analog integrated circuits can be usually considered as a perturbation from the nominal linear circuit operation, therefore they are conveniently described in terms of harmonic distortion. For this reason, harmonic distortion in weakly nonlinear systems will be considered hereafter.

#### 2.1.1 Classification and Effects of Harmonic Distortion

Harmonic distortion in systems which are designed to be linear is usually described in terms of the power series expansion of the static nonlinear characteristics which induce distortion:

$$f(x) = y_0 + \alpha_1 x + \alpha_2 x^2 + \alpha_3 x^3 + \dots$$

(2.1)

With reference to this expansion,  $y_0$  describes the output of the system if no input signal is applied (bias point term), the term  $\alpha_1 x$  describes the nominal linear operation of the system (linear term or small-signal term) while the terms  $\alpha_m x^m$  (m > 1) are referred to as m-th order distortion terms.

From (2.1), the generation of even-order or odd-order distortion terms can be directly related to the nonlinear characteristics and/or to the structure of a nonlinear system. In particular, it should be observed that a nonlinear characteristic which is an even function in the input signal, i.e.

$$f(x) = f(-x) \qquad \forall x,$$

may only generate even-order distortion terms, while a nonlinear characteristics which is an odd function of the input signals,

$$f(-x) = -f(x) \qquad \forall x$$

may only generate odd-order distortion. In particular, from the last condition, it can be derived that the output signal of fully balanced systems, i.e. systems whose output signal can be expressed as the difference between two identical functions of the input signal and its complement, i.e.

$$f(x) = g(x) - g(-x),$$

where g(x) is an arbitrary nonlinear function, do not generate even-order distortion as, in this special case f(x) is an odd function.

Furthermore, the concept of order of distortion is particularly expressive in the frequency domain analysis of weakly nonlinear system because it is closely related to the generation of harmonic content. In particular, it can be shown that if the input signals include harmonic components with frequencies  $\omega_1, \omega_2, \ldots, \omega_i$ , m-th order (m > 2) distortion generates spectral components with angular frequency

$$\omega = k_1 \omega_1 + k_2 \omega_2 + \ldots + k_i \omega_i,$$

with  $k_1, \ldots, k_i \in \mathbf{Z}$  and

$$\sum_{i=0}^{+\infty} |k_i| = m. \tag{2.2}$$

Moreover, the distinction between even-order and odd-order order distortion terms is particularly meaningful because these two kinds of distortion affect the operation of electronic circuits in different ways and, depending on the application, the effect of odd or even distortion can be either particularly harmful or negligible. It is well known in the literature [21], for instance, that odd order and especially third order distortion is particularly harmful in wide-band RF amplifiers, as this kind of distortion can mix the power of adjacent channels, while even-order distortion is a minor threat as it does not interfere with the operation of an RF amplifier in its nominal signal bandwidth.

On the basis of the above considerations, it is significative to highlight the different effects of even-order and odd-order distortion in the operation of baseband analog integrated circuits in the presence of RFI. To this purpose, the result of second-order and third-order distortion on a two-tone signal, which shows an inband signal component with frequency  $\omega_s$  and an out-of-band CW RFI component at frequency  $\omega_{RFI}$  is compared.

In this case, according with (2.2), second-order nonlinearity generates distortion terms at the following frequencies

$$\begin{aligned} &\omega_{RFI} - \omega_{RFI} = 0, \\ &\omega_{s} - \omega_{s} = 0, \\ &2\omega_{s}, \\ &2\omega_{RFI}, \\ &\omega_{RFI} - \omega_{s}, \\ &\omega_{RFI} + \omega_{s}, \end{aligned}$$

while third-order nonlinearity generates terms with frequency

$$\begin{split} &\omega_{\rm s} + \omega_{\rm RFI} - \omega_{\rm RFI} = \omega_{\rm s}, \\ &\omega_{\rm RFI} + \omega_{\rm s} - \omega_{\rm s} = \omega_{\rm RFI}, \\ &\omega_{\rm RFI} + 2\omega_{\rm s}, \\ &\omega_{\rm RFI} - 2\omega_{\rm s}, \\ &3\omega_{\rm RFI}, \\ &3\omega_{\rm s}. \end{split}$$

In particular, it can be observed that third order nonlinearity generates in-band contributions at frequency  $3\omega_s$  and  $\omega_s$ . The first term is related to the distortion of the in-band signal and it is not related to RFI, while the second term affects the linear in-band amplification and may induce either compression or expansion phenomena [21], i.e. a decrease or an increase in the nominal amplification (attenuation) of the baseband signal, which depends on the amplitude of RFI. This phenomenon is

not considered a major threat in baseband electronic circuit operation, because the RFI-induced fluctuations are usually very small if compared to the nominal value of nominal amplification (attenuation) parameters. Furthermore, electronic circuits are usually designed in order to be insensitive to the absolute values of amplification parameters of nonlinear devices.

Second-order nonlinearity, instead, generates an in-band distortion term with frequency  $2\omega_s$  and a DC term  $\omega_s - \omega_s = 0$ , which are not related to RFI, and a DC term ( $\omega_{RFI} - \omega_{RFI} = 0$ ), which depends on the presence of RFI. Most of the unwanted phenomena that are induced by RFI in analog circuits are related to this last term. An example of the effects of second order distortion is the RFI-offset voltage generation, which has been previously described with reference to Fig.1.3 and Fig.1.5. The same kind of distortion is also responsible of the demodulation of modulated RFI in analog integrated circuits.

The results which have been derived for second-order and third-order distortion can be generalized to even-order and odd-order distortion and let to conclude that inband operation of analog circuits is affected by out-of-band RF interference mainly because of the effects of even-order distortion. As a consequence, the analysis of the effects of RFI on analog ICs operation should be mainly focused on high-frequency even-order nonlinear effects. This consideration, in particular, will be exploited in the following Chapter in the derivation of simplified nonlinear circuit models which are customized to RFI susceptibility investigations.

### 2.2 Nonlinear Circuit Analysis

In the previous Section a qualitative description on the nature of the nonlinear phenomena which should be considered in the analysis of the susceptibility to EMI of analog ICs has been presented. In this Section, a review of the nonlinear circuit analysis techniques which can be employed to this purpose is provided and the advantages and limitations of each single technique are highlighted.

A nonlinear circuit analysis technique is any computer-aided or pen-and-paper technique which can express any electrical quantity y (voltage or current) of an electric network in terms of the values of its external excitations e and of the constitutive relations of the devices which are included in it.

From circuit theory, in particular, in any non-degenerated lumped parameter electric network, any electrical quantity (voltage or current) can be expressed as

$$y(t) = G(\mathbf{x}(t), \mathbf{e}(t)) \tag{2.3}$$

where  $\mathbf{x}(t)$  is the state vector which include capacitor voltages and inductor currents,  $\mathbf{e}(t)$  is the source vector which includes the voltage and current waveforms of independent voltage/current sources and  $G: \mathbf{R}^n \to \mathbf{R}$  is a generic function. Furthermore, the state vector  $\mathbf{x}(t)$  satisfies a system of nonlinear ordinary differential equations (ODEs):

$$\dot{\mathbf{x}}(t) = \mathbf{F}(\mathbf{x}(t), \mathbf{e}(t)) \tag{2.4}$$

where  $\mathbf{F}: \mathbf{R}^n \to \mathbf{R}^m$  is a generic vector function. Therefore, any output of an electric circuit can be obtained from (2.3)on the basis of the source vector  $\mathbf{e}(t)$  and of the initial state vector  $\mathbf{x}(0)$ .

The different approaches in nonlinear circuit analysis differ on the techniques which are employed in the solution of the nonlinear ODE (2.4). These techniques can be classified into *time-domain* and *frequency domain* or *steady-state* techniques and will be shortly presented in the following.

#### 2.2.1 Time-Domain Nonlinear Analysis Techniques

Time-domain nonlinear analysis techniques are based on the solution of (2.4) and (2.3) in the time domain. As there is no general expression for the solution of (2.4) when  $\mathbf{F}$  is a nonlinear function, such analysis can be performed either numerically by the discretization of (2.4) or by the piecewise linear approximation of  $\mathbf{F}$ . Both these techniques will be described in the following.

#### **Transient Simulation**

The most common approach in time-domain circuit analysis, which is employed in SPICE-like circuit simulation programs for transient analysis, is the numerical solution of the ODE (2.4) through time discretization. In particular, N time samples of the state and input variables are considered and the differential system (2.4) is transformed into a nonlinear algebraic system

$$\hat{F}_i(\mathbf{x}(T_0), \dots, \mathbf{x}(T_N), \mathbf{e}(T_0), \dots, \mathbf{e}(T_N)) = 0$$

$i = 1, \dots, N$  (2.5)

by approximating derivatives with finite increments. The resulting algebraic non-linear system, whose unknowns are the time samples  $\mathbf{x}(T_0), \dots, \mathbf{x}(T_N)$  of the state vector, is then solved by an iterative method (typically the Newton-Raphson method or its variants [24]).

Different ODE integration methods differ from the techniques which are employed in the sampling (fixed or variable step), in the discretization of the derivatives (one-step or multi-step methods, implicit or explicit methods) and in the iterative scheme which is employed to solve the nonlinear algebraic system. More details on the particular implementations can be found in [23, 24]. The choice of a particular numerical technique is related to the nonlinear circuit under consideration in order to achieve the best trade-off in terms of accuracy and efficiency. Most high-end circuit simulators provide a wide choice of integration algorithms which can be customized to the circuit under analysis [25, 26].

Time-domain transient simulation, if accurate models for active devices are available and if the values of the parasitic elements are properly extracted by post-layout back-annotation, provides probably the most accurate prediction of the dynamic behavior of any electronic circuit under any excitation and, in particular, it is suitable to analyze the effects of RFI on analog IC operation.

Nonetheless, this method is not efficient for RFI susceptibility analysis. In fact, when the effects of RF signals on baseband circuits are investigated, the largest sampling step in (2.5) should be much smaller than the frequency of RF signals (for a good accuracy, at least ten samples per period are required), while the overall simulation time should be much longer than the slowest time constant in the circuit, in order to reach the steady-state condition. For instance, if the effects of a 1GHz CW RF interference on a low frequency amplifier with a nominal bandwidth of 10 kHz is investigated, a simulation step of less than 100 ps and a simulation time of more than  $500 \mu \text{s}$  are required, as a consequence, more than five million samples are necessary and the simulation time can consequently be very long.

Furthermore, time-domain computer simulations do not provide a deep insight in the mechanisms which induce failures in analog IC operation: in particular, they do not relate the failures to particular circuit blocks nor they relate them to specific design parameters and parasitics. Therefore, time-domain computer simulation cannot be employed as a primary tool in the design of analog ICs immune to EMI, although they can are valuable both for the validation of simpler models and for post-design EMI immunity test on analog sub-systems.

#### Piecewise Linear Approximation

An approximated solution of circuit equations (2.3) and (2.4) can be obtained in the time domain by piecewise linear approximation of function  $\mathbf{F}$  in (2.4).

Employing this approach, the nonlinear system (2.4), can be written in the form

$$\dot{\mathbf{x}}(t) = \mathbf{A}_1 \mathbf{x}(t) + \mathbf{B}_1 \mathbf{e}(t) \quad \text{for} \quad \mathbf{x}(t), \mathbf{e}(t) \in S_1$$

$$\dot{\mathbf{x}}(t) = \mathbf{A}_2 \mathbf{x}(t) + \mathbf{B}_2 \mathbf{e}(t) \quad \text{for} \quad \mathbf{x}(t), \mathbf{e}(t) \in S_2$$

$$\vdots$$

$$\dot{\mathbf{x}}(t) = \mathbf{A}_N \mathbf{x}(t) + \mathbf{B}_N \mathbf{e}(t) \quad \text{for} \quad \mathbf{x}(t), \mathbf{e}(t) \in S_N$$

(2.6)

where  $S_1 ldots S_N \in \mathbf{R}^m$  is a partition of  $\mathbf{R}^m$ . In each region of the state and input space the system is described by an unique set of linear differential equations. The linear ODE corresponding to the region which includes the initial condition point  $\mathbf{x}(0), \mathbf{e}(0)$  is firstly solved, then, if the solution reaches the border of the definition region, the linear ODE which describes the circuit in this region is solved with the border point as initial condition. This procedure is repeated until the analysis time is elapsed and/or a steady-state (limit cycle) solution is obtained.

Although piecewise linear approximation techniques provide closed-form analytical expressions of the output signals of nonlinear circuits, these techniques are not particularly suitable to the analysis of the effects of EMI in analog circuits. In fact, the nonlinear characteristics of physical electronic devices employed in analog circuits are usually smooth in their nominal region of operation therefore an accurate piecewise linear approximation would require a very fine partition, which makes the analysis of these circuits impractical. Furthermore, it is rather difficult to extract analytically from the piecewise-defined output waveforms which are obtained by this technique the parameters which are employed to quantify the effects of EMI in analog circuits (i.e. offset voltage, intermodulation products, etc...) and consequently, the relation between EMI susceptibility and circuit parameters which could be obtained would be rather involved for design purposes.

#### 2.2.2 Frequency-Domain Steady-State Techniques

Frequency-domain analysis of analog circuits is very often much more expressive than the analysis of time-domain output waveforms. Frequency-domain analysis, in fact, is the natural tool for linear circuit analysis and highlights the most important features of electrical signals and systems. This consideration is valid, in particular, for the analysis of the effects of EMI. The concept of the influence of out-of-band disturbances in in-band circuit operation, for instance, refers to frequency domain analysis. For this reason, the techniques which provide results on the distortion of analog circuits directly in the frequency domain are particularly attractive.

Frequency-domain steady-state techniques are based on the assumption that both the input signals and the steady state output signals are periodic with the same fundamental frequency  $\omega_0$  and they can be conveniently described in terms of Fourier series expansion

$$x(t) = \sum_{n = -\infty}^{+\infty} X_n e^{jn\omega_0 t}$$

(2.7)

$$y(t) = \sum_{n=-\infty}^{+\infty} Y_n e^{jn\omega_0 t}.$$

(2.8)

This assumption makes these methods suitable to the analysis of harmonic distortion in weakly nonlinear systems while they may not be suitable to describe stronger nonlinear phenomena like chaos, in which non-periodic steady state behavior can be observed.

Rather than on the time-domain solution of the ODE (2.4), frequency domain methods are aimed to express the Fourier coefficients of the output signals  $Y_n$  in terms of the coefficients of the input signals  $X_n$  in an algebraic form. To this purpose, different techniques have been proposed in the literature, which can be suitable either for pen-and-paper or computer-aided analysis.

In the following, the Harmonic Balance, Volterra series and Describing Function methods are briefly discussed and, in particular, their suitability in RFI susceptibility design-oriented analysis is discussed.

#### Harmonic Balance

Harmonic Balance technique is a widely employed frequency domain analysis technique for computer-aided circuit simulation. According to Harmonic Balance technique, both the state vector  $\mathbf{x}(t)$  and the excitation vectors  $\mathbf{e}(t)$  are expanded in a truncated Fourier series where the first N harmonics of the fundamental frequency  $\omega_0$  are considered

$$\mathbf{x}(t) = \sum_{n=-N}^{+N} \mathbf{X}_n e^{jn\omega_0 t}$$

(2.9)

$$\mathbf{e}(t) = \sum_{n=-N}^{+N} \mathbf{E}_n e^{\mathrm{j}n\omega_0 t}.$$

(2.10)

The above expressions of  $\mathbf{e}(t)$  and  $\mathbf{x}(t)$  are substituted in (2.4), which becomes

$$\sum_{n=-N}^{+N} jn\omega_0 \mathbf{X}_n e^{jn\omega_0 t} - \mathbf{F} \left( \sum_{n=-N}^{+N} \mathbf{X}_n e^{jn\omega_0 t}, \sum_{n=-N}^{+N} \mathbf{E}_n e^{jn\omega_0 t} \right) = 0$$

(2.11)

Thanks to the Fourier representation, the derivative of the state vector is computed analytically and the ODE system (2.4) reduces to an algebraic relation between time domain waveform (2.11), where the unknowns are the Fourier series coefficients  $X_n$ .

Harmonic balance technique is aimed to find out a set X of coefficients  $X_n$  in terms of the set E of coefficients  $E_n$  which satisfy, i.e. "balance", Eqn. (2.11). In general, as the solution is not exactly represented by its truncated Fourier series representation, it is not possible to find out a set of coefficients which satisfy (2.11) exactly. Nonetheless, it is possible to find out the set of coefficients which provide the best truncated Fourier series approximation of the solution. To this purpose, as Eqn. (2.11) is in the form

$$\tilde{\mathbf{F}}(\mathbf{X}, \mathbf{E}, t) = 0 \tag{2.12}$$

and  $\tilde{\mathbf{F}}$  is periodic in time with fundamental frequency  $\omega_0$ , it can be expanded in Fourier series as

$$\tilde{\mathbf{F}}(\mathbf{X},\mathbf{E},t) = \sum_{n=-\infty}^{+\infty} \tilde{\mathbf{F}}_n(\mathbf{X},\mathbf{E}) e^{jn\omega_0 t}.$$

(2.13)

Therefore, Eqn. (2.12) can be expressed in terms of the Fourier coefficients of  $\tilde{\mathbf{F}}$  as

$$\tilde{\mathbf{F}}_n(\mathbf{X},\mathbf{E}) = 0$$

$n = 0,1,\dots,+\infty$  (2.14)

which is an infinite set of complex nonlinear algebraic equations in **X** and **E**. Solving the first N+1 equations

$$\tilde{\mathbf{F}}_n(\mathbf{X}, \mathbf{E}) = 0 \qquad n = 0, 1, \dots, N$$

(2.15)

it is possible to obtain the N+1 unknown Fourier coefficients **X** of the state vector. The solution of this nonlinear algebraic system can be efficiently found by *ad hoc* numerical techniques. The details on the numerical implementation of this technique can be found in [23].

Harmonic Balance technique, which is well known in microwave circuit analysis, can be employed in EMI susceptibility analysis as a valid alternative to time-domain computer simulations [27]. Such a technique, in fact, if the number N of frequencies in the truncated Fourier expansion is sufficiently high, shows almost the same accuracy of time-domain transient simulation with a substantial improvement in terms of computational efficiency. In particular, the computational overhead of transient simulations in the analysis of circuits with very slow time constants excited by RF signals is completely avoided.

Nonetheless, Harmonic Balance is a computer simulation oriented technique like transient simulation, therefore it does not give insight in the nonlinear mechanisms which induce distortion in analog ICs nor relates RFI-induced failures to design parameters and parasitic elements. For this reason, Harmonic Balance may replace time-domain simulation in post-design EMI susceptibility investigations and in the validation of simpler analytical models but it cannot be directly employed in the design of analog ICs robust to EMI.

#### Volterra Series

Volterra series method is a powerful tool in the analysis of weakly nonlinear systems. This method, which was formulated by the Italian mathematician Vito Volterra in [28] in the XIX century, has been extensively employed in the analysis of weakly nonlinear electronic circuits since the beginning of the XX century [29, 30, 31].

According to Volterra series representation, in a d-input weakly nonlinear system, a generic output signal y(t) can be expressed in the form

$$y(t) = \sum_{i=0}^{+\infty} y^{(i)}(t)$$

(2.16)

in which

$$y^{(0)} = y_0, (2.17)$$

$$y^{(i)}(t) = \int_{-\infty}^{+\infty} \cdots \int_{-\infty}^{+\infty} h^{k_1, \dots, k_i} (\tau_1, \dots, \tau_i)$$

$$x_{k_1} (t - \tau_1) \dots x_{k_i} (t - \tau_i) d\tau_1 \dots d\tau_i$$

(2.18)

where  $h^{k_1,\dots,k_i}(\tau_1,\dots,\tau_i)$  with  $1 \leq k_i \leq d$  is the *i*-order time-domain tensor Volterra kernel,  $x_{k_i}(t)$  is the time domain input tensor (for each value of the index  $k_i$  it

represents a scalar input of the system) and the product

$$p = h^{k_1, \dots, k_i} (\tau_1, \dots, \tau_i) x_{k_1} (t - \tau_1) \dots x_{k_i} (t - \tau_i)$$

is an inner tensor product, i.e.

$$p = \sum_{k_1=1}^{d} \cdots \sum_{k_i=1}^{d} h^{k_1,\dots,k_i} (\tau_1,\dots,\tau_i) x_{k_1} (t-\tau_1) \dots x_{k_i} (t-\tau_i).$$

(2.19)

It is to be observed that the Volterra kernel representation in (2.16) is not unique, in fact, equivalent representations of the same system can be obtained by permutation of variables  $\tau_k$  in the Volterra kernels. A unique Volterra kernel representation can be obtained if only symmetric kernels are considered, i.e. kernels which are invariant for any permutation of the variables  $\tau_k$ . In the following only symmetric Volterra kernel representations will be considered.

A Volterra series model is said to be of the n-th order if the sum in (2.16) is truncated to i = n, i.e. if it includes only kernels up to order n. An equivalent expression for  $y^{(i)}(t)$  in (2.16) can be obtained using frequency-domain Volterra kernels. In this case

$$y^{(i)}(t) = \frac{1}{(2\pi)^i} \int_{-\infty}^{+\infty} \cdots \int_{-\infty}^{+\infty} H^{k_1,\dots,k_i}(\omega_1,\dots,\omega_i)$$

$$X_{k_1}(\omega_1)\dots X_{k_i}(\omega_i) e^{j\omega_1 t} \cdots e^{j\omega_i t} d\omega_1 \dots d\omega_i$$

(2.20)

where  $X_{k_i}(\omega)$  is the frequency domain input tensor (for each value of the index  $k_i$  it represents the Fourier transform of a system input) and the frequency domain Volterra kernels  $H^{k_1,\ldots,k_i}(\omega_1,\ldots,\omega_i)$  are the *i*-fold Fourier transforms of the time-domain Volterra kernels and they are expressed by

$$H^{k_1,\dots,k_i}\left(\omega_1,\dots,\omega_i\right) = \int_{-\infty}^{+\infty} \dots \int_{-\infty}^{+\infty} h^{k_1,\dots,k_i}\left(\tau_1,\dots,\tau_i\right)$$

$$e^{-\mathrm{j}\omega_1\tau_1}\dots e^{-\mathrm{j}\omega_i\tau_2}\mathrm{d}\tau_1\dots\mathrm{d}\tau_i.$$

(2.21)

The product

$$H^{k_1,\ldots,k_i}\left(\omega_1,\ldots,\omega_i\right)X_{k_1}\left(\omega_1\right)\ldots X_{k_i}\left(\omega_i\right)$$

is an inner tensor product as before.

Finally, performing the Fourier transform of (2.16) and (2.21) one gets

$$Y(\omega) = \sum_{i=0}^{+\infty} Y^{(i)}(\omega)$$

(2.22)

where

$$Y^{(0)}(\omega) = y_0 \delta(\omega) \tag{2.23}$$

and

$$Y^{(i)}(\omega) = \int_{-\infty}^{+\infty} \cdots \int_{-\infty}^{+\infty} H^{k_1, \dots, k_i} \left( \omega_1, \dots, \omega - \sum_{n=1}^{i-1} \omega_n \right)$$

$$X_{k_1}(\omega_1) \dots X_{k_i} \left( \omega - \sum_{n=1}^{i-1} \omega_n \right) d\omega_1 \dots d\omega_{i-1}$$

$$(2.24)$$

Equation (2.22) relates the spectrum of the output signals to the spectra of the input signals and justifies the classification of Volterra series method among frequency domain analysis methods.

Volterra series can be considered either as the generalization of Taylor series analysis, which is suitable to describe nonlinear memoryless systems, or as the generalization of frequency-domain analysis, which is suitable to describe linear dynamic systems, in order to describe the behavior of (weakly) nonlinear dynamic systems.

In fact, it can be observed that in the case of a memoryless system, i.e. a system in which the output signals depend only on the present value of the input signals, the Volterra kernels can be written as

$$h^{k_1,\dots,k_i}\left(\tau_1,\dots,\tau_i\right) = \hat{h}^{k_1,\dots,k_i}\delta(\tau_1)\delta(\tau_2)\cdots\delta(\tau_i),$$

where  $\hat{h}^{k_1,\dots,k_i}$  is a scalar constant independent of  $\tau_i$ , therefore, from (2.19),

$$y^{(i)}(t) = \hat{h}^{k_1,\dots,k_i} x_{k_1}(t) x_{k_2}(t) \dots x_{k_i}(t)$$

(2.25)

and (2.16) reduces to the Taylor series expansion of the output signal of a d-input nonlinear memoryless system.

It can be also observed from (2.16) that first-order Volterra kernels  $h^{k_1}(\tau_1)$ , i.e. the kernels for which i=1, are the linear system pulse responses for an input excitation  $\delta(t-\tau_1)$  applied as the  $k_1$ -th system input and consequently, the first-order frequency domain kernels  $H^{k_1}(\omega_1)$  are the linear frequency domain transfer functions.

Volterra series method is particularly attractive in the analysis of harmonic distortion and, in particular, for the prediction of the susceptibility to RFI of analog integrated circuits. In fact Volterra series allow a closed-form calculation of the RFI-induced harmonic components in the spectra of analog circuit output signals in terms of design parameters and parasitic elements. This feature makes Volterra analysis very useful in the design of analog integrated circuits robust to EMI.

Nonetheless, Volterra series method suffers of some limitations: in particular, this method is particularly suitable to the description of weakly nonlinear systems with

polynomial nonlinearity, while non-polynomial nonlinearity can only be described through high order Volterra models which can be very complex. In particular, a nonlinear characteristic which is not continuous and smooth (i.e. derivable up to high orders) in a given interval cannot be properly represented by Volterra series expansion of any order. Therefore, with reference to the analysis of electronic circuits, Volterra series can accurately predict the nonlinear polynomial behavior of MOS (BJT) devices biased in their saturation (active) region of operation while they can describe very poorly their threshold (switching) characteristics.

On the basis of these considerations, unlike computer simulation techniques, Volterra series analysis is very accurate only as far as the amplitude of the input signal and/or disturbances keeps the active devices within their nominal region of operation, while it is no longer reliable when the amplitude of RFI excites the threshold effect in the nonlinear characteristics.

Volterra series method will be employed in the following Chapter for the derivation of a model for the prediction of the susceptibility of integrated opamp circuits to RFI superimposed onto the nominal input signals and/or onto the power supply rails.

#### **Describing Function**

Describing function method can be considered as a simplified version of the Harmonic Balance technique which is suitable to closed-form calculations. This method, in particular, is effective for the frequency-domain analysis of weakly nonlinear dynamical systems which include only one insulated memoryless nonlinearity.

According with the describing function method, a memoryless nonlinearity f(x) is described in the frequency domain in terms of the harmonic content of its output signal when its input is a harmonic signal

$$x(t) = A\cos(\omega t + \varphi).$$

In this case, the output signal

$$y(t) = f(x(t)) = f(A\cos(\omega t + \varphi))$$

is a periodic signal with fundamental frequency  $\omega$ , therefore it can be expanded in Fourier series as

$$y(t) = \sum_{n=0}^{+\infty} H_n(A, \omega, \varphi) \cos(\omega t + \varphi_H(A, \omega, \varphi))$$

(2.26)

The Fourier expansion coefficients  $H_n(A,\omega,\varphi)$  and  $\varphi_H(A,\omega,\varphi)$  describe the operation of the nonlinear system in terms of the parameters (amplitude, frequency and

phase) of the input harmonic signal therefore they are referred to as describing functions. In other words, the describing function method characterizes the harmonic response of nonlinear systems in terms of amplitude and phase dependent frequency domain transfer functions. A describing function analysis of a nonlinear dynamical systems can be obtained on the bases of the frequency-domain characterization of the memoryless nonlinear section of the system and on the transfer functions which describe the linear section.

This method, which is widely employed in control theory, can be also employed in the analysis of the susceptibility of analog ICs to EMI. To this purpose, the describing function method is particularly attractive as it does not suffer of the limitation in terms of signal amplitude of Volterra series method and lets to relate the susceptibility to EMI of analog circuits to design parameters and parasitics. Nonetheless, unlike Volterra series method, its application is not straightforward and systematic. Analog circuits, in facts, typically include much more than a single memoryless nonlinearity and, furthermore, the signals which feed the nonlinearity are not pure harmonic signals. For these reasons, the main nonlinear mechanisms which are responsible of the EMI-induced failures in analog circuits should be firstly highlighted and ad hoc simplified models of the analog circuits should be developed which focus the main nonlinear effects. If the describing function method is properly employed, very accurate and effective analytical models for the prediction of the susceptibility to EMI of analog circuits may be derived.

## Chapter 3

# Prediction of Operational Amplifier Susceptibility to RFI

Integrated operational amplifiers (opamps), which are probably the most common and versatile analog building blocks in analog circuit design, have proven to be very susceptible to RFI superimposed onto their input terminals and/or onto the power supply rails. The susceptibility to RFI of IC opamp deserves a particular attention not only for the widespread diffusion of opamp circuits in more complex analog sub-systems but also because the case of opamp circuits is emblematic of the main aspects which should be taken into account in the prediction of the susceptibility to RFI of analog ICs.

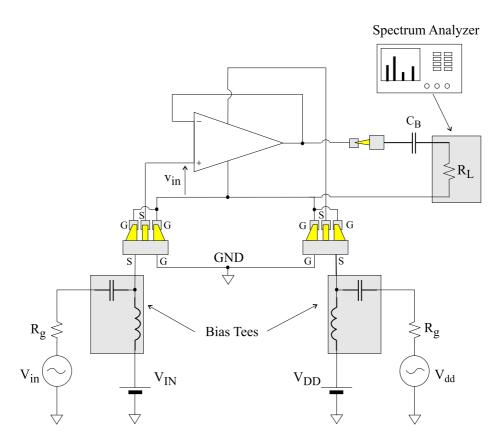

In this Chapter the susceptibility to EMI of integrated operational amplifiers is investigated. To this purpose, three different analytical models which predict the behavior of integrated opamp circuits in the presence of RFI are presented. After some basic considerations on the structure of integrated opamp circuits, the susceptibility of opamp ICs subjected to RFI superimposed onto the input voltages is investigated through Volterra series analysis. Then, Volterra series analysis is extended in order to take into account the demodulation of RFI superimposed onto opamp power supply rails.

Furthermore, the numerical model which has been proposed by Fiori in [20] for the prediction of the RFI-induced offset voltage in opamp circuits under large-signal excitation has been reconsidered. In particular, this model has been extended in order to provide a closed-form expression of the RFI-induced offset voltage in opamp circuits and in order to highlight the dependence on RFI frequency of the RFI-induced offset has been highlighted. This extension overcomes the limit of Volterra series analysis in closed-form prediction of the distortion induced by large signal RFI in opamp circuits.

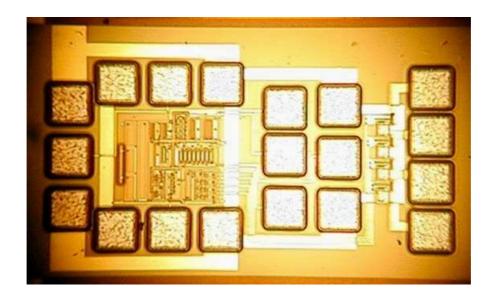

All the models which are discussed in this Chapter are validated by comparison

of model predictions and direct injection on-wafer CW RFI susceptibility measurements which have been carried out on opamp test chips that have been designed and diffused on silicon to this purpose.

## 3.1 Nonlinear Effects of RF Interference in Opamps

In this Section some qualitative considerations on the main nonlinear phenomena which may induce RFI distortion within IC opamp circuits are discussed. In particular, RF and baseband signal propagation within an opamp circuit is firstly investigated, then the peculiar role in RFI susceptibility which is played by the opamp input stage is highlighted and a general-purpose opamp macromodel for RFI susceptibility investigation is presented. Finally, more insight on the relation between the differential pair RFI-induced distortion and its parasitic capacitances is provided.

On the bases of these considerations, reported in [32, 33], the models which are presented in the following will be derived.

#### 3.1.1 Signal Propagation within Operational Amplifiers

Previous work shown that the nonlinear mechanisms that cause the demodulation of RFI which is superimposed onto the input terminals of CMOS opamps are almost only due to the input differential pair [12, 15]. This fact, that has also been experimentally verified, can be ascribed to two concurrent causes which are related to the propagation of RFI and baseband signals throughout CMOS opamps.

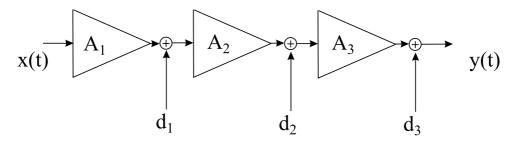

In particular, in order to evaluate in-band distortion of out-of-band RFI, an opamp can be regarded as the cascade connection of elementary amplifying stages, the first of which is usually a differential pair (Fig. 3.1). Each amplifying stage shows an amplification  $A_i(\omega)$  which is very high within its nominal bandwidth  $\omega_{B,i}$  while it is very low (about zero) out of this bandwidth, i.e.

$$\begin{cases} |A_i(\omega)| \gg 1 & \text{for } \omega < \omega_{B,i} \\ |A_i(\omega)| \simeq 0 & \text{for } \omega > \omega_{B,i}. \end{cases}$$

(3.1)

Figure 3.1. Block diagram of a three-stage amplifier.

Furthermore, each amplifying stage generates a certain amount of in-band distortion  $d_i$  due to the effects of RFI, which is related to the peak amplitude of RFI superimposed onto its input signal.

On the basis of (3.1), the out-of-band RFI that is superimposed onto the input voltages of a CMOS opamp essentially does not propagate beyond the input differential pair. In fact, if the frequency of RFI is out of the bandwidth of the differential pair, it is strongly attenuated by its transfer function. As a consequence, RFI does not reach the following stages and the amount of in-band distortion  $d_i$ , independently of its nonlinear characteristics, is intrinsically much smaller than the in-band distortion  $d_1$  generated by the differential pair.

Furthermore, assuming for the sake of simplicity that the in-band amplification of each stage is frequency independent (i.e.  $A_i\omega = A_i$ ), the output signal y of a three-stage opamp can be written in the form

$$y = A_1 A_2 A_3 x + A_2 A_3 d_1 + A_3 d_2 + d_3$$

=  $y_{\text{nom}} + y_{\text{d}}$  (3.2)

in which

$$y_{\text{nom}} = A_1 A_2 A_3 x$$

is the nominal output signal and

$$y_{\rm d} = A_2 A_3 d_1 + A_3 d_2 + d_3 \tag{3.3}$$

is the RFI-induced distortion.

From (3.3), the contribution of each single stage to the overall output distortion is given by the distortion generated by the stage multiplied by the amplifications of the stages that follow it. From (3.1) the in-band amplification of the cascaded stages is usually (very) high, therefore, even assuming the terms  $d_i$  of the same order of magnitude, the overall output offset is dominated by the contribution of the first stage.

From the above considerations on signal propagation within opamp circuits, it is essential to highlight the distortion phenomena induced by RFI in the input differential pair to the purpose of modelling the in-band effects of out-of-band RF interference, while the following amplifying stages can be assumed to be linear without appreciable loss of accuracy.

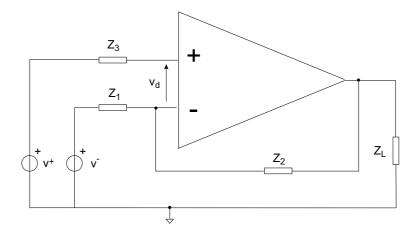

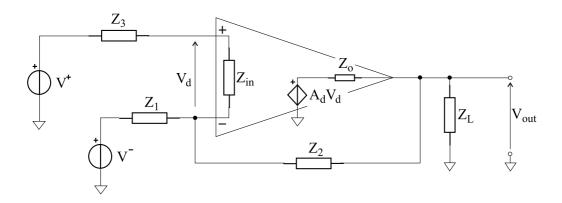

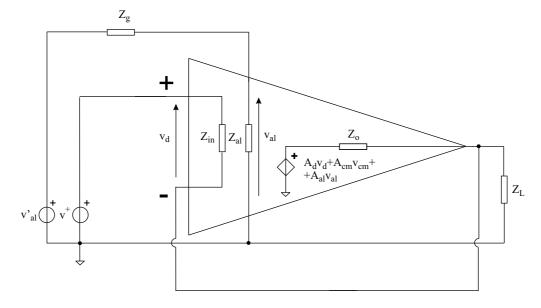

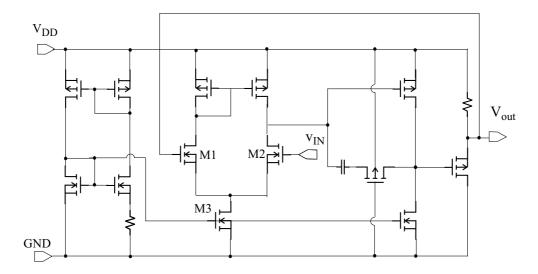

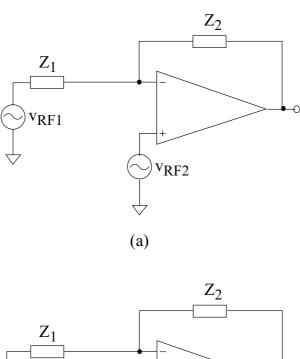

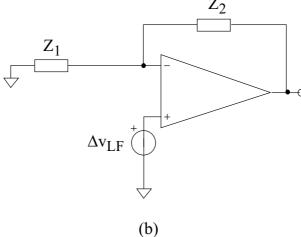

#### 3.1.2 An RFI-Oriented Opamp Circuit Model

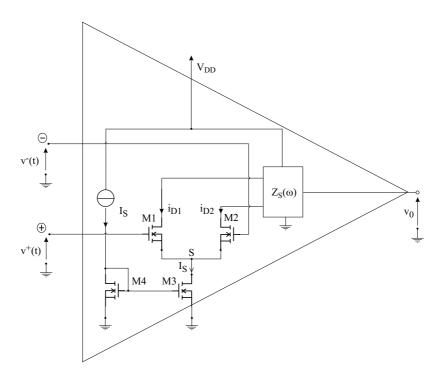

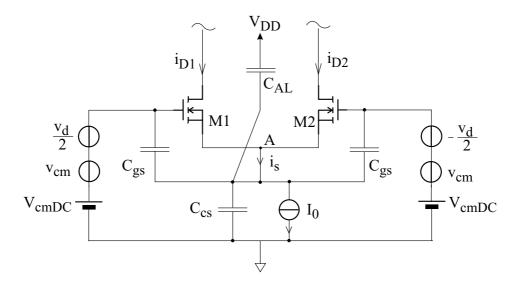

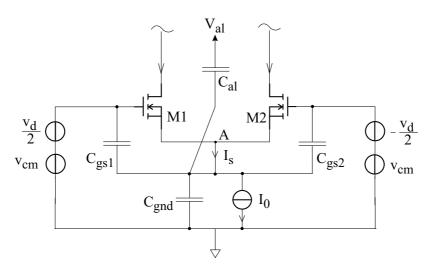

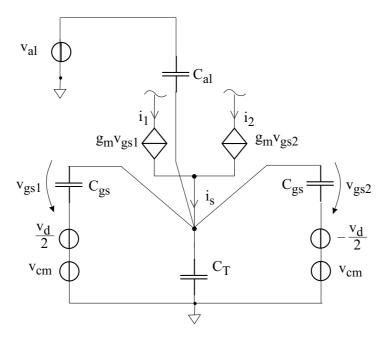

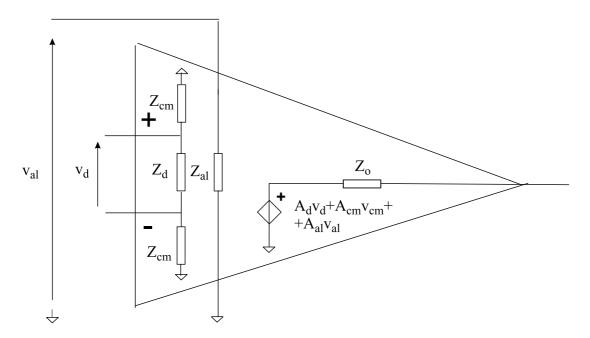

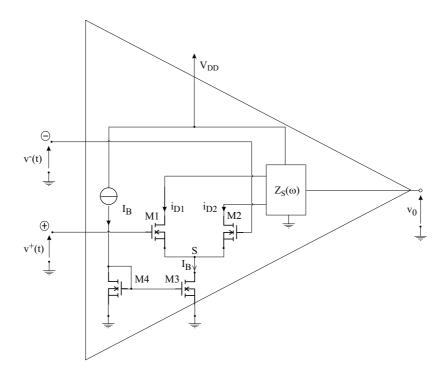

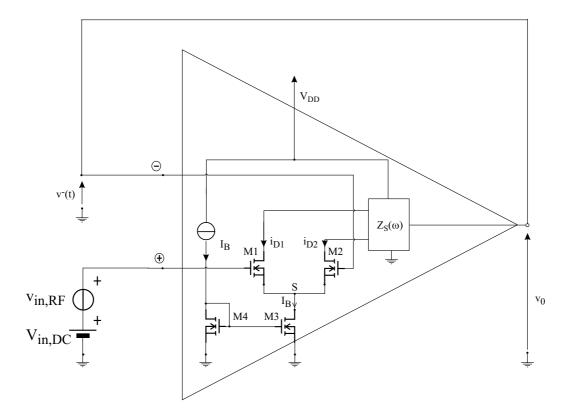

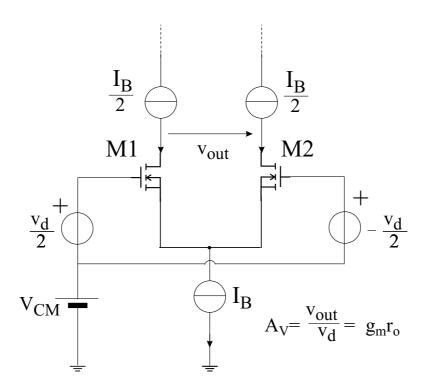

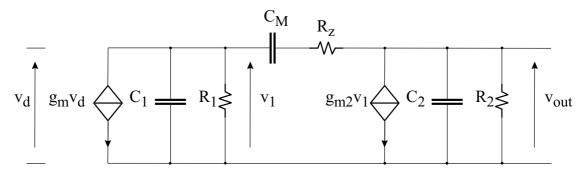

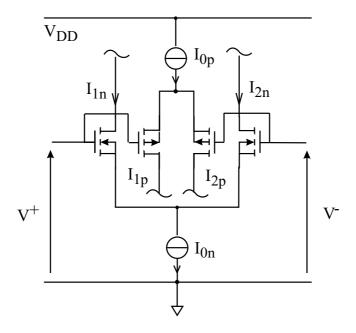

The considerations on opamp structure and signal propagations which have been presented above lead to the CMOS opamp circuit model shown in Fig.3.2. Such a circuit is composed by a differential pair cascaded with an ideal transimpedance amplifier  $(Z_s)$ .

The input differential stage is made up of two source coupled nMOS transistors (M1 and M2) biased by the current source  $i_{\rm S}$  and the input voltages  $v^-$  and  $v^+$ . The nonlinear characteristics of the input devices M1 and M2 are taken into account and the differential pair parasitics are properly extracted. The output signal is the current  $i_{\rm D}$ , which is defined as

$$i_{\rm D} = i_{\rm D1} - i_{\rm D2}.$$

(3.4)

This current drives the linear transimpedance amplifier  $(Z_s(\omega))$ . The transimpedance  $Z_s(\omega)$  is related to the open-loop differential amplification  $A_d(\omega)$  of the overall opamp circuit, in particular, it is given by

$$Z_{\rm s}(\omega) = \frac{A_{\rm d}(\omega)}{g_{\rm m}},$$

Figure 3.2. RFI-oriented opamp model.

where  $g_{\rm m}$  is the small-signal differential transconductance of the differential pair. The input voltages  $v^-$  and  $v^+$  in Fig.3.2 describe both nominal and interfering signals and they can be also expressed in terms of the common mode voltage

$$v_{\rm CM} = \frac{v^+ + v^-}{2},\tag{3.5}$$

and of the differential mode voltage

$$v_{\rm D} = v^+ - v^-. (3.6)$$

Such an opamp macromodel will be referred to in the following for the derivation of analytical models of the behavior of opamp circuits in the presence of EMI. To this purpose, in particular, the RFI-induced distortion in the differential pair which is included in it will be investigated.

#### 3.1.3 Differential Pair Nonlinear Operation

Differential pairs, because of their intrinsic symmetry, are usually considered to be free from even-order distortion, which is the main cause of RFI demodulation. Nonetheless, a particular high-frequency distortion phenomenon which is related to differential pair parasitics and occurs even in perfectly matched differential pairs has been highlighted [32, 33].

This phenomenon, which is the main cause of the susceptibility of CMOS opamps to RFI, is now illustrated with reference to the differential pair circuit in Fig.3.3. Under the assumption that transistors M1 and M2 are perfectly matched and at the same temperature, the relationship between the input differential voltage  $v_{\rm D}$  and the output differential current  $i_{\rm D}$  is given by

$$i_{\rm D} = \begin{cases} -i_{\rm S} & v_{\rm D} \le -\sqrt{\frac{i_{\rm S}}{\beta}} \\ v_{\rm D}\sqrt{2\beta i_{\rm S}}\sqrt{1 - \frac{\beta v_{\rm D}^2}{2i_{\rm S}}} & |v_{\rm D}| \le \sqrt{\frac{i_{\rm S}}{\beta}} \\ i_{\rm S} & v_{\rm D} \ge \sqrt{\frac{i_{\rm S}}{\beta}} \end{cases}$$

(3.7)

where  $i_{\rm S}$  is the bias current of the differential pair and

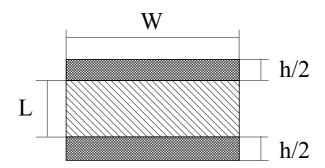

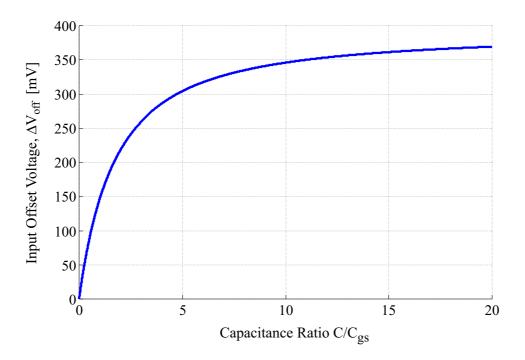

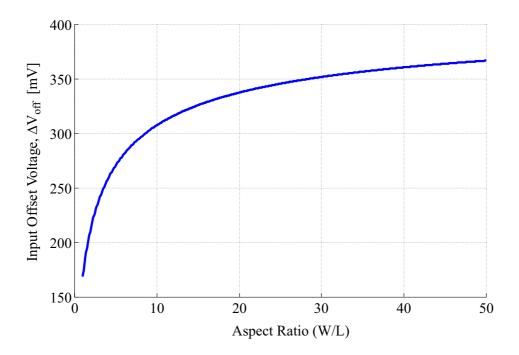

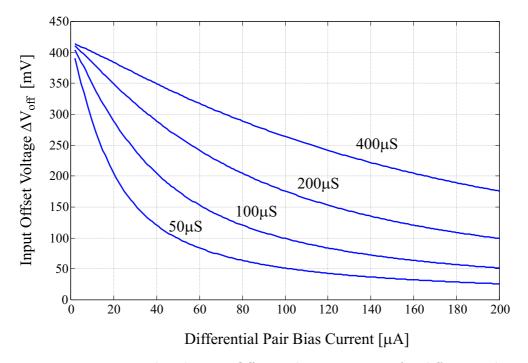

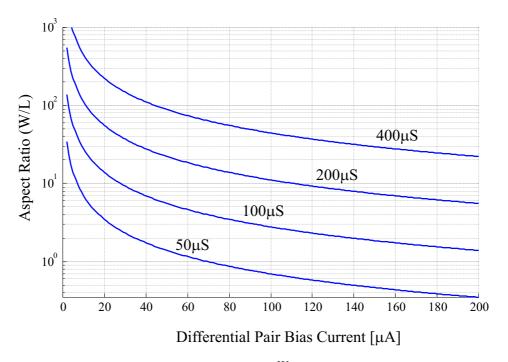

$$\beta = \frac{\mu C_{\text{ox}}}{2} \frac{W}{L}$$

where  $\mu$  is the mobility of electrons (holes) in nMOS (pMOS) devices,  $C_{\text{ox}}$  is the capacitance of the gate oxide per unit of area and W and L are the width and the length of the gate area of the MOS devices of the pair.

Figure 3.3. MOS Differential Pair.

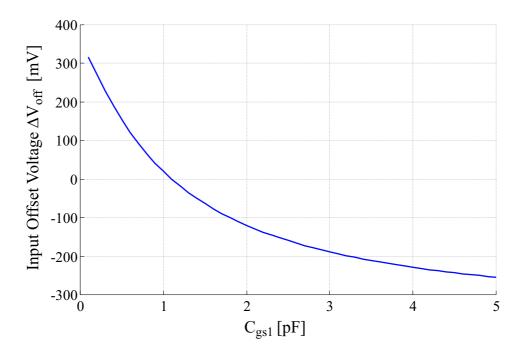

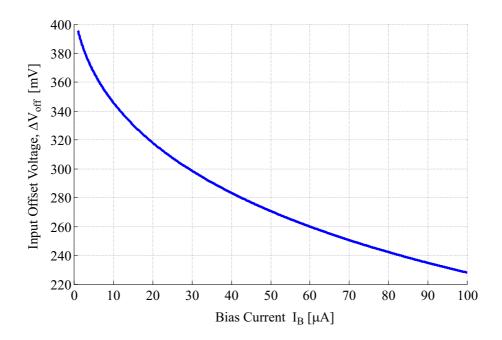

Expression (3.7) is usually regarded as a function of the only variable  $v_D$ , while  $\beta$  and  $i_S(t) = I_0$  are assumed to be constant design parameters. On the basis of this assumption, a differential pair is a completely symmetrical structure and therefore it does not generates even order distortion [30]. This fact is also implicit in (3.7), which shows that the differential current  $i_D$  is an odd function of  $v_D$ . In actual differential pairs, however, because of the finite admittance of the bias current source, RF fluctuations of the input common-mode voltage cause RF fluctuations on the effective bias current  $i_S$  which induce even-order distortion in the differential current because of a mixing effect.

This effect can be qualitatively illustrated performing a two-input, second-order Taylor series expansion of (3.7). By so doing, the differential current  $i_D$  is expressed as

$$i_{\rm d} = g_{\rm m} v_{\rm d} + g_{\rm p} v_{\rm d} i_{\rm s}. \tag{3.8}$$

where

$$g_{\rm m} = \sqrt{2\beta I_0}$$

is the linear transconductance of the differential pair and

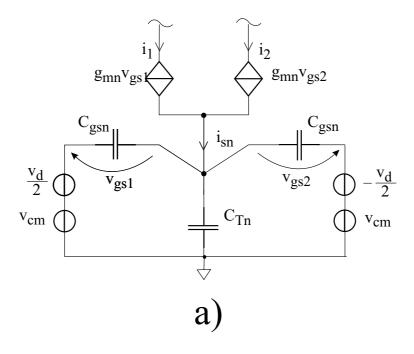

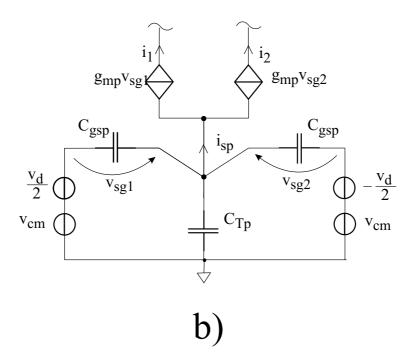

$$g_{\rm p} = \sqrt{\frac{\beta}{2I_0}}.$$

Furthermore, with reference to the differential pair shown in Fig.3.3, whose small-signal equivalent circuit is shown in Fig.3.4, the RFI fluctuations of the effective bias current can be expressed as

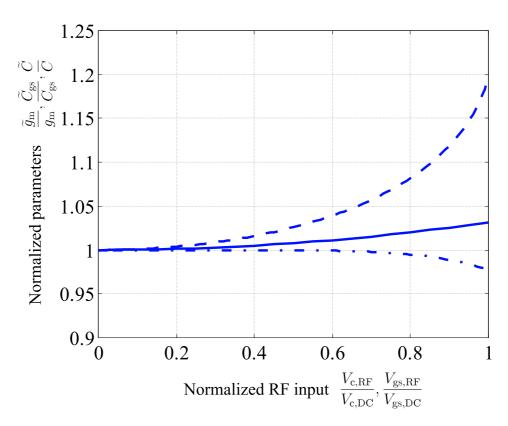

$$I_{s}(j\omega) = V_{cm}(j\omega) \frac{2g_{m}j\omega C_{T}}{j\omega (2C_{gs} + C_{T}) + 2g_{m}}$$

$$= V_{cm}(j\omega) Y(j\omega). \tag{3.9}$$

where

$$C_{\rm T} = C_{\rm cs} + C_{\rm AL}$$

is the parasitic capacitance connected between node S and AC ground whereas  $V_{\rm d}(j\omega)$  and  $V_{\rm cm}(j\omega)$  are respectively the differential and the common mode component of the input voltage in the frequency domain, as shown in Fig.3.4.

Eqn.(3.8) shows that, in the presence of RF fluctuations of the bias current, a differential pair acts as a mixer and performs the product between the RF components of  $v_{\rm D}$  and  $i_{\rm S}$ . Furthermore, because of the parasitic capacitance  $C_{\rm T}$ , as shown in (3.9), RF interference superimposed onto opamp input terminals induces RF fluctuations on the input differential voltage and on the bias current. As a consequence, the above mentioned mixing effect results in second-order distortion and in RFI demodulation.

On the basis of such considerations, the parasitic capacitances of the input differential pair strongly influence the susceptibility to EMI of CMOS opamps, for this reason the next Section is devoted to the physical origin of these parasitic capacitances.

## 3.1.4 Physical Origin of Differential Pair Parasitics

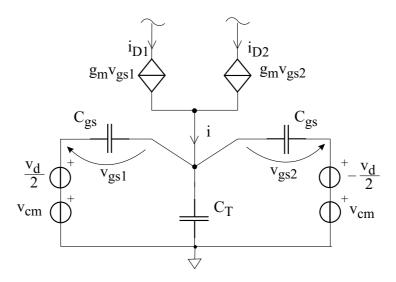

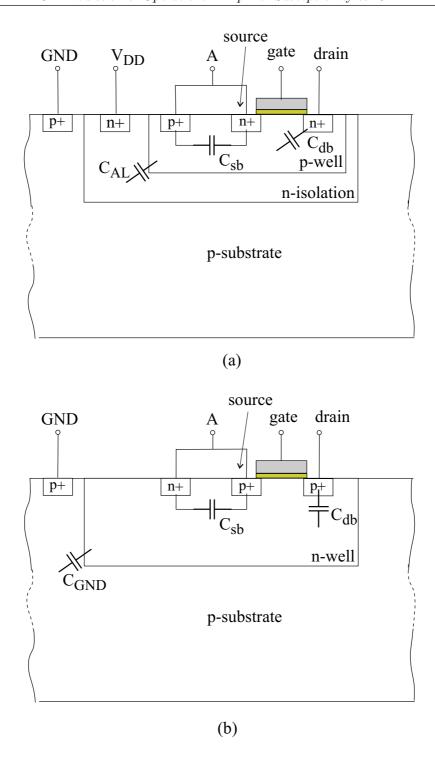

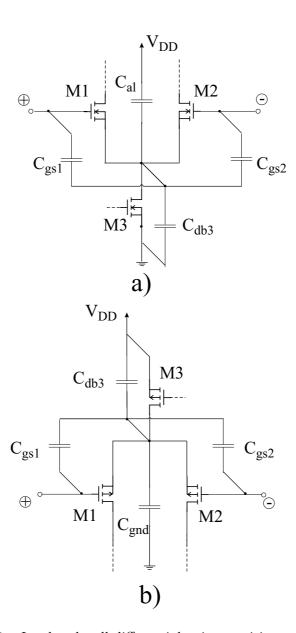

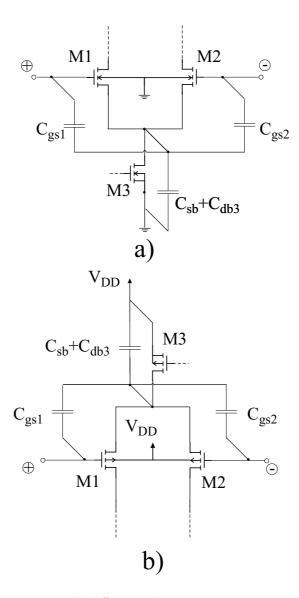

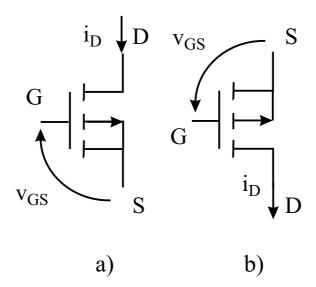

The parasitic capacitances which are included in a differential pair play a fundamental role in the susceptibility to RFI of CMOS opamps, as it has been highlighted in the previous Section, therefore it is meaningful to trace each parasitic capacitance back to its physical origin on the basis of the cross section of a CMOS technology process shown in Fig.3.5.

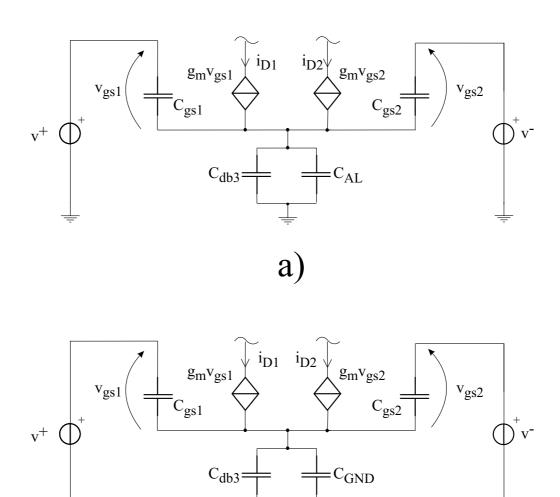

With reference to the nMOS differential pair in Fig.3.6a and to the cross section of an nMOS transistor in a standard twin-tub CMOS process which is provided in Fig.3.5a,  $C_{\rm db3}$  represents the drain-body reverse junction capacitance of transistor M3 while  $C_{\rm gs1}$  and  $C_{\rm gs2}$  in Fig.3.6a are the gate-to-source capacitances of transistors M1 and M2 respectively. The capacitance  $C_{\rm AL}$  in the same figure is related to the reverse biased junction between p-well and n-isolation as shown in Fig.3.5a. The parasitic capacitance  $C_{\rm sb}$  of M1 and M2 is not relevant because it is shorted by the connection between body and source.

If the p-well in which the differential pair is laid out is tied to ground, or if a single-well bulk CMOS process is employed and nMOS transistors are laid out directly on the substrate, as shown in Fig.3.7, the parasitic capacitance  $C_{\rm AL}$  is either connected between power supply and ground or it is absent at all. In both cases, it

Figure 3.4. Small signal equivalent circuit of the differential pair.

is not included in the signal path. In this case, however, the parasitic capacitances  $C_{\rm sb}$  of the input devices is connected between the common source node and ground and plays the same role in of  $C_{\rm AL}$  in the distortion of RFI.

With reference to Fig.3.6b and Fig.3.5b, the origin of the parasitic capacitances in a pMOS differential pair can be traced back in a similar way. It has to be noted that, in this case, the role of  $C_{\rm AL}$  is played by  $C_{\rm GND}$ , i.e. the capacitance of the reverse biased junction between n-well and the substrate. If the differential pair n-well is connected to the power supply voltage,  $C_{\rm GND}$  is no longer relevant and its role is played by  $C_{\rm sb}$ .

From the above analysis it can be pointed out that the parasitic capacitances  $C_{\rm AL}$  and  $C_{\rm GND}$  or  $C_{\rm sb}$ , which are included in the parasitic capacitance  $C_{\rm T}$  in (3.9), both depends on the layout of the differential pair. Therefore, an accurate prediction of this capacitance and, consequently, of the susceptibility of a given differential pair to EMI, can be made only on the basis of the physical layout of the circuit. Furthermore, the results on the effects of differential pair parasitics on the susceptibility to EMI can be translated into layout rules to increase the immunity to EMI.

Figure 3.5. Cross section of a twin-tub CMOS technology process.

${\bf Figure~3.6.} \quad {\bf Insulated-well~differential~pair~parasitic~capacitances.}$

Figure 3.7. Bulk differential pair parasitic capacitances.

## 3.2 A Two-Input Volterra Series Opamp Model

Volterra series are a very powerful analytical tool to describe nonlinear effects in weakly nonlinear dynamic systems. This analytical method, which has been already described in Section 2.2.2, provides the natural extension of frequency domain analysis to nonlinear systems and it enables to relate the nonlinear distortion properties of circuits to design parameters and to parasitics. These features make this approach particularly attractive in the modelling of the nonlinear effects of RFI in operational amplifiers.

Even though Volterra series have been extensively employed to predict harmonic distortion in analog integrated circuits and, in particular, in opamp circuits, the models which have been previously developed [30] were focused to in-band distortion and, in particular, do not include the high frequency distortion effect due to the differential pair parasitic capacitances which has been highlighted in the previous Section. Therefore, these models are not suitable to the prediction of the effects of RFI in opamp operations.