# POLITECNICO DI TORINO Repository ISTITUZIONALE

Small-Signal Circuit Model for Synchronous Buck DC/DC Converter featuring ZVS at Low-Side

# Original

Small-Signal Circuit Model for Synchronous Buck DC/DC Converter featuring ZVS at Low-Side / Gabriele, F.; Pareschi, F.; Setti, G.; Rovatti, R.; Lena, D.; Borghi, M. R.. - ELETTRONICO. - 2023:(2023), pp. 1-5. (Intervento presentato al convegno 56th IEEE International Symposium on Circuits and Systems, ISCAS 2023 tenutosi a Monterey, USA nel May 21-25, 2023) [10.1109/ISCAS46773.2023.10182213].

Availability:

This version is available at: 11583/2981143 since: 2023-08-20T08:49:36Z

Publisher:

Institute of Electrical and Electronics Engineers Inc.

Published

DOI:10.1109/ISCAS46773.2023.10182213

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# Small-Signal Circuit Model for Synchronous Buck DC/DC Converter featuring ZVS at Low-Side

Francesco Gabriele\*, Fabio Pareschi\*,<sup>‡</sup>, Gianluca Setti\*,<sup>‡</sup>, Riccardo Rovatti<sup>†,‡</sup>,

Davide Lena<sup>§</sup>, and Maria Rosa Borghi<sup>§</sup>

\* DET – Politecnico of Torino, corso Duca degli Abruzzi 24, 10129 Torino, Italy.

email:{francesco.gabriele, fabio.pareschi, gianluca.setti}@polito.it

† DEI – University of Bologna, viale Risorgimento 2, 40136 Bologna, Italy. email: {riccardo.rovatti}@unibo.it

† ARCES – University of Bologna, via Toffano 2/2, 40125 Bologna, Italy.

§ STMicroelectronics s.r.l. – Torino, Italy. email: {davide.lena, maria-rosa.borghi}@st.com

Abstract—In this paper we provide an improved small-signal equivalent circuit model of a synchronous Buck converter which operates in Continuous Conduction Mode (CCM) and includes an alternative Zero Voltage Switching (ZVS) mechanism for the low-side power MOSFET that rely on the MOSFETs output capacitance. The addressed analysis improves the state of the art in DC/DC small-signal modeling as it is capable to predict unexpected effects on the dynamical system response such as the dependency on input voltage introduced by parasitics. Therefore, a complete design tool which permits to evaluate the impact of the MOSFETs output capacitance and the ZVS network on the converter dynamics is proposed. The derived equivalent circuit model which includes an additional feedforward path and a feedback loop is analyzed and the main open-loop transfer functions (control-to-output, line-to-output, output impedance) are analytically assessed. A verification has been carried out through SIMPLIS circuital simulations, corroborating the validity of the whole evaluation process.

#### I. INTRODUCTION

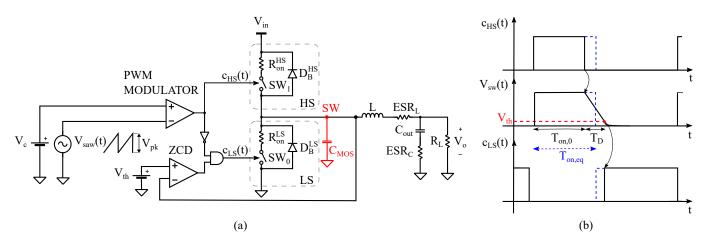

Synchronous Buck converters have become widely popular in practical applications [1], [2] due to the looming need to improve the overall power converters efficiency. Employing an half-bridge MOSFET switches to regulate a controlled output voltage a simultaneous conduction condition of the power MOSFETs must be avoided, therefore their control is synchronized. Typically, for a Buck converter which operates in CCM (as the one depicted in Fig. 1(a)) the employed power MOSFETs are complementary turned ON and OFF with a break-before-make control approach, where both the High Side (HS) and Low-Side (LS) switches are turned OFF for a dead-time interval.

With the aim of further minimizing the overall power losses, switching-losses contributions must be carefully reduced. To achieve this scope, a commonly used technique is based on the exploitation of *soft-switching* [3] [4] [5], which allows to recover a non-negligible amount of energy that otherwise would be lost during the switching transitions of the semiconductor devices. Concerning a power MOSFET, its stored energy can be lost when the device is turned on. Therefore, it is preferable to operates MOSFETs with ZVS throughout their turn-on transitions.

Focusing on the LS MOSFET operation during the deadtime interval  $T_{\rm D}$  (refer to the solid black lines waveforms in Fig. 1(b)), the current soaked up by the inductor starts to discharge the MOSFETs output capacitance, consequently decreasing the switching node voltage  $V_{\rm SW}(t).$  Whether the switching node voltage reaches the threshold voltage of the body diode  $D_{\rm B}^{\rm LS}$  (Fig. 1(a)) it becomes forward biased, leading to both diode conduction losses and diode reverse recovery losses. On the other side, the premature LS switching-on completely discharges its output capacitance, leading to a further switching loss contribution.

From this simplified analysis, it is inferrable that the appropriate turning on point must anticipates the body-diode forwarding bias and minimize the waste of energy stored in the output capacitor, turning the LS MOSFET ON when its drain-source voltage is very small. The optimum instant of time can be identified introducing the Zero Crossing Detection (ZCD) comparator portrayed in Fig. 1(a), which triggers the turning on command as soon as the SW node voltage drops below a certain threshold value (as graphically represented in Fig. 1(b)). Nevertheless, the ZCD comparator introduction impacts on the power converter dynamics, altering the Buck transient response and the overall system performance.

The contribution of this paper is precisely to examine the dynamic behaviour alteration of a traditional voltage mode controlled Buck converter when the whole ZVS network is introduced, deriving both an equivalent circuit model and evaluating the main open loop transfer functions (control-to-output, line-to-output and output impedance). The achieved results clearly show how the ZCD introduction translates into the addition of a current feedback loop and a voltage feed-forward into the traditional small-signal model of a Buck converter which operates in CCM, affecting the whole duty cycle perturbation.

The manuscript is hence organized as follows. An overview of the Buck converter behaviour under analysis is reported in Section II, highlighting the impact of the added ZVS network on the small-signal dynamics of the system. A canonical equivalent circuit model which includes the described ZVS mechanism is then proposed in section III and validated through a set of SIMPLIS simulations in section IV, where the main small-signal transfer functions are considered.

## II. DC/DC BUCK CONVERTER WITH ZCD

The following analysis is relied on the simplified schematic of the Buck converter shown in Fig. 1(a), empirically evaluating the ZCD block and the MOSFET output capacitance  $C_{\rm MOS}$  impact on the converter dynamic performances. The circuital topology taken into account is a voltage-mode controlled Buck converter, which includes a traditional sawtooth-based PWM modulator.

The power stage in Fig. 1(a) comprises the HS and LS power MOSFETs, modeled as a switch  $SW_{1,0}$  and a conduction resistance  $R_{\rm on}^{\rm HS,LS}$  in series, while the capacitive effect is modeled as the capacitance  $C_{\rm MOS}.$  The converter output filter includes an inductance L with an equivalent series resistance  $ESR_{\rm L}$ , a capacitance  $C_{\rm out}$  with an equivalent series resistance  $ESR_{\rm C}$  and the load resistor  $R_{\rm L}.$  An input voltage feed-forwarding is implemented, fixing the sawtooth peak voltage amplitude  $V_{\rm pk}=V_{\rm in}.$  This technique is very common,

Fig. 1. (a) Schematic of a Buck converter with ZVS Control on the low-side. (b) Dead time of synchronous Buck converter when the ZVS Control on LS MOSFET is present. The SW node voltage decreases linearly when the HS MOSFET is turned OFF, and the LS MOSFET is turned on when  $V_{\rm SW}=V_{\rm th}$ .

Fig. 2. Control-to-Output Transfer function and  $V_{\rm in}$  variation with and without the ZCD loop and  $C_{\rm MOS}$  presence

as it provides an output voltage dynamics that is ideally independent from the input voltage value  $V_{\rm in}$ .

To easily tackle the study of PWM converters dynamics, averaged linear time-invariant small-signal models [6], [7], [8] turn out to be very useful tools able to approximate the system non-linear switching behaviour with an analytically described equivalent model which allows to estimate the frequency response around a periodic steady-state operating point.

The mathematical model validation is performed with specific circuital simulator designed to handle the small-signal

frequency response of switching power systems. In this case, a set of Periodic Operating Point (POP) analyzes followed by AC simulations of the circuit in Fig. 1(a) (accounting the component values listed in Table I) have been performed in SIMPLIS, showing an unexpected Vin dependence on the output voltage Vo dynamic response with respect to the perturbation of the control voltage  $V_c$  when the feed-forwarding mechanism is present (i.e.,  $V_{\rm pk}=V_{\rm in}$ ). The collected results are shown in Fig. 2, where the open-loop control-to-output transfer function is drawn, showing an increasing damping effect for an input voltage sweep  $V_{\rm in}=30,50,70V$ . These simulation results are compared with the ones achieved from a canonical equivalent small-signal representation of the whole Buck converter, operating in CCM. The latter is derived exploiting the high versatility of the traditional small-signal AC model of the switching network in Fig. 1(a), which includes the pair of switches  $SW_{1,0}$  and the respective HS and LS MOSFET conduction resistances  $R_{on}^{\rm HS,LS}$  [9] but it does not account the MOSFET output capacitance  $C_{MOS}$ .

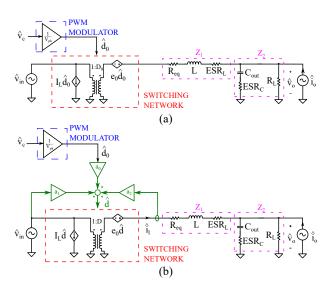

#### III. SMALL-SIGNAL CIRCUIT MODEL

The canonical small-signal equivalent circuit [10] in Fig. 3(a) can be obtained, where the switching network is enclosed into the red dashed box while the PWM modulator model is enclosed into the blue dashed box. The symbol  $\hat{\cdot}$  denotes the small-signal quantities while the steady state part is represented with capital letters. The PWM modulator provides the duty cycle perturbation  $\hat{d}_0$  from the control voltage perturbation  $\hat{v}_c$ , which together with the  $\hat{v}_{\rm in}$  and  $\hat{i}_o$  perturbations allows to study the system dynamical performances.

The switching network model includes a controlled current source whose value depends on the steady-state CCM average current in the inductor  $I_{\rm L}$  and a controlled voltage source dependant on  $e_0=V_{\rm in}$  -  $R_{\rm on}^{\rm HS}I_L+R_{\rm on}^{\rm LS}I_L$ . The transformer has a turns ratio which changes accordingly to the steady-state duty cycle  $D_0=T_{\rm ON,0}/T_{\rm SW}=V_{\rm O}/V_{\rm IN}$  and an equivalent series resistance  $R_{\rm eq}=R_{\rm on}^{\rm HS}D_0+R_{\rm on}^{\rm LS}(1-D_0)$  is introduced to account the MOSFET conduction resistances. The output filter network is directly connected from the original schematic of Fig. 1(a).

From the circuit in Fig. 3(a) the control-to-output transfer function between  $\hat{v}_c(s)$  and  $\hat{v}_o(s)$  is hence derived employing a

TABLE I

BUCK CONVERTER COMPONENT VALUES - SIMPLIS SIMULATIONS

| $R_L(\Omega)$ | V <sub>out</sub> (V) | $R_{ m on}^{ m HS}({ m m}\Omega)$ | $R_{ m on}^{ m LS}({ m m}\Omega)$ | L(µH) | $C_{ m out}(\mu { m F})$ | $\mathrm{ESR}_L(\mathrm{m}\Omega)$ | $\mathrm{ESR}_C(\mathrm{m}\Omega)$ | $f_{\rm SW}({ m kHz})$ | $C_{\text{MOS}}(\text{nF})$ |

|---------------|----------------------|-----------------------------------|-----------------------------------|-------|--------------------------|------------------------------------|------------------------------------|------------------------|-----------------------------|

| 1             | 3.3                  | 8                                 | 6                                 | 2.2   | 800                      | 10                                 | 2                                  | 500                    | 2                           |

Fig. 3. Small-Signal Model of a Buck Converter. (a): without ZVS; and (b): with ZVS.

TABLE II OVERALL DUTY CYCLE PARAMETERS

| $a_0$                                                                                                  | $a_1  (V^{-1})$                          | $a_2 (A^{-1})$                                       |

|--------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------|

| $\left(1 - \frac{C_{\text{MOS}}V_{\text{IN}}(V_{\text{IN}} - V_{\text{O}})}{4LI_{\text{PK}}^2}\right)$ | $\frac{C_{ m MOS}}{2T_{ m SW}I_{ m PK}}$ | $-\frac{C_{ m MOS}V_{ m IN}}{2T_{ m SW}I_{ m PK}^2}$ |

linear superposition, i.e. imposing  $\hat{v}_{\rm in}(s)$  =0 and  $\hat{i}_o(s)$  =0. This allows to obtain:

$$\frac{\hat{v}_o(s)}{\hat{v}_c(s)} = \frac{e_0}{V_{\rm pk}} \cdot \frac{Z_2(s)}{Z_2(s) + Z_1(s)} \tag{1}$$

where the impedances  $Z_1(s)$  and  $Z_2(s)$  enclosed in the purple boxes in Fig. 3(a) can be derived as:

$$Z_1(s) = sL + \text{ESR}_L + \text{R}_{eq}$$

$$Z_2(s) = \left(\frac{1}{sC_{\text{out}}} + \text{ESR}_C\right) // \text{R}_L.$$

(2)

As shown in Fig. 2, despite the compactness of the circuital model and its easy algebraic maneuverability, it does not include the ZVS mechanism impact on the small-signal model. Note that the capacitance  $C_{\rm MOS}$  is not present into the schematic of Fig. 3(a). Plugging it directly in the schematic may be tempting, but it does not provide the correct result. In fact, such approach does not take into account the ZCD loop behaviour (which must be carefully analyzed starting from its operating principle in the time domain portrayed in Fig. 1(b)) and consequently, its impact on the system small-signal model.

Looking at the waveforms in Fig. 1(b), as soon as the HS MOSFET is turned OFF the capacitance  $C_{\rm MOS}$  starts to discharge due to the presence of the inductor L, which sinks an amount of current approximately constant and equal to:

$$I_{\rm pk} = I_l + \frac{1}{2} \frac{V_{\rm in} - V_{\rm o}}{L} T_{\rm on,0}$$

(3)

where  $I_l$  is the average inductor current. The  $C_{\rm MOS}$  voltage  $V_{\rm sw}(t)$  decreases until the ZVS comparator detects a switching node voltage  $V_{\rm sw}=V_{\rm th}$ . Assuming without loss of generality that  $V_{\rm th}=0$ , the dead-time  $T_{\rm d}$  where both the HS and LS MOSFETs are turned OFF is equal to:

$$T_d = \frac{C_{\text{MOS}}V_{\text{in}}}{I_{\text{pk}}}.$$

(4)

The ZVS technique acts as a duty cycle alterations and indeed an equivalent ON time  $T_{\rm on,eq} = T_{\rm on,0} + T_d/2$  can be derived simply rearranging the shape of the  $V_{\rm sw}(t)$  voltage, as depicted in Fig. 1(b). In particular, the underlying area the  $V_{\rm sw}(t)$  voltage curve during  $T_{\rm D}$  is smeared to obtain a novel square wave. The ON time variation directly reflects on the Buck conversion ratio d as:

$$d = \frac{T_{\text{on,eq}}}{T_{\text{SW}}} = \frac{T_{\text{on,0}} + T_d/2}{T_{\text{SW}}}.$$

(5)

Perturbing and linearizing the independent parameter d, substituting (3) and (4) in (5) and replacing each quantity with a steady state part plus a time varying small signal contribution, namely:

$$d = \hat{d} + D \qquad d_0 = \hat{d}_0 + D_0 \qquad V_{\text{in}} = \hat{v}_{\text{in}} + V_{\text{IN}}$$

$$I_l = I_L + \hat{i}_l \qquad T_{\text{on},0} = \hat{t}_{\text{on},0} + T_{\text{ON},0}.$$

(6)

The overall duty cycle steady-state and perturbation expressions (respectively, D and  $\hat{d}$ ) are hence derived:

$$\hat{d} = a_0 \hat{d}_0 + a_1 \hat{v}_{in} + a_2 \hat{i}_l$$

$$D = D_0 + \frac{C_{\text{MOS}} V_{in}}{I_{\text{PK}}} \frac{1}{2T_{\text{SW}}}$$

(7)

where the new parameters introduced are defined in Table II. The extended small-signal equivalent circuit model which embeds the terms in (7) is represented in Fig. 3(b). It correctly introduces the effect of the capacitance  $C_{\rm MOS}$  and clearly shows how the ZVS mechanism gives rise to a voltage feed-forward path and an inner current feedback loop, similarly to what described in [11], [12], affecting the system dynamic behaviour.

The input voltage perturbation  $\hat{v}_{\rm in}$ , the output current perturbation  $\hat{i}_o$  and the control voltage perturbation  $\hat{v}_c$  are considered to determine the main open-loop small-signal transfer functions of the extended Buck converter model. Notice that the new circuit model in Fig. 3(b) can be directly derived from the original one in figure Fig. 3(a) simply substituting

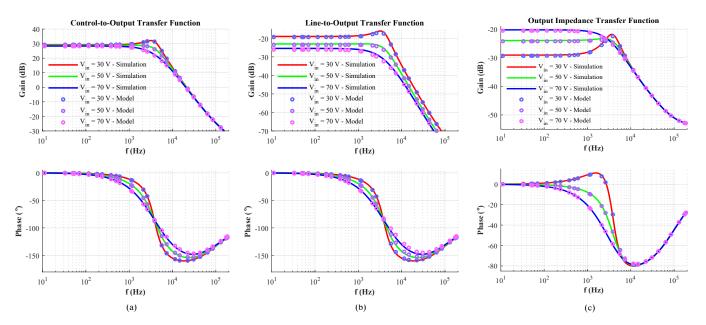

Fig. 4. Comparison between SIMPLIS simulation results and the extended small-signal model derived in IV of the main transfer functions for different  $V_{\rm in}$  values. (a) Control-to-output transfer function. (b) Line-to-output transfer function. (c) Output Impedance.

the nominal duty cycle values ( $d_0$  and  $D_0$ ) with the new ones (d and D), and introducing the green network resulting from (7).

### IV. MODEL VERIFICATION

From the extended small-signal model in Fig. 3(b) it is possible to evaluate the dynamic performance of the system, as analytically described from the transfer functions listed in the following.

1) Control-to-Output Transfer Function: For the purpose of determining the control-to-output transfer function, the independent external perturbation sources  $\hat{i}_o$  and  $\hat{v}_g$  are removed, evaluating the the  $\hat{v}_c$  impact on the Buck output voltage  $\hat{v}_o$ . Following this procedure, the desired transfer function is given by:

$$\frac{\hat{v}_o(s)}{\hat{v}_c(s)} = \frac{a_0 e_0}{V_{\rm pk}} \frac{Z_2(s)}{Z_2(s) + Z_1(s) + a_2 e_0}.$$

(8)

Eq. (8) clearly shows how the  $\hat{i}_L$  feedback loop in the overall small-signal model ( $a_2$  in Fig. 3(b)) dampens the control-to-output transfer function. It indeed introduces an equivalent resistance  $a_2e_0$  whose value is  $V_{\rm in}$  dependent. The control-to-output transfer function is plotted based on different  $V_{\rm in}$  values together with the results offered from the SIMPLIS simulation tool, as shown in Fig. 4(a).

2) Line-to-Output Transfer Function: The open-loop line-to-output transfer function could be derived by nullifying  $\hat{i}_o$  and  $\hat{v}_c$ . Evaluating the transfer function from  $\hat{v}_{\rm in}$  to  $\hat{v}_o$ :

$$\frac{\hat{v}_o(s)}{\hat{v}_{\rm in}(s)} = \frac{Z_2(s)(D + a_1 e_0)}{Z_1(s) + Z_2(s) + a_2 e_0}.$$

(9)

Both the  $\hat{v}_{\rm in}$  feedforward path and the the  $\hat{i}_L$  feedback loop concur in altering the audiosusceptibility of the Buck converter. However, this does not lead to a line transient degradation with respect to the original small-signal model.

The line-to-output transfer function is plotted based on different  $V_{\rm in}$  values together with the results offered from the SIMPLIS simulation tool, as shown in Fig. 4(b).

3) Output Impedance: Short-circuiting both the control voltage and the input voltage  $\hat{v}_{\rm in}(s)$  and perturbing with a current source  $\hat{i}_o(s)$  the converter output port, the correspondent output voltage perturbation  $\hat{v}_o(s)$  can be measured, deriving the open-loop output impedance as:

$$Z_{\text{out}}(s) = \frac{\hat{v}_o(s)}{\hat{i}_o(s)} = Z_2(s)||(Z_1(s) + a_2 e_0).$$

(10)

Similarly to what has been discussed for the control-to-output transfer function, the output impedance of the converter became larger and it is also damped due to the  $\hat{i}_L$  feedback loop. This consequently modifies the load transient response of the Buck converter.

The output impedance transfer function is plotted based on different  $V_{\rm in}$  values together with the results offered from the SIMPLIS simulation tool, as shown in Fig. 4(c).

# V. CONCLUSION

The ZVS mechanism for the LS MOSFET in a synchronous Buck converter has been analytically described and embedded into the traditional equivalent small-signal model of Buck converter operating in CCM. The analysis carried out on the extended small-signal model allowed to predict how the implemented ZVS technique impacts the dynamic performance of the open-loop Buck converter, evaluating the main system transfer functions (i.e., control-to-output, line-to-output and output impedance). Finally, SIMPLIS simulations have been performed to confirm the validity of the derived model, which accurately tracks the system frequency response.

This is the author's version of the article that has been presented at IEEE ISCAS2023 The editorial version of the paper is available at http://dx.doi.org/10.1109/ISCAS46773.2023.10182213

#### REFERENCES

- [1] L6983 Data sheet. STMicroelectronics.

- LMR36503 Data Sheet. Texas Instruments Inc. G. Hua and F. Lee, "Soft-switching techniques in PWM converters," IEEE Transactions on Industrial Electronics, vol. 42, no. 6, pp. 595—

- [3] G. Hua and F. Lee, Sott-switching techniques in FWM converters, IEEE Transactions on Industrial Electronics, vol. 42, no. 6, pp. 595–603, Dec. 1995. doi: 10.1109/41.475500

[4] C. Henze, H. Martin, and D. Parsley, "Zero-voltage switching in high frequency power converters using pulse width modulation," in APEC '88 third annual IEEE applied power electronics conference and exposition, Feb. 1988, pp. 33–40. doi: 10.1109/APEC.1988.10548

[5] T.-F. Wu, S.-A. Liang, and C.-H. Lee, "A unified approach to developing soft switching PWM converters," in 2000 IEEE 31st annual power electronics specialists conference. Conference proceedings (cat. No.00CH37018), vol. 1, Jun. 2000, pp. 193–198 vol.1. doi: 10.1109/PESC.2000.878836 ISSN: 0275-9306.

[6] R. D. Middlebrook and S. Cuk, "A general unified approach to modelling switching-converter power stages," in 1976 IEEE power electronics specialists conference, 1976, pp. 18–34. doi: 10.1109/PESC.1976.7072895

[7] S. Sanders and G. Verghese, "Synthesis of averaged circuit models for switched power converters," IEEE Transactions on Circuits and Systems, vol. 38, no. 8, pp. 905–915, 1991. doi: 10.1109/31.85632

[8] P. Krein, J. Bentsman, R. Bass, and B. Lesieutre, "On the use of averaging for the analysis of power electronic systems," IEEE Transactions on Power Electronics, vol. 5, no. 2, pp. 182–190, 1990. doi: 10.1109/63.53155

[9] V. Verperian "Simplified analysis of PWM converters using model of

- 10.1109/63.53155

- 10.1109/63.53155

[9] V. Vorperian, "Simplified analysis of PWM converters using model of PWM switch. Continuous conduction mode," *IEEE Transactions on Aerospace and Electronic Systems*, vol. 26, no. 3, pp. 490–496, May 1990. doi: 10.1109/7.106126

[10] S. Cuk, "Modelling, analysis, and design of switching converters," Dissertation (Ph.D.), California Institute of Technology, 1977.

[11] A. Witulski, "Buck converter small-signal models and dynamics: comparison of quasi-resonant and pulsewidth modulated switches," *IEEE Transactions on Power Electronics*, vol. 6, no. 4, pp. 727–738, Oct. 1991. doi: 10.1109/63.97774

[12] V. Vorperian, R. Tymerski, and F. Lee, "Equivalent circuit models for

- [12] V. Vorperian, R. Tymerski, and F. Lee, "Equivalent circuit models for resonant and PWM switches," *IEEE Transactions on Power Electronics*, vol. 4, no. 2, pp. 205-214, Apr. 1989. doi: 10.1109/63.24905