Doctoral Dissertation Doctoral Program in Electrical, Electronics and Communications Engineering (XXXIV.th cycle)

# A Real Time Locating System based on TDOA estimation of UWB pulse sequences

Stefano Bottigliero

Supervisor Prof. Riccardo Maggiora, PhD, Supervisor, Polytechnic of Torino

> Politecnico di Torino May 2, 2022

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Stefano Bottigliero

Turin, May 2, 2022

# Summary

One of the most popular technologies adopted for indoor localization is Ultra Wideband impulse radio (IR-UWB). Due to its peculiar characteristics, it is able to overcome the multipath effect that severely reduces the capability of receivers (Sensors) to estimate the position of transmitters (Tags) in complex environments. The architecture of the localization system requires time synchronization among the Sensors by means of very precise, high cost clocking mechanism or by means of a complex high level communication protocol between Sensors and Tags.

In this thesis work, we introduce a new low-cost real-time locating system (RTLS) that does not require time synchronization among Sensors and uses a one-way communication scheme to reduce the cost and complexity of Tags. The system is able to evaluate the position of a large number of Tags by computing the time difference of arrival (TDOA) of UWB pulse sequences received by at least three Sensors in known positions. In the presented system, the Tags transmit sequences of 2-ns UWB pulses with a carrier frequency of 7 GHz. Each Sensor processes the received sequences with a two-step correlation analysis performed first on a field-programmable gate array (FPGA) chip and successively on an on-board processor (ARM). The result of the analysis are the Time Of Arrival (TOA) of the pulse sequence at each Sensor and the Tag ID associated to it. These results are sent to a host PC implementing the trilateration algorithm based on the TDOA computed between couples of Sensors. To compute the 2D position of a Tag it is sufficient to use the TDOA among three Sensors.

Two different applications are developed. The first application, called LOCalization SYstem (SILOC in Italian) has the goal of localizing and tracking the position of different Tags inside a localization area with high precision and accuracy. The application is optimized to track moving Tags using a standard operating mode with good accuracy and high responsiveness and super-resolution operating mode with better accuracy but slower responsiveness. The second application, called Package Tracker (PackTrack) integrates new features on top of the SILOC application. It allows the user to monitor Tags attached to valuable goods (e.g. packages) in fixed positions over long periods of time. The application triggers an alarm whenever a Tag moves away from its position by a distance larger than the tolerance and continuously update a data log to keep track of each Tag's movement.

In the following Chapter 1, we first introduce the UWB signal in general and its application to indoor localization, we then briefly describe the most commonly used modulations and which one we adopted. The last part of the chapter introduces the different methods used for indoor localization and describes the details of the pulse sequence adopted in this project.

In Chapter 2 we discuss the design choices and implemented solutions of the developed hardware. We introduce the custom UWB transmitter with its digital and RF componets and the UWB receiving chain, made up of a custom UWB antenna and receiver. The chapter concludes with the description of the custom processing board and the system final prototype.

In Chapter 3 we discuss the details of the developed software. The chapter is divided in three main sections: The first section deals with the design of the FPGA firmware implementing a custom architecture able to receive a continuous stream of data, to recognize the presence of a transmitted sequence and to compute its TOA. The second section describes the ARM processor software that uses the information obtained by the FPGA, refines it and associate it to the correct Tag ID. The last section deals with the graphic user interface (GUI) developed to compute the TDOA among Sensors, to perform the trilateration algorithm and plot the localized Tags on a 2D map for user visualization.

The last chapter shows the results obtained with the RTLS system installed in our institution laboratory. The system tracking capabilities and localization accuracy have been evaluated by means of a measurement campaign. The obtained localization accuracy of 10 cm is demonstrated and discussed.

Acknowledgements

# Contents

| List of Tables |        |         |                                             | IX |

|----------------|--------|---------|---------------------------------------------|----|

| Li             | ist of | Figur   | es                                          | Х  |

| 1              | Ult    | ra Wio  | le Band Localization                        | 1  |

|                | 1.1    | Introd  | luction to UWB signals                      | 1  |

|                | 1.2    | UWB     | Modulations                                 | 4  |

|                | 1.3    | Comp    | arison between UWB localization techniques  | 5  |

|                |        | 1.3.1   | Received Signal Strength Indicator (RSSI)   | 5  |

|                |        | 1.3.2   | Time Of Flight (TOF)                        | 6  |

|                |        | 1.3.3   | Time Difference Of Arrival (TDOA)           | 8  |

|                |        | 1.3.4   | Phase Difference Of Arrival                 | 9  |

|                |        | 1.3.5   | Existing systems available on the market    | 10 |

|                |        | 1.3.6   | Proposed Implementation                     | 11 |

|                | 1.4    | Tag ti  | ransmitted Sequence                         | 12 |

| 2              | Har    | dware   | Design                                      | 17 |

|                | 2.1    | Introd  | luction                                     | 17 |

|                | 2.2    | Ultra   | Wide Band Receiver                          | 18 |

|                |        | 2.2.1   | UWB Receiving antenna                       | 18 |

|                |        | 2.2.2   | RF Receiver: Block Diagram                  | 20 |

|                |        | 2.2.3   | RF Receiver: PCB Design                     | 25 |

|                | 2.3    | First 1 | Prototype Tag                               | 28 |

|                |        | 2.3.1   | Design Overview                             | 28 |

|                |        | 2.3.2   | Block diagram                               | 28 |

|                |        | 2.3.3   | Radio frequency oscillator                  | 35 |

|                |        | 2.3.4   | PCB design                                  | 38 |

|                | 2.4    | Secon   | d Low-Power Tag Prototype                   | 41 |

|                |        | 2.4.1   | Block Diagram                               | 41 |

|                |        | 2.4.2   | Power gating implementation                 | 43 |

|                |        | 2.4.3   | Elliptic Dipole Antenna design              | 44 |

|                |        | 2.4.4   | UWB Antenna and RF Oscillator Co-Simulation | 44 |

|   |                | $2.4.5 Measured Results \ldots 46$                                                                                                      |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

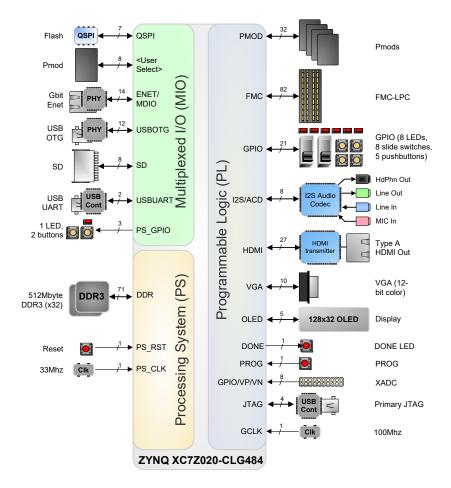

|   | 2.5            | Processing board prototype overview                                                                                                     |

|   | 2.6            | Sensor final prototype                                                                                                                  |

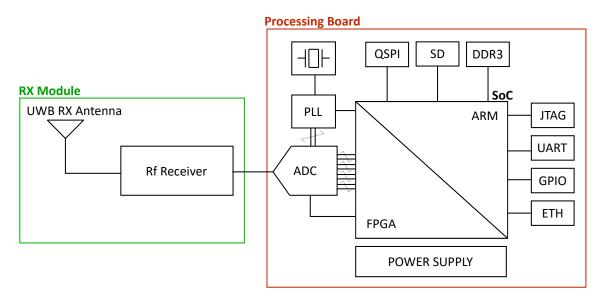

|   |                | 2.6.1 Block diagram                                                                                                                     |

|   |                |                                                                                                                                         |

| 3 |                | ware Design 61                                                                                                                          |

|   | 3.1            | Introduction                                                                                                                            |

|   | 3.2            | FPGA firmware design62                                                                                                                  |

|   |                | $3.2.1  Introduction \dots \dots$ |

|   |                | 3.2.2 Block diagram                                                                                                                     |

|   |                | 3.2.3 LVDS data management                                                                                                              |

|   |                | 3.2.4 Correlation                                                                                                                       |

|   |                | 3.2.5 Manual and Automatic Threshold implementation 72                                                                                  |

|   |                | 3.2.6 Data management                                                                                                                   |

|   | 3.3            | ARM firmware design                                                                                                                     |

|   |                | 3.3.1 Introduction                                                                                                                      |

|   |                | 3.3.2 System configuration                                                                                                              |

|   |                | 3.3.3 Sequence correlation                                                                                                              |

|   |                | 3.3.4 Ethernet Communication                                                                                                            |

|   | 3.4            | Boot Sequence                                                                                                                           |

|   | 3.5            | Host Application                                                                                                                        |

|   |                | 3.5.1 Introduction                                                                                                                      |

|   |                | 3.5.2 Time Difference Of Arrival                                                                                                        |

|   |                | 3.5.3 Multilateration                                                                                                                   |

|   |                | 3.5.4 Localization and position plotting                                                                                                |

|   |                | 3.5.5 UDP Packets Management                                                                                                            |

|   |                | 3.5.6 Graphic User Interface layout                                                                                                     |

|   |                |                                                                                                                                         |

| 4 | $\mathbf{Res}$ |                                                                                                                                         |

|   | 4.1            | Accuracy test                                                                                                                           |

|   | 4.2            | Resolution test                                                                                                                         |

|   | 4.3            | Tracking test                                                                                                                           |

|   | 4.4            | Comparison with other systems                                                                                                           |

|   | 4.5            | Summary of innovations                                                                                                                  |

|   | 4.6            | Conclusions                                                                                                                             |

# List of Tables

| 1.1 | Spectral Power Density Mean values allowed in the UWB frequency       |     |

|-----|-----------------------------------------------------------------------|-----|

|     | band                                                                  | 3   |

| 1.2 | Spectral Power Density Peak values allowed in the UWB frequency       |     |

|     | $\operatorname{band}$                                                 | 3   |

| 1.3 | The table reports the known Barker codes, from the shortest long      |     |

|     | only two symbols, to the longest one of thirteen symbols. On the      |     |

|     | right side is reported the sidelobe level with respect to the peak of |     |

|     | the autocorrelation function                                          | 15  |

| 2.1 | Details of the components adopted in the simulation                   |     |

| 4.1 | Comparison among UWB RTLS systems                                     | .13 |

|     |                                                                       |     |

# List of Figures

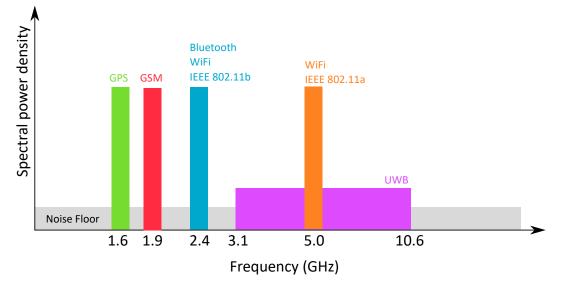

| 1.1 | Frequency Band allocation in comparison with the UWB frequency band.                                                           | 2               |

|-----|--------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.0 |                                                                                                                                | Z               |

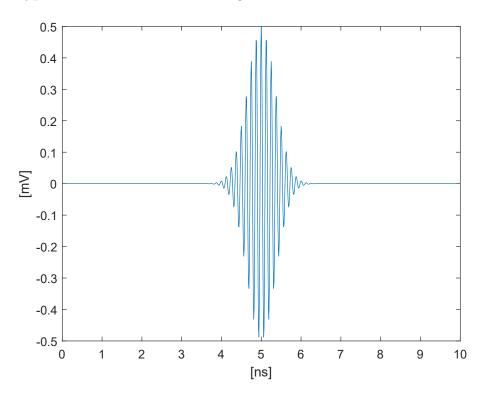

| 1.2 | Waveform of the transmitted UWB Pulse with 2 ns duration and carrier frequency of 7 GHz.                                       | 4               |

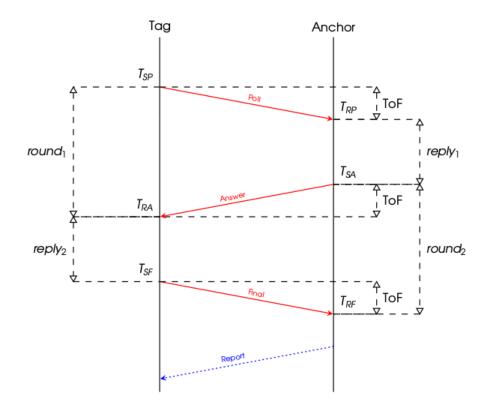

| 1.3 | Symmetrical Double-Sided Two Way Ranging communication scheme                                                                  | 7               |

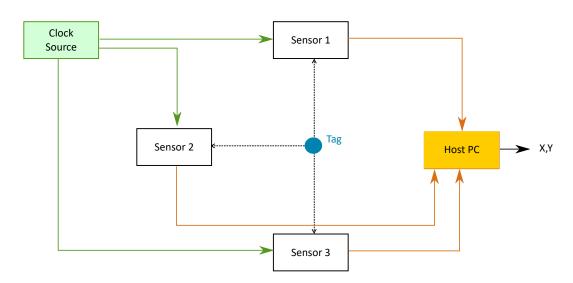

| 1.4 | High level scheme of a TDOA based RTLS system. The Three Sensors are connected with a common clock source and to a host PC for |                 |

|     | data processing and transmission.                                                                                              | 9               |

| 1.5 | Block diagram of the proposed architecture based on the use of a                                                               |                 |

|     | reference Tag to compensate the time offset among the Sensors clocks.                                                          | 12              |

| 1.6 | Graphical representation of the Barker 7 sequence                                                                              | 13              |

| 1.7 | Representation of the Barker 7 sequence autocorrelation function.                                                              |                 |

|     | The peak magnitude is equal to the sequence length and the sidelobe                                                            |                 |

|     | level is kept below zero.                                                                                                      | 14              |

| 1.8 | Graphical representation of the modified Barker 7 sequence.                                                                    | 16              |

| 1.9 | Comparison between the autocorrelation function of the original                                                                |                 |

|     | Barker 7 sequence (in blue) and the correlation between the orig-                                                              |                 |

|     | inal Barker 7 and our modified version (in red).                                                                               | 16              |

| 2.1 | Front, Bottom and cross section views of the final UWB receiver                                                                |                 |

|     | antenna 3D model                                                                                                               | 18              |

| 2.2 | Geometrical parameters of the receiving antenna model with the                                                                 |                 |

|     | corresponding values.                                                                                                          | 19              |

| 2.3 | Front view of the manufactured prototype with the reference coor-                                                              |                 |

|     | dinates system used for measurements.                                                                                          | 19              |

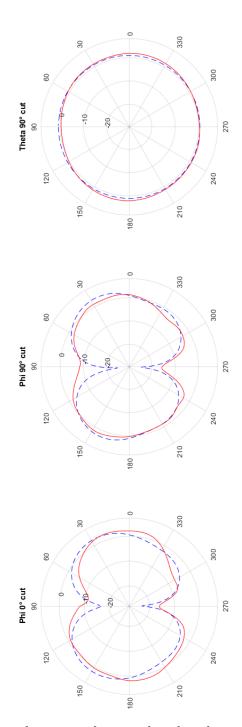

| 2.4 | Comparison between the simulation results (blue) and the measured                                                              |                 |

|     | ones (red) for the $\phi = 0^{\circ}$ cut.                                                                                     | 20              |

| 2.5 | Comparison between the simulation results (blue) and the measured                                                              |                 |

|     | ones (red) for the $\phi = 90^{\circ}$ cut                                                                                     | 21              |

| 2.6 | Comparison between the simulation results (blue) and the measured                                                              |                 |

|     | ones (red) of the reflection coefficient $(S_{11})$                                                                            | 21              |

| 2.7 | UWB receiver block diagram                                                                                                     | $\frac{-1}{22}$ |

|     |                                                                                                                                |                 |

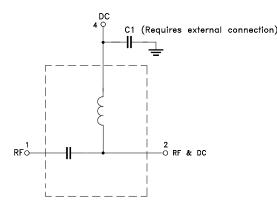

| 2.8  | TCBT-14R+ schematic. The inductor let the DC voltage pass in                 |  |  |

|------|------------------------------------------------------------------------------|--|--|

|      | order to supply the chip and block high frequency signal while the           |  |  |

|      | capacitor decouples the DC voltage supply allowing only the high             |  |  |

|      | frequency signal to pass                                                     |  |  |

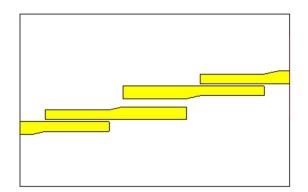

| 2.9  | Coupled Line Band Pass Filter                                                |  |  |

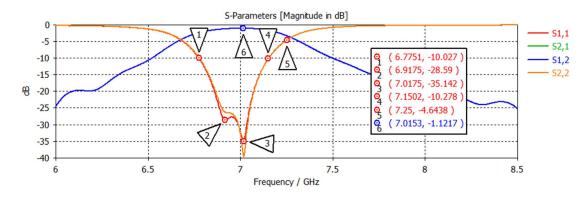

| 2.10 | Coupled line microstrip BPF simulation Results                               |  |  |

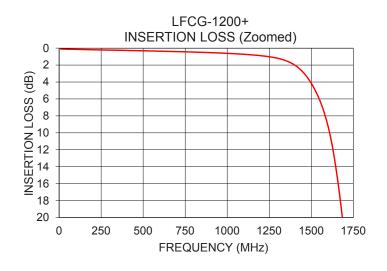

| 2.11 | Integrated LPF Insertion Loss behavior                                       |  |  |

|      | The manufactured receiver prototype. The two coupled lines BPF               |  |  |

|      | are shown without the metal case cover                                       |  |  |

| 2.13 | UWB receiver board Stack-Up                                                  |  |  |

|      | High level block diagram of the first Tag prototype                          |  |  |

|      | Tag power supply block schematic                                             |  |  |

|      | Clock generation circuit                                                     |  |  |

|      | Digital circuit schematic showing the pulse sequence, SRF timing             |  |  |

|      | and the short pulse generation circuits                                      |  |  |

| 2.18 | Low-cost 2 ns pulse generation circuit                                       |  |  |

| 2.19 | Timing of the pulse generation circuit used to produce the oscillator        |  |  |

|      | driving signal                                                               |  |  |

| 2.20 | Schematic of the 7 GHz pulsed oscillator                                     |  |  |

| 2.21 | Radiation patter of the Taoglas ceramic chip antenna. The images             |  |  |

|      | are taken from the component datasheet                                       |  |  |

| 2.22 | Evaluation board of the Taoglas antenna with the detail of the co-           |  |  |

|      | ordinates system orientation                                                 |  |  |

| 2.23 | Tag Stack-Up                                                                 |  |  |

| 2.24 | Layout of the first prototype bare PCB. The full circuit was never           |  |  |

|      | mounted since the oscillator was unstable due to parasitics $3$              |  |  |

| 2.25 | The new implementation of the first prototype moves the RF oscil-            |  |  |

|      | lator on a dedicated two layer PCB and uses an external antenna. $\ . \ \ 4$ |  |  |

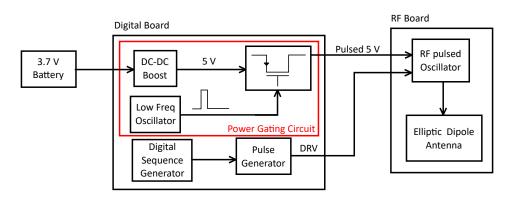

| 2.26 | Tag's high level block diagram. The digital board generates the              |  |  |

|      | pulsed voltage supply and the modulating pulse sequence for the RF           |  |  |

|      | oscillator                                                                   |  |  |

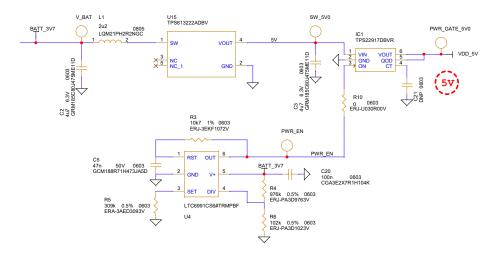

| 2.27 | Power gating circuit implemented to reduce power consumption.                |  |  |

|      | Only the LTC6991 low frequency oscillator and the DC-DC con-                 |  |  |

|      | verter are always powered on                                                 |  |  |

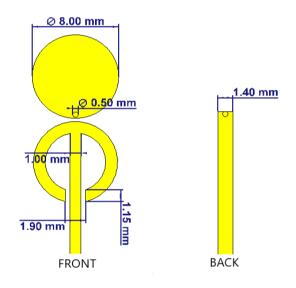

| 2.28 | Detail of the antenna geometric parameters, front and back view of           |  |  |

|      | the antenna                                                                  |  |  |

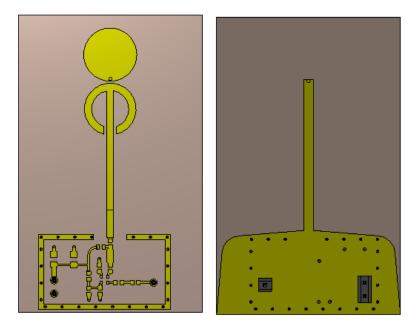

|      | Top and bottom view of the PCB 3D model                                      |  |  |

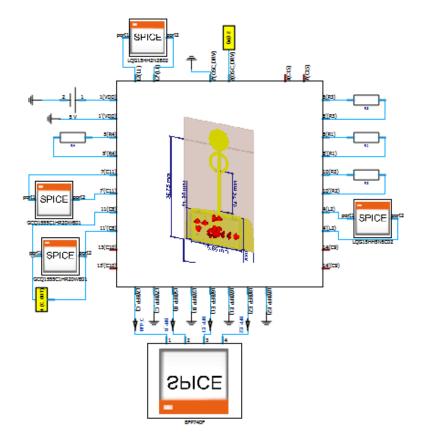

| 2.30 | CST transient simulation schematic. The 3D model used in the EM              |  |  |

|      | simulation is instantiated as an N-port component                            |  |  |

| 2.31 | Voltage of the RF output across the output capacitor (red), and the          |  |  |

|      | driving signal (blue) 4                                                      |  |  |

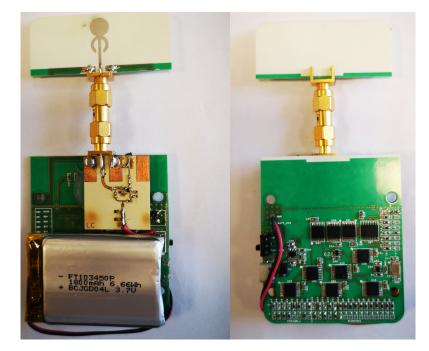

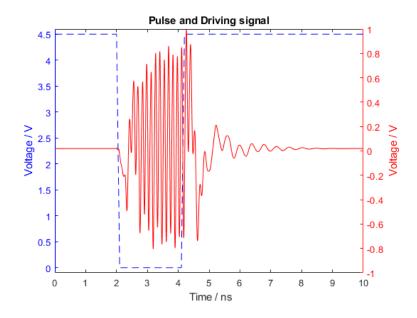

| 2.32 | Front view of the assembled low-power Tag prototype with the os-          |

|------|---------------------------------------------------------------------------|

|      | cillator and antenna board connected to the digital control circuit       |

| 2.33 | Comparison between the simulated radiation pattern (dashed line)          |

|      | and the measured one (red curve)                                          |

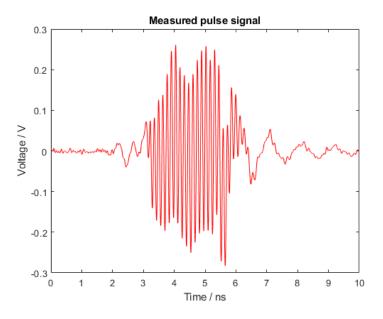

| 2.34 | Voltage of the radiated pulse signal measured on the oscilloscope         |

|      | with the antenna probe placed at 1 mm from the Tag antenna                |

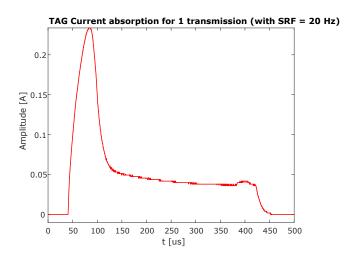

| 2.35 | Measured waveform of the current absorbed from the battery, with          |

|      | focus on the 470 $\mu$ s during the On state of the circuit. The waveform |

|      | is obtained averaging 64 successive transmissions.                        |

| 2.36 | Zedboard block diagram                                                    |

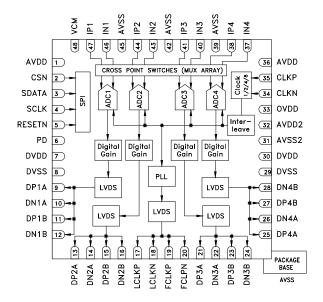

| 2.37 | HMCAD1511 1 GSPS ADC block diagram                                        |

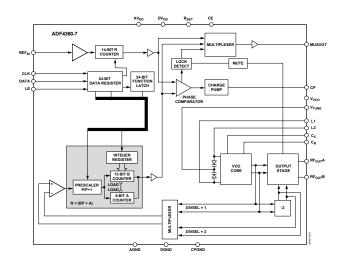

|      | ADF4360-7 VCO chip block diagram.                                         |

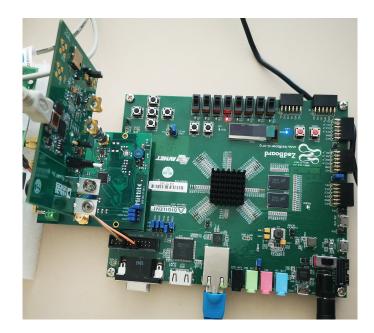

|      | The first Sensor prototype where the evaluation boards of the Xilinx      |

|      | SoC, the ADC, and VCO are connected together.                             |

| 2.40 | The Final Sensor prototype                                                |

| 2.41 | New Sensor processing board and UWB receiver assembly                     |

| 2.42 | Final aspect of the Sensor board enclosed in the box.                     |

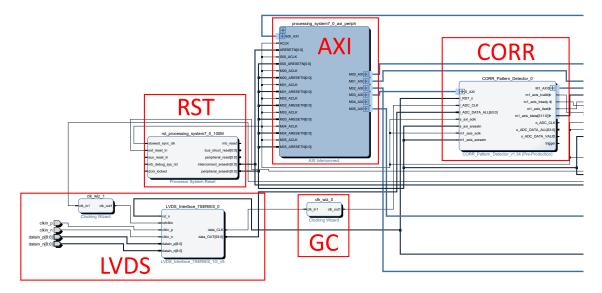

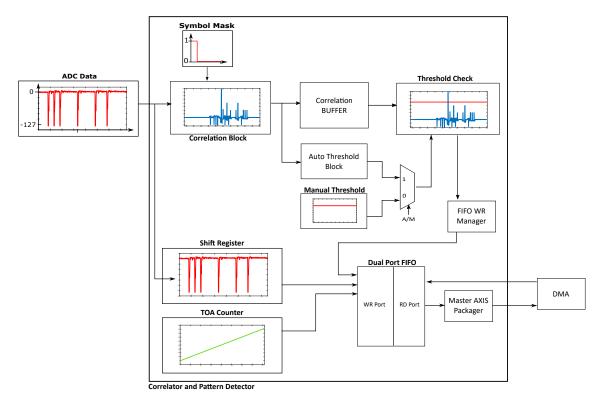

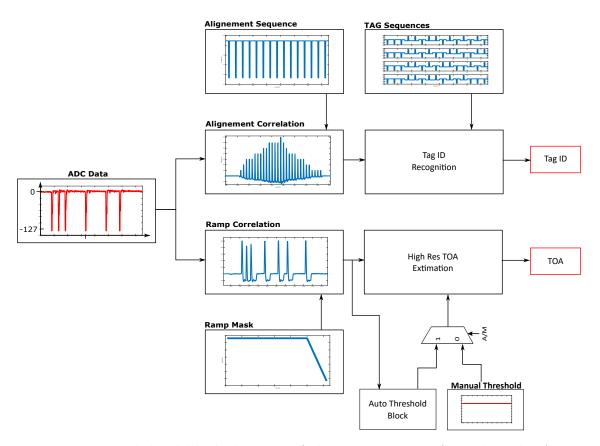

| 3.1  | High level block diagram of synthesized FPGA architecture. Detail         |

|      | of the LVDS data management interface and correlation block               |

| 3.2  | High level block diagram of synthesized FPGA architecture. Detail         |

|      | of the ARM processor block and its peripherals.                           |

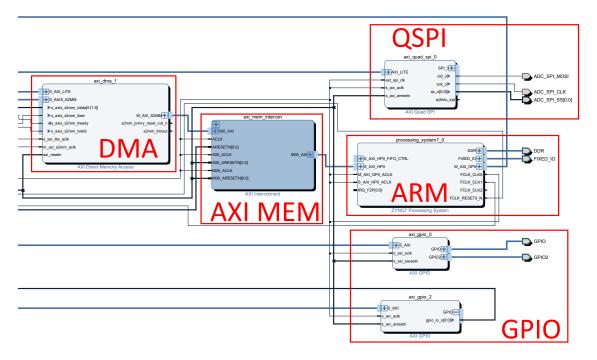

| 3.3  | Timing diagram of the LVDS data received by the FPGA. The image,          |

|      | taken from the HMCAD1511 ADC datasheet, shows the relation                |

|      | between the LCLK, FCLK and sampling clock signals and the ADC             |

|      | data                                                                      |

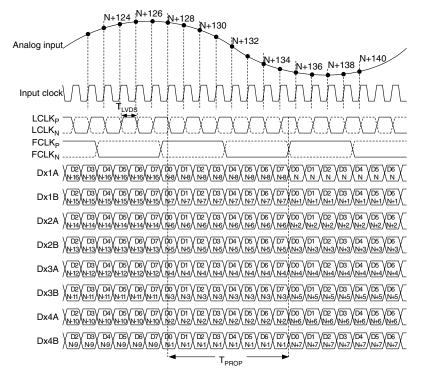

| 3.4  | Implemented LVDS Deserialization architecture showing the LCLK            |

|      | receiving chain in the upper part of the figure, and the FCLK and         |

|      | data receiving chain in the bottom side                                   |

| 3.5  | High-level block diagram of the processing steps performed in FPGA        |

|      | starting from the correlation of the incoming data with the symbol        |

|      | mask, to the thresholding operation to the final storage in the data      |

|      | buffer.                                                                   |

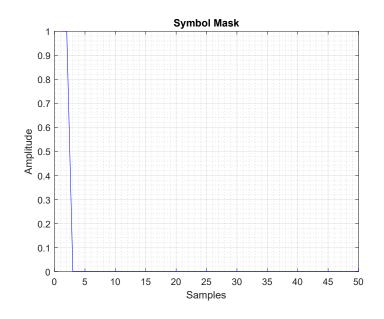

| 3.6  | The symbol mask used for the correlation operations. The mask has         |

|      | is shaped as a 2 ns rectangular pulse                                     |

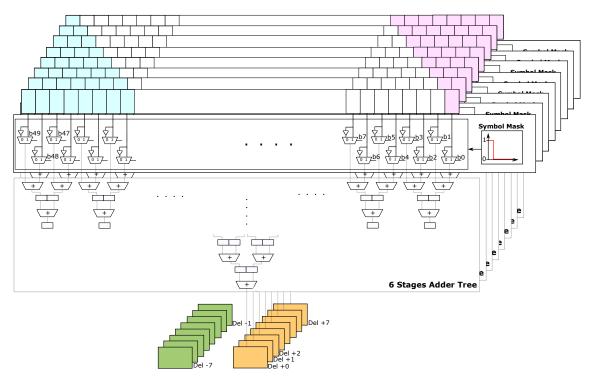

| 3.7  | Block diagram of the correlator block. It shows the eight instantia-      |

|      | tions of the elaboration blocks that compute the correlation delays       |

|      | and the final buffer where all the correlation results are stored. Each   |

|      | clock cycle the data buffer receives eight new data (in pink) and dis-    |

|      | cards the eight oldest data (in cyan). The newest correlation result      |

|      | (Del + 7) is computed using all the eight newest data                     |

|      |                                                                           |

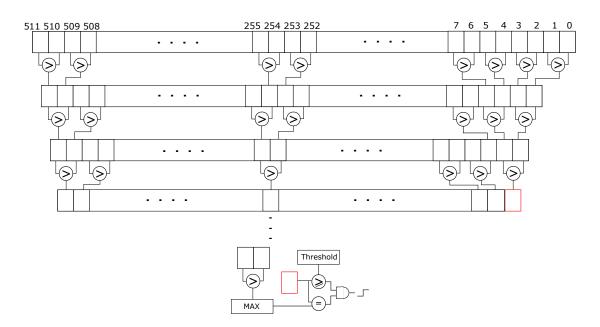

| 3.8  | FPGA threshold mechanism. We search for the maximum among the               |     |

|------|-----------------------------------------------------------------------------|-----|

|      | 512 correlation results and we require it to be in the middle of the        |     |

|      | comparisons window. If this condition is satisfied and the maximum          |     |

|      | value is larger than the threshold, we set the Thresh flag to 1             | 73  |

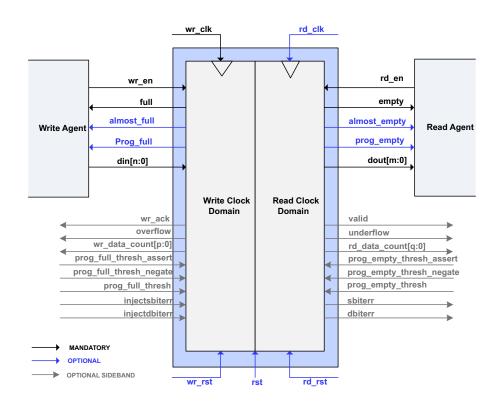

| 3.9  | Native FIFO IP interface presented in the Xilinx datasheet. On the          |     |

|      | left there is the write interface while the read interface is on the right. | 74  |

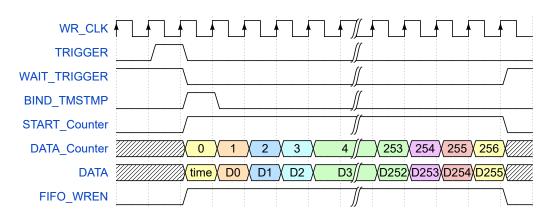

| 3.10 | FIFO Write process Timing                                                   | 75  |

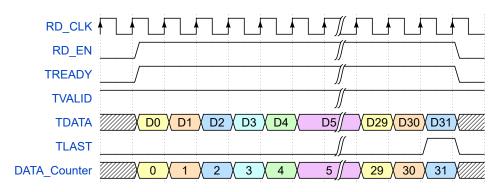

|      | FIFO Read process Timing                                                    | 76  |

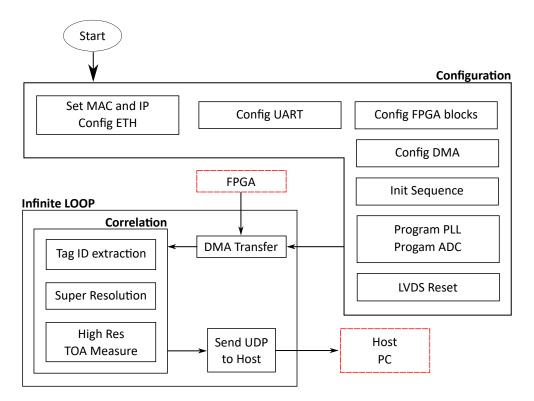

|      | High level block diagram of the ARM software program                        | 78  |

|      | Behaviour of complete Tag sequence 111001001010101: 1110010 rep-            |     |

|      | resents the common preamble while 01010101 is the unique binary             |     |

|      | Tag ID sequence corresponding to Tag 85                                     | 79  |

| 3 14 | High level block diagram of the operations performed in the ARM             |     |

| 0.11 | software to recognize the Tag ID associated to the received pulse           |     |

|      | sequence and its TOA.                                                       | 81  |

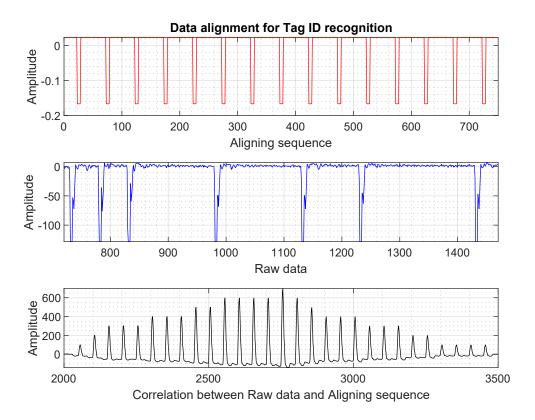

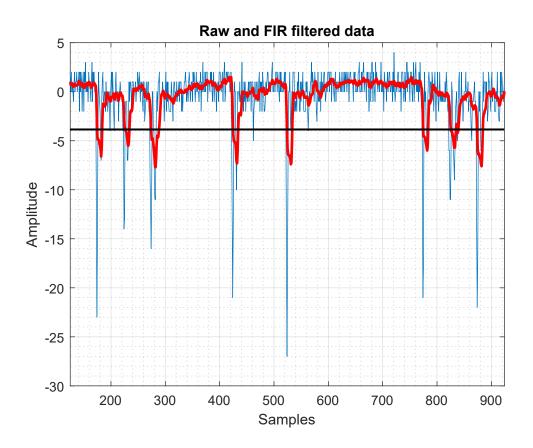

| 3 15 | Correlation between the raw data and the alignment sequence, the            | 01  |

| 0.10 | correlation has an absolute maximum when the two sequence are               |     |

|      | aligned. The x axis of the first two plots correspond to the sample         |     |

|      | positions.                                                                  | 83  |

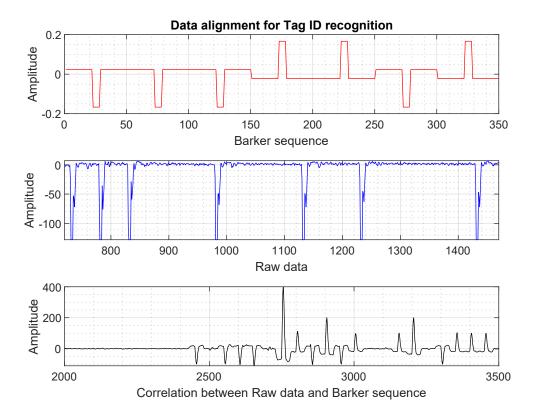

| 3 16 | Correlation between the raw data and the Barker 7 sequence, the             | 00  |

| 0.10 | correlation has an absolute maximum when the two sequence are               |     |

|      | aligned. The x axis of the first two plots correspond to the sample         |     |

|      | positions                                                                   | 85  |

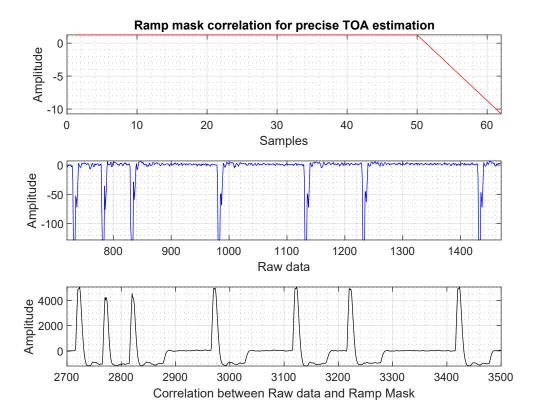

| 3 17 | Tag ID recognition by mean of thresholding the FIR filtered data.           | 86  |

|      | Correlation between the Ramp-like mask signal and the raw data,             | 00  |

| 0.10 | the correlation results underline the edge of the pulses                    | 88  |

| 3 10 | Content organization of the UDP packet sent to the host interface.          | 91  |

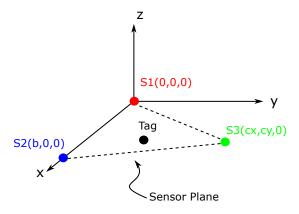

|      | Coordinate system used for the multilateration technique. The origin        | 51  |

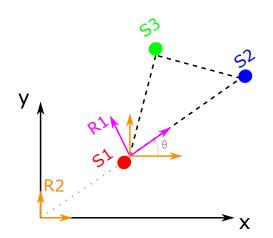

| 0.20 | of the reference system is placed in the reference Sensor position          | 95  |

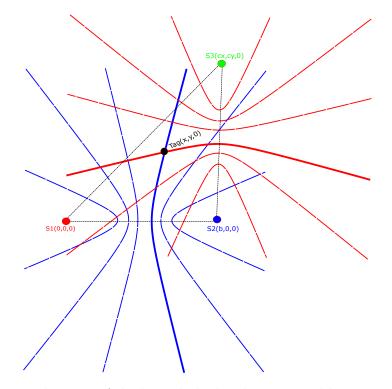

| 2 91 | Visualization of the hyperbolic localization problem using TDOA             | 30  |

| 0.21 | computation. The reference Tag in known position fixes the point            |     |

|      | where the two curves intersect                                              | 96  |

| ວ ດດ |                                                                             | 90  |

| 3.22 |                                                                             |     |

|      | coordinate system like R1. The passage between coordinates system           | 00  |

| 2 99 | is done through rototranslation.                                            | 99  |

| 3.23 | Custom format of the UDP Packets used for configuration command.            | 100 |

| 2.24 | 1                                                                           | 100 |

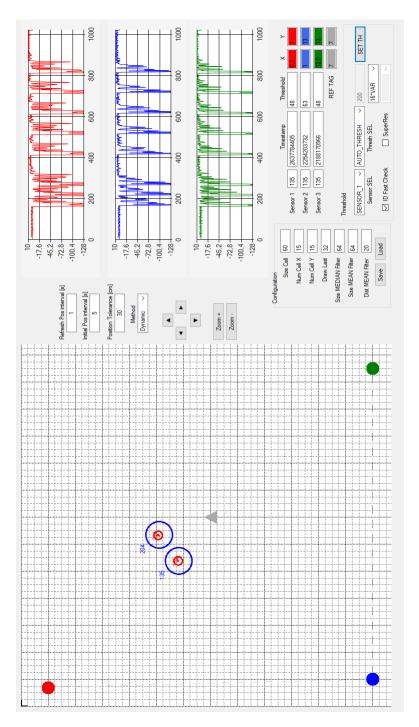

| 3.24 | Graphic User Interface layout, on the left is shown the localization        |     |

|      | area mapped by the Sensors and the mapped tags. The right side              | 100 |

| 0.05 | 1 0                                                                         | 102 |

| 3.25 | Second form, used to show some relevant statistics.                         | 105 |

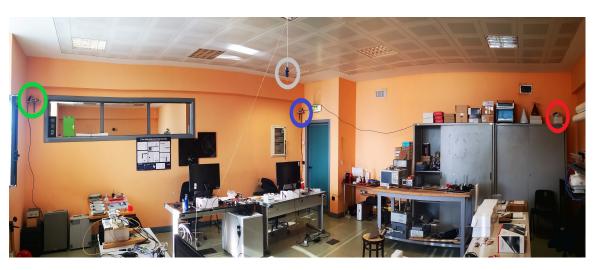

| 4.1 |                                                                       |     |  |

|-----|-----------------------------------------------------------------------|-----|--|

|     | are highlighted respectively the three Sensors and reference Tag po-  |     |  |

|     | sitions                                                               | 108 |  |

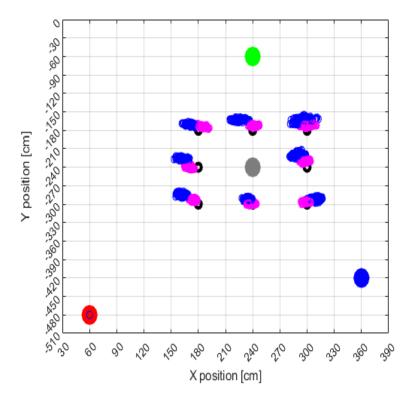

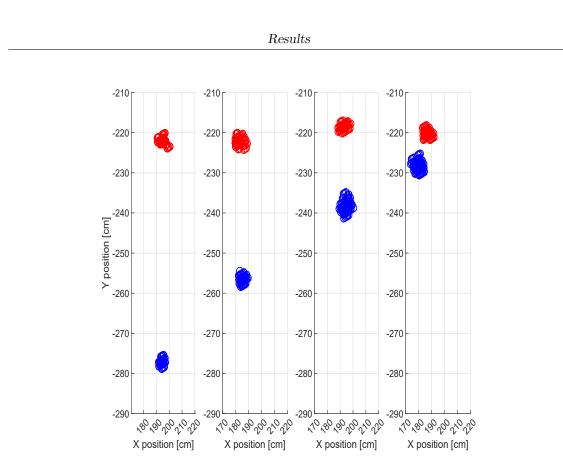

| 4.2 | Ground truth accuracy measurement. The case with super resolu-        |     |  |

|     | tion (magenta) performs better both in accuracy and precision when    |     |  |

|     | compared with the standard use case (blue)                            | 109 |  |

| 4.3 | Resolution measurement using two tags spaced 60, 40, 20 and 10 cm     |     |  |

|     | apart and enabling the super resolution.                              | 110 |  |

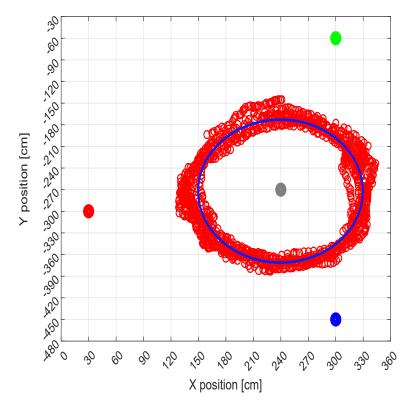

| 4.4 | The tracking measurement results. The red dots represents the 4096    |     |  |

|     | localization results of a Tag rotating around the reference Tag while |     |  |

|     | the blue circle is the real track of the Tag with 90 cm radius        | 111 |  |

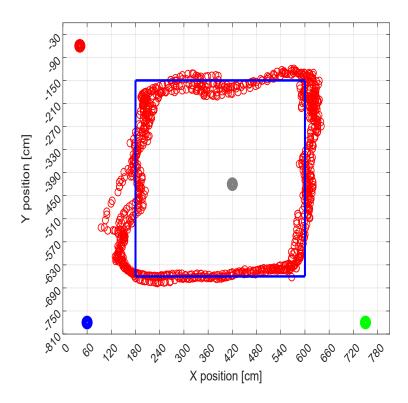

| 4.5 | The tracking measurement results. The Sensors are moved further       |     |  |

|     | away to cover the whole room area. The blue lines represents the      |     |  |

|     | track walked carrying the Tag, the red dots represents 1050 localiza- |     |  |

|     | tion results.                                                         | 112 |  |

# Chapter 1 Ultra Wide Band Localization

## 1.1 Introduction to UWB signals

As our world gets more and more connected, there is an increasing interest into those applications that are able to give us informations about the precise position, with respect to a reference coordinate system, of specific objects of interest, whether they are goods, pieces of machinery or persons.

Nowadays, there are many different solutions to this problem such as Global Positioning System (GPS), ultrasound and infrared time of flight technologies as well as other RF based solutions like WiFi and Bluetooth.

The GPS is a satellite based technology able to provide a very good position approximation (few meters) of satellite signals receivers [17]; it is integrated by many devices such as mobile phones, cars and boats. It is the optimal solution for outdoor positioning but, when we deal with indoor environments, since the signal coming from satellites is very weak, it is not a suitable solution [1].

Among the most used technologies for indoor positioning, there are the infrared light [18] and ultrasound [6] based technologies; these allow low cost solutions and a good accuracy (few centimeters) in the evaluation of the position. However, they require the Line Of Sight (LOS) between the object to be located or tracked and the Sensor used to locate it. This impose a huge constraint on the type of scenario for which these solutions are suitable; for example, a scene with many obstacles makes almost impossible for these system to guarantee an accurate localization.

To overcome the LOS constraints, the WiFi and Bluetooth technologies can be used. Relying on radio frequency signals they can easily be used for indoor localization but, due to high sensitivity to multi-path phenomena, they are not able to reach accuracy lower than a meter [76].

In this landscape of localization technologies another one emerged: Ultra Wide Band (UWB). The Ultra Wide Band is a radio technology based on the IEEE 802.15.4a and 802.15.4z standards [22]; it allows low power communications using

very short pulses with a bandwidth in the order of GHz. The frequency band allocated for UWB application was set in 2002 by the US Federal Communications Commission (FCC) from 3.1 GHz to 10.6 GHz [23].

An overview of the radio regulations applied in Europe is presented in [20] and [56].

Figure 1.1: Frequency Band allocation in comparison with the UWB frequency band.

The signals transmitted in the European band must comply with an Effective Isotropic Radiated Power (EIRP) transmission mask that establish the maximum values for the power spectral density peak, and mean values. In Europe the power spectral density mean value must be below the -41,3dBm/MHz threshold while the peak power spectral density must be 0dBm/50MHz maximum when the pulse carrier frequency is in a range between 6 and 8,5 GHz.

The limits on the Peak power density become more strict in those cases where the Pulse Repetition Frequency (PRF) is very low, meaning that the mean power is very limited; differently, when the PRF is higher, the mean power increases as well. The European standard sets the minimum Pulse Repetition Frequency to be 1 MHz, frequency at which the mean spectral power density is most strict.

The limit for these two parameters in the UWB band are reported in Tables 1.1 and 1.2. It is possible to notice that the frequency range where the requirements are less stringent is the 6,0 < f < 8,5GHz one. The UWB technology is suitable for localization applications and, differently with respect to other technologies such as Global Positioning System (GPS), infrared, ultrasound, WiFi and Bluetooth, it benefits of the following advantages:

• Very Low Energy levels: The duration of the pulse is very short compared to

| Frequency (GHz)     | EIRP Mean Density (dBm/MHz) |

|---------------------|-----------------------------|

| $f \leq 1, 6$       | -90                         |

| $1,6 < f \le 2,7$   | -85                         |

| $2, 7 < f \le 3, 4$ | -70                         |

| $3,4 < f \le 3,8$   | -80                         |

| $3,8 < f \le 4,8$   | -70                         |

| $4,8 < f \le 6,0$   | -70                         |

| $6, 0 < f \le 8, 5$ | -41,3                       |

| $8,5 < f \le 10,6$  | -65                         |

| f >10,6             | -85                         |

1.1 – Introduction to UWB signals

Table 1.1: Spectral Power Density Mean values allowed in the UWB frequency band.

| Frequency (GHz)     | EIRP Peak Density (dBm/50MHz) |

|---------------------|-------------------------------|

| $3,4 < f \le 3,8$   | -40                           |

| $3,8 < f \le 4,2$   | -30                           |

| $4,2 < f \le 4,8$   | 0                             |

| $4,8 < f \le 6,0$   | -30                           |

| $6, 0 < f \le 8, 5$ | 0                             |

| $8,5 < f \le 10,6$  | -25                           |

| f >10,6             | -45                           |

Table 1.2: Spectral Power Density Peak values allowed in the UWB frequency band.

the symbol duration reducing the overall transmitted energy;

- High immunity to multipath: In the field of indoor localization GPS is not a suitable choice and Wifi and Bluetooth are heavily affected by multipath. The UWB is much more resilient to this phenomenon thanks to the use of very short pulses with large frequency content allowing to separate the direct path contribution;

- High accuracy ranging: the usage of short pulses enables to achieve ranging accuracy in the order of few centimeters;

- High penetration through and around obstacles: many materials have absorption peaks over a narrow frequency band, in such cases, having a very large bandwidth is an advantage.

## 1.2 UWB Modulations

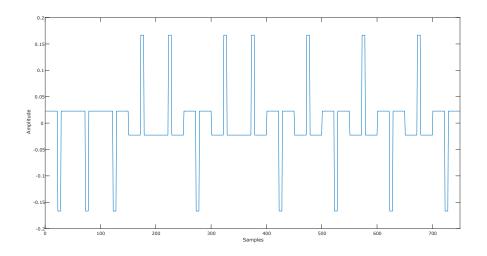

The transmitted UWB pulses adopted in this thesis are obtained by the multiplication of a short, few nanoseconds base band pulse with a local oscillator signal switching at a central frequency in the working bandwidth between 6.0 and 8.5 GHz. A typical waveform is shown in Figure 1.2.

Figure 1.2: Waveform of the transmitted UWB Pulse with 2 ns duration and carrier frequency of 7 GHz.

The presented waveform represents the basic bit of information. It is necessary to find the best modulation technique in order to represent each bit with the proper signal. The most common binary modulation techniques used in UWB communications are:

- Pulse Position Modulation (PPM), where the position of the pulse inside a bit period (symbol) is used to encode the bit value;

- Amplitude Modulation (PAM), where the bit value is encoded in the variation of the amplitude of the pulse;

- Pulse Width Modulation (PWM), where the bit value is associated to the different pulse durations;

- Pulse Shape Modulation (PSM), where the coding of the bit value is associated to a combination of phase and/or frequency modulations. An example is the Binary Phase Shift Keying (BPSK) where the two bit values are associated to pulses that are 180° phase shifted with respect to each others.

- On Off Keying (OOK), where the bit value is associated to the presence or the absence of a pulse inside the bit period.

The very short duration of the signal envelop makes it very hard to use the common modulations that rely on changes in the carrier phase or frequency since during the signal envelop only few carrier periods are present; as a consequence, the modulations commonly used for UWB signals are base band modulation.

The duration of the pulse is in the order of 2 ns while the bit duration is in the order of microseconds. The very short time occupation of the pulse inside the bit period allows very low power communications.

Among the presented modulations, the PPM modulation is the most suitable one to adopt when the symbol we want to transmit in a single period has more than one bit. In this project, in order to keep both the cost and the complexity of the transmitting and receiving chain low, we adopted the OOK modulation with a symbol corresponding to one bit.

## 1.3 Comparison between UWB localization techniques

The problem of indoor localization has raised over the years a large interest both scientific and economic. Over time, many different techniques have been implemented to increase the localization accuracy. A detailed survey on UWB localization technologies is provided in [77]. In the following sections, an overview of the most widely used techniques is provided.

#### 1.3.1 Received Signal Strength Indicator (RSSI)

The received signal strength (RSS) is an indication of the power of a radio signal received by a generic receiver and is usually expressed in dBm. Since it gives an indication of the power level of the received signal, the greater the RSSI the better reception we have. The RSSI can be used to estimate the absolute distance between two devices as long as a model for the path-loss propagation is provided and the power at a reference point is known. The RSSI can be estimated as:

$$RSSI = -10nlog_{10}(d) + A \tag{1.1}$$

Where n is the path loss exponent and A is the reference signal strength at a certain distance from the receiver. As proposed in [16], to localize an object, it is necessary

to evaluate the RSSI at three receiving stations, compute the absolute distance at each station and compare them with those of a reference node .The main advantage of using this technique is that it has very low implementation costs. However, the RSSI is strongly influenced by the fading multipath effect and by additional attenuation due to Non Line Of Sight (NLOS) conditions caused by the localization environment. This leads to poor localization accuracy.

#### 1.3.2 Time Of Flight (TOF)

The choice of using a time-based location-dependent parameter instead of powerbased one like RSSI, is associated with the higher accuracy that the time-based parameters allow to achieve [35] [41]. The TOF represents the time needed by a signal to travel from a Sensor to a Tag or viceversa. The TOF is multiplied by the speed of light to compute the distance between the two.

$$d = c \cdot TOF \tag{1.2}$$

To compute the position of a Tag it is necessary to evaluate its distance with respect to a number of Sensors (sometimes called Anchors) located in known positions and apply the multilateration algorithm

In a 2D RTLS system, in order to locate the Tags, a minimum of three Sensors is required for trilateration.

At each Sensor the distance between the Sensor itself and each Tag is computed defining a circumference with radius equal to the distance between the two and centered in the Sensor position. The intersection between the three circumferences individuated gives the position of the Tag.

The TOF based RTLS systems have stringent synchronization requirements between Sensors and Tags. When the sensors do not share the same time reference it is possible to time the communication by means of the Symmetrical Double-Sided Two Way Ranging (SDS-TWR) exchange. The TWR communication scheme, shown in Figure 1.3 performs three steps:

- The Tag broadcasts a timestamped message to all Sensors (Poll message) and wait for a reply;

- Each Sensor receives the message and replies adding the transmission time and including the Poll receiving time (Answer message);

- The Tag receives the answer from the Sensor and save the receiving time then send back a message (Final message) embedding the retransmission time.

Each Sensor receives the Final message that contains all timing informations and compute the TOF as:

$$TOF = \frac{(t_{round1} - t_{reply1}) + (t_{round2} - t_{reply2})}{4}$$

(1.3)

Figure 1.3: Symmetrical Double-Sided Two Way Ranging communication scheme

where  $t_{round1}$  is the Tag turnaround time to transmit the Poll message, wait the Sensor response and receive the response message,  $t_{round2}$  is the Sensor turnaround time to transmit the response message and receive the final response from the Tag. The  $t_{reply1}$  and  $t_{reply2}$  values are the time required by the Tag and the Sensor to reply.

This communication scheme requires the Tag to be able to transmit as well as receive (transceiver) informations from the Sensors increasing not only its hardware complexity but also its power consumption and cost.

The ToF base RTLS systems use the absolute signal propagation time to perform the localization. This technique provides high localization accuracy and, differently from those based on RSSI, do not require any fingerprinting of the surrounding environment. The main disadvantage is that it requires a transceiver Tag with more complex hardware.

#### 1.3.3 Time Difference Of Arrival (TDOA)

The localization technique based on TDOA solves the problem of synchronizing Tags and sensors by exploiting the difference of propagation time among the receiving sensors. The Tag does not need to be a transceiver anymore and can be simplified to a transmit only device. In this configuration only the Sensors share the same time base. This allows to reference the TDOA measured at each couple of Sensors to the same transmission event.

The computed TDOA are used in the Multi-lateration algorithm to compute the position of the Tags. To compute the 2D position of the Tags, a minimum number of three sensors is required.

Since the communication is unidirectional where the Tag only transmits and does not receive, this localization method is also known as One Way ranging (OWR).

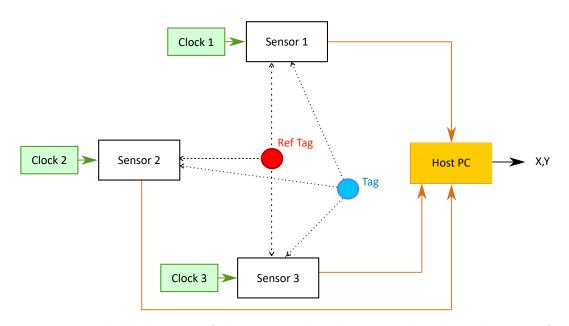

Figure 1.4: High level scheme of a TDOA based RTLS system. The Three Sensors are connected with a common clock source and to a host PC for data processing and transmission.

The crucial aspect of this solution is the time synchronization between the Sensors that must satisfy very strict requirements. For example, a difference of 1 ns in the distribution of the clock from one Sensor to another leads to an error in the position estimation of 30 cm, equal to the distance travelled by the light in 1 ns. The Sensor synchronization constraint increases the overall system installation cost as well as its complexity.

#### 1.3.4 Phase Difference Of Arrival

The Phase Difference of Arrival (PDOA) solution is implemented using an array of antennas at each Sensor and exploiting the fact that an incident plane wave does not impringe on all the antennas in the array at the same time but there is a delay in the time of arrival between two antennas associated to the distance between the antennas expressed by the formula:

$$p = d \cdot \sin(\theta) \tag{1.4}$$

Where d is the distance between the antennas,  $\theta$  is the Angle (or Direction) Of Arrival (AOA/DOA) of the impringing waveform and p is the difference in path length.

Consider a wave with carrier frequency f and wavelength  $\lambda = \frac{c}{f}$ , the PDOA  $\alpha$  is:

$$\alpha = \frac{2\pi}{\lambda} p = \frac{2\pi f}{c} p \tag{1.5}$$

From 1.5, solving for  $\theta$  one can obtain the relation between the measured PDOA and the AOA/DOA

$$\theta = \arcsin\frac{\alpha\lambda}{2\pi d} \tag{1.6}$$

With this method, using two Sensors and intersecting the AOA/DOA it is possible to determine the Tag 2D location.

The main advantage of the PDOA technique is that the Tag position in a 2D environment can be estimated with just two Sensors with a receiving array of antennas [75]. The architectures based on this technique are very sensitive to the multipath effect and the performance rapidly deteriorates in NLOS conditions.

#### 1.3.5 Existing systems available on the market

On the market, there are already various solutions with different time-based approaches, such as DecaWave [13], Ubisense [59] and Zebra [78].

The DecaWave DW1000 system uses the TWR TOF measurement approach reaching a ranging accuracy of 10 cm [8] and a typical update rate of 3.5 Hz. The update rate needs to be lowered as the number of Tags to track increases. Each device can be configured as a Sensor or Tag and, due to the TWR approach, does not need a common clock source.

Nowadays, several commercial solutions, such as Pozyx [47], TimeDomain [57], Sewio [51], Quantitec [48], and OpenRTLS [44], adopt the DecaWave chipsets. Some of these systems use the UWB TWR approach together with the information coming from an Inertial Measurement Unit (IMU) embedded in the Tag that allows generating useful attitude information. The fusion of different kinds of locationdependent parameters is used in indoor navigation systems under the name of hybrid localization [32].

The performances of this kind of systems are evaluated in [50] [11] [54]. Among them, the position accuracy and Sensor performances of the Pozyx commercial solution are evaluated in [12] and [40]. Even though systems based on hybrid localization techniques allow achieving 10-cm range accuracy, the higher complexity of the Tag hardware increases the overall solution cost.

The Ubisense system adopts the TDOA and PDOA approaches using the timedifference information determined between pairs of Sensors connected with a timing cable [53]. The system is capable to provide a localization accuracy of 15 cm and an update rate from 0.1 to 20 Hz. The performances of the DecaWave and Ubisense systems are compared in [29].

In [38], a technique that combines TDOA and TOF measurements is proposed. It is based on the DecaWave DW1000 system and, due to the combination of the two methods, allows to compensate for their respective limitations and to increase the localization accuracy in a cooperative scenario [33], [64]. The combination of the

two methods can effectively improve the accuracy of the TDOA method alone but requires a more complex architecture.

The Zebra system uses the TDOA approach and is capable to reach 30-cm localization accuracy with a maximum update rate of 200 Hz. The overall cost of the hardware infrastructure and Tags is very high compared to DecaWave and Ubisense systems but allows tracking of a large number of fast moving Tags.

#### 1.3.6 Proposed Implementation

In this work, we propose a one-way, UWB real-time locating system (RTLS) based on TDOA computation using a Sensors network where the time synchronization among the Sensors is not wired but wireless and implemented by means of a reference Tag, identical to any other Tag to track, placed in a known and fixed position. A similar approach is described in [61]. The goal is to design an RTLS system with better performances with respect to the system already on the market, designing and prototyping custom hardware, and implementing dedicated software to reduce the overall cost of the system infrastructure.

In a 2D TDOA based RTLS system, a minimum of three Sensors is required. The main disadvantage of TDOA architecture is that the Sensors require a common time base to synchronize the measurements. For this reason, we adopt a different architecture that does not require a wired common clock among the Sensors but, instead, uses a reference Tag, placed in a known fixed position to provide the required synchronization.

In this configuration, each Sensor has its own independent clock and, by comparing the TOA measurements with respect to the ones coming from the reference Tag, it is capable to compensate for the time offset among the Sensor clocks and for error drifts. The implemented architecture is the presented in Figure 1.5.

Figure 1.5: Block diagram of the proposed architecture based on the use of a reference Tag to compensate the time offset among the Sensors clocks.

## 1.4 Tag transmitted Sequence

The Tag is designed to transmit a sequence of UWB pulses. The implemented technique is based on the OOK modulation to simplify the Tag architecture. This allows to code a bit equal to one whenever we detect a pulse during a bit period. This period is set equal to 50 ns by a 20 MHz clock used to time the Tag transmission operations. The case where no pulse is detected during the bit period codes a bit equal to zero. Using this modulation we reduce the Tag's hardware complexity since we need to produce only one type of signal.

The transmitted sequence is fifteen bits long where the first 7 bits of the sequence represents the Preamble of the message while the remaining 8 bits represents the Tag ID number. The Preamble sequence is common to all Tags and is used in the Sensor processing to recognize the presence of a pulse sequence in the incoming data stream and to calculate its TOA. The successive eight bits represents the unique Tag ID number. The Tag ID number is used during the Sensor processing to associate the TOA to the specific Tag transmitting the sequence. The Tag ID can assume any possible value obtainable by the combination of 8 bits with the exception of the all zeros case.

Differently from the Tag ID, the Preamble need to have two specific characteristics in order to maximize the detection:

• It needs to maximize the sidelobe level ratio with respect to the peak of its

autocorrelation function;

• It needs to be as short as possible.

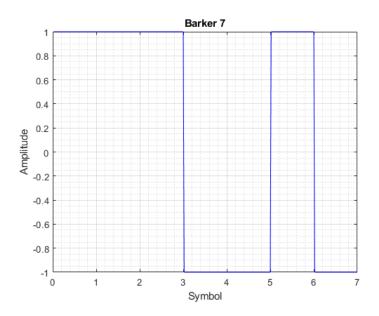

To satisfy these requirements we chose to implement the Preamble sequence using the Barker 7 sequence [31] as a good compromise between code length and performances. Other sequences, like longer Barker sequences or even longer sequences like the Golay codes were not taken into account due to their excessive length and processing requirements. Moreover, longer codes require to transmit larger amount of energy that reduces the battery duration.

A Barker code is a finite sequence of N values that can assume the values  $\pm 1$  with an autocorrelation function with coefficient defined as:

$$c_v = \sum_{j=1}^{N-v} a_j a_{j+v} \tag{1.7}$$

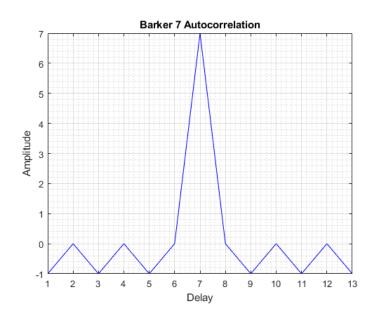

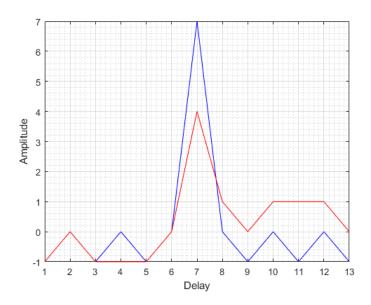

where the  $|c_v| \leq 1$  for all  $1 \leq v < N$ . This result can be interpreted as the sum of adjacent symbols should be less than or equal to 1 in all partial lengths of the sequence. This kind of sequence has the peculiar property of having an autocorrelation function with minimum sidelobe level equal to 1/N times the peak value. The Barker 7 sequence graphical representation is shown in Figure 1.6 while its autocorrelation function is shown in Figure 1.7.

The Barker sequences are commonly used in bi-phase modulation for pulse com-

Figure 1.6: Graphical representation of the Barker 7 sequence.

pression techniques in radars [63][30]. The known Barker codes are reported in

Figure 1.7: Representation of the Barker 7 sequence autocorrelation function. The peak magnitude is equal to the sequence length and the sidelobe level is kept below zero.

| Sequence Length | Codes                      | Sidelobe level ratio |

|-----------------|----------------------------|----------------------|

| 2               | +1-1                       | - 6 dB               |

| 3               | +1+1-1                     | - 9.5 dB             |

| 4               | +1+1-1+1                   | - 12 dB              |

| 5               | +1+1+1-1+1                 | - 14 dB              |

| 7               | +1+1+1-1-1+1-1             | - 16.9 dB            |

| 11              | +1+1+1-1-1-1+1-1-1+1-1     | - 20.8 dB            |

| 13              | +1+1+1+1+1-1-1+1+1-1+1-1+1 | - 22.3 dB            |

#### Table 1.3.

Table 1.3: The table reports the known Barker codes, from the shortest long only two symbols, to the longest one of thirteen symbols. On the right side is reported the sidelobe level with respect to the peak of the autocorrelation function.

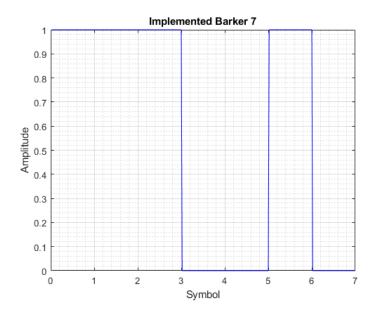

In this work, a variation of the Barker 7 sequence has been implemented due to OOK modulation. The implemented Barker 7 sequence substitutes the signal corresponding to a negative one with zeros, due to the absence of a pulse during the bit period. The graphical representation of the modified Barker 7 sequence is shown in Figure 1.8. The comparison between the autocorrelation function of the original Barker 7 sequence and the correlation between the Barker 7 sequence and our modified signal is shown in Figure 1.9. The correlation of our signal with the original Barker sequence has a lower peak value and higher sidelobes when compared to the Barker 7 autocorrelation function but represents a good trade-off between performance, complexity of implementation, and hardware cost.

The transmitted UWB pulse in each bit period is 2 ns long with a carrier frequency of 7 GHz. As already stated, the duration of the bit period is 50 ns, corresponding to a bit frequency of 20 MHz, far larger than the minimum frequency of 1 MHz required by the standard.

The time occupation of the pulse inside the bit period corresponds to a duty cycle of D = 4%: this very low value of D allows the transmission to require very low energy.

Figure 1.8: Graphical representation of the modified Barker 7 sequence.

Figure 1.9: Comparison between the autocorrelation function of the original Barker 7 sequence (in blue) and the correlation between the original Barker 7 and our modified version (in red).

## Chapter 2

## Hardware Design

## 2.1 Introduction

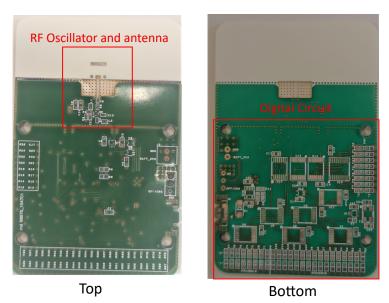

The goal of the project is to implement a low cost RTLS system; to accomplish this task, it is first necessary to identify the target hardware for both the Sensors and the Tags. The solution we implemented required the design of custom hardware for the Tag as well as for the Sensor RF receiver while, for the Sensor analog to digital conversion and processing, we initially relied on Components Off The Shelf (COTS) hardware leading us to the assembly of the first working prototype. Then we proceeded to a complete custom design both for the Tag and for the Sensor.

In the following sections the design choices, the schematics and the characteristics of the custom hardware manufactured are introduced. The discussion starts with the Sensor RF receiver, the daughter board that connects the receiving antenna to the processing part of the Sensor, and then proceeds presenting the design of the Tag low power transmitter.

Successively, the first prototype of the Sensor is introduced. In order to simplify and speed up the design process, we firstly selected evaluation boards available on the market for the analog to digital conversion and for the digital processing. The specifications of these boards will be presented together with the reasons that led us to their choice.

Once the first prototype was assembled and tested, it was time to optimize the Sensor hardware from an assembly of evaluation boards to a custom board dedicated to our application.

The discussion ends with the presentation of the final prototype of the Sensor made up of the custom processing board and RF receiver.

## 2.2 Ultra Wide Band Receiver

#### 2.2.1 UWB Receiving antenna

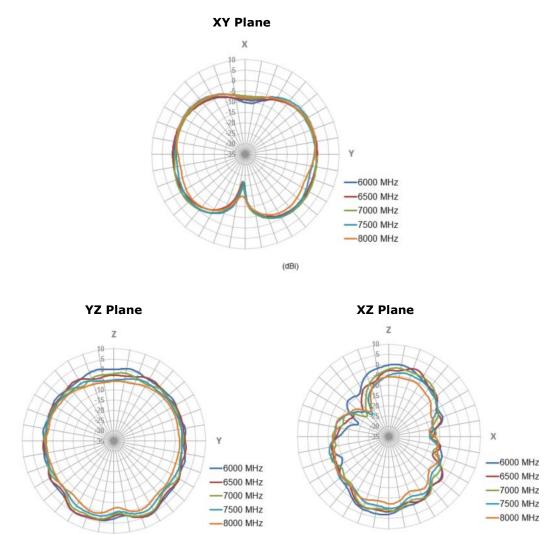

The Tag UWB pulse sequence is coded using an OOK modulation and transmitted using an elliptic dipole antenna in linear, vertical polarization. This fixes design constraints for the geometry of the receiving antenna. The antenna needs to have:

- Good matching and gain for a wide range of frequencies around the 7 GHz carrier;

- Wide angularfield of view in the horizontal plane;

- Linear vertical polarization;

- An easy connection to the receiver;

- Reasonable geometrical dimensions to satisfy the mechanical constraints imposed by the receiving Sensor enclosure.

Various solutions for UWB antennas are proposed in literature, from commercially available ceramic SMD chip solution [60] to PCB printed solutions based on different optimizations of the patch antenna geometry like in [34][46] [36][55].

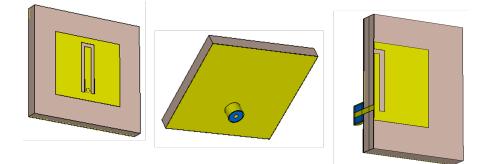

The solution we adopted is constituted by a single patch with a "U" shaped slot to increase the bandwidth. The antenna has been designed, simulated, and optimized using CST Microwave Studio software. The 3D model of the final solution is shown in Figure 2.1. The patch has been simulated on an FR-4 (lossy) substrate with a

Figure 2.1: Front, Bottom and cross section views of the final UWB receiver antenna 3D model

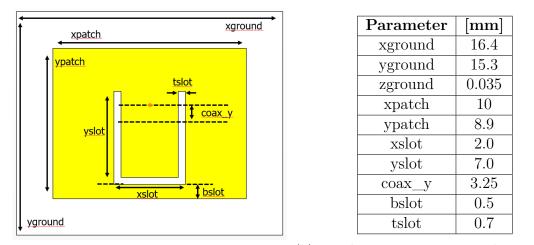

thickness of 1.6 mm and a dielectric constant  $\epsilon_r = 4.3$ . The geometrical parameters of the optimized antenna are reported in Figure 2.2a and Table 2.2b.

(a) Patch antenna geometrical parameters (b) Patch antenna geometrical parameters values

Figure 2.2: Geometrical parameters of the receiving antenna model with the corresponding values.

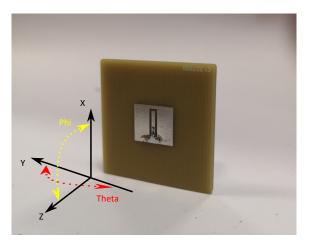

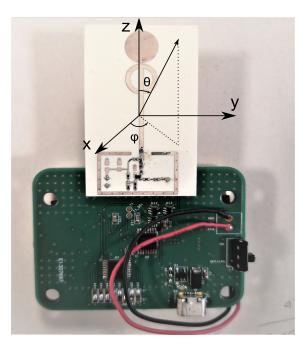

The vertical position of the feeding point for the coaxial connector determines the input impedance which has been set equal to  $50\Omega$ . The antenna has been manufactured and measured, the final prototype is shown in Figure 2.3.

The antenna has been measured in the anechoic chamber of our Institute. We

Figure 2.3: Front view of the manufactured prototype with the reference coordinates system used for measurements.

performed a spherical scan with angular steps of 5° along the  $\phi$  angle and 1° along the  $\theta$  angle measuring two orthogonal linear polarizations along  $\theta$  and  $\phi$ .

The gain of the Antenna Under Test (AUT) is obtained as:

$$G(\phi,\theta)_{dB} = 20 \cdot \log_{10}(\sqrt{G_{\theta}(\phi,\theta)^2} + G_{\phi}(\phi,\theta)^2) + KF_{dB}$$

(2.1)

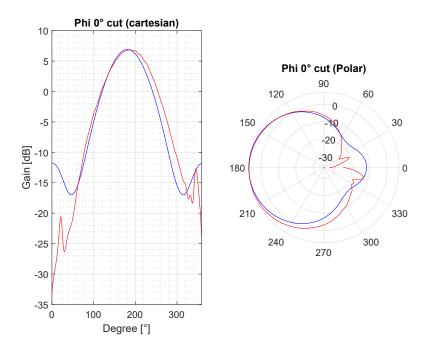

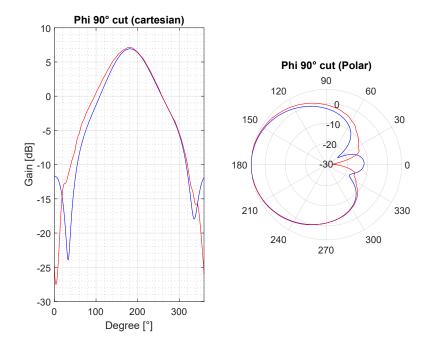

Where  $G_{\theta}(\phi, \theta)$  and  $G_{\phi}(\phi, \theta)$  are the measured polarization components and  $KF_{dB}$  is the standard-gain horn antenna probe correction factor. The obtained results are shown in Figure 2.4 and 2.5. The sidelobe level is well under -10 dB in both

Figure 2.4: Comparison between the simulation results (blue) and the measured ones (red) for the  $\phi = 0^{\circ}$  cut.

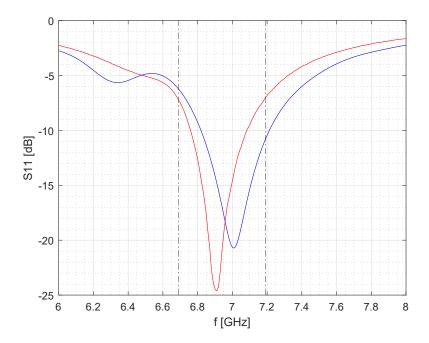

cuts, the angular width at -3 dB with respect to the maximum gain is 78° in the  $\phi = 0^{\circ}$  cut and 88° in the  $\phi = 90^{\circ}$  and matches with the simulations. The simulated maximum gain is very similar to the measured one. In Figure 2.6 the simulated and measured  $S_{11}$  at the antenna connector are shown indicating a very similar behavior with just a 100 MHz frequency shift between the two. The -10dB bandwidth of the antenna is close to 500 MHz as expected.

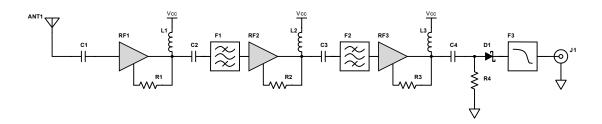

#### 2.2.2 RF Receiver: Block Diagram

The receiving antenna is connected through a SMA connector to the UWB receiver board. The high level block diagram of the receiver is shown in Figure 2.7. The receiver amplifies the signal using three cascaded Low Noise Amplifier (LNA) stages interspersed with two band pass filters centered at the carrier frequency.

Figure 2.5: Comparison between the simulation results (blue) and the measured ones (red) for the  $\phi = 90^{\circ}$  cut.

Figure 2.6: Comparison between the simulation results (blue) and the measured ones (red) of the reflection coefficient  $(S_{11})$ .

After amplification and filtering, the signal is rectified using a Schottky diode and low pass filtered to eliminate the unwanted higher frequency content.

Figure 2.7: UWB receiver block diagram

The antenna signal is DC filtered and provided to the first of three cascaded amplification stages. All three amplification stages use the same amplifier chip, the MAAL-011130 from Macom [5]. This chip is a broadband low noise amplifier with a minimum gain of 19 dB from 2 to 18 GHz and a noise figure of 1.4 dB at 10 GHz. The amplifier has a high 1 dB intercept point of 13 dBm at 6 GHz, this parameter is critical when cascading multiple amplifier with significant gain since it can cause the whole chain gain to flat if the signal received from the antenna is very high. In these situations, it is common for the third amplification stage to saturate causing the gain to drop, the noise floor to rise and the generation of distortions, visible in the received signal as the introduction of higher order harmonics.

The amplifier supports single voltage supply instead of the more common dual rail one. This allows the UWB receiver to be supplied using only one voltage simplifying the power distribution tree in the Sensor. The single voltage supply operation is enabled by connecting an external resistor between the bias control voltage pin (pin 4) and the RF/ $V_{cc}$  pin (pin 7). Since the RF output signal and the voltage supply  $V_{cc}$  rail share the same pin, it is necessary to decouple them by means of an external, integrated bias tee component. The circuit topology of such component is shown in Figure 2.8. It is important to chose a component that can fit in the design with small Insertion Loss (IL) to minimize the impact on the amplification budget and with minimum dimensions.

Figure 2.8: TCBT-14R+ schematic. The inductor let the DC voltage pass in order to supply the chip and block high frequency signal while the capacitor decouples the DC voltage supply allowing only the high frequency signal to pass.

The TCBT-14R+ from *Minicircuits* fits all the requirements, it has a low IL of 0.66 dB at the center frequency of 7 GHz, it is provided in a small package and it is cost effective. The cost of the amplifier and bias tee circuit remains in the order of 20 USD for a single piece.

After the first amplification stage we need to filter the signal. There are a lot of COTS solutions for X band filters but they are extremely expensive. In order to keep the costs as low as possible, we designed a custom Coupled Line Band Pass Filter (BPF) implemented in microstrip technology to perform the filtering operations. Figure 2.9 shows the final layout of the coupled line band pass filter. The filter has been designed and simulated in CST Microwave Studio using the

Figure 2.9: Coupled Line Band Pass Filter

RO4350B from Rogers as substrate. The datasheet of the material is available at [10]. This dielectric material has good thermal performances, very low losses  $(\tan \delta = 0.0037 \text{ at } 10 \text{ GHz})$  and a dielectric constant of  $\epsilon_r = 3.66$ . Compared with others high frequency, high performances dielectrics such as RO3003 [9] or Astra

MT77 [19], it offers comparable performances for a significantly lower cost per cm<sup>2</sup>. The simulation used a 20 mils (508  $\mu m$ ) thick substrate and dielectric constant of 3.66. The simulated copper trace thickness is fixed at 50  $\mu m$  to take into account the copper growth associated to two rounds of galvanization. The ground plane copper is 35  $\mu m$  thick. The simulation results are shown in Figure 2.10 where the relevant points to evaluate the central frequency, the filter bandwidth and the filter attenuation are highlighted. The filter input port as well as the output one are fed

Figure 2.10: Coupled line microstrip BPF simulation Results

using 50 $\Omega$  microstrip. The simulation results show a center resonance frequency at 7 GHz with a -10 dB bandwidth of  $\Delta B = 380$ MHz. The two ports are well matched having a -35 dB reflection coefficient. The filter introduces minimum attenuation of 1.1 dB on the received signal at the center frequency and deteriorates to almost 3 dB at the extremes of the filter bandwidth. This attenuation is a good tradeoff between the bandwidth of the filter and its dimensions.

The second amplification stage is identical to the first one and has the same filter at its output. The third stage is cascaded to the second filter. The output of the third stage is fed to the RF power detector circuit. The choice of using a power detector is justified by the necessity of computing the accurate time of arrival of the pulse sequence at the receiver. To perform this operation it is necessary to detect the sequence time of arrival and no further information on phase or frequency is required. Different examples of power detectors based on Schottky diodes are shown in [27]. To implement the power detector we adopted the SMS7621-079LF from Skyworks [52].

The last operation in the receiving chain is low pass filtering. There are multiple ways to implement a low pass filter; microstrip stepped impedance filters are cheap since they do not require any components but rely only on changes in the microstrip width to model an inductor or a capacitor, they can achieve any bandwidth with low insertion losses. However, their implementation requires a large amount of PCB space. Discrete component implementations are a much more compact solution and are very low cost. The order of the filter and cut-off frequency can be chosen. The main disadvantage of such solutions is the strong dependence of the transfer function on component tolerances. The adopted solution is based on integrate, ceramic chip Low Pass Filter (LPF). These components are available in standard SMD packages, do not depend on component tolerances and are 50  $\Omega$  matched. The LFCG-1200+ from Minicircuits [7] is chosen as LPF. The insertion loss behavior is shown in Figure 2.11, it is possible to see that up to 1 GHz the IL of the filter remain lower than 0.6 dB.

Figure 2.11: Integrated LPF Insertion Loss behavior

The output of the LPF is provided to an SMP connector that, throught a bullet adaptor, connects the receiver to the Sensor processing board ADC. In order to estimate the receiver amplification budget we need to take into account the gain of each amplifier and subtract the IL of all the components in the receiving chain. The total amplification budget, assuming the nominal gain of the amplifier to be 20 dBm at 7 GHz will be equal to:

$$G = 3G_{Amp} - 2IL_{BiasTee} - 2IL_{BPF} - IL_{LPF}$$

$$(2.2)$$

Substituting the obtained values in the equation we have:

$$G = 60 - 1.36 - 2.24 - 0.86 = 55.54dB \tag{2.3}$$

#### 2.2.3 RF Receiver: PCB Design

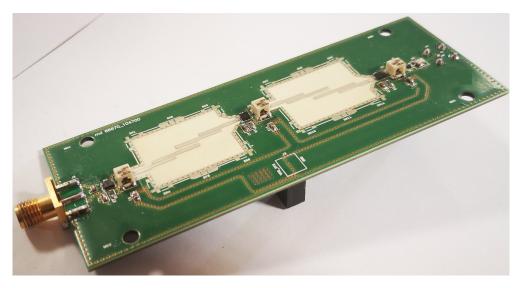

The UWB receiver has been manufactured and tested. The final view of the prototype is shown in Figure 2.12. The custom PCB of the receiver is connected to the Sensor processing board using a standard SMD in line connector for ground and voltage supply connections and an SMP connector for the received signal.

Figure 2.12: The manufactured receiver prototype. The two coupled lines BPF are shown without the metal case cover.

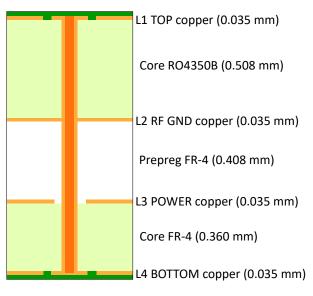

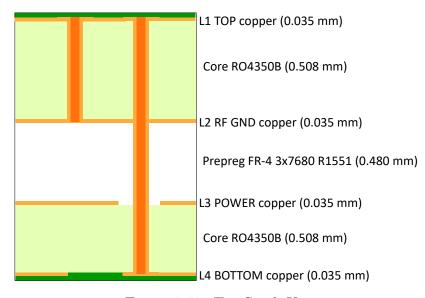

The board needs to be manufactured using RO4350B high frequency, low losses materials. To keep the costs low, an hybrid stack-up of RO4350B high frequency material and standard FR-4 has been used. The solution has four layers, the stackup of the board is shown in Figure 2.13. The first two layers are made of a 35  $\mu$ m thick copper layer standing on a 20 mils (508  $\mu$ m) RO4350B dielectric core. The top layer (L1) is used for component placing and routing while the second layer (L2), is the reference ground plane. The second core, connecting layer L3 and L4, is made up of a low cost FR-4 R-1566 1501 laminate from Panasonic [45] with nominal thickness of 14 mils (355  $\mu$ m). These two layer are used respectively for power supply routing (L3) and for component placing and ground (L4). The two cores are connected using two sheets preimpregnated (prepreg) R-1551 7628 from Panasonic with total thickness of 16 mils (406  $\mu$ m). The characteristics of the prepreg are the same as the FR-4 core mentioned above.

We choose to realize four layers to have higher separation between sensible nets

Figure 2.13: UWB receiver board Stack-Up

and noisy power lines and to increase mechanical stability. A common solution in high frequency designs to reduce interference from outside is to delimit the edges of the board with a row of through hole vias that connects the ground etching along the cross section of the board. The same concept has been applied to the microstrip filters by covering them with COTS metallic cages.

# 2.3 First Prototype Tag

# 2.3.1 Design Overview

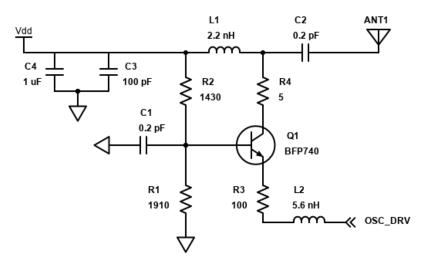

The Sensors receive the pulse sequences transmitted by UWB Tags; these devices are designed to generate the OOK modulated pulse sequence with the correct bit and sequence repetition timing. In order to keep the manufacturing costs and power consumption low, we need to generate the signal using discrete components. The implemented solution uses a single transistor based oscillator circuit that generate the 7 GHz carrier and a custom controller to modulate it. The OOK modulation transmits an UWB pulse only when the sequence has a bit equal to "1" while, when the bit is equal to "0", no pulse is transmitted. The single bit interval is fixed to 50 ns (20 MHz) and largely satisfy the requirement on minimum bit duration (1 MHz).

During the bit interval the controller needs to gate the carrier signal with 2 ns pulses in order to have the required pulse bandwidth. The Sequence Repetition Frequency as well as the pulse sequence itself, are hardwired for each Tag.

Two different Tag prototypes have been manufactured. The two designs had different focus, the first prototype had the goal to verify the feasibility of designed solution and its performances. The second prototype optimizes power consumption, dimensions, cost and performances.

In the following sections we will describe in detail the high level block diagram of both solutions and describe their differences. We will then proceed describing the custom board design and manufacturing details and discuss the performances by comparing simulations results and measurements.

# 2.3.2 Block diagram

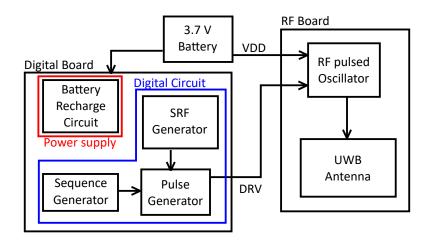

The first prototype high level block diagram is presented in Figure 2.14. The transmitter architecture can be subdivided in three macro blocks:

- The power supply block, represented by the 3.7 V battery and the battery recharge circuit;

- The digital block, made up of three different sub-blocks: the sequence generator and sequence repetition frequency generator circuits drive the pulse generator circuit. The digital circuit output is the driving signal for the RF oscillator;

- The RF block, composed by the oscillator that generates the carrier signal and the UWB antenna.

Figure 2.14: High level block diagram of the first Tag prototype

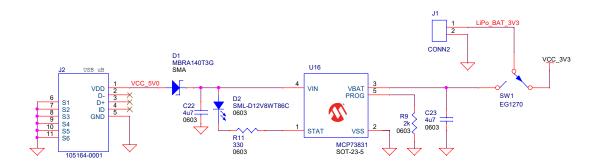

The power supply circuit schematic is shown in Figure 2.15. It is possible to notice that the Tag is powered using a 3.7 V lithium polymer (LiPo) rechargeable battery connected to the board through a Single Pole Double Through (SPDT) switch. To recharge the battery, it is necessary to power down the Tag. The digital and

Figure 2.15: Tag power supply block schematic.

RF circuits are disconnected and the battery is directly connected to the recharge circuit.

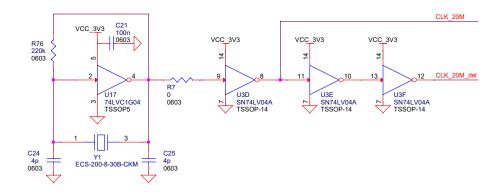

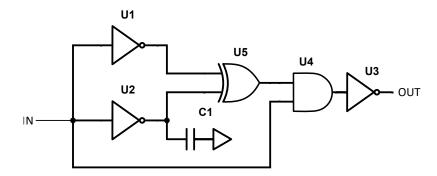

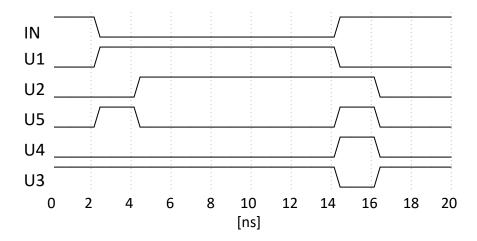

The adopted charge management controller is the MCP73831 chip from Microchip [39]. To recharge the battery, it is sufficient to connect the Tag to a USB port; the charge management controller is directly power supplied by the USB port otherwise it is kept in power down mode. The duration of the recharging process can be reduced by increasing the current that the charge management controller provides to the battery. To do that, it is sufficient to change the resistance connected to the chip's PROG pin (pin 5). We used a 2 k $\Omega$  resistor to set the maximum current value available: 500 mA. During recharge, a red LED is turned on and is kept lit until the battery is completely charged then turns off at the end of the recharge. The digital circuitry is timed by a 20 MHz reference clock signal generated by a basic CMOS crystal oscillator with feedback inverter and a decoupling inverter at the output. The schematic of the clock signal generation circuit is shown in Figure 2.16. The resulting 20 MHz clock is delayed with two cascading inverters with nominal delay of one nanosecond each. The delayed clock is used in the pulse generation circuit to window the sequence signal with a certain margin from the switching front. The digital block performs three distinct operations:

- Set the digital sequence to transmit;

- Manage the symbol and the frequency repetition timing;

- Generate the 2 ns pulses to modulate the oscillator carrier signal.

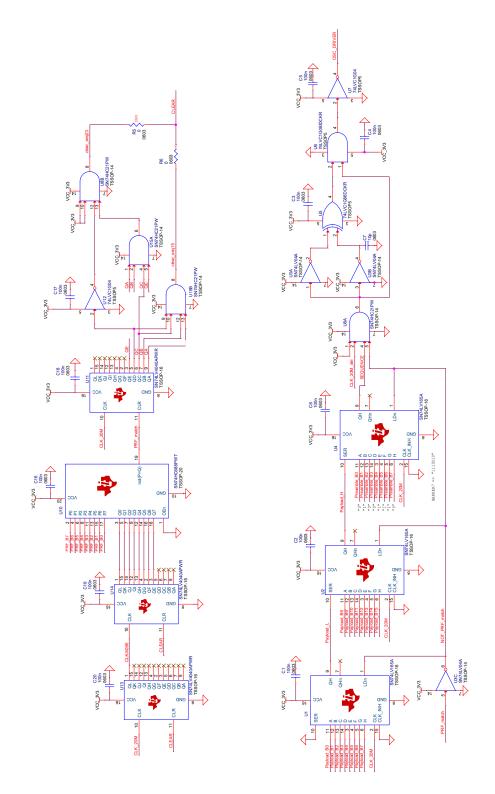

The schematic of the entire digital block is shown in Figure 2.17.

The generation of the sequence repetition timing (SRF) is performed in order to

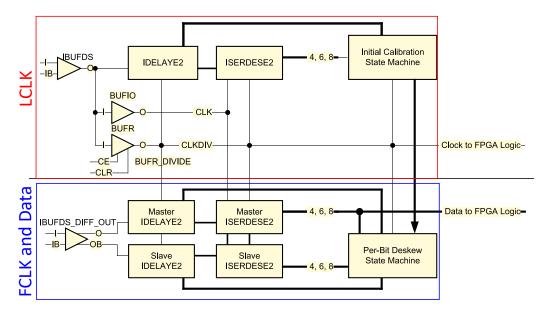

Figure 2.16: Clock generation circuit

Figure 2.17: Digital circuit schematic showing the pulse sequence, SRF timing and the short pulse generation circuits.

allows a fast reconfiguration since the SRF needs to be adjusted as the number of Tags to track changes. If the total number of Tags to track is small, we can use high SRF thus increasing the number of computed positions per second. However, as the number of Tags increases, the processing load of the Sensor increases to the point where the Sensor is not able to complete the processing of a sequence before the reception of the next. To overcome this bottleneck we have to reduce the SRF of Tags linearly as the number of Tag increases.

To accommodate the solution for a large number of SRF, we apply the frequency division technique from the 20 MHz reference clock. The frequency division circuit is implemented by two cascaded 12-bit counters shown in the bottom left corner of Figure 2.17. The first counter is clocked using the 20 MHz reference clock signal coming from the clock generation circuit while the second counter uses as clock the Most Significant Bit (MSB) signal from the first counter. In this configuration, the LSB signal of the second counter is a square wave with frequency 2<sup>12</sup> times slower than the reference 20 MHz clock.