# Distributed Nonlinear Shielding in Power Delivery Networks on Printed Circuit Boards

Torben Wendt, Cheng Yang and Christian Schuster

Institute of Electromagnetic Theory

Hamburg University of Technology

Hamburg, Germany

torben.wendt, cheng.yang, schuster@tuhh.de

Marco De Stefano, Stefano Grivet-Talocia

Dept. of Electronics and Telecommunications

Politecnico di Torino

Torino, Italy

marco.destefano, stefano.grivet@polito.it

Abstract—Nonlinear shielding from voltage spikes is commonly designed in a one dimensional setting, e.g. on transmission lines, where protection consists of a single lumped voltage clamp. This paper investigates the extension to the two dimensional case, i.e. protection from a voltage pulse between two parallel plates of a PCB. Opposed to the one dimensional case, where the protection is concentrated in a point, for two dimensional case the protection elements are arranged on a curve, creating a nonlinear fence in the two dimensional plane. It is shown that the spacing of the elements on the curve has a strong impact on the shielding effectiveness. Additionally, the effect of resistive losses in the voltage clamps is investigated.

*Index Terms*—Electrostatic Discharge, ESD, Power Delivery Network, PCB, nonlinear, macromodeling, voltage suppressor, diodes, nonlinear, multiport

#### I. Introduction

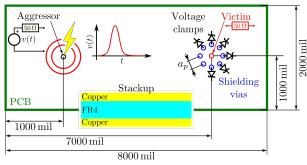

A widespread application of nonlinear shielding is the protection from electrostatic discharge (ESD), which can impair the functioning of a device and potentially damage it. In order to harden a device against ESD, protection components such as voltage clamps are added to the system. These elements generally exhibit nonlinear behaviour and function by suppressing transient voltage spikes above a certain threshold. Usually, the voltage spike travels along a transmission line towards a victim and can be reflected by a single nonlinear element located at a point between aggressor and victim. This is not the case for a voltage spike propagating in a plane, e.g. on a PCB, where the fields travel around a single protection element to reach the victim. Additionally, the angle of incidence of the pulse may not be clearly defined due to multi-path propagation via the edges of the PCB, which indicates that protection of the victim from all sides is advisory. This can be achieved by placing multiple vias on a closed curve around the victim in the power plane, which collectively form a reflecting wall for incident waves if the voltage exceeds a defined threshold due to termination with voltage clamps, as shown in Fig 1. Recently, the three dimensional case has been investigated in [1]-[3], where the victim is shielded from fields in three dimensional space by nonlinear elements spread across a plane. The PCB topology investigated in this paper is shown in Fig. 1 with the dimensions as follows; via radius is 5 mil, antipad radius is

This work is supported by the German Research Foundation.

Fig. 1: Nonlinear shielding PCB topology in a two dimensional setting. A high voltage pulse is injected into the aggressor port and excites the parallel plate resonator. The red victim port is surrounded by voltage clamps forming a nonlinear shield against the incident fields.

8 mil, copper thickness is  $1.2 \, \text{mil}$  and dielectric thickness is  $10 \, \text{mil}$ . On the left, the aggressor injects a high voltage spike through a voltage generator into the parallel plate resonator formed by the two copper sheets separated by a dielectric. On the right, protection of the red victim via is deployed by enclosing it in a circle of blue shielding vias, which are terminated with voltage clamps forming the nonlinear shield. The objective is to achieve high attenuation of the voltage observed in the victim load. This paper investigates the effect of changing the via pitch  $a_p$  of the shielding vias on the achieved attenuation, as well as the effect of resistive parasitics in the voltage clamps using a macromodel based hybrid simulation approach [3]–[5] for efficient simulation.

# II. METHODOLOGY

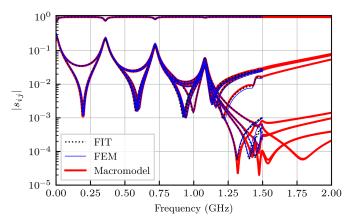

We start by computing the tabulated scattering response  $\check{\mathbf{S}}(j\omega_n)$  of the linear PCB structure with the diodes removed using a linear field solver, e.g. Finite-Element Method (FEM) [6] or Finite Integration Technique [6] shown in Fig. 2. The resulting  $\check{\mathbf{S}}(j\omega_n)$  is then subject to a standard Vector Fitting (VF) process [7], [8] followed by passivity enforcement, yielding the Positive Real rational function

$$\mathbf{S}(s) = \sum_{l=1}^{L} \frac{\mathbf{R}_l}{s - p_l} + \mathbf{R}_0. \tag{1}$$

where s is the complex frequency (Laplace variable),  $p_l$  are the poles of the model, here assumed to be common to all transfer

Fig. 2: Magnitude of scattering parameters obtained using linear full wave solvers FIT and FEM compared to passive macromodel extracted from the FIT scattering data.

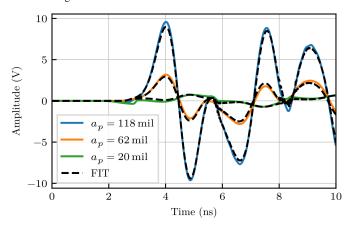

Fig. 3: Voltage across a  $50\,\Omega$  termination connected to the victim via for three different via pitches  $a_p$  under Gaussian pulse excitation obtained using the hybrid approach compared to FIT. A higher density of nonlinearly loaded vias leads to a better shielding.

function entries in order to model correctly global resonances,  $\mathbf{R}_l$  are the residues corresponding to the poles  $p_l$  and  $\mathbf{R}_0$  capture direct coupling. Using standard methods [8] the model (1) can be evaluated in time domain using recursive convolution [9]. The aggressor port of the structure is then terminated by a voltage generator with internal resistance  $50\,\Omega$  and open circuit voltage v(t), the victim port is loaded with a  $50\,\Omega$  load and the shielding vias are loaded with voltage clamps as defined in Fig. 5. The port voltage is then computed by using a windowed Newton-Krylov solver [10], similar to [5]. Validation of the adopted method is presented in Fig. 3, which compares the victim port voltages of the adopted method to the results obtained using Finite Integration Technique (FIT) [6] for three different values of  $a_p \in \{118\,\mathrm{mil}, 62\,\mathrm{mil}, 20\,\mathrm{mil}\}$ , excited by a Gaussian pulse

$$v(t) = \hat{v}e^{at^2}, \quad a = \frac{(\pi f_c b_w)^2}{4 \cdot \log(10^{\frac{b_w r}{20}})},$$

(2)

where  $\hat{v}=10\,\mathrm{kV}$  is the pulse amplitude,  $f_c=200\,\mathrm{MHz}$  is the center frequency,  $b_w=4.7$  is the fractional bandwidth and  $b_{wr}=-6$  is the reference level in dB at which the fractional bandwidth is calculated.

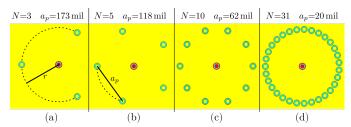

Fig. 4: Top view of four investigated nonlinear shielding via arrangements on a two layer PCB with different via densities with (a) three, (b) five, (c) ten and (d) 31 shielding vias aranged on a circle with radius  $r=100\,\mathrm{mil}$ . Copper plating is shown in yellow and the dielectric in turquoise. The aggressor (not shown) is located  $6000\,\mathrm{mil}$  to the left of the victim (red marking), which is located in the center of the different shielding circles. The leftmost shielding via is always located in the line of sight between aggressor and victim.

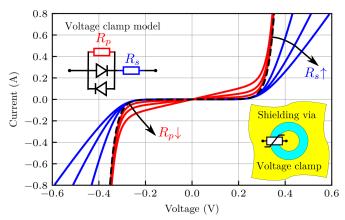

Fig. 5: Voltage-current characteristic of voltage clamps with parallel and in series parasitic resistance. The two terminals of the clamp are connected to the top and bottom copper planes.

## III. RESULTS AND DISCUSSION

In order to quantify the attenuation performance of different nonlinear shields we define the Shielding Effectiveness (SE)

$$SE := \max |\boldsymbol{v}_{v}^{Ref}(t)| / \max |\boldsymbol{v}_{v}(t)|, \tag{3}$$

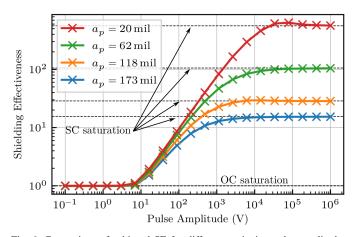

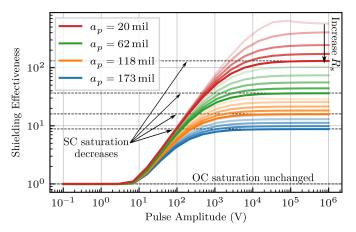

where  $v_v^{\text{Ref}}(t)$  is the voltage under reference conditions across the victim load, e.g. with no shielding and  $v_v(t)$  the voltage with shielding applied, yielding a measure of the additional attenuation compared to no shielding where larger values imply better performance. Figure 6 compares the SE for the different shielding arrangements from Fig. 4 under Gaussian pulse excitation (2) for a wide range of pulse amplitudes and indicates that the number of shielding vias does not affect the SE if the voltage clamps are in the non-conducting state due to a weak excitation. Here, the shielding vias are effectively terminated with an open circuit (OC) denoted by the lowest black dashed line, which shared by all configurations. Increasing the amplitude of the excitation increases the voltage clamps conductivity, which eventually leads to saturation of the SE, which corresponds to the shielding achieved if all vias are shorted (black dashed lines). Opposed to the OC saturation, the short circuit (SC) saturation depends on  $a_p$ , where the attenuation is higher for smaller  $a_p$ . Figure 7 shows the effect of adding series parasitic resistance  $R_s$  as depicted

Fig. 6: Comparison of achieved SE for different excitation pulse amplitudes for the four investaged PCB configurations.

Fig. 7: The SE saturation level for strong excitations decreases with increasing parasitic series resistance. The series resistance is linearly increased from  $0\,\Omega$  (lowest opacity) to  $180\,\mathrm{m}\Omega$  (highest opacity).

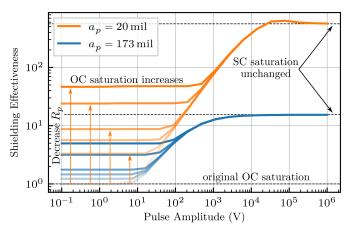

in Fig. 5 on the SE and demonstrates that increasing the series resistance decreases the SC saturation level relevant for strong excitations, while the OC level remains unchanged. The effect is more pronounced for the high density shield (small  $a_p$ ) which has more ports resulting in a smaller condensed parallel resistance. Figure 8 shows the effect of parallel parasitic resistance  $R_p$  as depicted in Fig. 5 on the SE and demonstrates that decreasing the parallel resistance increases the OC saturation relevant for weak excitations, while the SC level of each configuration remains unchanged, where the values for  $R_p$  are selected to demonstrate the effect. The effect is again more pronounced for the high density shield which has more ports resulting in a smaller condensed parallel resistance. This shows that the effects of  $R_s$  and  $R_p$  are decoupled, where  $R_s$  effects the SC and  $R_p$  the OC saturation. However, the separation of the OC and SC levels is always decreased by adding parasitic resistance, making the nonlinear shielding effect less pronounced.

### IV. CONCLUSION

We presented a nonlinear shielding technique for a two dimensional PDN problem on PCBs. The shielding effectiveness

Fig. 8: The SE saturation level for weak excitations increases with decreasing parasitic parallel resistance. The parasitic parallel resistance is replaced by an open circuit (lowest opacity),  $10\,\Omega$ ,  $5\,\Omega$ ,  $3\,\Omega$ ,  $1\,\Omega$  and  $0.5\,\Omega$  (highest opacity).

of vias loaded with voltage clamps was simulated, validated and the effect of parasitic resistance in the voltage clamps was studied. It was shown that smaller shielding via pitch leads to better shielding for strong excitations, whereas the shielding for weak excitations remains unaffected for the investigated setups. All investigated cases showed that the nonlinear SE saturated at the equivalent levels of open and short circuit terminations for weak and strong excitations, respectively. Adding parallel or series parasitic resistance influenced the weak or strong excitation saturation levels, but the separation of the levels always decreased.

#### REFERENCES

- C. Yang, P. Liu, H.-D. Brüns, and C. Schuster, "Design aspects for HIRF protection of a rectangular metallic cavity using energy selective diode grids," in 2016 Asia-Pacific International Symposium on Electromagnetic Compatibility (APEMC), 5 2016.

- [2] C. Yang, T. Wendt, M. D. Stefano, M. Kopf, C. Becker, S. Grivet-Talocia, and C. Schuster, "Analysis and optimization of nonlinear diode grids for shielding of enclosures with apertures," *IEEE Transactions on Electromagnetic Compatibility*, vol. nil, no. nil, pp. 1–12, 2021.

- [3] T. Wendt, C. Yang, H. D. Brüns, S. Grivet-Talocia, and C. Schuster, "A macromodeling-based hybrid method for the computation of transient electromagnetic fields scattered by nonlinearly loaded metal structures," *IEEE Transactions on Electromagnetic Compatibility*, vol. 62, no. 4, pp. 1098–1110, 2020.

- [4] T. Wendt, C. Yang, S. Grivet-Talocia, and C. Schuster, "Numerical complexity study of solving hybrid multiport field-circuit problems for diode grids," September 2019. International Conference on Electromagnetics in Advanced Applications (ICEAA 2019).

- [5] S. B. Olivadese and S. Grivet-Talocia, "Transient analysis of high-speed channels via newton-gmres waveform relaxation," in 2012 IEEE 21st Conference on Electrical Performance of Electronic Packaging and Systems, p. nil, 10 2012.

- [6] Dassault Systems, "Microwave Studio." https://www.cst.com, 2019.

- [7] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting," *IEEE Transactions on Power Delivery*, vol. 14, no. 3, pp. 1052–1061, 1999.

- [8] S. Grivet-Talocia and B. Gustavsen, *Passive Macromodeling*. John Wiley & Sons, Inc, 2015.

- [9] V. Loggia, S. Grivet-Talocia, and H. Hu, "Transient simulation of complex high-speed channels via waveform relaxation," *IEEE Transac*tions on Components, Packaging and Manufacturing Technology, vol. 1, no. 11, pp. 1823–1838, 2011.

- [10] "SciPy documentation." https://docs.scipy.org/doc/scipy/reference/ generated/scipy.optimize.newton\_krylov.html. Accessed: 2021-07-29.