$\label{eq:Doctoral Dissertation} Doctoral Program in Control and Computer Engineering (33^{rd} cycle)$

# Effective techniques for systems validation and security

Aleksa Damljanovic

\* \* \* \* \* \*

Supervisor Prof. Giovanni Squillero, Supervisor

#### **Doctoral Examination Committee:**

Prof. Giorgio di Natale, Referee, CNRS - TIMA Prof. Mottaqiallah Taouil, Referee, Delft University of Technology Prof. Alberto Tonda, Institut national de la recherche agronomique Prof. Stefano Quer, Politecnico di Torino Prof. Bartolomeo Montrucchio, Politecnico di Torino

> Politecnico di Torino 17th September, 2021

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

.....

Aleksa Damljanovic Turin, 17th September, 2021

# Acknowledgements

To my parents without whom I would never be the person I am today, to my other half - my brother, to my grandparents who gave me so much love.

I don't have many close and special friends in my life, but those I have I keep close to my heart. During last three years I've missed them so much, nevertheless, they were my support and strength. Thank you Aleksandra, Sofija, Adam, Petar, Ruzica and Andrijana for being the part of my life. Many thanks to a colleague and first new friend in Turin, Esteban Josie Rodriguez Condia, to my friend, roommate and professor of Italian (and Sicilian) language, Andrea Floridia, and someone with the kind heart and beautiful smile (to whom I have been the worst ski instructor) Annachiara Ruospo.

I would like to thank Matteo Sonza Reorda for giving me his trust and opportunity to do a PhD, and Giovanni Squillero for his undivided support as my tutor. I would also like to thank Ernesto Sanchez for his collaboration and Riccardo Cantoro for helping me to start my research.

Artur Jutman and Anton Tsertov from Testonica deserve thanks from my side for their industrial expertise and fruitful discussions that were essential for my research.

Special thanks go to all people involved in the RESCUE project during 3 years of joint research.

Without all of these people, this thesis would never see the light of the day and my life would never be the same. This journey was an extraordinary life experience; it was not only a school of PhD but also a school of life. Ko sme taj može, ko ne zna za strah, taj ide napred.

### Abstract

The increasing number of embedded instruments used to perform test, monitoring, calibration and debug within a semiconductor device has called for a brand new standard—the IEEE 1687. Such a standard resorts to a *Reconfigurable Scan Network* to provide efficient, reliable and flexible access to instruments and to handle complex structures. As it has to deliver reliable service, many approaches, both formal and simulation-based, have been proposed in the literature to perform test, diagnosis, and verification of such networks.

So far, most of the test-generation approaches were either too computationally demanding to be applied in complex cases, or too approximate to yield high-quality tests. A recent idea has been exploited in this thesis in a following manner: the state of a generic reconfigurable scan chain is modelled as a finite state automaton and a low-level fault, as an incorrect transition; it then proposes a new algorithm for generating a functional test sequence able to detect all incorrect transitions far more efficiently than previous ones. Such an algorithm is based on a greedy search, and it is able to postpone costly operations and eventually minimize their number. Experimental results demonstrate that the proposed approach is broadly applicable; has limited computational requirements; and the test sequences are order of magnitudes shorter than the ones previously generated by approximate methodologies. Together with testing the system for defects that may affect the scan chains themselves, the diagnosis of such faults is also important. Therefore, a method has been proposed for generating stimuli to precisely identify permanent high-level faults in a IEEE 1687 reconfigurable scan chain. A chapter is dedicated to the problem of post-silicon validation of a network, a problem that has not been adequately addressed, yet. The mismatches between the specification and its silicon implementation were analyzed, and then a methodology was proposed to detect a subset of them by applying functional patterns and observing the length of the active scan path.

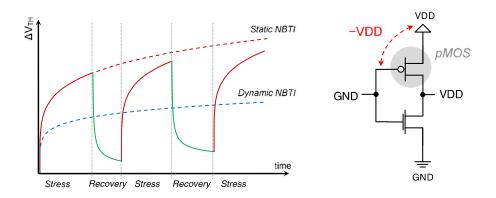

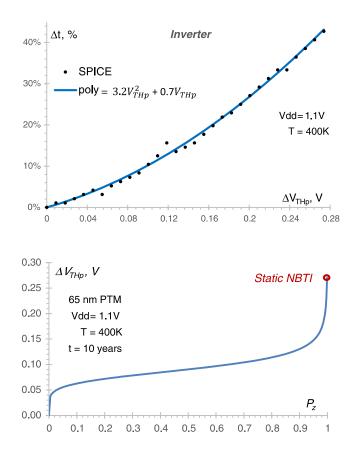

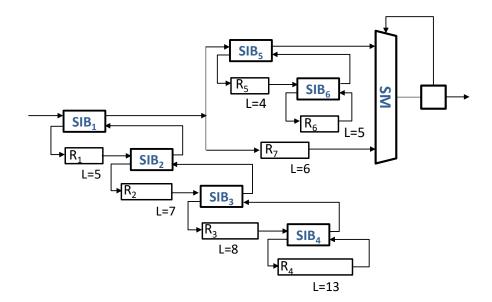

While reconfigurable scan networks are commonly used to provide fault management and embedded instrumentation access, such as safety mechanisms, in advanced safety- and mission-critical electronic systems, a failure in such infrastructure itself has a high severity. Another aspect this thesis addressed is assessment and mitigation of NBTI aging induced delays in logic paths within IEEE 1687 IJTAG Reconfigurable Scan Networks. This methodology is based on a scalable hierarchical (transistor-to-architecture) modelling of the NBTI impact on timingcritical logic paths in RSN implementations. The evaluation implies analysis of gate input signal probabilities based on the configurations and test data selected for the RSN infrastructure.

A fundamental part of the new IEEE Std 1687 is the Instrument Connectivity Language (ICL), which allows for abstract description of the scan network. The big novelty if compared to legacy solutions like BSDL is the possibility of describing new topology-enabling elements such as the ScanMuxes in a behavioural way which can be easily and efficiently exploited by Test Generation Tools to retarget instrument-level operations to top-level patterns. This means that for a given design, the Developer will have to write both the RTL and the ICL descriptions: to the author's best knowledge there is no automated tool to make the translation RTL to ICL. This methodology is error-prone due to the human factor, the difference in intent in the two descriptions and the syntactic and semantic complexity of the languages. Incoherence between ICL and RTL will result in retargeting errors, so it is fundamental to validate the equivalence between the two descriptions. In this thesis an automated methodology is presented that starting from the ICL description is able to generate a set of RTL testbenches that can be simulated against the original RTL model to detect discrepancies and incoherence, and provides quantitative metrics in terms of code and functional coverage.

Experimental results for these approaches are reported on the set of ITC2016 set of benchmark networks.

Recent trends in integrated circuits industry include decentralization of the production flow by involving different integration teams, third-party IP vendors and other untrusted entities. As a result, this is opening up a door to new types of attacks that may lead to devastating consequences, such as denial of service or data leakage. Therefore, the problem of ensuring hardware security has gained much attention in the last years, especially early in the design cycle, when an attacker may insert malicious circuitry at register transfer (RT) or gate level – a Hardware Trojan. Due to the increased complexity of modern devices, the research community is spending a lot of effort in developing more sophisticated detection methodologies and smarter attacks. However, the main problem is that they are validated on the existing benchmarks that do not reflect the real complexity. Trying to fill this gap, this thesis proposes a set of RT-Level Hardware Trojan benchmarks injected in a RISC-based pipelined microprocessor core. To prove the viability, the impacts on area, power and frequency are presented and discussed. For any proposed Hardware Trojan, the functional description, the implementation details and the effects once activated are provided.

Furthermore, despite the considerable effort that has been invested in this area, the evergrowing complexity of the modern devices always calls for sharper detection methodologies. In this regard, the last chapter of the thesis illustrates a pre-silicon, simulation-based techniques to detect Hardware Trojans. The technique exploits well-established machine learning algorithms. All of the background concepts are presented together with the methodology and the automatized flow. The validity of the approach has been demonstrated on the *AutoSoC* CPU, an industrial-grade, safety-oriented, automotive benchmark suite. Experimental results demonstrate the applicability and effectiveness of the approach: the proposed technique is highly accurate in pinpointing suspicious code sections. None of the Trojans from the set has been left undetected.

# Contents

| Li | st of          | Table  | S                                                                   | XIII |

|----|----------------|--------|---------------------------------------------------------------------|------|

| Li | st of          | Figur  | es                                                                  | XV   |

| In | trod           | uction |                                                                     | 1    |

| Ι  | $\mathbf{IJ}'$ | TAG    | Reconfigurable Scan Networks Dependability                          | 7    |

| 1  | Bac            | kgrou  | nd                                                                  | 9    |

|    | 1.1            |        | 1149.1 – JTAG                                                       | 10   |

|    | 1.2            | IEEE   | 1687 – IJTAG                                                        | 10   |

|    | 1.3            | Relate | ed works                                                            | 15   |

|    | 1.4            | IEEE   | 1687 Benchmark RSNs                                                 | 17   |

| 2  | Tes            | t      |                                                                     | 19   |

|    | 2.1            | Fault  | model                                                               | 19   |

|    | 2.2            | Test p | procedure                                                           | 20   |

|    | 2.3            | A Sen  | ni-Formal Test Generation Technique for Reconfigurable Scan         |      |

|    |                | Netwo  | orks                                                                | 23   |

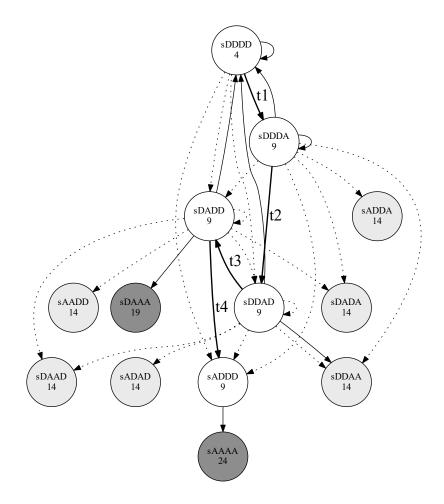

|    |                | 2.3.1  | Network representation: FSA                                         | 24   |

|    |                | 2.3.2  | Greedy search algorithm                                             | 25   |

|    | 2.4            | Enhar  | nced version                                                        | 27   |

|    |                | 2.4.1  | Search algorithm                                                    | 28   |

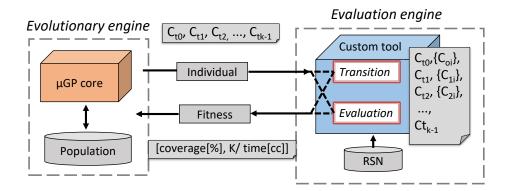

|    | 2.5            | Evolut | tionary approach to test reconfigurable modules in RSNs $\ .$ $\ .$ | 30   |

|    |                | 2.5.1  | Methodology Basics                                                  | 32   |

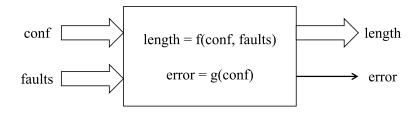

|    |                | 2.5.2  | Transition function                                                 | 34   |

|    |                | 2.5.3  | Evolutionary algorithm                                              | 36   |

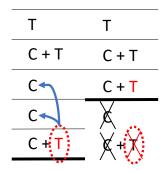

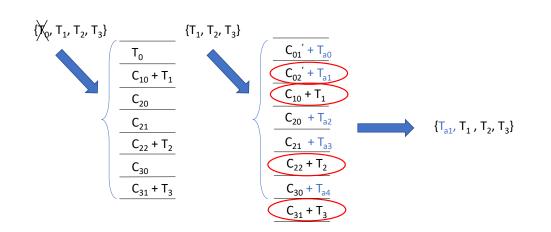

|    |                | 2.5.4  | Individual encoding                                                 | 37   |

|    |                | 2.5.5  | Post-processing techniques                                          | 41   |

|    | 2.6            | Exper  | imental Results                                                     | 43   |

|    |                | 2.6.1  | Experiments for FSA approaches from Section 2.3 and Sec-            |      |

|    |                |        | tion 2.4                                                            | 43   |

|    | 2.7 | 2.6.2 Experiments for Evolutionary approach from Section 2.5 Chapter Summary | $\frac{47}{53}$ |

|----|-----|------------------------------------------------------------------------------|-----------------|

| 3  | Dia | gnosis                                                                       | 55              |

| Ű  | 3.1 | Fault model and Diagnostic Mechanism                                         | 56              |

|    | 3.2 | Proposed Diagnostic Methodology                                              | 61              |

|    | 0.2 | 3.2.1 Finite State Automaton to model an RSN                                 | 61              |

|    |     | 3.2.2 Search Algorithm                                                       | 64              |

|    |     | 3.2.3 Diagnostic analysis                                                    | 65              |

|    | 3.3 | Experimental Results                                                         | 68              |

|    | 3.4 | •                                                                            |                 |

|    | 0.4 | Chapter Summary                                                              | 12              |

| 4  | NB  | TI-induced aging analysis in IEEE 1687 RSNs                                  | 73              |

|    | 4.1 | Hierarchical Modelling of the NBTI-Induced Delays                            | 74              |

|    | 4.2 | Proposed approach: analysis and mitigation                                   | 76              |

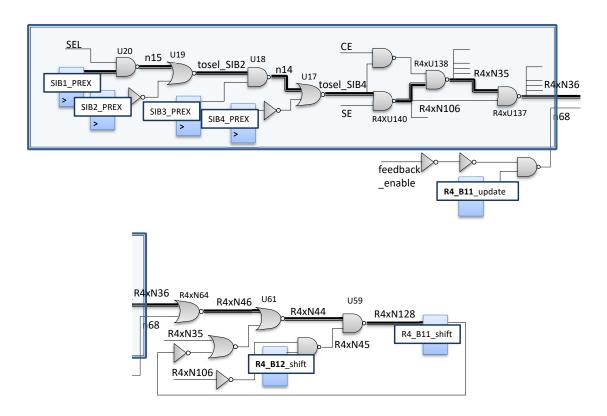

|    | 4.3 | Case study                                                                   | 78              |

|    | 4.4 | Experimental results                                                         | 80              |

|    | 4.5 | Chapter summary                                                              | 82              |

| 5  | Pos | t-silicon validation                                                         | 83              |

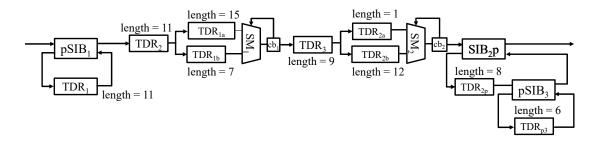

|    | 5.1 | Proposed "black-box" approach to post-silicon validation                     | 84              |

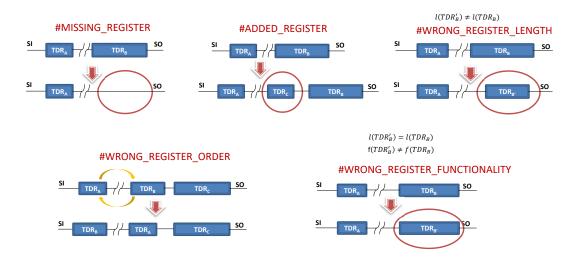

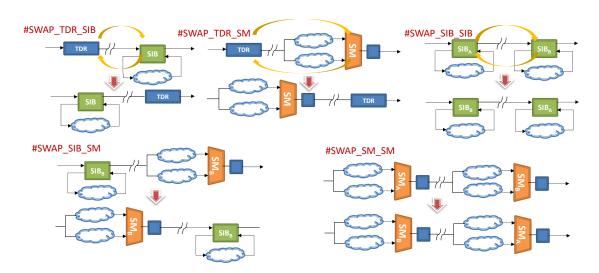

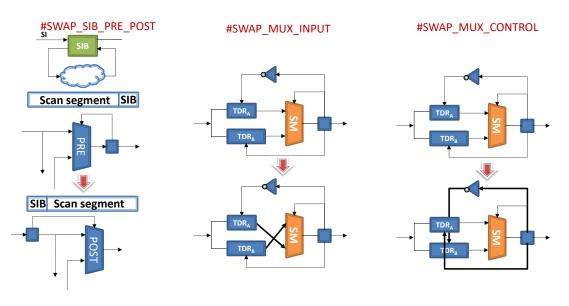

|    |     | 5.1.1 Mismatch model                                                         | 84              |

|    |     | 5.1.2 Undetectable mismatches                                                | 87              |

|    |     | 5.1.3 Detection mechanism                                                    | 89              |

|    |     | 5.1.4 Configuration generation procedure                                     | 90              |

|    | 5.2 | Experimental results                                                         | 92              |

|    | 5.3 | Chapter summary                                                              | 94              |

|    |     |                                                                              | -               |

| 6  |     | ulation-based equivalence checking between IEEE 1687 IC                      |                 |

|    |     | I RTL                                                                        | 99              |

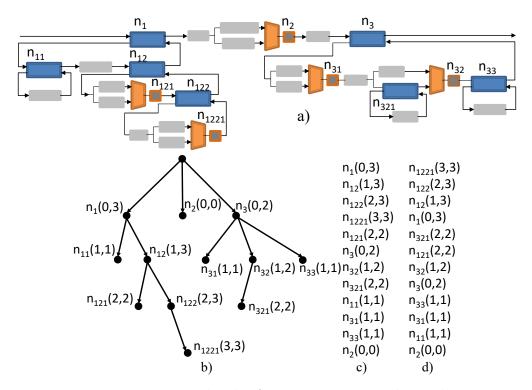

|    | 6.1 | ICL                                                                          | 100             |

|    | 6.2 | Proposed approach                                                            |                 |

|    |     | 6.2.1 Post-silicon validation approach                                       | 102             |

|    |     | 6.2.2 Application to RTL Equivalence                                         | 104             |

|    | 6.3 | Experimental Results                                                         | 105             |

|    |     | 6.3.1 Setup                                                                  | 105             |

|    |     | 6.3.2 Results                                                                | 107             |

|    | 6.4 | Chapter summary                                                              | 110             |

| Su | ımm | ary of Part I                                                                | 111             |

| Π  | Н                  | ardware Security: Hardware Trojans 1                                                                                                                                            | .13                                                                                     |

|----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 7  | <b>Bac</b><br>7.1  | Related Works                                                                                                                                                                   | $115 \\ 116 \\ 117 \\ 117 \\ 117$                                                       |

| 8  |                    | Hardware Trojans       Trojan Implementation and Analysis                                                                                                                       | 119<br>120<br>123<br>127                                                                |

| 9  |                    | Design Verification and ML concepts9.1.1Digital Design Verification9.1.2Artificial Neural Networks9.1.3Support Vector Machine9.1.3Support Vector MachineProposed Detection Flow | 129<br>130<br>131<br>131<br>133<br>136<br>138<br>141<br>142<br>143<br>143<br>146<br>148 |

| Su | 9.4<br>1 <b>mm</b> |                                                                                                                                                                                 | 150 $153$                                                                               |

|    |                    |                                                                                                                                                                                 | 155 $159$                                                                               |

|    | ~                  |                                                                                                                                                                                 | - 50                                                                                    |

# List of Tables

| 1.1 | Set of possible configurations of the RSN in Fig. 1.6.                   | 16  |

|-----|--------------------------------------------------------------------------|-----|

| 1.2 | ITC'16 benchmark networks list                                           | 18  |

| 2.1 | Test procedure for the network in Fig.1.6                                | 22  |

| 2.2 | Test procedure for the network in Fig.1.6                                | 25  |

| 2.3 | Enhanced test procedure for the network in Fig.1.6                       | 31  |

| 2.4 | List of faults excited by the RSN in Fig. 1.6.                           | 34  |

| 2.5 | List of undetectable faults                                              | 45  |

| 2.6 | IEEE 1687 test algorithm experimental results                            | 45  |

| 2.7 | Experimental comparison of the enhanced algorithm $(FSA_2)$ – Sec-       |     |

|     | tion 2.4 against the previous version [51] – Section 2.3, a Depth-       |     |

|     | first algorithm [25], and an Evolutionary approach [27]. Columns         |     |

|     | ending with "vs." show the comparison against the current result;        |     |

|     | percentages quantify how much the results delivered by the previous      |     |

|     | approaches are worse                                                     | 46  |

| 2.8 | Experimental results on the ITC'16 benchmark networks                    | 51  |

| 2.9 | Comparison of the experimental results with the approaches from          |     |

|     | [25] and $[27]$                                                          | 52  |

| 3.1 | Set of possible scan-chain fault models and their effect on the inserted |     |

|     | pattern 00110011                                                         | 57  |

| 3.2 | Set of possible configurations of the RSN in Fig. 3.1 (top)              | 59  |

| 3.3 | Diagnostic procedure for the network in Fig.3.3                          | 68  |

| 3.4 | Benchmark networks list                                                  | 70  |

| 3.5 | IEEE 1687 algorithm experimental results                                 | 71  |

| 3.6 | Experimental comparison of the proposed algorithm vs. $[22]$             | 72  |

| 4.1 | Experimental results                                                     | 81  |

| 5.1 | List of considered and injected mismatches for the network from          |     |

|     | Fig. 5.1                                                                 | 86  |

| 5.2 | Post-silicon validation experimental results                             | 97  |

| 6.1 | Benchmark networks list                                                  | 106 |

| 6.2 | Experimental results on RSN benchmarks for 3 types of mutations          |     |

|     | showing the range of obtained coverage for mutated RTLs                  | 109 |

| 8.1 | Number of RTL Hardware Trojan benchmarks available on Trust-            |     |

|-----|-------------------------------------------------------------------------|-----|

|     | Hub [80] [92]                                                           | 120 |

| 8.2 | Trojan Benchmarks Description                                           | 121 |

| 8.3 | Synthesis results                                                       | 125 |

| 9.1 | Experimental results of the four SVM classifiers with different kernels |     |

|     | and following metrics: Recall, Accuracy, Precision, and F1-score        | 146 |

| 9.2 | Experimental results of the NN                                          | 149 |

| 9.3 | Meaning of the confusion matrix in the context of HT detection          | 149 |

# List of Figures

| s and TAP controller $.$ 11             |

|-----------------------------------------|

|                                         |

| ed schematic (left) and                 |

|                                         |

| (left) and symbol (right) 13            |

|                                         |

|                                         |

| tions for fault-free and                |

|                                         |

|                                         |

|                                         |

| 41                                      |

|                                         |

|                                         |

| age as a reference one;                 |

| ; the bottom one with                   |

| Í input segments 58                     |

| from Fig. 3.3 63                        |

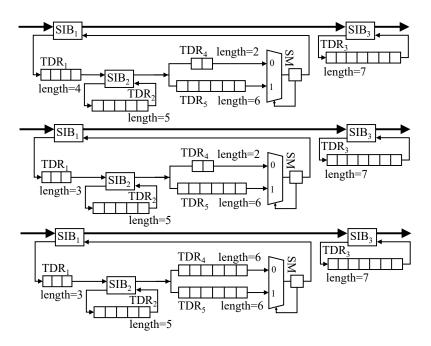

| $1 \text{ length of } 5 \dots \dots 67$ |

| for network from Fig.                   |

|                                         |

| ld voltage in a pMOS                    |

|                                         |

| of signal probability $P_z$             |

| voltage threshold shift                 |

|                                         |

| SM, six SIBs and seven                  |

| 70                                      |

|                                         |

| n in the case-study RSN 80              |

|                                         |

|                                         |

| 5.2  | Mismatches involving TDRs                                                                | 87  |

|------|------------------------------------------------------------------------------------------|-----|

| 5.3  | ScanMux and SIB position mismatches                                                      | 88  |

| 5.4  | SIB type, ScanMux control lines and input mismatch                                       | 88  |

| 5.5  | ScanMux configuration mismatches                                                         | 89  |

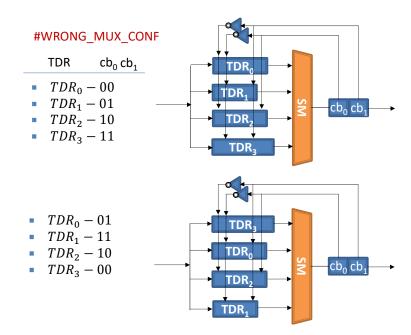

| 5.6  | Hierarchical information on network's nodes                                              | 92  |

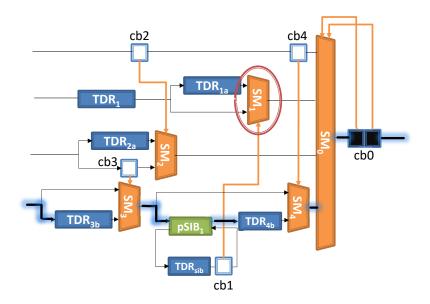

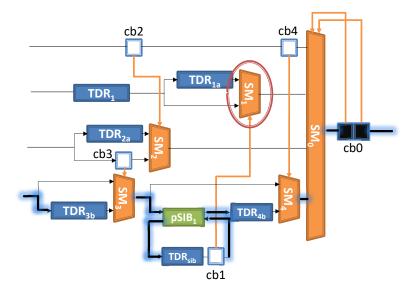

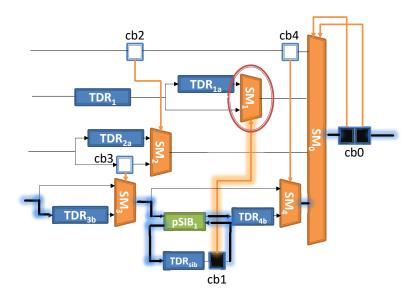

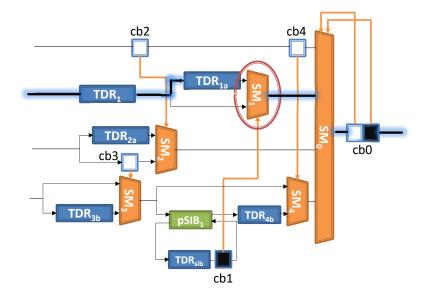

| 5.7  | Testing $SM_1$ in steps: $SM_1$ with its input segment 0 on active path                  | 94  |

| 5.8  | Testing $SM_1$ in steps: accessing its configuration bit $cb_1$ ; $pSIB_1$ has           |     |

|      | to be included into the active path                                                      | 95  |

| 5.9  | Testing $SM_1$ in steps: accessing its configuration bit $cb_1$ ; $pSIB_1$ has           |     |

|      | to be asserted                                                                           | 95  |

| 5.10 | Testing $SM_1$ in steps: setting $cb_1$ to $1 \dots \dots \dots \dots \dots \dots \dots$ | 96  |

| 5.11 | Testing $SM_1$ in steps: putting back $SM_1$ to the active path; input                   |     |

|      | segment that is now selected is 1 $(TDR_{1a})$                                           | 96  |

| 6.1  | 1687 RSN example                                                                         | 100 |

| 6.2  | Description of the pre-SIB as module in ICL                                              | 101 |

| 6.3  | Parameteres in ICL                                                                       | 102 |

| 6.4  | SIBs with TDRs in ICL                                                                    | 102 |

| 6.5  | ScanMux and TDR in ICL                                                                   | 103 |

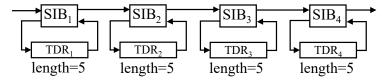

| 6.6  | TreeBalanced ScanMux with equal length registers                                         | 107 |

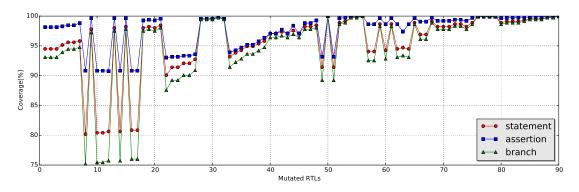

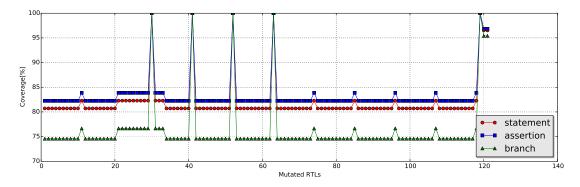

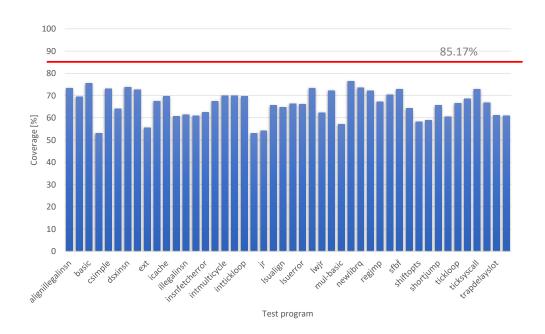

| 6.7  | Coverage for mutated RTL designs with wrong register lengths –                           |     |

|      | N73D14 benchmark circuit                                                                 | 107 |

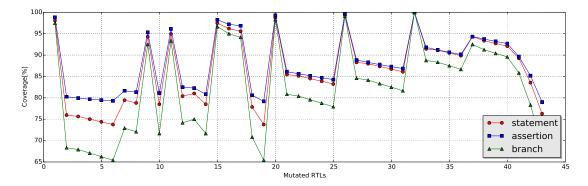

| 6.8  | Coverage for mutated RTL designs with wrong SIB types – TreeBal-                         |     |

|      | anced benchmark circuit                                                                  | 108 |

| 6.9  | Coverage for mutated RTL designs with exchanged ScanMux input                            |     |

|      | segments – TreeBalanced benchmark circuit                                                | 108 |

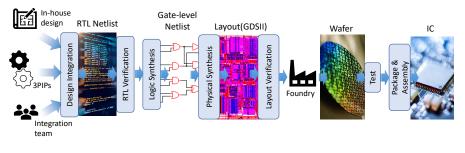

| 7.1  | IC production flow                                                                       | 115 |

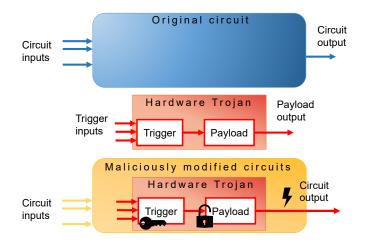

| 7.2  | Hardware Trojan structure                                                                | 116 |

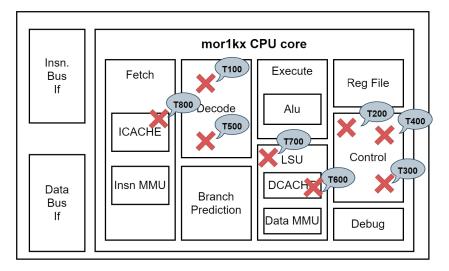

| 8.1  | Proposed RTL Hardware Trojans in the <i>Cappuccino</i> configuration of                  |     |

|      | the mor1kx CPU                                                                           | 122 |

| 8.2  | Trigger T200 condition                                                                   | 123 |

| 8.3  | Trigger T200 counters                                                                    | 124 |

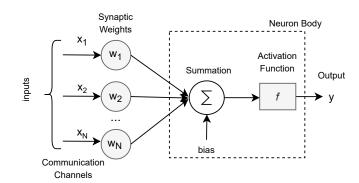

| 9.1  | The basic architecture of the perceptron                                                 | 132 |

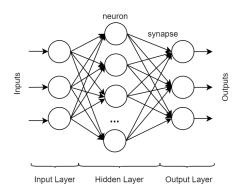

| 9.2  | Artificial Neural Network: a basic representation.                                       | 132 |

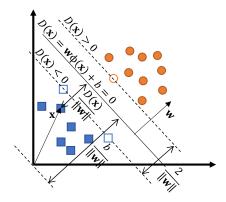

| 9.3  | Defining a border between classes using an SVM (support vectors                          |     |

|      | are marked with $\Box$ and $\circ$ )                                                     | 133 |

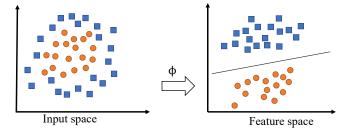

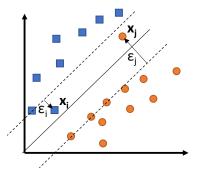

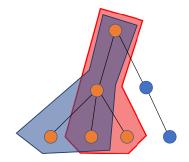

| 9.4  | Using non-linear kernel functions to map input space                                     | 135 |

| 9.5  | To prevent overfitting, avoiding narrow margin is recommended.                           |     |

|      | This can sometimes be achieved by introducing a margin and al-                           |     |

|      | lowing a certain degree of misclassification                                             | 136 |

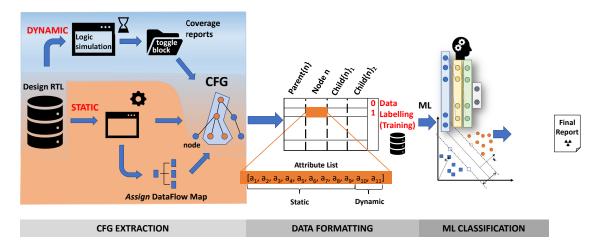

| 9.6  | Detailed framework flow including three main steps: CFG extraction,                      |     |

|      | Data formatting and ML classification                                                    | 137 |

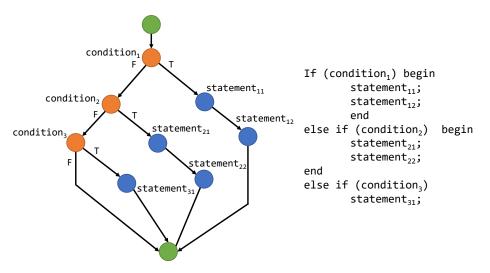

| 9.7  | CFG with the corresponding code structure                                                | 138 |

| 9.8  | Assign statements                                                        | 140 |

|------|--------------------------------------------------------------------------|-----|

| 9.9  | Assign DataFlow Map                                                      | 140 |

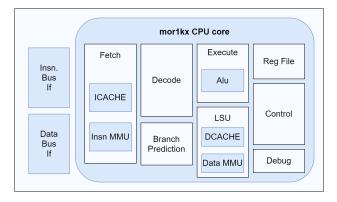

| 9.10 | mor1kx CPU core in cappuccino configuration                              | 143 |

| 9.11 | Individual coverage of each program on <i>mor1kx</i> core                | 145 |

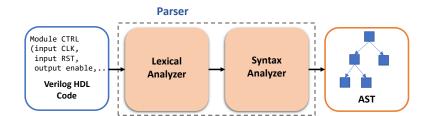

| 9.12 | Pyverilog parser                                                         | 145 |

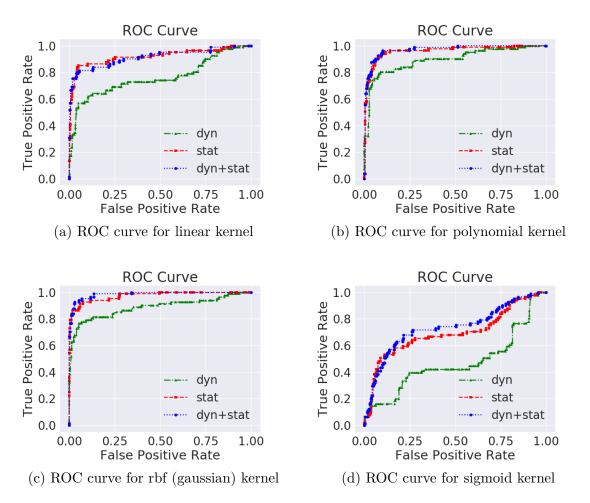

| 9.13 | ROC curves for 4 different kernels including different set of extracted  |     |

|      | attributes (farther from the 45-diagonal, i.e., closer to the upper-left |     |

|      | corner, the better)                                                      | 147 |

| 9.14 | Set of nodes belonging to HT as TP and FN                                | 150 |

# Introduction

Nanoelectronic systems are at the core of all industry sectors and are deployed in many life-critical domains such as automotive, security, healthcare, etc. [1] In the recent decades we witnessed new advances and immense progress in this field [2]. Emerging technologies, shrinking of the technology nodes, but above all the complexity of modern devices and the integration of many different components within a system pose significant challenges in terms of design and mutually dependent aspects of security, reliability and quality [3]–[5].

Given the criticality of their application and the role nanoelectronic systems have as a backbone of the large infrastructure and Cyber-Physical systems, the need of providing the intended functionality as well as being reliable and secure is of utmost importance. On the other hand, due to the complexity and miniaturization of the process nodes towards the physical limits, such requirements are getting increasingly hard to satisfy. How much will it cost? Does it satisfy initial requirements? How robust it is? Will it work and how efficient will be? How much time does it take to design and produce? These are only some of the most important questions to answer during the product's life-cycle (Fig. 7.1).

As soon as integrated circuits (ICs) emerged, the need for design tools became evident. Obviously, the design of modern ICs containing billions of devices would be infeasible without software tools that are used at every stage [6]. Related tools and methodologies that are used are called electronic design automation (EDA) [7]. It can be said that EDA, i.e. Computer-Aided Design (CAD) tools revolutionized the IC industry and continue to do so even today. They can be used to develop new designs, reuse the existing ones, and integrate entire systems [8], [9]. Such tools can have different role in the process of design, manufacturing, and test: simulation (electrical, logic gate or high-level), ATPG test vector generation, layout design, placement and route, logic synthesis, design optimization (timing, power and cost/area) and device performance prediction, verification (formal, functional, equivalence checking), etc.

A variety of complementary tools and methods were added to conventional design flows. Furthermore, library vendors started offering a whole spectrum of libraries for optimal design choices (high-performance, low-power, etc.). In that way, design was made portable across processes and foundries, thus making the whole cycle significantly more efficient. Some new design areas have matured in the meantime: gate sizing (choosing the best transistor width to obtain better performance), clock design and synthesis (reliable synchronization due to high number of sequential elements), three-dimensional ICs (continuing to follow the Moore's law and stack ICs one on top of the other).

In general, all of the listed types of tools not only automate the work of engineers, but also process large amounts of heterogeneous data. In comparison with human designers they are also definitely able to perform more accurate analyses and more efficient and advanced optimizations.

Figure 1: Life cycle of an IC

This thesis focuses on the new techniques developed to support the designer of nanoelectronic systems in the validation of their correctness. This task requires considering not only the space of all possible scenarios where the system is used, but also a further dimension represented by the possible hardware faults and external attacks the system is designed to face. Assessing the correct functionality of the system with such a huge combination of possibilities can only be done by combining different techniques coming from different communities (e.g., the one of software validation, the one of hardware validation, the one of hardware testing) and exploiting different paradigms (e.g., resorting to formal techniques, simulation, to evolutionary computation, etc.).

The growing adoption of electronic systems in systems where safety is a concern asks for strict requirements in terms of fault prevention , detection , and management , so that the probability of occurrence of any failure due to a hardware fault is kept under the acceptable threshold. More recently, another issue arose, related to the attacks that may be purposely driven against an electronic system to steal the information it stores, or to modify its behavior. Due to the increasing frequency of these attacks, it is crucial that the system is designed in such a way that the chances of their success are minimized (security) [10]–[16]. The solutions adopted by the designer to face the requirements in terms of both safety and security must be assessed in terms of correctness and effectiveness (validation).

The bridge that exists between pre-silicon validation (verification) and postsilicon validation, has to be mitigated to alleviate time-to-market pressure. With the growing design complexity, technology scaling, with improving performance and high levels of integration, design validation challenges are continuously increasing. Time required to perform design validation and verification is extremely consuming and in some complex cases may occupy most of product design cycle. As reported in [17] design verification as the most important aspect of the product development process can consume as much as 80% of the total product development time. What is even more critical is the cost needed to find and correct design errors later in the design flow [18]. Another issue is that often system design requirements in terms of security and system validation do not go along with each other.

Dependability has become a key concern, demanding the presence of numerous and various resources embedded within integrated circuits (ICs). These are used for supporting test, such as Built-In Self-Test (BIST) modules , for monitoring internal parameters such as current, temperature or delay sensors and configuration/calibration of different modules through registers . Due to the requirements for having a large number of these devices it became infeasible to include them into the single scan chain or provide a separate instruction for accessing every single one, relying on IEEE 1149.1. Additionally, instruments (or IPs) could easily originate from different vendors, making the integration a long and complicated procedure. There was not a simple and standardized way to perform the integration, but more a set of ad-hoc solutions based on the instructions from the IP provider given to the ASIC test/design engineer. It included extensive learning and different setup for each new IP, as well as integration into the latest ASIC and latest process node.

A solution for simplifying not only the access to embedded resources and reducing the overhead, but also alleviating the aforementioned issues with the integration has been described and published as the IEEE 1687 standard [19]. The standard has enabled designers to flexibly trade-off between area, access time and other parameters, since the scan chain accessible through the JTAG's Test Access Port (TAP) can now be split and configured. Furthermore, it offers a standard test hardware description, and a standard test procedure language for each IP. More details about the standard itself and so called, Reconfigurable Scan Networks (RSNs) will be given in Chapter 1.

The correct operation of IJTAG-compliant infrastructure is a product of many aspects and components including the actual hardware on the chip, the respective standard descriptions, such as ICL (Instrument Connectivity Language) and PDL (Procedure Description Language) files as well as the software used to import the descriptions and control the hardware. Being a relatively new standard, there are still many different aspects insufficiently explored related to the infrastructure it describes, especially in the context of dependability. I believe that such research is essential for providing support and therefore wide-spread usage of this infrastructure. The first part of this thesis is oriented on the following issues:

- post-manufacturing test and efficient techniques for generating configurations used to test reconfigurable modules within RSNs.

- identifying faults within RSNs (diagnosis)

- post-silicon validation of RSNs

- in-field use, and reliability issue related to NBTI-aging effect

- equivalence checking between ICL and RTL—verification

Another argument that this thesis will advance is the Hardware Security. In the recent years, the growing complexity of modern devices and the fabrication costs led the IC industry to pursue a new global business model. The half-trillion-dollar semiconductor supply chain is one of the world's most complex. The production of a single computer chip often requires more than 1,000 steps passing through international borders 70 or more times before reaching an end customer [20]. In that regard, even more companies around the world are deeply involved in all phases of the IC supply chain. The outsourcing of part of the process to untrusted third-party entities raises increasing concerns about the hardware security of the products. The problem of ensuring hardware security has gained much attention in the last ten years, especially early in the design cycle, when an attacker may insert malicious circuitry at register-transfer (RT) or gate level. Such type of attacks that may lead to devastating consequences, such as denial of service or data leakage.

Particularly, Hardware Trojans (HTs) are an important topic not only for industry and academia, but also for government bodies [21].

Hardware Trojans are modifications that an adversary is able to make in original circuitry to gain access to sensitive information (encryption keys), downgrade the performance, prevent user access or completely disable the device or its functions. It is assumed that the attacker is able to access the design (or its part) and perform maliciously modifications before or during fabrication.

What renders difficult to detect such alterations is:

- large number and the complexity of soft, firm and hard IPs that are present in modern SoC designs;

- the cost of applying reverse engineering and inspecting physically **each** device given their complexity and technology miniaturization;

- given the characteristics of the advanced technology used nowadays, physical measurements in a circuit infected by a Trojan may still stay within the margins due to process variation and thus, remain undetected;

- Trojan are by construction difficult to activate (a set of complex low-probability conditions) and while the attacker might have information about the design, the defender might not have any information about the Trojan, i.e., its type, size, position etc.;

- manufacturing tests that are applied on every device are ineffective for the reasons listed above.

Due to evolving attacks, the research community is spending a lot of effort in developing more and more sophisticated detection methodologies. However, the problem is that they are validated on the benchmarks that do not reflect the real complexity of the devices used for industrial applications, such as automotive. First contribution related to the aforementioned issue in the release of new benchmarks targeting a pipelined open-source RISC microprocessor core.

Although most of the detection techniques work at the gate level, shifting the detection of HTs inserted at RTL to the gate level would result in increased design and verification costs. That is why a new and efficient method for detecting such Trojans has been developed. It will be presented as a second contribution in this part of the thesis. A branch of artificial intelligence (AI) and computer science that continues to receive tremendous attention and has alleviated life to many engineers is Machine Learning (ML). This is especially true in the context of ICs, given the large amounts of available data from both production and use life-cycle phases.

The proposed methodology is based on ML technique for Hardware Trojans detection, based on a deep analysis of the RT-Level model. The analysis is based on dynamic and static properties extracted from such model. An Artificial Neural Network (ANN) as well as the Support Vector Machine (SVM) algorithm are used to identify suspicious code fragments potentially hiding a Trojan.

# Part I

# IJTAG Reconfigurable Scan Networks Dependability

# Chapter 1 Background

In many of the latest ICs designers introduced resources whose purpose is not to support the circuit functionality, but rather to support ancillary features such as test, calibration, debug and monitoring. In particular, current ICs often integrate a plethora of sensors and actuators, each associated to a register to be read and/or written from the outside, sometimes at the end of the manufacturing process, sometimes during the operational phase. Many test solutions, such as BIST, also require registers to activate/initialize the test and retrieve results. In order to effectively access all these registers (also called instruments, or TDRs), companies used to include them into a single chain, often accessed through the standard IEEE 1149.1 interface. With the significant rise in complexity and the number of devices, existing infrastructure became inefficient. One of the limitations originated from the length of a single scan chain which was constantly increasing; performing access to communicate with a single device resulted in large time overhead. Moreover, the reliability of such structure became an issue, since a problem on a single bit would render the entire scan-chain non-operational and consequently, lead to a catastrophic breakdown. Another possibility involving architecture for accessing each instrument individually, apart from limited flexibility it provides, requires infeasible number of instructions to be implemented. To tackle these issues solutions based on so called Reconfigurable Scan Networks (RSNs) were introduced. 1149.1. was updated to support such constructs, while 1687 introduced increased flow flexibility and the possibility to define more complex structures in the network during the chip integration phase in a newly developed description language. Nevertheless, both 1687 and 1149.1-2013 have a lot of common advantage in terms of reuse, efficiency, automation and improved quality that affect several stages of chip development. They can provide a means of standardization of IP verification, insertion, internal IP test interface, etc. Both standards introduce dynamically reconfigurable scan chains. For the sake of simplicity as different terminology is used, basic network constructs will be described as a part of IEEE 1687 Std in Section 1.2.

### 1.1 IEEE 1149.1 – JTAG

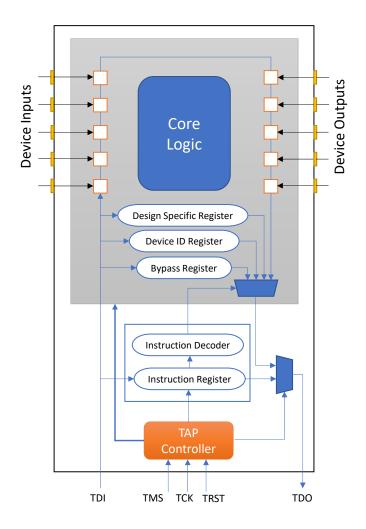

As the devices' complexity increased and with the limitations in terms of number, cost and physical access to its pins, it became both impractical and inefficient to use them for accessing the device and test the interconnections between different ICs. To deal with these issues, IEEE 1149.1 industrial standard was devised. It is commonly known as Joint Tag Access Group (JTAG) and describes a testing infrastructure. Registers described by the standard, boundary scan cells, as their name suggests are composed of individual bits, or cells that are located at the boundary of the device. They are placed between the functional core and the pins or balls by which it is connected to a board. The standard also introduced the description of a logic block called Test Access Point (TAP). TAP consists of a controller in charge of executing access and data flow, which is a sequential state machine, Instruction Register, and a number of Data Registers providing write and read functionality (Fig. 1.1). Given its flexibility for implementing additional commands and adding new logic blocks, TAP soon found its alternative application for programming and debugging devices. The JTAG interface consists of 5 signals: Test Data In (TDI), Test Data Out (TDO), Test Clock (TCK), Test Reset (TRST) and Test Mode Select (TMS).

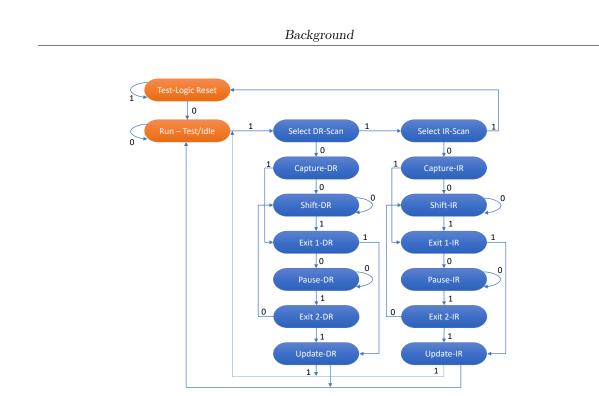

The TAP controller as defined by the IEEE-1149.1 standard represents a 16state finite state machine. It is controlled by TCK and TMS. Each transition is determined on the rising edge of TCK, by the state of TMS. Two analogous paths through the state machine are used to capture and/or update data by scanning through the instruction register (IR) or through a data register (DR). The JTAG state machine is depicted in Fig. 1.2.

### **1.2** IEEE 1687 – IJTAG

Exacerbated by the increasing number of instruments within a single scan chain, the lack of flexibility is a major issue in both IEEE 1149.1 boundary-scan (JTAG) and IEEE 1500 core test standards, along with weaknesses of the test scheduling and scalability limitations. The new IEEE 1687 standard (IJTAG) [1] was designed to be able to deal with problems caused by the long scan chains and the substantial number of instructions required to access instruments. It exploits the idea of Reconfigurable Scan Networks (RSNs), residing between device interface and instrument interface and allowing a scan chain to be partitioned into segments that can be selectively included or excluded. Through dynamic configuration and variable-length scan-chain, IJTAG enables flexible and efficient access to all instruments. Thus, designers are able to take into account various configurations and choose the best trade-off between parameters such as area or access time. Although the standard does not impose an external access mechanism, the most widely accepted one is

Figure 1.1: JTAG boundary scan with dedicated registers and TAP controller

TAP. The IEEE 1687 standard also introduces two languages: Instrument Connectivity Language (ICL) and Procedural Description Language (PDL) that allow describing the structure of the network and the protocol to access the different instruments.

To interface each instrument, a register of a variable length is used. This corresponds to a set of scan cells, IEEE 1149.1-compatible, referred to as a TDR. TDRs can be Read-Only, Write-Only or Read-Write. Furthermore, three operations are used to control the network and read/write data from/to TDRs: capture (C), shift (S), update (U).

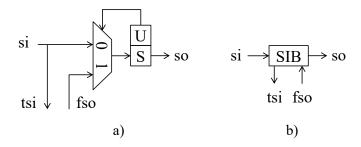

Apart from TDRs, the network is composed out of two types of programmable modules. These are used to partition the set of instruments; including or excluding a set of instruments obviously has an effect on the scan chain length. A segment insertion bit (SIB) module behaves as a gateway with respect to the segment it

Figure 1.2: TAP controller state machine

controls: it is able either to bypass the segment or to include the segment into the active path (Fig. 1.3(a)). In the bypass state it is referred to as de-asserted, while it is said to be asserted when is configured to expand the scan chain. SIBs can be used to obtain a hierarchical structure of the network, allowing hierarchical access to the registers interfacing the instruments. The Fig. 1.3(b) shows a symbol used to represent a SIB.

Figure 1.3: Segment Insertion Bit (SIB) module: Simplified schematic (left) and symbol (right)

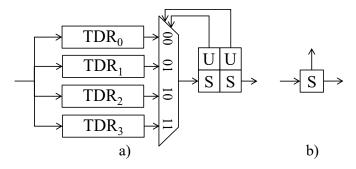

Other than using a SIB to include or bypass a segment, a different module is used to support exchange of one scan chain segment for another. A scan multiplexer with shift-update cells (ScanMux, SM) can be seen as a configurable multiplexer, which is used to alter the scan chain by selecting which of its input branch segments are to be included into the active path. Thus, the existence of mutually exclusive scan chains is supported, reinforcing the trade-off of access time with access length. The example given in Fig. 1.4(a) shows a scan multiplexer with a two-bit shiftupdate control register which is used to choose one among four segments. The symbol shown in Fig. 1.4(b) will be used to represent a shift-update cell. Control registers of the modules consist out of two stage cells. A cell is referred to as a flip-flop with additional control logic. Shift (S) cell is a part of scan chain and it shifts values, while Update (U) cell stores the S cell value, when update operation is performed. The configuration of the module is defined by the value in the U cell. For example, a SIB module is configured by shifting in the desired value into the S scan cell, followed by an update, thus storing the value from the S cell to the U scan cell. Indicatively, as illustrated by Fig. 1.3(a), in this work a SIB is considered to be asserted if the latched bit is 1 and if so, it includes the path between tsi and fso terminals. Conversely, it is regarded as being in a de-asserted state if the latched bit is 0, bypassing the segment between tsi and fso terminals, directly connecting si and so through the S cell. The provided shortcut has the length of one bit.

Figure 1.4: ScanMux (SM) module: Simplified schematic (left) and symbol (right)

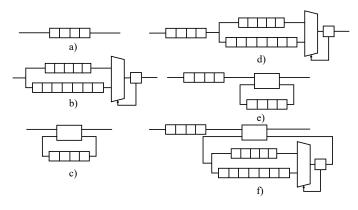

Depending on the position of the configuration bit(s) with respect to the programmable module itself the module can be either inline or remote. A module is considered to be inline if its associated configuration cell is located in the same segment of the related module. Otherwise, it is said to be remotely controlled. Some basic architectural constructs, varying on the organization of TDRs, are provided in Figure 3. A simplest one is a flat structure where TDR is always accessible (Fig. 1.5a). MUXed TDRs enable mutually exclusive access (Fig. 1.5b), while excludable TDR is either a part of the active path or is bypassed (Fig. 1.5c). Partial configurations involve combining previous structures, thus in Fig. 1.5d (partially selectable TDRs) always two TDRs belong to the active path (one fixed, another selectable), while in Fig. 1.5e (partially excludable TDRs) one or two registers belong to the active path (path always includes one, while the other one can be inserted). The Fig. 1.5f shows the partially excludable and selectable configuration (one TDR is always accessible, while one of the remaining two can be included into the active path). These can be combined to design more complex networks.

Figure 1.5

To keep the drawings simple inFig. 1.3 and Fig. 1.4, the clock, reset, control signals (namely, *shift, update*, and *capture*), and the *select* signal used to gate the control signals are not shown. To follow the examples in this work, it should suffice to assume that only the TDR connected to the selected port of a ScanMux receives (i.e., reacts to) the clock and control signals. It should be noted that the configuration of the network (i.e., the status of the latched bits) does not change when shifting a new vector through the shift cells, but only in the update phase where the shifted vector is latched into the U cells.

To operate an IEEE 1687 network from outside the chip, the IEEE 1149.1 TAP can be used. The TAP finite state machine provides the control signals needed to configure the IEEE 1687 network and access the instruments through it.

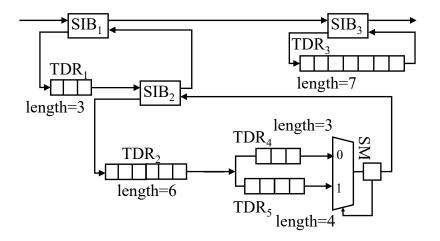

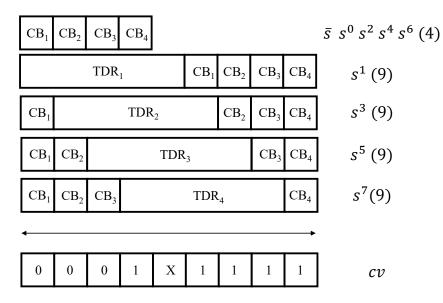

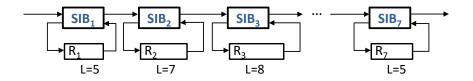

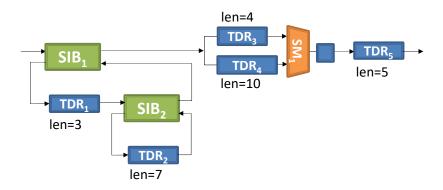

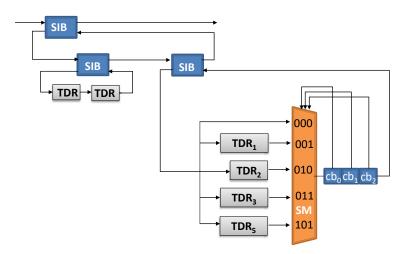

As an example, let us consider an RSN that includes five instruments: the user can access them through the TAP port, reading or writing from/to the associated Test Data Registers (TDR<sub>1</sub> to TDR<sub>5</sub>). In order to save time when accessing to the instruments, the designer, instead of connecting all TDRs into a single chain, like in 1149.1-complaint circuits, may decide to adopt an IEEE 1687 network including three SIBs and one ScanMux (SM), as shown in Fig. 1.6; each of these four configuration modules can be configured to allow the access to a given subset of TDRs (and the associated instruments). Table 1.1 reports sixteen possible configurations supported by this network, which depend on how the SIBs and the ScanMux have been configured. In Table 1.1, "A" means asserted, "D" means de-asserted, 0 and 1 correspond to the two possible positions of the ScanMux, and "-" appears when a module belongs to an inaccessible segment.

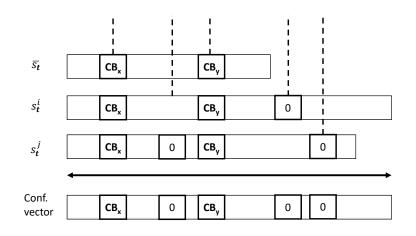

In order to move the network to a given configuration, the user must first shift-in a suitable sequence of bits, so that the S flip-flops of SIBs and ScanMuxes hold the correct value, then activate the update signal to move these bits to the U latches. The sequence of bits to configure the network is called *configuration vector*. A generic configuration vector is referred to as  $cv_i$ . Once a configuration is reached, a given subset of the TDRs is accessible, which constitutes the so-called *active*

Figure 1.6: Example of IEEE 1687 RSN.

path. The rightmost column of Table 1.1 reports the length of the active path for each configuration, which corresponds to the number of TDR and S flip-flops in the path. The reader should note that moving from one configuration to another may require more than one configuration vector. For example, in the network of Fig. 1.6 moving from  $C_2$  to  $C_{13}$  requires first turning SIB<sub>1</sub> into the asserted state (e.g., moving to  $C_8$ ) and only then we will be able to change the configuration of the SM scan multiplexer to select input branch 1 and turn SIB<sub>2</sub> into the asserted state. Hence, moving from  $C_2$  to  $C_{13}$  requires 2 configuration vectors.

### 1.3 Related works

In recent years the IEEE 1687 standard and RSNs have been subject of many research works, addressing test, verification, security and design. However, to our knowledge, apart from [22], this is the only work addressing the issue of permanent RSN fault diagnosis.

As already discussed, although reconfigurable scan networks introduced flexibility, minimizing access time has arisen as a potential issue. The authors in [23] analyzed various structures with different access scheduling to estimate overall access time. Additionally, the same authors developed the CAD tool to support design automation of optimized 1687 SIB networks [24]. Based on the access schedule and the set of instruments, the tool is able to design a network with optimized access time and low hardware overhead.

In [25] a general approach has been proposed to automatically generate a test sequence for an IEEE 1687 RSN with respect to permanent faults. It provides techniques for testing SIBs and ScanMuxes, and then it describes how to combine

#### Background

| Configuration                                       | $\operatorname{SIB}_1$ | $\mathrm{SIB}_2$ | SM                                    | $SIB_3$ | Active path               | Length |

|-----------------------------------------------------|------------------------|------------------|---------------------------------------|---------|---------------------------|--------|

| $\begin{array}{c} C_0\\ C_1\\ C_4\\ C_5\end{array}$ | D                      | D                | 0<br>1<br>0<br>1                      | D       | -                         | 2      |

| $\begin{array}{c} C_2\\ C_3\\ C_6\\ C_7\end{array}$ | D                      | D<br>A           | 0<br>1<br>0<br>1                      | А       | $\mathrm{TDR}_3$          | 9      |

| $C_8$<br>$C_9$                                      | А                      | D                | $\begin{array}{c} 0 \\ 1 \end{array}$ | D       | $TDR_1$                   | 6      |

| $\begin{array}{c} C_{10} \\ C_{11} \end{array}$     | А                      | D                | $\begin{array}{c} 0 \\ 1 \end{array}$ | А       | $TDR_1, TDR_3$            | 13     |

| $C_{12}$                                            | А                      | А                | 0                                     | D       | $TDR_1, TDR_2, TDR_4$     | 16     |

| C <sub>13</sub>                                     | А                      | А                | 1                                     | D       | $TDR_1, TDR_2, TDR_5$     | 17     |

| $C_{14}$                                            | А                      | А                | 0                                     | А       | $TDR_1,TDR_2,TDR_3,TDR_4$ | 23     |

| $C_{15}$                                            | А                      | А                | 1                                     | А       | $TDR_1,TDR_2,TDR_3,TDR_5$ | 24     |

Table 1.1: Set of possible configurations of the RSN in Fig. 1.6.

them into a single comprehensive test. This test is independent on the specific representation of the network elements and does not require any change in the hardware implementing the network. Test generation can directly start from the network's ICL description, as mandated by the IEEE 1687. The proposed test generation algorithms are based on different heuristics that could easily run even on relatively large RSNs.

In [26] that approach was refined to minimize the duration of the resulting test sequence: the faced problem was properly modelled according to the graph theory, and an optimal algorithm able to generate the minimum-duration test sequence was described. Unfortunately, such an approach works only on relatively small RSNs, and sub-optimal solutions must be accepted when dealing with real cases.

An alternative approach based on an evolutionary algorithm was developed in [27] to generate test sequence for a generic RSN with minimum duration. The usage of formal techniques to generate the minimum duration sequence able to test all reconfigurable modules in the network is explored in [28], providing a lower bound

for small networks and thus assessing the effectiveness of the other approaches.

The authors of [22] analyzed the effect of permanent fault on RSN elements to determine diagnostic properties. The test sequence generated by the procedure described in [25] is further extended to enable localization of faults, i.e., to satisfy the defined properties.

A number of works also analyze the use of IEEE 1687 infrastructure to support on-line health monitoring and fault management [29]-[35].

Modelling, verification and optimal pattern generation is tackled in [36]. RSN formal model is presented considering structural and functional dependencies. The problem is transformed into Boolean Satisfability Problem. The formal method is also used for pattern retargeting, i.e., to generate scan-in data for reconfiguration and execution of commands in instrument access procedures. Moreover, the paper describes pattern generation method for efficient concurrent access. For the retargeting modelled as a sequential problem unrolled over number of time frames (CSU operations), the authors in [37] proposed a method for calculating an upper-bound on the number of required CSU operations. Knowing the upper-bound is used to deal with the model complexity for large designs and reduce the search space while preserving the optimum solution.

Defining and verifying security properties is addressed in [38]. In this work it is described how specified permissions and restrictions are transformed into predicated for a formal model unbounded checking.

The authors in [39] considered introducing some DfT modifications to enable observability of shadow registers and update logic. Moreover, different test methods are proposed for stuck-at, flip-flop transparency and bridge-faults in the RSN. Security in RSN is another important aspect considered is literature. In [40], [41], obfuscation strategies are proposed to modify the structure of the network by introducing additional logic for controlling the state of reconfigurable modules, as well as creating false paths to confuse the attacker. On the other hand, other works consider validating security properties and preventing unauthorized access by the means of external filter module both online and fixed-precomputed [42]–[44].

### 1.4 IEEE 1687 Benchmark RSNs

In [45] authors from both academia and industry proposed and published a set of benchmarks to enable fair and objective comparison of the developed methodologies across research groups. The benchmarks are also typical and challenging examples utilizing many different constructs and features supported by the standard. They can be classified in four different categories based on the architecture and purpose. Table 1.2 reports some basic information about the networks used to perform evaluation. In column 2 and 3, the table reports for each network the number of SIBs and SMs, respectively. The number of configuration bits of SIBs and SMs is given in the fourth column. The column  $Max \ depth$  indicates the maximum hierarchical depth of each network (for SIB-based networks this value equals to the maximum number of nested SIBs, according to [45]). The column  $Max \ path$  reports the length of the longest path in the network, and the rightmost column the number of bits in all the TDRs.

| Network        | SIB | SM  | Tot. | Max                    | Max         | Scan        |

|----------------|-----|-----|------|------------------------|-------------|-------------|

| INELWOIK       | SID | SM  | bits | $\operatorname{depth}$ | path        | cells       |

| Mingle         | 10  | 3   | 13   | 4                      | 171         | 270         |

| TreeBalanced   | 43  | 3   | 48   | 7                      | $5,\!219$   | $5,\!581$   |

| $TreeFlat\_Ex$ | 57  | 3   | 62   | 5                      | $5,\!100$   | $5,\!195$   |

| TreeUnbalanced | 28  | —   | 28   | 11                     | $42,\!630$  | $42,\!630$  |

| a586710        | _   | 32  | 32   | 4                      | 42,381      | 42,410      |

| p22810         | 270 | —   | 270  | 2                      | $30,\!356$  | $30,\!356$  |

| p34392         | —   | 96  | 96   | 4                      | $27,\!899$  | $27,\!990$  |

| p93791         | _   | 596 | 596  | 4                      | 100,709     | $101,\!291$ |

| q12710         | 27  | —   | 27   | 2                      | $26,\!185$  | $26,\!185$  |

| t512505        | 159 | _   | 159  | 2                      | $77,\!005$  | 77,005      |

| N132D4         | 39  | 40  | 79   | 5                      | 2,555       | 2,991       |

| N17D3          | 7   | 8   | 15   | 4                      | 372         | 462         |

| N32D6          | 13  | 10  | 23   | 4                      | 84,039      | $95,\!158$  |

| N73D14         | 29  | 17  | 46   | 12                     | $190,\!526$ | $218,\!869$ |

| NE1200P430     | 381 | 430 | 811  | 127                    | $88,\!471$  | $108,\!148$ |

| NE600P150      | 207 | 194 | 401  | 78                     | $23,\!423$  | 28,250      |

Table 1.2: ITC'16 benchmark networks list

# Chapter 2

### Test

When a circuit includes an RSN, the issue of testing the related hardware must clearly be considered, checking for possible defects affecting it. Failing to effectively solve this issue may lead to completely false results when using the RSN itself. Some works faced the issue of testing the test circuitry mandated by the IEEE 1149.1 standard [46], while other works focused on the test of possible permanent faults affecting a standard scan chain, e.g., by shifting into the chain a sequence of alternated 0s and 1s, and checking that the same sequence appears at the other extreme of the chain [47]-[49]. However, to test an RSN is a more complex task with respect to the standard scan chain test, since examining the ability of flip-flops comprising the scan chain to shift is not sufficient to guarantee correct functionality and expected performance. In addition, testing should check whether the network can be moved from one configuration to another and if it operates correctly after enforcing whichever legal configuration. Although testing an RSN clearly shares some similarities with the task of design validation [36], time required to perform test, i.e. test stimuli duration is considered to be more important with more strict limitations.

### 2.1 Fault model

Testing a non-reconfigurable scan chain for permanent faults can be performed by shifting a suitable sequence of 0s and 1s through the scan chain. RSNs are however far more complicated to test: in addition to flip-flops composing the TDRs, which have to be tested to check whether they can correctly shift values when included in the active path, the reconfigurable modules (i.e., SIBs and ScanMuxes) have to be also tested to check whether they are able to move the network to the corresponding configurations.

For all of the test-related techniques that will be described in this thesis, highlevel fault model that was first introduced in [25] will be used. The faults affecting the reconfigurable modules, such as ScanMuxes, are modelled such that a different configuration is selected rather than the expected one. Such a fault leads to a different active path (called *faulty path*) than the expected one, and the two are likely to have a different length. For example, in Fig. 1.6 the multiplexer (ScanMux) may be affected by a permanent fault whose effect is that the segment connected to the input 0 is always selected, no matter the value in the selection cell. The same may arise for the generic SIB<sub>i</sub>, which can be affected by faults named *stuck-at asserted* (SIB<sub>i</sub>-s@A) and *stuck-at de-asserted* (SIB<sub>i</sub>-s@D). The stuck-at faults in the scan bits of the selection cells are considered as detected by implication by testing such high-level faults, which cover also the faults affecting the update logic of the reconfigurable modules.

Moreover, such faults cover some faults affecting the reset logic, whose effect is that the module is stuck at the reset value. The other reset faults (i.e., those that make the reset ineffective) are not considered but can be targeted by employing the techniques described in [39].

## 2.2 Test procedure

Resorting to the high-level fault model, one can test an RSN by first configuring the RSN so that the target fault is excited, and then comparing the length of the activated path against the length of the expected path. Since the number of possible configurations of a network grows exponentially with the number of configurable modules, the problem of identifying a sequence of sessions which guarantees that 1) all the configurations modules are fully tested, and 2) the total test duration is minimized, is not trivial. Coming back to the example of Fig. 1.6, this means identifying the sequence of configurations (out of the 16 possible ones) that matches the two above goals.

As an example, the high-level fault that affects the ScanMux of Fig. 1.6, to always select the segment connected to the input 1, can be excited by a configuration which selects the input 0; configurations  $C_{12}$  and  $C_{14}$  fulfil this requirement. Once one of them is activated, one can measure the length of the active path by shifting a given sequence (called *test vector*) in TDI and checking when it will appear on TDO. Any fault modifying the length of the active path can be detected in this way. A generic test vector is referred to as  $tv_i$  in this paper.

In order to test all configurable modules in a RSN, the test sequence can be organized in *sessions*: in each session the network is first configured via one or more configuration vectors (so that each SIB and each ScanMux is switched into a given position), and then a check is performed for whether the expected path has been inserted between TDI and TDO via test vector, i.e., whether right segments can be accessed.

A proper test sequence consists of an alternating bits sequence 0101..., as long as

the active path length followed by a sequence terminator, such as two consecutive 0s or 1s. For example, if the network in Fig. 1.6 is configured to  $C_8$  (see Table 1.1), a proper test vector is 01010101011, that is, 9 bits of alternated 0s and 1s followed by the sequence terminator. Faults affecting the network may corrupt the network by changing the active path, which will cause the sequence terminator to be observed on the scan output in an unexpected clock cycle. For example, if a stuck-at fault affects the selection of the module SIB<sub>1</sub> (which is supposed to be asserted in the fault-free scenario), then the network may exclude the SIB<sub>1</sub>'s controlled segment, as in the SIB<sub>1</sub>'s de-asserted case. Thus, the active path selected in such a faulty scenario would be the same of the configuration  $C_0$  of Table 1.1. In the faulty scenario, the path length is 2, meaning that the sequence terminator is observed earlier than expected on the scan output pin.

The complete process consists of the following steps:

- shifting in the sequence consisting of same values (all 0s or all 1s), while the length of the sequence is equal to the length of the longest path in the network; the goal of this phase is the initialization of the scan cells;

- shifting in the second, test sequence, of alternated 0s and 1s (i.e., 0101...01), with the predetermined (expected) length

- the last sequence shifts values from the currently active path. Determining fault-caused modifications of values in the scan chain and the length of the active scan path is performed by verifying previously inserted test vector; in parallel with observing the values appearing at the output, new configuration vector is shifted in.

Applying the configuration vector demands an update operation. The duration of the complete test procedure, referred to as a total cost, depends on the duration of each step and is composed of configuration step cost and test step cost, both expressed in terms of number of clock cycles. The configuration step cost is the time needed to apply configuration vectors. The time overhead of the JTAG protocol is also included, since moving the TAP controller from shift to update state and vice versa also requires a few clock cycles (Fig. 1.2). The test phase cost is the time required to shift in the test sequence. Furthermore, the duration of a session is determined by the length of the TDRs included in the path, as well as by the previous configuration.

In this thesis several testing procedures are presented. Two are semi-formal techniques to generate the set of configurations that yield high coverage and low test time based on representing the network as a Finite State Machine, while the third one uses meta-heuristic evolutionary approach combined with post-processing techniques.

1. Perform reset (SIB<sub>1</sub>  $\rightarrow$  SIB<sub>3</sub>)

| Input Fault free |                                                   | $SIB_1$                                           |                                                   | $SIB_2$                                           |              | $\mathbf{SM}$                                     |                                                   | $SIB_3$                                           |             |

|------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|--------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|-------------|

|                  | $\overline{s}$                                    | s@D- <i>s</i> <sup>0</sup>                        | $s@A-s^1$                                         | $s@D-s^2$                                         | $s@A-s^3$    | $s@0-s^4$                                         | $s@1-s^5$                                         | $s@D-s^6$                                         | $s@A-s^7$   |

| reset<br>observe | $\begin{array}{c} \text{DD0D} \\ (2) \end{array}$ | $\begin{array}{c} \text{DD0D} \\ (2) \end{array}$ | $\begin{array}{c} \text{AD0D} \\ (6) \end{array}$ | $\begin{array}{c} \text{DD0D} \\ (2) \end{array}$ | DA0D<br>(2)  | $\begin{array}{c} \text{DD0D} \\ (2) \end{array}$ | $\begin{array}{c} \text{DD1D} \\ (2) \end{array}$ | $\begin{array}{c} \text{DD0D} \\ (2) \end{array}$ | DD0A<br>(9) |

| 1000<br>observe  | $\begin{array}{c} \text{AD0D} \\ (6) \end{array}$ | DD0D<br>(2)                                       |                                                   | AD0D<br>(6)                                       | AA0D<br>(16) | AD0D<br>(6)                                       | AD1D<br>(6)                                       | $\begin{array}{c} \text{AD0D} \\ (6) \end{array}$ |             |

| 1100<br>observe  | AA0D<br>(16)                                      |                                                   | ,                                                 | AD0D<br>(6)                                       |              | AA0D<br>(16)                                      | AA1D<br>(17)                                      | AA0D<br>(16)                                      |             |

| 1110<br>observe  | AA1D<br>(17)                                      |                                                   |                                                   |                                                   |              | AA0D<br>(16)                                      |                                                   | AA1D<br>(17)                                      |             |

| 1111<br>observe  | AA1A<br>(24)                                      |                                                   |                                                   |                                                   |              |                                                   |                                                   | AA1D<br>(17)                                      |             |

Table 2.1: Test procedure for the network in Fig.1.6

Test

- 2. Perform initialization

- 3. Insert test sequence

- (a) Shift in 01 (length = 2)

- (b) Shift in 11 (length = 2)

- 4. Check test sequence while applying new configuration

- (a) Shift in 01 and observe the output; update  $(TDR_1 \rightarrow SIB_2 \rightarrow SIB_1 \rightarrow$  $SIB_3$ )

- 5. Perform initialization

- 6. Insert test sequence

- (a) Shift in 010101 (length = 6)

- (b) Shift in 11 (length = 2)

- 7. Check test sequence while applying new configuration

- (a) Shift in 011XXX and observe the output; update (TDR<sub>1</sub>  $\rightarrow$  TDR<sub>2</sub>  $\rightarrow$  $TDR_4 \rightarrow SM \rightarrow SIB_2 \rightarrow SIB_1 \rightarrow SIB_3)$

- 8. Perform initialization

- 9. Insert test sequence

- (a) Shift in 010101010101010101 (length = 16)

- (b) Shift in 11 (length = 2)

- 10. Check test sequence while applying new configuration

- (a) Shift in 0111XXXXXXXXXXX and observe the output; update (TDR<sub>1</sub>  $\rightarrow$  TDR<sub>2</sub>  $\rightarrow$  TDR<sub>5</sub>  $\rightarrow$  SM  $\rightarrow$  SIB<sub>2</sub>  $\rightarrow$  SIB<sub>1</sub>  $\rightarrow$  SIB<sub>3</sub>)

- 11. Perform initialization

- 12. Insert test sequence

- (a) Shift in 01010101010101010 (length = 17)

- (b) Shift in 11 (length = 2)

- 13. Check test sequence while applying new configuration

- (a) Shift in 1111XXXXXXXXXXXX and observe the output; update (TDR<sub>1</sub>  $\rightarrow$  TDR<sub>2</sub>  $\rightarrow$  TDR<sub>5</sub>  $\rightarrow$  SM  $\rightarrow$  SIB<sub>2</sub>  $\rightarrow$  SIB<sub>1</sub>  $\rightarrow$  TDR<sub>3</sub>  $\rightarrow$  SIB<sub>3</sub>)

- 14. Perform initialization

- 15. Insert test sequence

- (a) Shift in 01010101010101010101010101 (length = 24)

- (b) Shift in 11 (length = 2)

- 16. Last check of the test sequence

- (a) Shift in a sequence of longest path length (24)

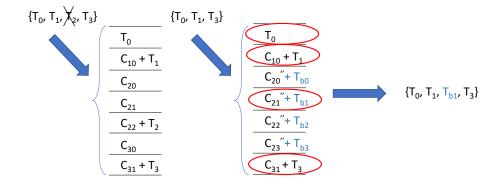

# 2.3 A Semi-Formal Test Generation Technique for Reconfigurable Scan Networks