## New Techniques for On-line Testing and Fault Mitigation in GPUs

Josie Esteban Rodriguez Condia

\* \* \* \* \* \*

### Supervisor

Prof. Matteo Sonza Reorda

#### **Doctoral Examination Committee:**

Prof. Maksim Jenihhin, Referee, Tallinn University of Technology Prof. Bernd Becker, Referee, University of Freiburg Prof. Dimitris Gizopoulos, National and Kapodistrian University of Athens Prof. Luigi Carro, Federal University of Rio Grande do Sul (UFRGS) Prof. Stefano Di Carlo, Politecnico di Torino

> Politecnico di Torino September, 2021

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that the contents and organisation of this dissertation constitute my own original work and do not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Josie Esteban Rodriguez Condia Turin, September, 2021

## Summary

Currently, Graphics Processing Units (GPUs) are crucial devices able to boost the execution of complex algorithms in the scientific and artificial intelligence domains. Moreover, GPU-based platforms are also relevant components now included in several safety-critical applications (e.g., in the automotive and autonomous machines fields), where reliability and functional safety are essential requirements.

The doctoral research activities were focused on identifying new online techniques for testing and mitigation of faults affecting GPUs.

This work also describes a new microarchitectural GPU model (FlexGripPlus), a supporting tool for detailed reliability evaluation. FlexGripPlus can also be used to support the development of functional test approaches and mitigation solutions. This GPU model is compatible with the CUDA programming environment and is a corrected and extended version of a previous GPU model implementing the G80 architecture by NVIDIA. The GPU model's extensions include support for floating-point operations and for the execution of trigonometric and transcendental operations using Special Function Units.

FlexGripPlus was used to develop, evaluate, and validate functional test techniques based on the software-based self-test (SBST) strategy. More in detail, two main strategies are proposed for GPUs: i) the multi-kernel test approach, and ii) the modular approach of testing.

On the one hand, the multi-kernel approach exploits the GPU's main operative behavior as a special-purpose accelerator. This approach is based on the parallel execution of test programs intended to detect and propagate the fault effects on any GPU core's available outputs. For this purpose, a set of parallel test programs with different GPU configuration parameters allows the generation of test patterns after dividing a target module into fault groups. This division process allows the coverage of sensitive locations that implicitly remain constant by the effect of the configuration of a parallel program. Moreover, this technique also uses a threadbased method to propagate and identify faults into the GPU's available outputs, simplifying the evaluation of specific modules in the GPU architecture, such as the pipeline registers.

On the other hand, the modular testing approach combines the microarchitectural details of a given module, its functional operation, its major constraints, and a target fault model to design a generic description of a feasible test program. More in detail, these GPU features are combined to generate a scalable high-level abstraction test program, which can later be transformed into the equivalent software routines to test a target module. This modular approach exhibited a good effectiveness when testing internal memories and the divergence stack of the GPU core.

It is worth noting that in both strategies (multi-kernel and modular), the combination of high-level programming and low-level assembly language was adopted whenever it was possible. Moreover, several compilation constraints and limitations were listed when implementing the test programs. Both functional test strategies were evaluated targeting the detection of permanent fault models.

Finally, three hybrid and flexible strategies were proposed to harden the GPU architecture. The proposed hardening solution allows the online fault testing and in-field fault mitigation. All three strategies are configurable using custom instructions, so allowing their adoption as part of the code of an application.

The first strategy is based on a flexible approach for in-field fault detection applied to the execution units of the GPU core. This strategy exploits the high regularity of the execution units and provides hardening with reduced overhead costs. The second strategy allows in-field fault mitigation of any functional unit once a fault is detected. In this approach, several in-field configurable spare units are used to provide repair capabilities in the GPU.

The third strategy aims at detecting and mitigating faults at the same time. This flexible approach allows the activation of one or both reliability features. Moreover, the reliability analysis of the proposed strategy showed a considerable increase in the reliability of the targeted units with a minor effect on the running applications code and minimal effect on performance. Furthermore, the implementation of the strategies was evaluated in several configurations, so determining different hardware overhead figures of the proposed hardware mitigation architectures. In the end, these analyzes provide a advisable configuration to obtain maximum reliability benefits with reduced hardware and performance overheads.

Thanks to the availability of the FlexGripPlus model, this work includes for the first time (to the best our knowledge) quantitative results in terms of microarchitectural reliability evaluations aimed at identifying the fault impact of transient faults on several modules of a GPU core, including the scheduler controller, the pipeline registers, the register file, and the branch unit. All these evaluations were performed using several parallel applications. Furthermore, as described above, this model was used as a validation tool in the quantitative evaluation of several online test solutions and hardening strategies for GPUs.

The main results of the research activities are intended to support the development of fault detection and fault-tolerance mechanisms for GPU devices devoted to safety-critical applications, based on the proposed solutions for online testing and mitigation of faults. Moreover, the experimental results support the evaluation of the different reliability solutions, which are required in the current trends of continuous increment of GPU devices in applications, where the effect of faults is critical.

Finally, as product of the research activities and according to the obtained experimental results, the developed strategies for functional in-field test and infield mitigation increase the reliability (in up to 50%) and functional-safety (ASIL B) of the GPU, so the combination of the developed strategies can be employed as alternative or complementary fault-tolerance mechanisms for GPUs devoted to applications in the safety-critical domain.

## Acknowledgements

- To my Mom and Dad, who encouraged me with tremendous moral support and reminded me to follow my dreams.

- To my sister Melissa and my cousin Sebastian, who supported me with good vibes and fun when were required.

- I would like to express my respect and huge thanks to my mentor and advisor, Prof. Matteo Sonza Reorda, for the vast support and for showing me how simple ideas can turn into reality with discipline and hard work.

- To my friends Aleksa D., Andrea F. and Pratyush K. for the academic and moral support in all steps of this journey.

- To my friends "*ESRs*" from RESCUE-ETN project for the huge support; each meeting was a way to recharge myself with good energy to continue working with more determination.

- To the RESCUE-ETN project, to make this journey possible.

- To all the people that in any way contributed to the development of this work. Gracias a todos!

### And I dedicate my roses to no one

Roses to No One The Savage Poetry, 2000 Edguy

ר**י** ....

## Contents

| List of Tables XI     |      |                                                                  | XIII |

|-----------------------|------|------------------------------------------------------------------|------|

| List of abbreviations |      |                                                                  |      |

| 1                     | Intr | oduction                                                         | 1    |

|                       | 1.1  | Main Motivation                                                  | 1    |

|                       | 1.2  | Contribution                                                     | 5    |

| 2                     | GP   | Us in safety-critical applications                               | 9    |

|                       | 2.1  | Architectural organization of a GPU                              | 11   |

|                       |      | 2.1.1 The Streaming Multiprocessor                               | 13   |

|                       |      | 2.1.2 Execution units                                            | 15   |

|                       |      | 2.1.3 Special Function Units                                     | 16   |

|                       |      | 2.1.4 Memory hierarchy                                           | 17   |

|                       |      | 2.1.5 Scheduler Controllers                                      | 18   |

|                       | 2.2  | GPU devices Reliability                                          | 20   |

|                       | 2.3  | GPU models as tools for reliability research                     | 23   |

|                       |      | 2.3.1 Functional models                                          | 23   |

|                       |      | 2.3.2 Microarchitectural Models                                  | 25   |

|                       | 2.4  | From FlexGrip to FlexGripPlus                                    | 26   |

|                       |      | 2.4.1 Technology dependency                                      | 28   |

|                       |      | 2.4.2 Instruction format support                                 | 28   |

|                       |      | 2.4.3 Compiler restrictions                                      | 29   |

|                       | 2.5  | Conclusions                                                      | 33   |

| 3                     | Ana  | alysis of transient fault effects in GPUs                        | 35   |

|                       | 3.1  | Experimental set up for transient fault injection campaigns      | 36   |

|                       |      | 3.1.1 Fault injection environment                                | 36   |

|                       |      | 3.1.2 Benchmarks                                                 | 39   |

|                       | 3.2  | Analyzing the data path modules in a GPU against transient fault |      |

|                       |      | effects                                                          | 40   |

|   |      | 3.2.1            | Register File                                                 | 41           |

|---|------|------------------|---------------------------------------------------------------|--------------|

|   |      | 3.2.2            | Pipeline Register                                             | 42           |

|   | 3.3  | Analy            | zing the control path modules in GPUs                         | 44           |

|   |      | 3.3.1            | Scheduler controller                                          | 45           |

|   |      | 3.3.2            | Divergence stack                                              | 50           |

|   | 3.4  | Analy            | zing CNN workloads to assess fault impacts in GPU modules     | 52           |

|   |      | 3.4.1            | Proposed characterization strategy                            | 53           |

|   |      | 3.4.2            | Experimental results                                          | 57           |

|   | 3.5  | Conclu           | usions                                                        | 63           |

| 4 | Fun  | ctiona           | l testing on GPUs: Software-based solutions for in-field      | l            |

|   | faul | t dete           | ction                                                         | 65           |

|   | 4.1  | Functi           | ional test of the warp scheduler controller in GPUs           | 66           |

|   |      | 4.1.1            | A method for functional testing for the Scheduler Controller  | 68           |

|   |      | 4.1.2            | Experimental Analysis                                         | 72           |

|   |      | 4.1.3            | An on-line testing technique for the scheduler memory of a    |              |

|   |      |                  | GPU                                                           | 78           |

|   |      | 4.1.4            | Effects of permanent faults in the memory of the Scheduler    |              |

|   |      |                  | controller                                                    | 80           |

|   |      | 4.1.5            | Fault primitives for the memory in the scheduler              | 81           |

|   |      | 4.1.6            | Operational restrictions of the memory in the scheduler       | 84           |

|   |      | 4.1.7            | Adapting FPs to test the memory in the scheduler              | 86           |

|   |      | 4.1.8            | Methods to Generate SBST Patterns for the Scheduler Memory    |              |

|   |      | 4.1.9            | Test Pattern Generation                                       | 89           |

|   | 4.0  | 4.1.10           | 1                                                             | 103          |

|   | 4.2  |                  | kernel approach of functional test on GPUs                    | 109          |

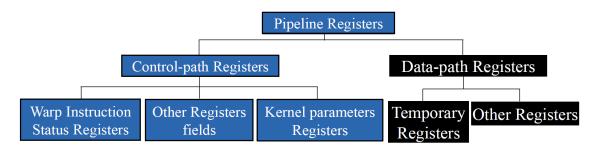

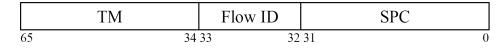

|   |      | 4.2.1            | PRs in GPU architectures                                      | 110          |

|   |      | 4.2.2            | Proposed approach                                             | 111          |

|   | 4.9  | 4.2.3            | Experimental results                                          | 117          |

|   | 4.3  |                  | lar testing of GPUs                                           | 120          |

|   |      | 4.3.1            | Embedded memories in the GPU core                             | 121          |

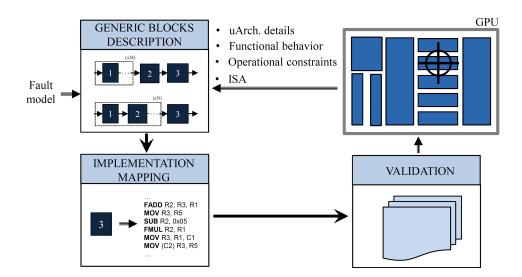

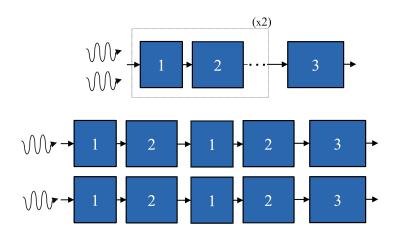

|   |      | $4.3.2 \\ 4.3.3$ | A modular approach of functional testing                      | 123<br>126   |

|   |      | 4.3.3<br>4.3.4   | Stack Memory    Predicate Register File                       | 126<br>133   |

|   |      | 4.3.4<br>4.3.5   | Address Register File and Vector Register File                | $135 \\ 135$ |

|   |      | 4.3.6            | Limitations and constraints                                   | 138          |

|   |      | 4.3.7            | Experimental results                                          | 138          |

|   | 4.4  |                  | lementary test strategies and general overview of the SBST    | 100          |

|   | 7.7  | -                | gy on GPUs                                                    | 144          |

|   |      | 4.4.1            | Adapting automated approaches of functional test on GPUs      | 144          |

|   |      | 4.4.2            | Overall evaluation of the SBST strategy in GPUs               | 147          |

|   |      | 4.4.3            | Functional safety evaluation of the SBST strategy in GPUs.    | 148          |

|   |      | 1.1.0            | i dictional ballety contraction of the SDST behavesy in GIOS. | <b>T T</b> O |

|   | 4.5 | Conclusions                                                                      |

|---|-----|----------------------------------------------------------------------------------|

| 5 |     | xible hybrid mechanisms for in-field fault detection and miti-<br>on in GPUs 153 |

|   | 5.1 | DDWC: A Dynamic Hardware Mechanism for In-field Fault Detec-                     |

|   | 0.1 | tion in GPUs                                                                     |

|   |     | 5.1.1 Main idea of the DDWC mechanism                                            |

|   |     | 5.1.2 Implementation and experimental evaluation                                 |

|   |     | 5.1.3 Experimental Results                                                       |

|   | 5.2 | BISR: a dynamic reconfiguration mechanism to increase the reliabil-              |

|   |     | ity of GPUs                                                                      |

|   |     | 5.2.1 BISR mechanism in GPU cores                                                |

|   |     | 5.2.2 Experimental Results                                                       |

|   | 5.3 | DYRE: a flexible solution to increase GPU's reliability 179                      |

|   |     | 5.3.1 Proposed DYRE architecture                                                 |

|   |     | 5.3.2 Experimental Results                                                       |

|   |     | 5.3.3 Power and performance analysis                                             |

|   |     | 5.3.4 Reliability analysis                                                       |

|   | 5.4 | Conclusions                                                                      |

| 6 | Cor | clusions 191                                                                     |

| Ũ | 6.1 | Summary                                                                          |

|   | 6.2 | Main contributions                                                               |

|   |     | 6.2.1 Reliability evaluation of GPUs                                             |

|   |     | 6.2.2 Functional software-based self-testing of GPUs                             |

|   |     | 6.2.3 Fault mitigation strategies for GPUs                                       |

|   | 6.3 | Future works                                                                     |

| 7 | Pub | plication list 197                                                               |

|   | 7.1 | Part of the research work                                                        |

|   | 7.2 | Other publications                                                               |

| Α | The | FlexGripPlus GPU model 201                                                       |

|   |     | A.0.1 Warp Scheduler controller                                                  |

|   |     | A.0.2 Convergence management unit                                                |

|   |     | A.0.3 Memory hierarchy                                                           |

|   |     | A.0.4 Functional units 205                                                       |

|   |     | A.0.5 Supported instructions                                                     |

|   |     |                                                                                  |

## List of Tables

| 2.1   | Comparative analysis of main features in the FlexGrip and Flex-        |       |

|-------|------------------------------------------------------------------------|-------|

|       | GripPlus models                                                        | 31    |

| 3.1   | Main features of the benchmarks used in the experiments                | 40    |

| 3.2   | Size of the PRs according to the number of SPs in the SM of Flex-      |       |

|       | GripPlus.                                                              | 43    |

| 3.3   | Distribution of SEU effects in the scheduler causing single and mul-   |       |

|       | tiple errors in the outputs.                                           | 47    |

| 3.4   | Microarchitectural Fault Injection Results                             | 58    |

| 4.1   | Fault detection results in warp pool memory                            | 76    |

| 4.2   | Fault detection results in the interconnections of the scheduler con-  |       |

|       | troller of the GPU                                                     | 77    |

| 4.3   | Effects of permanent faults affecting the memory in the scheduler      |       |

|       | controller                                                             | 82    |

| 4.4   | Fault primitives for a single memory cell                              | 82    |

| 4.5   | Static Fault Primitives for coupling cells in memory                   | 84    |

| 4.6   | Selected test patterns for coupling fault detection in a LE            | 90    |

| 4.7   | MATS+ and (*) MATS++ operations as a sequence of CUDA kernel           |       |

|       | executions                                                             | 99    |

| 4.8   | Example of a TP sequence for coupling fault evaluation                 | 102   |

| 4.9   | Performance parameters of the implemented test programs to eval-       |       |

|       | uate different LE sizes. The symbol (+) identifies the cost for active |       |

|       | kernel functions, only                                                 | 103   |

| 4.10  | Fault coverage of the MATS++ test kernels for a SC memory with         |       |

|       | 32 LEs. (*) FPs that were not initially considered in the proposed     |       |

|       | technique.                                                             | 106   |

| 4.11  | Performance parameter for the original and optimized version of a      | 100   |

| 1 10  | test kernel. (*) The resource overhead is calculated per kernel        | 108   |

|       | General information about PRs in FlexGripPlus (Control-Path only).     | . 111 |

| 4.13  | Characteristics of the implemented test kernels and applications. (*)  | 110   |

| 4 1 4 | using the CPT.                                                         | 118   |

|       | FC of selected applications in control-path fields of PRs              | 118   |

| 4.15  | FC of the proposed SBST approach                                       | 119   |

| 4.16 | FC in the individual pipeline registers (PRs)                       | 119 |

|------|---------------------------------------------------------------------|-----|

| 4.17 | Performance parameters of the SBST programs using the two ap-       |     |

|      | proaches to detect permanent faults in the LEs                      | 139 |

| 4.18 | FC results for the representative benchmarks and the proposed SBST  |     |

|      | strategies                                                          | 142 |

| 4.19 | Main features and fault coverage of several test programs for the   |     |

|      | functional units (SP and SFU) in the GPU.                           | 146 |

| 4.20 | A summary of the FC obtained for the different modules of the Flex- |     |

|      | GripPlus GPU model using the proposed SBST approaches. All test     |     |

|      | programs were used to determine the FC of the module                | 147 |

| 5.1  | Hardware and performance overhead of the DDWC mechanism for         |     |

|      | multiple configurations in the GPU core using the 45nm technology   |     |

|      | library                                                             | 162 |

| 5.2  | Hardware overhead of the BISR mechanism for multiple configura-     |     |

|      | tions of the GPU                                                    | 176 |

| A.1  |                                                                     | 206 |

| A.2  | Arithmetic and logic instructions in FlexGripPlus                   | 207 |

| A.3  | Data handling and memory instructions in FlexGripPlus               | 208 |

| A.4  | Floating Point Unit (FPU) instructions supported in FlexGripPlus.   | 208 |

| A.5  | Special Function Unit (SFU) instructions supported in FlexGripPlus. | 208 |

## List of Figures

| 1.1 | Principal investments in the automotive sector (Top), Trends in the                                                                   |            |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.1 | market (Bottom) Extracted from McKinsey Analysis.                                                                                     | 3          |

| 1.2 | A scheme of the trend of FIT rate of transistor integration technolo-                                                                 | 0          |

|     | gies. Adapted from [16].                                                                                                              | 5          |

| 2.1 | A general scheme of a modern GPU architecture.                                                                                        | 13         |

| 2.2 | A general scheme of the internal organization of a Streaming Multi-                                                                   | -          |

|     | processor in a GPU.                                                                                                                   | 15         |

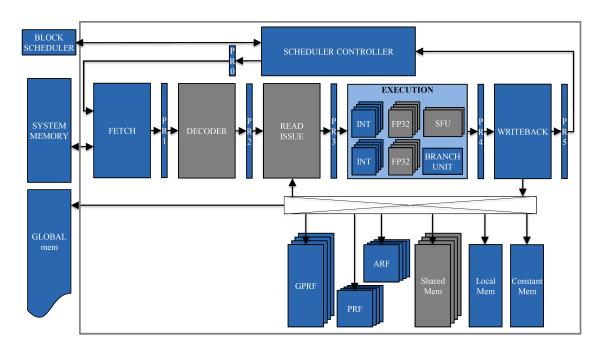

| 2.3 | A general scheme of the internal organization of one SM core in the                                                                   |            |

|     | FlexGripPlus GPU model. The modules in gray represent the added                                                                       |            |

|     | modules or modified from the FlexGrip model                                                                                           | 32         |

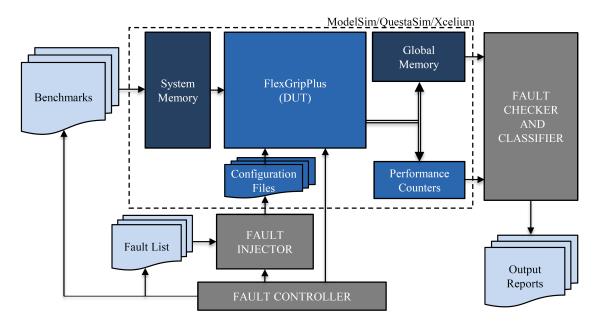

| 3.1 | A general scheme of the custom environment for the fault injection                                                                    |            |

|     | campaigns                                                                                                                             | 38         |

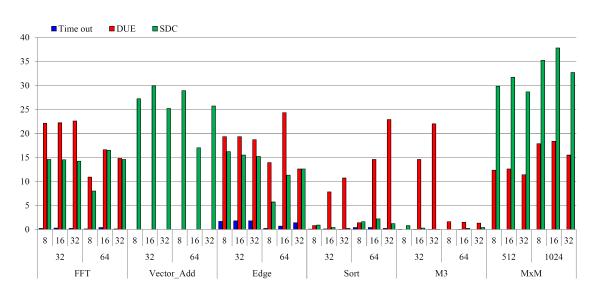

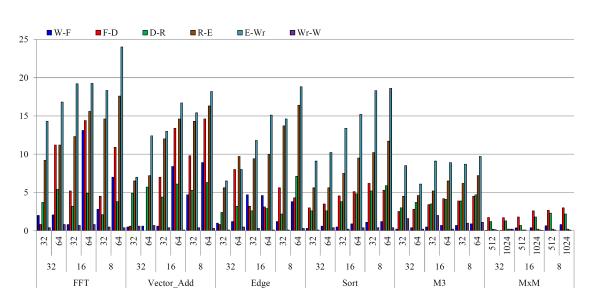

| 3.2 | Fault rate results in the RF of FlexGripPlus (the horizontal axis,                                                                    |            |

|     | from top to bottom, are $\#$ SPs, $\#$ Threads and application name).                                                                 | 42         |

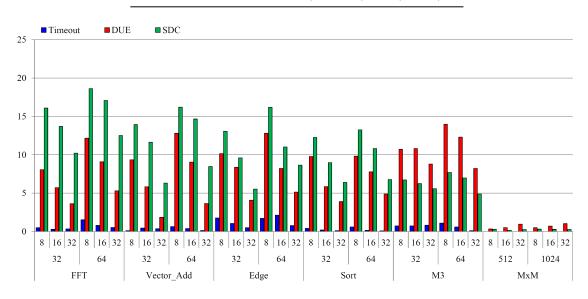

| 3.3 | Fault rate results in the PRs in FlexGripPlus (the horizontal axis,                                                                   |            |

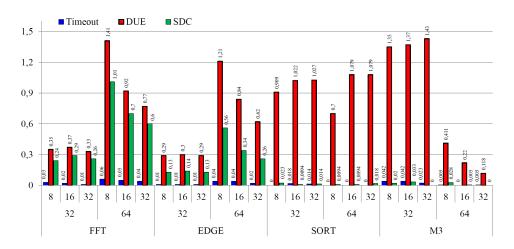

|     | from top to bottom, are $\#$ SPs, $\#$ Threads and application name).                                                                 | 43         |

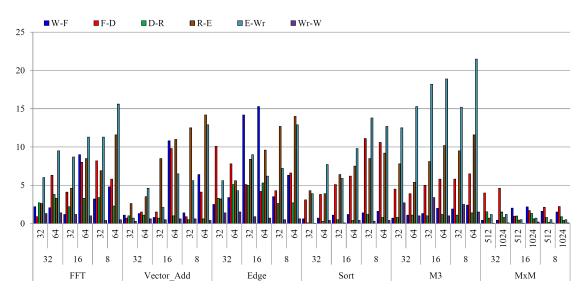

| 3.4 | SDC rate results per pipeline register in the SM for the evaluated                                                                    |            |

|     | applications (the horizontal axis, from top to bottom, are #threads,                                                                  |            |

|     | #SPs and application name)                                                                                                            | 45         |

| 3.5 | DUE rate results per pipeline register in the SM for the evaluated                                                                    |            |

|     | applications (the horizontal axis, from top to bottom, are #threads,                                                                  |            |

|     | #SPs and application name).                                                                                                           | 45         |

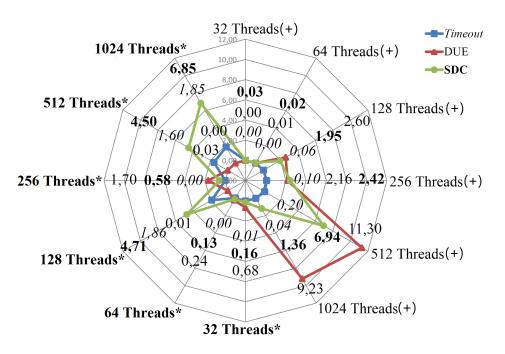

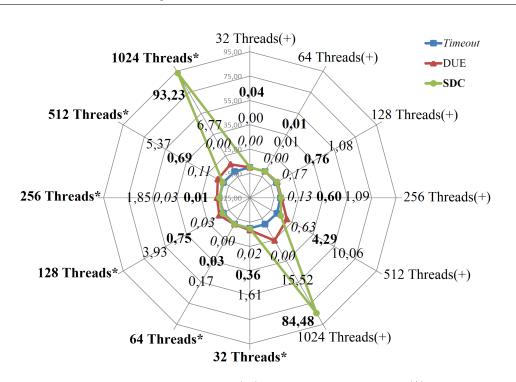

| 3.6 | AVF results in the memory $(+)$ and the control logic $(*)$ of the sched-                                                             |            |

|     | uler controller of the GPU when executing the VectorAdd application                                                                   | 40         |

| 2.7 | and increasing the number of threads                                                                                                  | 49         |

| 3.7 | AVF results in the memory $(+)$ and the control logic $(*)$ of the sched-                                                             |            |

|     | uler controller of the GPU when executing the M3 application and increasing the number of threads                                     | 50         |

| 20  | increasing the number of threads.                                                                                                     | 50         |

| 3.8 | Fault injection results for the Divergence module (the horizontal axis, from top to bottom, are #SPs, #Threads and application name). | 51         |

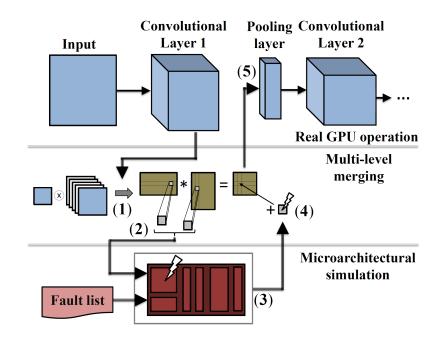

| 3.9 | A general scheme of the proposed method                                                                                               | $51 \\ 54$ |

| 0.9 | A general scheme of the proposed method.                                                                                              | 04         |

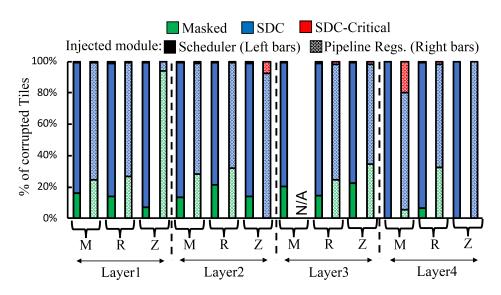

| 3.10 | Corrupted Max (M), Random (R), and Zero (Z) tiles that propagate to LeNet output generating a critical/not critical SDC or are masked.                                                                                                                                                                   | 59         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

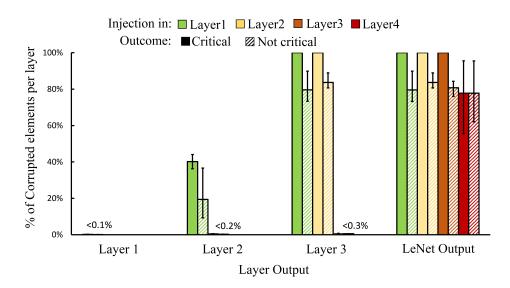

| 3.11 | Percentage of corrupted elements in a layer output for injections in<br>the layer identified by the bars color. As the fault propagates thought<br>the layers the percentage of corrupted element significantly increases.<br>Solid lines are critical errors, and dashed lines are not critical errors. |            |

|      | Error bars report the maximum difference between Z, R, and M tiles.                                                                                                                                                                                                                                      | 61         |

| 3.12 | Magnitude (left) and spatial (right) distribution of the effect of faults<br>in the scheduler of the GPU when operating tiles of the LeNET CNN.                                                                                                                                                          |            |

| 4.1  | Pseudocode for method M1 (white), M2 (white and light gray), and M3 (white and dark gray).                                                                                                                                                                                                               | 71         |

| 4.2  | General pseudocode for a routine implementing Method M1. Z is<br>the number of threads per block or threads defined for the application.                                                                                                                                                                 | 74         |

| 4.3  | Pseudo-CUDA-code for method M2. Z is the number of threads per                                                                                                                                                                                                                                           |            |

| 4 4  | block or thread in the application.                                                                                                                                                                                                                                                                      | 76         |

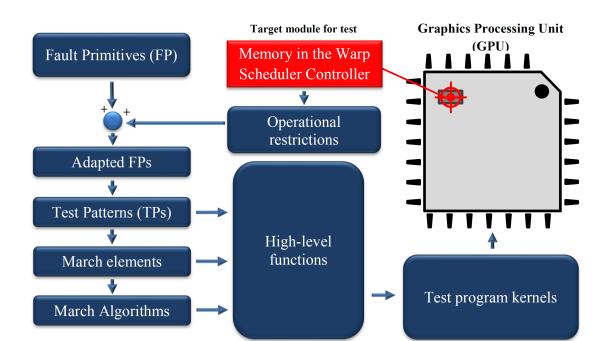

| 4.4  | General scheme of the proposed approach for mapping TPs targeting<br>FPs into test kernels.                                                                                                                                                                                                              | 80         |

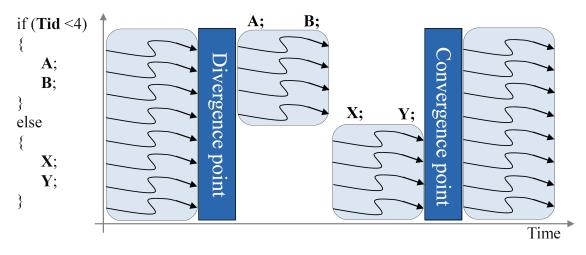

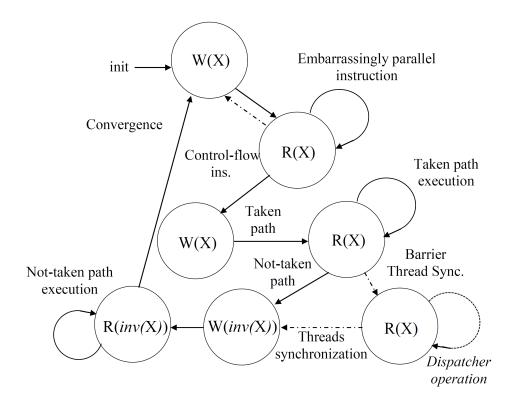

| 4.5  | A general scheme of the classical intra-warp divergence management<br>for the NIVIDIA's Pascal and previous GPU architectures                                                                                                                                                                            | 89         |

| 4.6  | A general scheme of the write and read operations generated by a                                                                                                                                                                                                                                         |            |

|      | divergence path function in a bit of the TAM field. The nesting                                                                                                                                                                                                                                          | 90         |

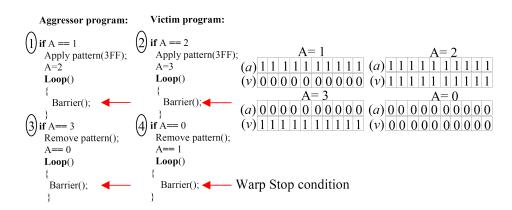

| 4.7  | divergence case is not considered in the scheme                                                                                                                                                                                                                                                          | 90         |

|      | consecutive aggressor and victim cells.                                                                                                                                                                                                                                                                  | 92         |

| 4.8  | A normal sequence of March operations and the adapted approach<br>for the scheduler memory, (*) Example of initialization operations.                                                                                                                                                                    | 98         |

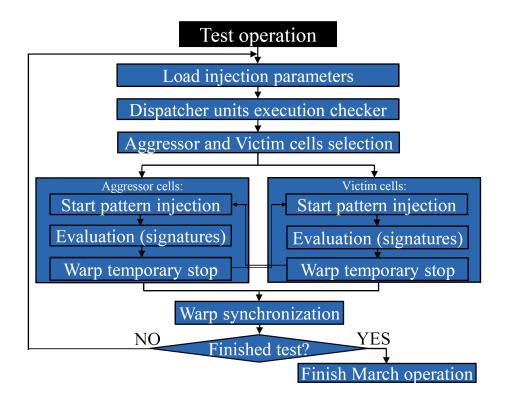

| 4.9  | A general flow diagram of the test algorithm for the TAM and WPC fields in the scheduler memory.                                                                                                                                                                                                         | 100        |

| 4.10 | A pseudocode (CUDA) describing the program kernel implementation to detect coupling faults. $(¥)$ Functions to generate divergence                                                                                                                                                                       | 100        |

|      |                                                                                                                                                                                                                                                                                                          | 101        |

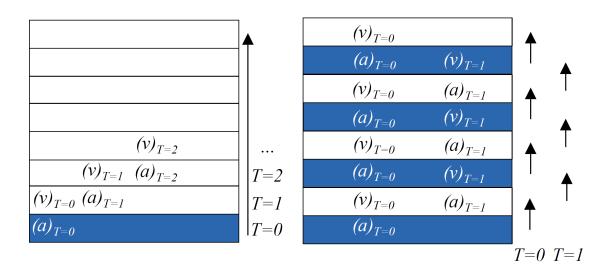

| 4.11 | Proposed methods to apply a March operation including the direc-<br>tion parameter. (Left) Sequential method using software techniques<br>to skip the dispatcher unit operation. (Right) Using a parallel arbi-                                                                                          |            |

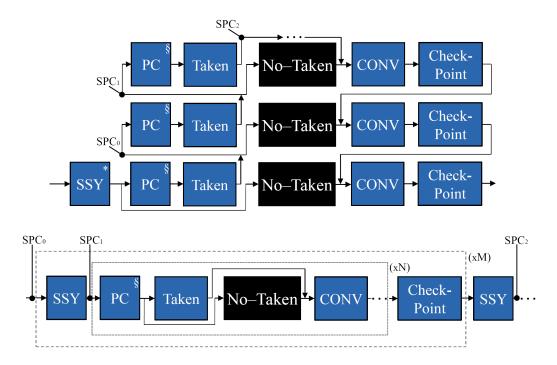

| 4.12 | trary injection in pairs of LEs                                                                                                                                                                                                                                                                          | $107\\112$ |

|      | Pseudo-code of the routine targeting the WPC fields. (*) Assembly<br>instructions manually included. The subroutines where explicitly                                                                                                                                                                    |            |

|      |                                                                                                                                                                                                                                                                                                          | 113        |

| 4.14 | Pseudo-code of the test program for the ATHM fields. (*) Assembly                                 |       |

|------|---------------------------------------------------------------------------------------------------|-------|

|      | instructions included                                                                             | 114   |

| 4.15 | Organization of the LEs in the stack memory of FlexGripPlus                                       | 122   |

| 4.16 | A general scheme of the proposed modular approach to develop func-                                |       |

|      | tional test programs.                                                                             | 124   |

| 4.17 | An example of the modular organization of a test program. General                                 |       |

|      | organization and test program description (Top), Equivalent organi-                               |       |

|      | zation per thread (Bottom)                                                                        | 125   |

| 4.18 | A general scheme of the proposed modular SBST strategies Nest-                                    |       |

|      | ing (Top) and Sync-Trick (Bottom) to test the stack memory. (*)                                   |       |

|      | Optional function to test the odd LEs. (§) Optional functions to                                  |       |

|      | distribute the test functions in the system memory                                                | 128   |

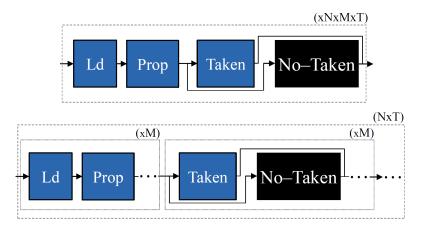

| 4.19 | General schemes of the modular approaches to test the PRF                                         | 134   |

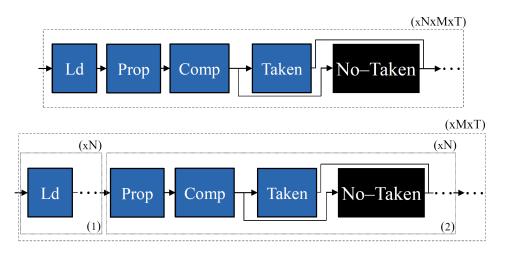

| 4.20 | General schemes of the modular approaches to test the ARF and VRF.                                | 137   |

| 5.1  | A general scheme of the proposed DDWC structure for in-field fault                                |       |

|      | 1 1                                                                                               | 158   |

| 5.2  | Examples of code modifications when using the DDWC mechanism.                                     |       |

|      | The static selection (left) maintains configuration according to the                              |       |

|      | constant channel CH0. The dynamic selection (right) employs a gen-                                |       |

|      | eral purpose register to address any channel, so allowing the online                              |       |

|      | configuration of the DDWC mechanism.                                                              | 161   |

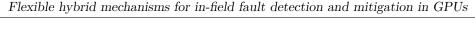

| 5.3  | Fault coverage results for several applications when enabling the                                 |       |

|      |                                                                                                   | 164   |

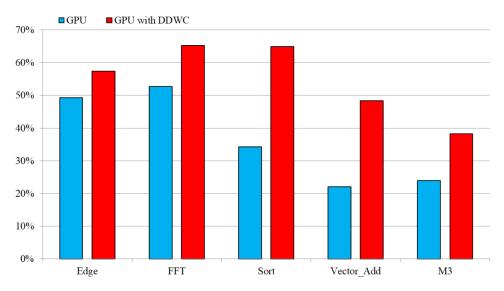

| 5.4  | The maximum value of ETFD for multiple frequencies of the DDWC_i                                  |       |

|      | instruction (100, 200, 300, and 400 instructions) in the application                              |       |

|      | code and under multiple SPs configurations in the SM                                              | 166   |

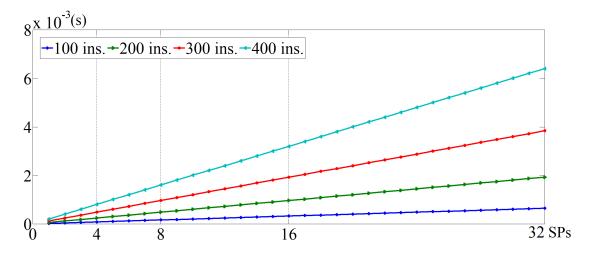

| 5.5  | A general scheme of the detection, identification, and configuration                              |       |

|      |                                                                                                   | 170   |

| 5.6  | A general scheme of the adopted circular switching method for SP                                  | -     |

|      | 0                                                                                                 | 170   |

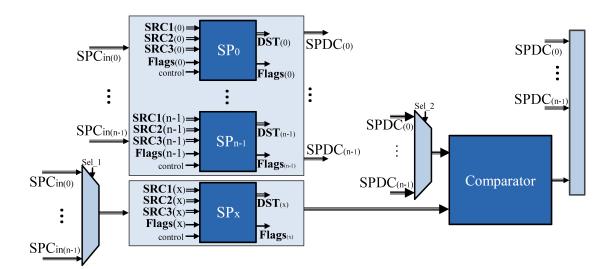

| 5.7  | A general scheme of the implemented structure in the FlexGripPlus                                 | 1 = 0 |

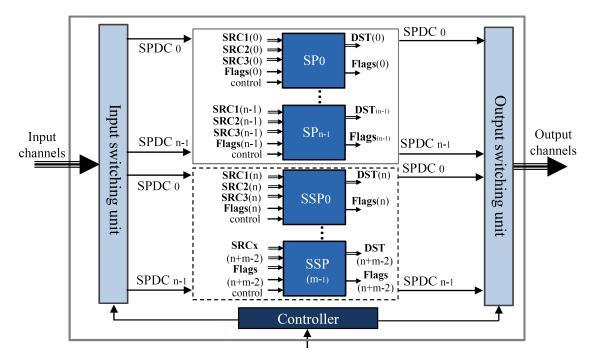

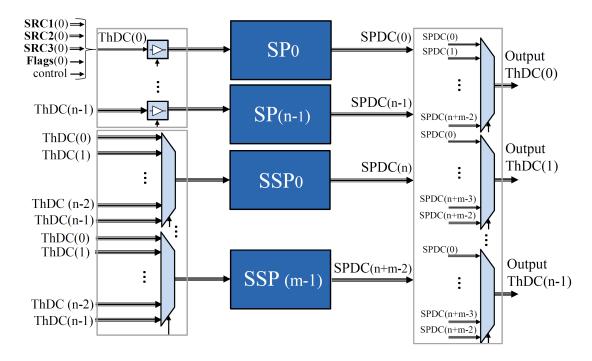

| -    |                                                                                                   | 173   |

| 5.8  | Improvement in the reliability of the BISR structure for multiple                                 |       |

|      | probabilities of correct execution under multiple configurations of                               | 170   |

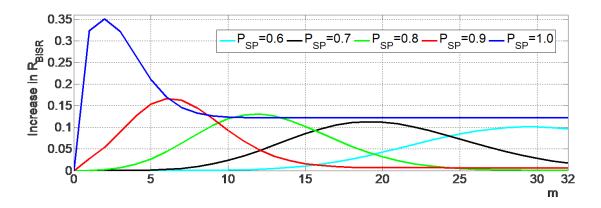

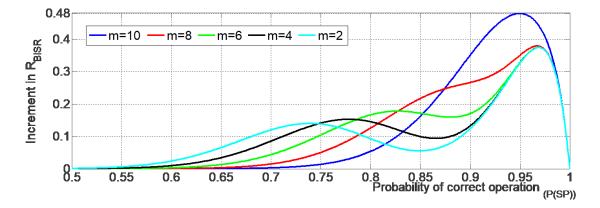

| 5.0  | the SSPs (m).                                                                                     | 178   |

| 5.9  | Improvement in the reliability of the system RBISR with respect to                                | 170   |

| 5 10 | 1 0 ( )                                                                                           | 178   |

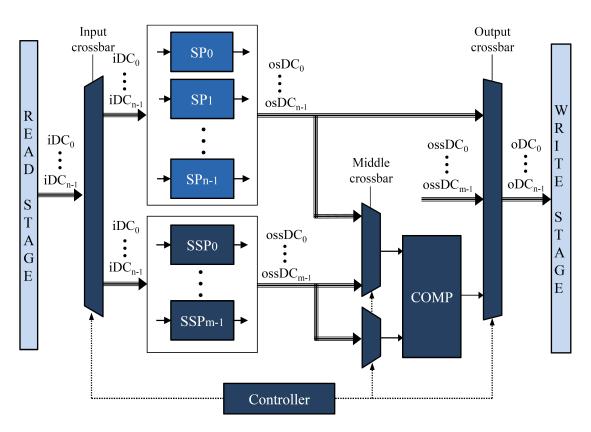

| 5.10 | A general scheme of the Execute stage of a GPU with the DYRE                                      | 101   |

| 5 11 | architecture.                                                                                     | 181   |

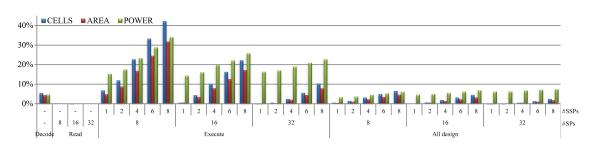

| 0.11 | Percentage of overhead cost of the DYRE architecture on each adapted module and in the ontine CPU | 101   |

|      | module and in the entire GPU.                                                                     | 184   |

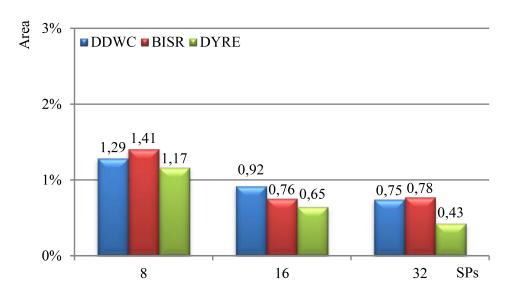

| 5.12 | Area overhead for the DDWC, BISR and DYRE architectures with             |     |

|------|--------------------------------------------------------------------------|-----|

|      | respect to the original design evaluated in the 8, 16 and 32 SP cores $$ |     |

|      | configurations with one SSP                                              | 185 |

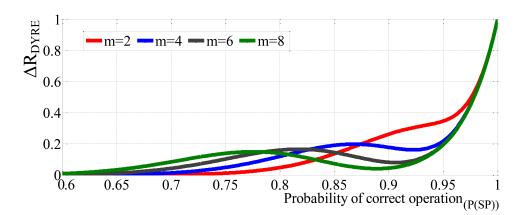

| 5.13 | Reliability benefit in the system for multiple probabilities of correct  |     |

|      | operation                                                                | 188 |

| 5.14 | Reliability comparison of a standard GPU and other using the two         |     |

|      | features of the DYRE architecture with two SSPs                          | 188 |

| A.1  | A general scheme of the scheduler controller in one SM of the Flex-      |     |

|      | GripPlus model.                                                          | 202 |

## List of abbreviations

**ABFT** Algorithm-Based Fault-Tolerance **aTM** Active Threads Mask **ADAS** Advanced Driver-Assistance Systems **AFFP(SCH)** Addressable Functional Fault Primitive for the scheduler **AI** Artificial Intelligence **ARF** Address Register File **ASIL** Automotive Safety Integrity Level **AVF** Architectural Vulnerability Factor Acc Accumulative **BBK** Basic Block Kernel **BISR** Built-In Self-Repair **BIST** Build-In Self-Test **CFR** Component Fault Rate **CFst** State Coupling Faults **CMU** Convergence Management Unit **CNN** Convolutional Neural Network **CORDIC** COordinate Rotation DIgital Computer **CP** Convergence Point **CUDA** Compute Unified Device Architecture **CpT** Counter-per-Thread C Carry **DDWC** Dynamic Duplication With Comparison **DETT** DETection Trigger **DMR** Double Modular Redundancy **DMU** Divergence Management Unit **DRDF** Deceptive Read destructive fault **DUE** Detected Unrecoverable Error **DWC** Duplication with Comparison **DYRE** DYnamic REconfigurable structure for infield detection and mitigation of faults **Dec** Detection **DfT** Design for Testability **Dia** Diagnosis **ECC** Error Correcting Code **EMI** Electromagnetic Interference **ETFD** Estimate the time for fault detection **EU** Execution Unit FAS Fault Administration Structure

FC Fault Coverage

${\bf FFT}$  Fast Fourier Transformation

**FIT** Failures In Time **FPGA** Field Programmable Gate Arrays **FP** Fault Primitives FP32/FP64 Floating-Point Unit **FUF** Functionally Untestable Fault **GEMM** General Matrix Multiplication **GPGPU** General-Purpose Graphics Processing Unit **GPRS** General-Purpose Registers **GPU** Graphics Processing Unit **HPC** High Performance Computing **IM** Infant Mortality **INT** Integer Units **IP** Intellectual Property **IRF** Incorrect Read Faults **ISA** instruction set architecture **IST** In-System-Structural-Test **LBIST** Logic Build-In Self-Test **LE** Line Entry LRU Least Recently Used LSU Load/Store unit **MBIST** Memory Build-In Self-Test MIMD Multiple-Instruction Multiple-Data **MITT** MITigation Trigger **MxM** Matrix Multiplication M Max **NVM** Non Volatile Memory **OpenCL** Open Computing Language **O** Overflow **PRF** Predicate Register File **PRs** Pipeline Registers **PTX** Parallel Thread Execution pseudo-language **R(x)** Reading **RAM** Random Access Memory **RCP** Reciprocal **RDF** Read destructive fault **RFU** Register Forwarding Unit **RF** Register File **RISC** Reduced-Instruction Set Computer **RSQ** Reciprocal of the Square Root **RTL** Register Transfer Level  $\mathbf{R}$  Random **SASS** Streaming ASSembly language

**SBST** Software-Based Self-Testing **SBU** Single Bit Upset SC Scheduler Controller **SDC** Silent Data Corruption **SEU** Single Event Upset **SFU** Special Function Unit **SIMD** Single-Instruction Multiple-Data **SIMT** Single-Instructions Multiple-Thread **SM** Streaming Multiprocessor **SOS** Sensitizing Operation Sequence **SPC** Program Counter of a warp **SPDC** Output Data Channel of an Streaming Processor SPs Streaming/Scalar Processor SPx Redundant Streaming Processor **SSP** Spare Streaming Processor **ST** Execution Time SoCs Systems-On-Chips **SpT** Signature-per-Thread S Sign **TAM** Thread Mask **TCU** Tensor Core Unit **TFC** Testable Fault Coverage **TF** Transition fault **TLM** Transaction-Level Modeling **TMR** Triple Module Redundancy **TM** Thread Mask **TP(SCH)** Test Pattern for the scheduler **TPB** Threads per block  ${\bf TP}$  Test Pattern **UDR** Utilization De-Rating **VHDL** Very High Speed Integrated Circuit Hardware Description Language **wPC** Warp Program Counter W(x) Writing **WDF** Write destructive fault **XBIST** X-state Build-In Self-Test  $\mathbf{Z}$  Zero

## Chapter 1 Introduction

Currently, new technologies boost our life quality in numerous aspects while increasing the productivity and the efficiency in the society. Simple examples, such as innovative environmental-friendly transportation systems and high-end production methods, reduce the human effort, and optimize appliances and services' production.

In case of automotive systems, new technology trends are focused on introducing new features, which extend the number of on-board embedded systems (and processors) [1]. In the automotive domain, these systems are intended to optimize energy consumption, extend the user's experience by introducing infotainment support, and also provide autonomous and semi-autonomous control mechanisms, including strategies for cruise control and autonomous pilot [2]. Furthermore, in the production case, new tendencies of automation promote cooperative work environments between humans and autonomous robots interacting and increasing the production. Moreover, this automation method aims at reducing the human risk when hazard conditions are involved.

Both cases (automotive and industrial production) are current examples of safety-critical applications where any functional failure of the equipment, machines or devices supporting the application can generate severe consequences, including critical injuries, deaths, significant property damage or extensive environmental damages [3]. For this purpose, the complex electronic devices, which are now integrated into systems, must accomplish strict safety, reliability and security constraints to guarantee the correct operation of the entire system.

#### **1.1** Main Motivation

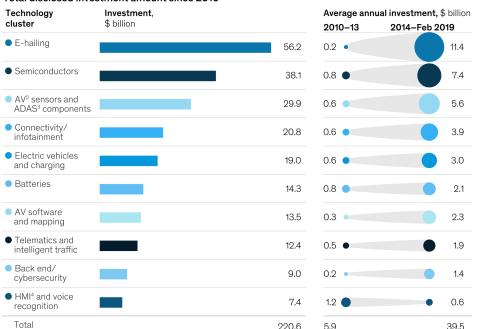

In the automotive sector, leading companies have invested (and plan to invest) billions in new technologies to implement and extend their usage to several applications involved in the sector, as reported in Figure 1.1. Those applications include

the development of various levels of autonomy in vehicles motivated by the benefits in terms of safety and security for the users, latency reduction in the traffic and energy efficiency. However, these technological benefits also imply several technology challenges without clear solutions till the moment.

In principle, mature methods of design and development of safe and secure devices can be employed for devices used in these new applications. However, both sectors (automotive and autonomous machines) now exploit several innovative technologies, such as Artificial Intelligence (AI) and computer vision, which suppose a big advantage for more efficient procedures. However, this trend also implies that modern devices can implement such sophisticated algorithms, so increasing the application's complexity and imposing huge restrictions in terms of real-time operation, available power budget and performance.

In practice, the development of modern safety-critical applications require mainly three elements: i) a high performance operation and power efficiency, ii) affordable costs, and iii) safety and reliability [4]. In many cases, these requirements are faced by most manufacturers and designers using the latest transistor technology and scaling approaches in their products, so reaching the limits of the Moore's law in order to include a high number of transistors in the same device, so obtaining considerable improvements in execution performance, power consumption and practical production costs. However, several studies [5], [6], [7], [8], [9] demonstrated that new devices implemented with these cutting-edge technologies are also prone to be affected by multiple types of faults arising at the early operational stages and, more frequently, during their operative life. These faults can be caused by two main factors: i) internal defects derived by the manufacturing processes or component fatigues, and ii) environmental or external ones [10].

In the first case, the faults in a device can be the consequence of manufacturing defects that were not identified or detected during the end-of-production testing, so causing unexpected behaviors during its operative life. Furthermore, a device is also prone to suffer of degradation (e.g., electromigration or gate-oxide effects) of its components after long-periods of operation, or even when the device is not used (e.g., idle operational mode) [11], and produce intermittent or permanent faults. In the previous scenarios, the faults are produced by aging or wearout effects [12], [13], [14].

On the other hand, external effects can also affect the operation of a device. In this case, environmental effects change the electrical parameters temporary (or permanently) and produce transient fault effects, so affecting the running application in the device. These fault effects are propagated across the device as soft-errors, which are produced only when the application is running on an affected device.

The exposure of a device to high energy particles (producing radiation effects) or to electromagnetic interference (EMI) increases the sensibility of the device to temporary fault (transient faults), which swap the electronic charge of any or multiple storage components in the device, so switching ON or OFF a transistor used

1.1 – Main Motivation

Total disclosed investment amount since 2010<sup>1</sup>

<sup>1</sup>Sample of 1,183 companies. Using selected keywords and sample start-ups, we were able to identify a set of similar companies according to text-similarity algorithms (similarity to companies' business description) used by the Competitive Landscape Analytics team. <sup>3</sup>Autonomous vehicle. <sup>3</sup>Advanced driver-assistance system.

<sup>1</sup>Human machine interface Source: CapitalIQ; Pitchbook; McKinsey analysis

Automotive software, and E/E<sup>1</sup> Automotive sales, Compound annual growth 2020-30, \$ billion market, 2020-30, \$ billion rate, 2020-30, % 3,800 469 Software (functions, ~9 OS, middleware) Integration, verification, 3,027 ~10 362 and validation services 2,755 Electronic control units (ECUs)/domain control units (DCUs) 238 20 13 Sensors Power electronics 81 ~15 (excluding battery cells) 50 Other electronic 85 63 76 components<sup>2</sup> 2020 2025 2030 2020 2025 2030 Note: Figures may not sum, because of rounding. 'Electrical and electronic components.

~5

~8

~3

Figure 1.1: Principal investments in the automotive sector (Top), Trends in the market (Bottom) Extracted from McKinsey Analysis.

to store data. When this data is propagated through the circuit, several errors can arise in the application. In the most extreme case, the device can be permanently damaged as effect of those external interventions.

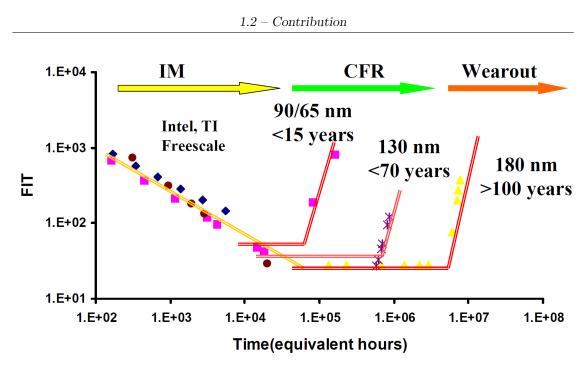

Modern processors and also accelerators, such as Graphics Processing Units (GPUs), which are implemented with the latest integration technologies, can suffer from both types of faults. In fact, the Failures In Time (FIT) rate is larger than it was before in the previous technology scaling generations (see Figure 1.2). Thus, these technology issues originate new reliability challenges for modern devices characterized by a dense number of transistors targeted to operate safety-critical applications. These devices and the target operational environment (safety-critical) demand the development and adaptation of new test and reliability solutions.

More in detail, the trend observed in the scheme of Figure 1.2 suggests that modern integration technologies maintain almost a constant Infant Mortality (IM), but new devices are reaching the end-of-life state before the previous generations (the Component Fault Rate (CFR) period is shorter than in previous integration technologies). Thus, the extension of the operative life in modern technologies requires innovative in-field testing solutions beyond the traditional end-of-line testing, which is performed at the end of the production phase. End of production testing is not affordable anymore in complex devices and becomes a relevant issue in devices targeted for safety-critical applications and expected long-operative lives.

In the safety-critical domain, the reliability becomes imperative, so the compliance with standards of reliability and safety is a must. Most of the reliability constraints and safety development guidelines are included in industrial standards such as the ISO26262 and the IEC61508. These guidelines provide a set of requirements and needs that must be fulfilled in order to maintain optimal levels of functional safety in an application. Moreover, the complexity and the requirements in new applications, currently exploit the usage of (once called!) emerging technologies, such as Field Programmable Gate Arrays (FPGAs) and GPUs.

FPGA technologies are flexible and versatile. However, the development and configuration processes are difficult and complex, so have been historically confined to prototyping and a few critical applications. On the other hand, GPUs are less versatile than FPGAs, but more simple and flexible in programming. In fact, the programming capabilities, performance and internal features of GPUs have evolved to become one of the principal actors used in the development of safetycritical applications involving the implementation of algorithms for image and video processing and more recently AI.

More in detail, currently, GPUs are among the most complex embedded systems available in the market [15] and are now positioned as one of the most popular technologies employed in the development of several safety-critical applications, including automotive and autonomous machines in the industrial sectors. However, these technologies still have several issues in terms of reliability, which are detailed in detail in chapter 2.

Figure 1.2: A scheme of the trend of FIT rate of transistor integration technologies. Adapted from [16].

Taking into account the reliability issues, technological challenges and the high complexity in GPU devices presented above, the following questions motivate the work on the present thesis:

- What is the individual impact of faults on the internal modules of a GPU during its operative life, and how do the faults affect the execution of applications?

- How to adapt or develop in-field testing techniques based on a functional approach to detect fault affecting internal modules on GPUs?

- What are the rules to consider in the development of in-field testing solutions based on a functional approach for the GPU architecture?

- Is it possible to face reliability challenges by exploring and developing hybrid mitigation architectures for GPUs?, Which are the procedures, and what is the cost of these structures in the GPUs?

These questions served as a guide for the research activities in this work.

#### **1.2** Contribution

This dissertation focuses on three main pillars: i) The microarchitectural reliability evaluation focusing on particular modules of the GPU architecture, ii) The proposal of several functional strategies for online test on GPUs, and *iii*) the development of some new hardware structures for in-field fault mitigation in GPUs.

Concerning the microarchitectural reliability evaluation, individual modules of the GPU are evaluated and analyzed for the first time. One particular case in GPU architectures (with respect to the CPU ones) is the presence of task scheduler controllers. This work evaluated the fault sensitivity in the scheduler controller of a GPU. This module is one of the most critical units. Results allow us to support this claim about its fault sensitivity since a considerable percentage (about 25%) of transient faults are propagated, causing fault effects on several of the evaluated applications. Furthermore, other particular modules in the GPU were evaluated, such as the pipeline registers, which are those registers located between consecutive pipeline stages but hidden for the programmer. Other modules were also targeted as part of the sensitivity characterization, including the execution units and the stack memory. However, results also show that the fault sensitivity in these modules is lower than the scheduler controller (in the range of 1% to 15%).

On the other hand, the proposal of several strategies of in-field functional testing and mitigation structures mainly target faults arising during GPUs' operative life.

The proposed functional test methods are based on the Software-Based Self-Test (SBST)[17, 18] strategy that uses the computer programming capabilities of the GPU to design test programs at multiple abstraction levels when possible. It is worth noting that a similar approach based on SBST is frequently used for the in-field test of processor-based systems.

The programming capabilities in a GPU allow the design of SBST programs at a high level. However, restrictions and constraints are fully faced only using a combination of three levels of programming abstraction in the GPU (high-level, pseudo-assembly, and assembly levels).

Three different strategies are proposed for functional tests. The first approach employs a custom approach to combine the operational restrictions of the scheduler controller, in a GPU core, with fault primitives to define the possible test patterns for functional tests. Results show that the proposed solutions can test the module ( $\approx 100\%$ ), hence covering all faults on the targeted fault model.

The second approach of functional testing is based on the operation of multiple test programs to cover different groups of faults. This approach is focused on detect all faults that cannot be observed by the dynamic features of the GPUs, which remain static during the operation of the device. This approach is effective to test several modules inside the GPU and it was validated on the pipeline registers of the GPU core, that handles data and control path information. Furthermore, the results provide main advantages and limitations on developing test programs at high, medium and low abstraction levels.

Finally, the third method is based on a modular approach to develop test programs. This method aim at the exploration of different options in the composition of test programs. More in detail, this approach provides the mechanisms to develop test programs using basic blocks to represent the controllability and observability of faults in a module. Both features (controllability and observability) are combined with the operational parallel features of the GPUs, their main constraints, and a target fault model to develop the generic blocks that, once mapped, describe and implement the test routines for the target unit in the GPU. This approach was validated in several modules of a GPU core, providing adequate coverage of fault and contributing to explore different alternatives in the composition of test programs.

To the best of my knowledge, this is the first time that microarchitectural evaluations and fault injection campaigns on GPUs are performed to measure the effectiveness of functional test solutions based on SBST in GPUs.

The proposed test strategies and mitigation structures are intended to solve testing issues and reliability challenges present in such complex devices.

Other research activities focused on the proposal and evaluation of flexible solutions to mitigate faults in the GPU core. The proposed solutions are optimized combinations of hardware and software structures aiming at the fault detection, fault mitigation, or both in specific modules of the GPU core.

Three flexible solutions are developed and validated using the FlexGripPlus model. the first strategy targets the in-field detection of faults affecting the functional units in the GPU core. The results show that exploiting the high regularity of these functional units, the area overhead of the solution is less than 20%. The second strategy targets the mitigation of faults on the same modules of the GPU core. Finally, the third strategy explore a flexible architecture to provide in-field detection and mitigation of fault on the GPU. Results show a moderate hardware overhead for this solution (<10%). For the second and third strategies, the reliability of the harden module in the GPU reaches more than 40%.

The specific contributions of this research work are the following:

- A complete microarchitectural GPU model (FlexGripPlus), which is an opensource model described in VHDL and based on the G80 architecture of NVIDIA. FlexGripPlus was developed on top of the FlexGrip model [19] and intended to support the analysis of fault effects in GPU cores, perform validation and exploration of software-based techniques, and can be used to implement and evaluate hardware and hybrid mechanisms for fault testing and fault mitigation.

- Several functional test strategies based on SBST approaches targeting the detection of permanent faults in critical units of the GPU architecture. This work introduces for the first time quantitative results about the fault coverage on several modules.

- The proposal of flexible structures for the efficient detection and mitigation of faults, using combinations of hardware structures and software commands.

Several analyzes of reliability and overhead costs are presented for the proposed mechanisms and allows the evaluation of the most suitable trade-offs for implementation.

• The individual microarchitectural reliability evaluation of several data path and control path modules in a GPU device. The evaluation allows us to observe the sensitivity to faults of the targeted modules and to analyze the criticality effect of each module in the operation of a GPU core. Results also support the evaluation of complex applications, such as Convolutional Neural Networks (CNNs) in GPU platforms.

The reminder of this manuscript is structured as follows: Chapter 2 introduces the reliability features of GPUs employed in safety-critical applications and introduces the FlexGripPlus model as a tool to perform reliability research at microarchitectural level.

Chapter 3 describes the main finding of the reliability evaluations performed on several modules of the GPU and also provides the main observations of the reliability evaluation performed on CNN workloads. Then, Chapter 4 describes and reports the main findings of the proposed functional test techniques and solutions for GPU cores employing the SBST strategy.

Chapter 5 describes the flexible strategies developed to optimize the detection and mitigation of faults during the in-field operation of a GPU as combinations of hardware structures and software instructions. Finally, Chapter 6 provides the conclusion of the dissertation and the future works in the topic. The Appendix A describes the microarchitectural details of the FlexGripPlus model and also includes a list of the supported assembly instructions.

## Chapter 2

# GPUs in safety-critical applications

In the last decade, the GPUs have become the main workhorse in many highperformance and data-intensive applications, mostly present in the High Performance Computing (HPC), industrial, aerospace and automotive sectors [20]. The highly parallel structure of GPU devices combined with their highly flexible programming capabilities perfectly match the requirements of the applications in these sectors, so exploiting the main operational benefits of these products. These modern GPU devices are also known as General-Purpose Graphics Processing Units (GPGPUs).

The GPGPUs are the most flexible and programmable versions of a GPU and are exceptionally effective when used with parallel workloads. In fact, currently these technologies are also solutions in safety-critical applications. Devices including GPUs are considered as one of the most complex Systems-on-Chip (SoCs) ever designed and manufactured [15]. Nowadays, the versatility of GPUs has extended their usage into a large number of domains. Moreover, it continues being the principal device in multimedia and gaming applications.

A GPU oriented to safety-critical tasks can support the development of operations related with the implementation of sensor fusion and deep learning algorithms for AI, such as the NVIDIA Drive [21]. In fact, GPUs can be integrated in the so called Advanced Driver-Assistance Systems (ADAS) in the automotive domain [22] [23] [24]. In this field, the GPUs are integrated in systems devoted to perform several functions, such as Automatic Cruise Control, Pedestrian Recognition and Protection, Forward Collision Warning, Automatic Parking and Automatic Pilot. All these ADAS systems commonly use sensors as inputs, including cameras, radars or lidars, producing a sustained flow of data that must be processed and perform decisions in real-time [25]. GPUs are very well suited for these data-intensive processing tasks and are being increasingly used as feasible solutions by several manufacturers. Moreover, ADAS are also considered as an intermediate step towards semi-autonomous and self-driving cars [26].

Modern safety-critical GPU designs must include strategies to comply with industrial standards, such as the ISO26262 in the automotive domain. These standards require certain conditions to guarantee the correct execution, and a sufficient level of functional-safety and reliability of GPU devices at the end of the production and most importantly, during the operative life of the device. These regulations and standards are relevant for three main factors: i operational constraints of the safety-critical application, ii technology scaling in GPU devices, and iii the architectural features and complexity of GPUs.

Concerning the first point, the proposed fault-tolerance solutions must consider limitations of real-time operation, limited power budget and a high data-intensive processing behavior. Moreover, the possible solutions must evaluate performance limitations in case of in-field testing and mitigation. Finally, the availability of the modules and other resources should be considered during the operation of the safety-critical application.

On the other hand, technology scaling approaches increase performance and reduce size, while maintaining affordable production cost. However, these cuttingedge scales also increase the sensitivity to faults, so new devices might be prone to be affected by faults originated by internal and external factors, such as radiation. More in detail, faults can arise in a GPU after long term operation (caused by *aging* or *wear-out*) or by external factors, including radiation effects, electromagnetic interference and severe variations in temperature and power supply [5], [8], [27], [28], [29]. Thus, fault-tolerance solutions and reliability evaluations become relevant in the safety-critical domain and are important in GPUs devoted to those applications.

Finally, the architectural features and complexity of GPU devices require special fault-tolerance solutions, hence GPUs are dense and complex parallel devices and several singular modules might require special attention. Moreover, the development of ad-hoc solutions would need the combination of suitable strategies from processor-based architectures and new custom approaches of testing and mitigation. Nevertheless, it must be noted that initial designs of these special-purpose processors were developed as dedicated units to support the rendering process conceived for gaming and multimedia workloads, only. Thus, the design and development of GPUs targeted different objective. Moreover, most of these GPU designs included internal modules and functionalities that were not intended for extended verification or targeting industrial certifications. In these cases, the initial GPU devices were designed for a typical commercial operative life, supported by the fast moving trends in technology, and constant changes in the requirements for the gaming and multimedia industries. In fact, the first generations of these devices did not include any fault-tolerant or reliability strategy to manage fault detection or mitigation.

Another relevant feature of GPU devices is the elaborated programming method, which is based on high-level user-friendly programming environments. This method is optimized for performance and fast application development [30], but complicates

the development of testing and mitigation solutions. The high-level abstractions of commands, the compiler optimizations and the missing information about the Instructions Set Architecture (ISA) due to proprietary characteristics provoke issues for system and integration companies, which lack of microarchitectural details. In this scenario, modern GPU devices used for safety-critical applications still cannot guarantee the functionality and reliability for long-term operation, so new solutions for the on-line testing and fault mitigation must be developed.

In order to propose reliability and fault-tolerance strategies, a clear description of a GPU is required. For that purpose, this chapter provides the general microarchitectural organization of a GPU and the main relevant modules in its architecture. The microarchitectural organization provides a common terminology used across the following chapters, and also allows the identification of the main operative modules in a GPU. Then, a brief overview of reliability strategies and fault-tolerance methods for GPUs is provided, so allowing to identify actual methods and possible open questions. More in detail, several GPU models and tools are presented. These models are commonly used to explore, implement and validate strategies in reliability research. Finally, the introduction of a new microarchitectural GPU model **FlexGripPlus** is presented. Moreover, the description includes the list of detailed changes and improvements. This model is intended to support the development of fault testing and fault mitigation strategies. For the purpose of this work, the NVIDIA terminology is employed to describe the microarchitectural composition of a GPU.

Section 2.1 introduces the general architectural organization of a GPU and its main relevant internal modules. Then, Section 2.2 provides an introduction to the main reliability challenges in GPU devices and the available reliability solutions. Section 2.3 describes the tools for reliability research. Finally, Section 2.4 introduces and describes the **FlexGripPlus** GPU model as a tool to explore, evaluate and validate methodologies aiming to improve reliability in GPU devices.

#### 2.1 Architectural organization of a GPU

GPUs are specialized parallel processors, which work as special-purpose processors (Hardware Accelerators), in the processing of data-intensive and highly parallel applications. At the beginning (early 90's) these devices were designed and devoted to accelerate 2D/3D rendering and geometry processes for multimedia-based applications [31].

The initial generations of GPUs were modeled and based on the concept of a *Graphics or Rendering Pipeline* [32]. This concept is based on the idea of a single graphics core composed of a set of hardware cores, organized as a pipeline, able to process graphics. More in detail, the graphics core includes a set of fixed-function pipeline stages (Pixel Shading Pipelines), implementing the required operations

(Application, Geometry and Rasterization) to transform 3D coordinates into 2D pixels, which are commonly employed in multimedia operations. The coordination and management of the fixed-function cores is performed through a host using APIs, such as OpenGL or DirectX [33].

The next generations of GPUs started to provide programmable features into the fixed-function cores, so enabling their configuration and extending their capabilities. This programmable trend was exploited in successive generations of GPUs, so evolving from fixed-function pipelines into microcoded processors, configurable processors, programmable processors and finally reaching GPU architectures based on Scalable Parallel Processors [34], which provides the general purpose functionality.

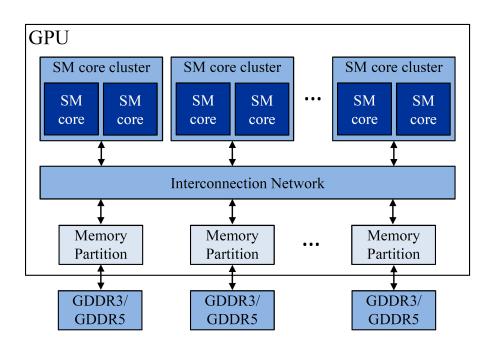

Modern GPU architectures exploit the best trade-off between state-of-the-art approaches in processors' design and traditional parallel architectures. More in detail, these new GPU architectures adopted more flexible processing cores allowing the general-purpose computation as GPGPUs. These General-Purpose GPUs are based on a multi-core design using massive parallel processors to perform highly parallel computations (see Figure 2.1). These fully programmable cores are known as Unified Programmable Shaders, Shader Cores, Single-Instructions Multiple-Thread (SIMT) cores [35] or Streaming Multiprocessor cores (SMs) [34].

In these new architectures, the traditional *Graphic Pipeline* is just a sotfware abstraction and is replaced by one or several SMs able to perform all operations, which were previously performed in the hardware cores of the former GPU generations. The SMs are mainly composed of several scalar cores, also known as Streaming/Scalar Processor cores (or SPs), and can operate sufficient parallel threads in an SM. More in detail, each SM processes the same instruction for several threads which are computed in the available SP cores in the SM.

The execution of a parallel task in a GPU is directly related to the microarchitectural organization and the configuration parameters defined in the task by the programmer. Firstly, the total scalable number of parts of the tasks (*blocks*) is defined. This parameter is internally managed by one or more general controllers in the GPU (*block scheduler*). The main purpose of the block scheduler is the submission and assignment of each block into the available SMs in the system. Then, each SM subdivides the block task into several sets of threads (also called *Warps* or *Wavefronts*) that are operated in parallel on the available SPs. The operation inside the SM follows the Single-Instruction Multiple-Data (SIMD) paradigm [36] or variations, such as the Single-Instruction Multiple-Thread (SIMT), when control-flow divergence among threads is allowed.

On the one hand, a multi-SM GPU architecture provides coarse-grain management of scalable data and task parallelism to execute multiple coarse-grain blocks of the same task, possibly in parallel. Furthermore, in modern GPU architectures, it is also possible the parallel execution of several blocks of two or more tasks. In this case, the blocks are associated to the available SMs, so the GPU follows the

Figure 2.1: A general scheme of a modern GPU architecture.

Multiple-Instruction Multiple-Data (MIMD) paradigm. This behavior is possible due to an extensive interconnection network linking the SMs in the systems and the memory resources in the GPU.

On the other hand, the available SPs in each SM provide fine-grained management of data and thread-level parallelism to execute hundreds or thousands of fine-grained operations (*threads*) in parallel.

It is worth noting that the same essential modules can be located in a GPU device among different manufacturers. These modules include controllers, processing elements or SMs, and the structures for accessing the memory resources. Some designs also include independent accelerators in parallel to the available SMs for specific purposes, such as texture modules, which are mainly devoted to rendering procedures in the multimedia domain. The composition of the processing elements and the dedicated accelerators directly depends on the device's operational targets and potential constraints in terms of power, area or performance.

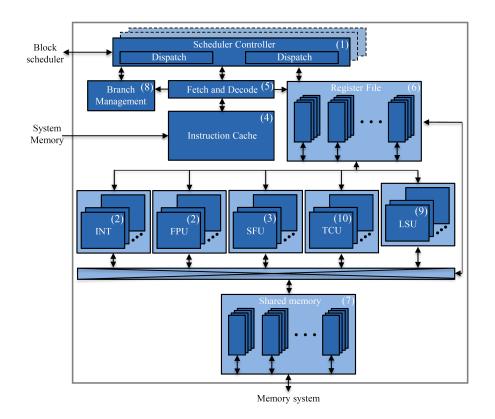

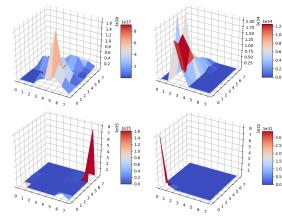

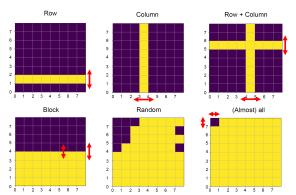

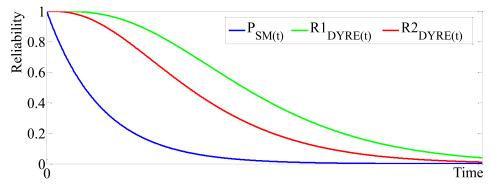

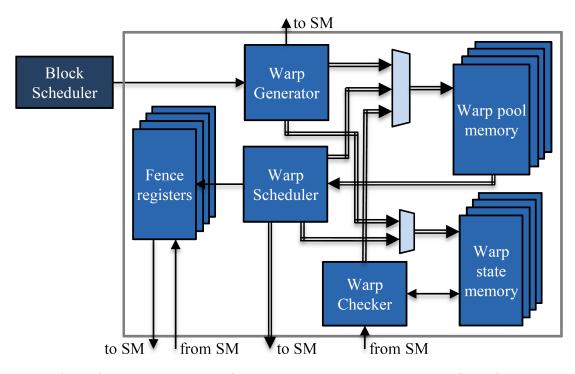

#### 2.1.1 The Streaming Multiprocessor