# POLITECNICO DI TORINO Repository ISTITUZIONALE

# Abstracting network elements from mask layout to network management: a case study

Original

Abstracting network elements from mask layout to network management: a case study / Ghillino, Enrico; Pasella, Pasquale; Stoffer, Remco; Richards, Dwight; Patel, Jigesh; Mena, Pablo; Scarmozzino, Rob; Bardella, Paolo; Virgillito, Emanuele; Pillori, Dario; Carena, Andrea; Curri, Vittorio. - ELETTRONICO. - (2020). (Intervento presentato al convegno SPIE OPTO 2020 tenutosi a San Francisco nel 1-6 February 2020) [10.1117/12.2546636].

Availability: This version is available at: 11583/2902532 since: 2021-05-25T09:46:55Z

Publisher: SPIE

Published DOI:10.1117/12.2546636

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

SPIE postprint/Author's Accepted Manuscript e/o postprint versione editoriale/Version of Record con

Copyright 2020 Society of PhotoOptical Instrumentation Engineers (SPIE). One print or electronic copy may be made for personal use only. Systematic reproduction and distribution, duplication of any material in this publication for a fee or for commercial purposes, and modification of the contents of the publication are prohibited.

(Article begins on next page)

# Abstracting network elements from mask layout to network management: a case study

Enrico Ghillino<sup>a</sup>, Pasquale Pasella<sup>b</sup>, Remco Stoffer<sup>c</sup>, Dwight Richards<sup>d</sup>, Jigesh Patel<sup>a</sup>, Pablo Mena<sup>a</sup>, Rob Scarmozzino<sup>a</sup>, Paolo Bardella<sup>b</sup>, Emanuele Virgillito<sup>b</sup>, Dario Pilori<sup>b</sup>, Andrea Carena<sup>b</sup>, and Vittorio Curri<sup>b</sup>

<sup>a</sup>Synopsys, Inc., 400 Executive Blvd Ste 101, Ossining, NY 10562, United States

<sup>b</sup>DET, Politecnico di Torino, Corso Duca degli Abruzzi 24, 10129 Torino, Italy

<sup>c</sup>Synopsys, Inc., Capitool 50, 7521 PL Enschede, the Netherlands

<sup>d</sup>College of Staten Island, CUNY, 2800 Victory Blvd, Staten Island, NY 10314, United States

## ABSTRACT

Using the vertical integration of the Synopsys environment, we analyze a  $2 \times 2$  integrated optical switch obtaining a layer-0 abstraction used to analyze the impact of the design options on transmission performances of a PM-64QAM 600G channel in multi-hop routing in meshed optical networks. The optical switch is designed targeting the Analog Photonics Process Design Kit. The QoT degradation depending on the design option and on the choice for the transmission technique is assessed, taking into account the number of traversed switches. In addition, different routing techniques for the integrated optical waveguides of the  $2 \times 2$  switches are investigated in terms of system performances.

The reported analysis is an example of comprehensive investigation carried out by abstracting the network elements starting from the component design up to the networking management. This approach is today mandatory to enable the maximum capacity in state-of-the art optical networks. To face this challenging problem, Synopsys proposes a vertically integrated software environment for the design of optical communication systems with photonic integrated circuits: it is the integration of OptSim© -optical communication system, OptSim Circuit -schematic-driven photonic circuit, OptoDesigner© -mask layout, and RSoft component design tools.

These tools have proven to be reliable aids to virtually designing and estimating the performance of optical transmission systems and photonic chips.

Keywords: PIC, Silicon Photonics, microrings, Synopsys, Benes, WDM

# 1. INTRODUCTION

The development of new photonic integrated circuits (PICs) as components for state-of-the art optical networks requires an abstraction of the network elements from the component design up to the networking management.

For this reason, Synopsys proposes a vertically integrated software environment for PIC and system design. It is based on the integration between four software of the Synopsys suite, namely OptSim, OptSim Circuit, OptoDesigner, and RSoft Design Suite. RSoft provides an environment for the design and simulation of single components, which can be used as building blocks in OptSim Circuit, a schematic-driven simulator of photonic circuits. The behaviour of such photonics circuits when inserted in a complete communication system can be simulated and studied with OptSim, assessing the performance of the specific PIC design. Finally, OptoDesigner can interact with RSoft and OptSim Circuit to generate mask layouts.<sup>1</sup>

In this work, we rely on such an integrated software environment to assess the impact on networking operations of design options for an optical switch in Silicon Photonics using Analog Photonics (AP) Process Design Kit (PDK) component library elements.<sup>2</sup>

Further author information:

E. Ghillino: E-mail: enrico.ghillino@synopsys.com

V. Curri: E-mail: vittorio.curri@polito.it

### 2. BENES SWITCH BASED ON DOUBLE-RING RESONATORS

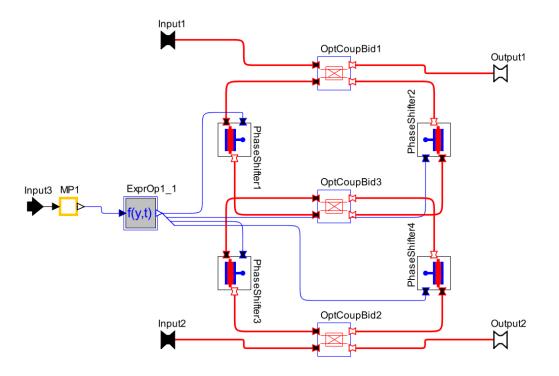

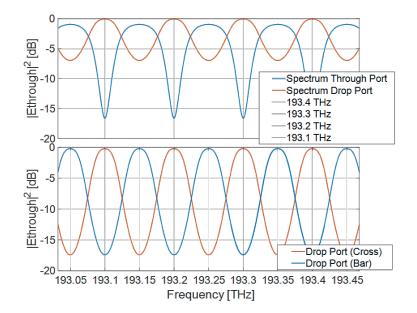

In this work we have studied a  $4 \times 4$  Benes switch structure based on six elementary blocks: each of them is a  $2 \times 2$  switch based on double-ring resonators that, whose OptSim circuit layout is shown in Fig. 1. This  $2 \times 2$  circuit has two nominal working condition: cross and bar.<sup>3,4</sup> First, we analyzed the input-output transfer functions of a single Double-Ring resonator (Fig. 2). The Silicon Photonics rings are 1.2 mm long, with k<sup>2</sup>=0.95; according to the selected PDK, 8.4 V are required to move from the cross to the bar configuration.

Figure 1. OptSim circuit for a single Double-Ring resonator.

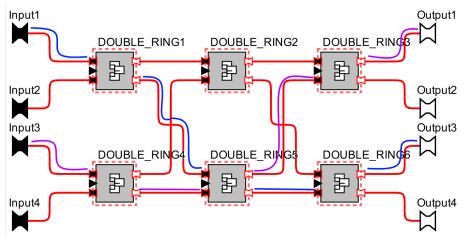

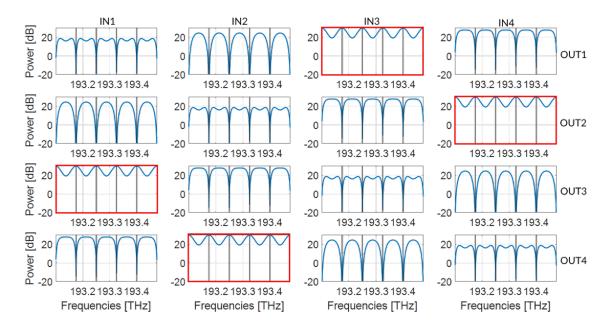

Following the analysis of the elementary building block, we moved to the simulation of the full Benes switch shown in Fig. 3 to fully characterize the routing behavior of this component for all the  $2^6=64$  driving voltage sets. Transfer functions for all 16 input-output combinations are shown in Fig. 4.

### **3. SYSTEM PERFORMANCE ANALYSIS**

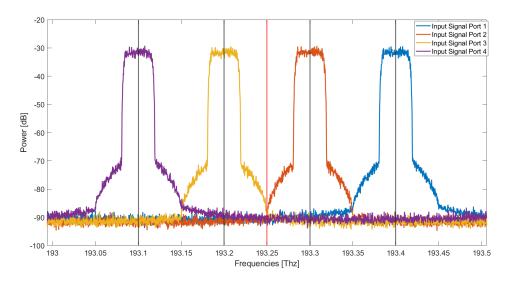

Simulations to determine the performance of a WDM systems routed using the switch were carried out using OptSim. The Benes switch model abstracted in the previous phase is now used to measure the impact of the proposed architecture. Time domain simulations of the whole chain, from transmitter to receiver, considers also all DSP needed at transmitter to spectrally shape the signal and at receiver to recover the information carried out (bits). Optical signals carrying PM-64QAM symbols are modulated at 32 Gbaud for a total net rate of 300 Gbps. At receiver side they require coherent detection: after analog-to-digital conversion at 2 samples-persymbol (64 GSa/s) a proper digital signal processing is needed to recover polarization, frequency and phase in order to decode information. Performances are evaluated through brute force error counting over  $2^{20}$  bits. To speed-up the analysis we considered an excerpt of a WDM system with 4 channels spaced at 100 GHz, as shown in Fig. 5.

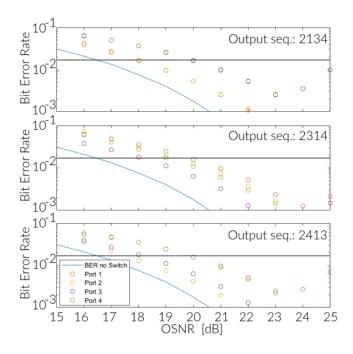

In a  $4 \times 4$  switch there are 24 possible routing states: all possible routing of the four wavelengths to any of the four outputs. On the other side, there are 64 switch states for the Benes structure, because of the 6

Figure 2. Simulated transfer functions of  $2 \times 2$  switch based on Double-Ring resonators.

Figure 3. OptSim circuit for the complete Benes switch. The paths of signals at Inputs 1 and 3 are shown for the case with all driving voltages set to 0 V.

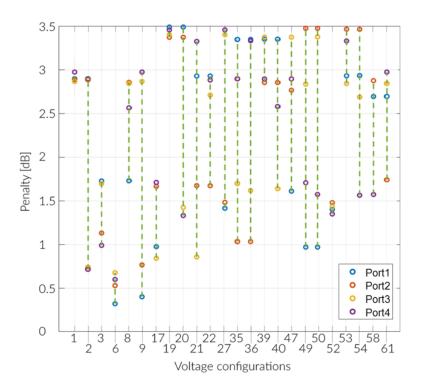

driving voltages, one for every elementary  $2 \times 2$  switch, that can be set to cross or bar condition: some of these states generate equivalent routing. We measured the OSNR penalty for all the cases to select the best between equivalent ones. In Fig. 6 we report some of the cases, labeled with the output sequence: "2134" means  $\lambda_2$  is on output 1,  $\lambda_1$  is on output 2,  $\lambda_3$  is on output 3 and  $\lambda_4$  is on output 4. Analyzing all possible combinations we derived the penalties for each of the four channels for the best 24 combinations. This final results are reported in Fig. 7: the OSNR penalty is plot for the 24 best cases (labeled as voltage configurations, i.e. a decimal number obtained converting the logical 6-bit word determining the cross-bar state of each  $2 \times 2$  switch). Colors refer to each of the four output port. The maximum OSNR penalty observed throughout all combinations is about 3.5 dB.

#### 4. CONCLUSIONS

We analyzed, using realistic PM-QAM optical signals, the characteristics of a  $4 \times 4$  Benes switch implemented in a Silicon Photonics platform, with numerical simulations performed using Synopsys OptSim and MATLAB. The

Figure 4. Transfer functions for all  $2^4 = 16$  input-output combinations in one of the  $2^6 = 64$  possible states of the Benes switch (all driving voltages set to 0 V, i.e. all rings in cross state. IN  $1 \rightarrow OUT$  3,  $2 \rightarrow 4$ ,  $3 \rightarrow 1$ ,  $4 \rightarrow 2$ )

Figure 5. Spectrum of the 4 WDM channels considered in the system performance analysis.

procedure can be extended to Benes with more input ports, and, taking advantage of the vertical integration of Synopsys suite, it could span from the system/network simulation and optimization (OptSim) to the mask creation (OptoDesigner) with a selected PDK. Results show that the Benes switch introduces a maximum penalty of 3.5 dB.

#### REFERENCES

Ghillino, E., Pasella, P., Staffer, R., Richards, D., Patel, J., Mena, P., Scarmozzino, R., Bardella, P., Virgillito, E., Pilori, D., Carena, A., and Curri, V., "Assessing the impact of design options for an optical switch in network routing impairments," in [2019 21st International Conference on Transparent Optical Networks (ICTON)], 1–4 (July 2019).

Figure 6. BER as a function of the OSNR for three exemplary combinations.

Figure 7. Comparison of OSNR penalty for the best 24 combinations.

- [2] Timurdogan, E., Su, Z., Shiue, R.-J., Poulton, C. V., Byrd, M. J., Xin, S., and Watts, M. R., "Apsuny process design kit (pdkv3.0): O, c and l band silicon photonics component libraries on 300mm wafers," in [Optical Fiber Communication Conference (OFC) 2019], Tu2A.1, Optical Society of America (2019).

- [3] Li, Q., Nikolova, D., Calhoun, D. M., Liu, Y., Ding, R., Baehr-Jones, T., Hochberg, M., and Bergman, K., "Single microring-based 2 × 2 silicon photonic crossbar switches," *IEEE Photonics Technology Letters* 27, 1981–1984 (Sep. 2015).

- [4] Papaioannou, S., Vyrsokinos, K., Tsilipakos, O., Pitilakis, A., Hassan, K., Weeber, J. ., Markey, L., Dereux, A., Bozhevolnyi, S. I., Miliou, A., Kriezis, E. E., and Pleros, N., "A 320 gb/s-throughput capable 2 × 2 silicon-plasmonic router architecture for optical interconnects," *Journal of Lightwave Technology* 29, 3185– 3195 (Nov 2011).