# Doctoral Dissertation Doctoral Program in Electrical, Electronics and Communications Engineering (XXXIII cycle)

# Signal processing techniques to improve interpolation and modulation in audio Digital to Analog Converters

Riccardo Peloso

**Supervisor**

Prof. Maurizio Martina

#### **Doctoral Examination Committee:**

Prof. Marina Bosi, Referee, Stanford University

Prof. Sergio Saponara, Referee, University of Pisa

Prof. Paolo Crovetti, Polytechnic University of Turin

Prof. Alberto Dassatti, School of Management and Engineering Vaud

Prof. Guido Masera, Polytechnic University of Turin

Politecnico di Torino March 11, 2021

| This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see <a href="https://www.creativecommons.org">www.creativecommons.org</a> . The text may be reproduced for non-commercial purposes, provided that credit is given to the original author. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that, the contents and organization of this dissertation constitute my own original work and do not compromise in any way the rights of third parties, including those relating to the security of personal data.                                                                                    |

Riccardo Peloso Turin, March 11, 2021

## Summary

Nowadays digital audio is ubiquitous, it can be easily acquired and reproduced with small and portable systems. The human hearing system evolved to an high accuracy in both time and frequency domains. To match this feature, a great effort is needed to design the device that converts the digital signal to its analog counterpart for physical fruition by a human listener. This system is called Digital to Analog Converter (DAC) and can be realized in many ways. Each implementation presents a slightly different sound signature and, for High Fidelity audio reproduction, this component must be able to accurately resolve the original analog signal. It can be difficult and expensive, in particular for people looking for the ultimate sound reproduction experience. Many stand-alone high-end DACs are available on the market but there is no clear winner, also due to the subjectivity of the end-user auditory tastes. It is thus important to be able to create a converter as sonically transparent as possible to let also the pickiest consumer enjoy the music content.

There are various issues associated with DAC designs. The main source of error is the analog part of the system, as the digital part exploits its intrinsic mathematical abstraction layer to reduce the error associated to its operations to the minimum. The analog part is prone to static and dynamic mismatch errors and susceptible to various noise contaminations. Fortunately, it is possible to employ clever Digital Signal Processing (DSP) algorithms to reduce the impact of mismatch and, to some extent, of noise on the analog stage. Modern Complementary Metal–Oxide–Semiconductor (CMOS) digital circuits can correct for many analog non-idealities with a relatively small resource utilization.

The most powerful idea in this field is to oversample the input signal and apply spectral shaping to error sources in order to force the error contribution to occupy a spectral zone

where it can be successfully filtered out without affecting the original input signal. The quantization error, the static mismatch error, or the dynamic Inter-Symbolic Interference (ISI) error can be all shaped resorting to appropriate algorithms. This paves the way for very compact and high performance integrated circuits realizations thanks to modern deep sub-micron CMOS technological processes.

Ultimate performance has not been reached yet, for both high-end stand-alone systems and mostly-digital integrated circuits. This thesis aims to propose some novel ways to reach the state of the art for modern audio DACs.

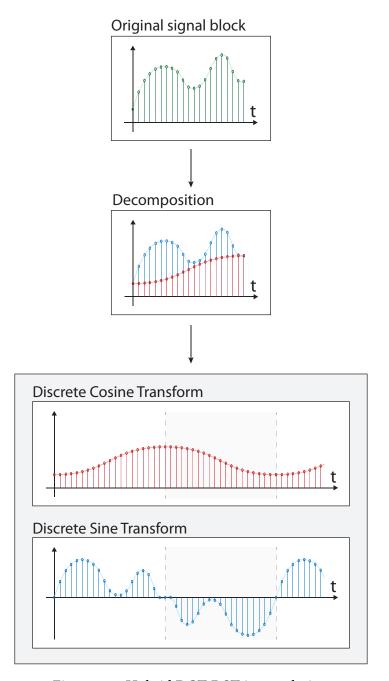

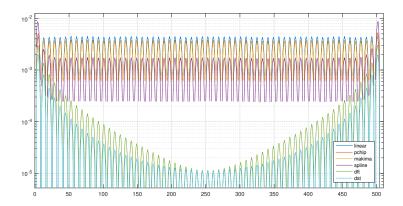

Oversampling usually requires an high quality interpolator to increase the sample rate. The first part of the novel contributions section revolves around two new ways to perform high quality interpolation. The first one optimizes FIR filtering by adding a recursion scheme, which is particularly efficient for linear phase filter kernels that can be represented sparsely in the frequency domain. The second method works directly in the frequency domain in a block-wise operation using a novel mix of Discrete Sine Transform (DST) and Discrete Cosine Transform (DCT) to reduce border artifacts.

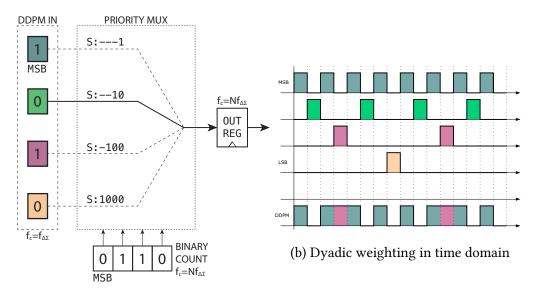

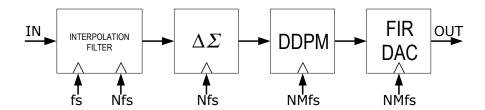

After that, some new modulation schemes are explored. The first one embeds the analog mismatch error shaping directly inside the main noise shaper. This extends the error correction scheme effectiveness while resorting to the classical Delta Sigma framework, which simplifies the system design. The second one works on the system stability, proposing a simple yet effective way to ensure a stable operation with a very little computational overhead. Next, a way to increase time-domain and frequency-domain signal fidelity is presented. The time-interleaving of two signals is used to compensate errors, leading to a simplified look-ahead scheme. Lastly, a mostly-digital low-power system is presented. It exploits the combination of a low-oversampling multi-level Delta Sigma modulator, Dyadic Digital Pulse Modulation (DDPM) and a shift-register-like DAC output to create a multi-level analog signal stemming from a two-level digital bitstream.

All the presented techniques are orthogonal in the solution space. They can potentially combined together to form an interesting DAC with a high quality interpolation scheme, intrinsic static mismatch error shaping, unconditional stability and high Signal to Noise Ratio (SNR).

## Acknowledgements

Through the development of this work I received a lot of help and support.

At first, I would like to thank Maurizio Martina, my supervisor in this journey, for his assistance and his mentoring on digital design together with Guido Masera. I need to acknowledge also Paolo Crovetti for his invaluable expertise in the mixed-signal field. I also thanks M. Bosi, S. Saponara and A.Dassatti for their kind support to finalize and discuss this work.

I thank my colleagues, in particular German S., Maurizio C., Kristjane C., Yuri A., Matteo S., Carmine P., Luca G., Simone A., Umberto G., Gianni C., Andrea M., Andrea C., Fabio R., Stefano B., Rossana T., Luciano P., Beatrice B., Walid W., Giulia S., Giovanna T., Fabrizio R., Marco V. and all the other members of the VLSI laboratory. You were like a second family, a reason for working happily everyday.

Next, I would not have reached this milestone without the help of my beloved parents and relatives, my girlfriend Zoe, my brother Stefano and Lucia. Their precious support, in particular during the last year, made me finish this work in time despite the lockdown difficulties.

I finally want to thank my friends for all the good times I had with them, in particular Mattia P., Nicoletta S., Francesca S., Nicola G., Louis A., Luca S., Andrea DP., Andrea M., Jessica B., Luca G., Xavier D., Cecilia C., Francesco L., Alessandro C., Paolo S., Greta M., Alberto M., Alice S., Michele P., Matteo C., Ali S., Elisa L., Noah U., Daniele B., Antonello P., Roberto C., Enrico V., Giuseppe D., Anna Chiara A., Luca B. and all the others I forgot to mention. Thanks for all.

## **Contents**

| Li | ist of Figures |         |                                 | IX   |

|----|----------------|---------|---------------------------------|------|

| 1  | Intr           | oductio | on                              | 1    |

|    | 1.1            | Anato   | omy of an audio DAC             | . 7  |

|    |                | 1.1.1   | Digital Back-End                | . 7  |

|    |                | 1.1.2   | Analog Front-End                | . 14 |

|    | 1.2            | Overs   | campling and error shaping      | . 15 |

| 2  | Re-            | sampli  | ng filters                      | 18   |

| 3  | Re-            | quantiz | zation modulators               | 24   |

|    | 3.1            | Two-l   | evels output                    | . 30 |

|    |                | 3.1.1   | Two-levels DAC simplified model | . 34 |

|    | 3.2            | Multi-  | -level output                   | . 36 |

|    | 3.3            | Direct  | t time-domain re-quantization   | . 40 |

|    |                | 3.3.1   | Pulse Width Modulation          | . 41 |

|    |                | 3.3.2   | Dyadic Digital Pulse Modulation | . 42 |

| 4  | Nov            | el Con  | tributions - Interpolation      | 45   |

|    | 4.1            | Sinus   | oidal Truncated IIR Filters     | . 46 |

|    |                | 4.1.1   | Bounded response TIIR           | . 47 |

|    |                | 4.1.2   | Basic constant TIIR             | . 48 |

|    |                | 4.1.3   | FIR approximation               | . 48 |

|    |                | 4.1.4   | Example                         | . 52 |

|    |                | 4.1.5   | Remarks                         | . 54 |

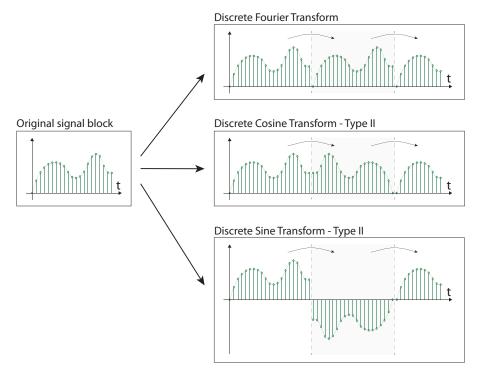

|   | 4.2 | Enhar  | nced DST-based Interpolation                         | 56 |

|---|-----|--------|------------------------------------------------------|----|

|   |     | 4.2.1  | Derivation                                           | 58 |

|   |     | 4.2.2  | Example                                              | 61 |

|   |     | 4.2.3  | Applications                                         | 63 |

|   |     | 4.2.4  | Remarks                                              | 65 |

| 5 | Nov | el Con | tributions - Modulation                              | 68 |

|   | 5.1 | Dynai  | mic element matching as parallel modulators          | 69 |

|   |     | 5.1.1  | DEM principle                                        | 69 |

|   |     | 5.1.2  | Parallel Delta Sigma Modulators can perform like DEM | 71 |

|   |     | 5.1.3  | Total error reduction                                | 72 |

|   |     | 5.1.4  | Extension to multiple branches                       | 73 |

|   |     | 5.1.5  | Calibration                                          | 74 |

|   |     | 5.1.6  | Example                                              | 75 |

|   |     | 5.1.7  | Remarks                                              | 76 |

|   | 5.2 | Increa | ased stability Delta-Sigma modulators                | 78 |

|   |     | 5.2.1  | Non-linear Delta-Sigma Modulator behavior            | 78 |

|   |     | 5.2.2  | Modified quantizer                                   | 79 |

|   |     | 5.2.3  | Modified Delta-Sigma Modulator                       | 80 |

|   |     | 5.2.4  | Example                                              | 81 |

|   |     | 5.2.5  | Remarks                                              | 82 |

|   | 5.3 | Time-  | interleaved streams                                  | 84 |

|   |     | 5.3.1  | Return-To-Zero coding                                | 84 |

|   |     | 5.3.2  | Stream interleaving                                  | 85 |

|   |     | 5.3.3  | Example                                              | 88 |

|   |     | 5.3.4  | Remarks                                              | 88 |

|   | 5.4 | DDPN   | M-based DAC                                          | 91 |

|   |     | 5.4.1  | DDPM review                                          | 91 |

|   |     | 5.4.2  | FIR-DAC                                              | 93 |

|   |     | 5.4.3  | Delta-Sigma modulator                                | 94 |

|   |     | 5.4.4  | Example                                              | 95 |

|   |     | 5.4.5  | Remarks                                              | 98 |

| 6  | Con                         | clusion                                        | 100 |

|----|-----------------------------|------------------------------------------------|-----|

| A  | Oth                         | er works                                       | 102 |

| В  | B Digital Serial Interfaces |                                                |     |

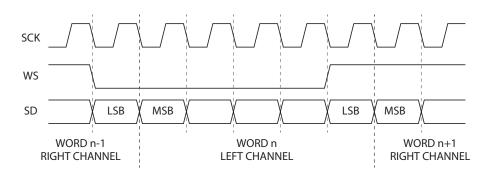

|    | B.1                         | Inter-IC Sound Interface (I2S)                 | 105 |

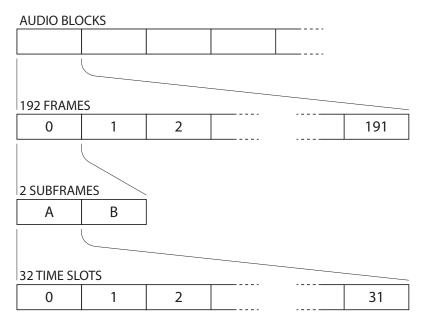

|    | B.2                         | Sony/Philips Digital Interface Format (S/PDIF) | 106 |

| Bi | Bibliography                |                                                |     |

## List of Figures

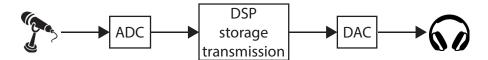

| 1.1  | Audio recording and reproduction chain          | 4  |

|------|-------------------------------------------------|----|

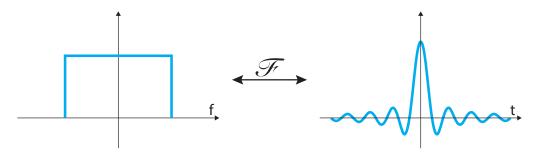

| 1.2  | Brick-wall filter                               |    |

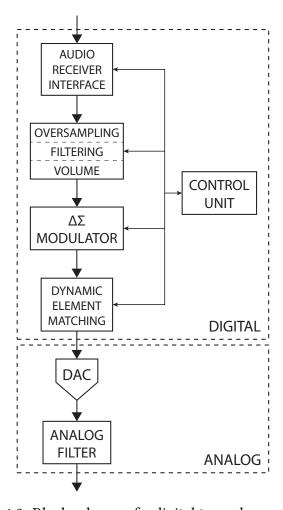

| 1.3  | Block scheme of a digital to analog converter   | 8  |

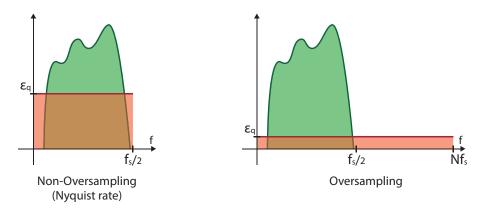

| 1.4  | Oversampling reduces error                      | 16 |

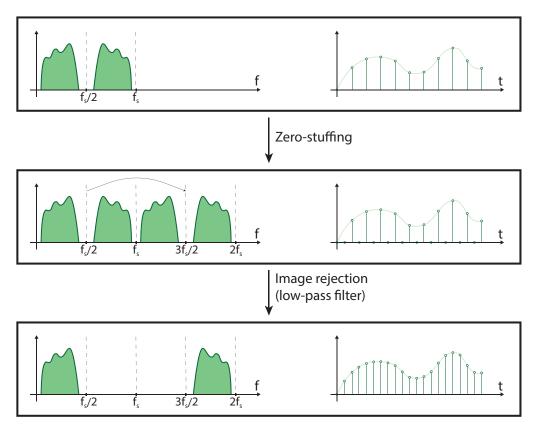

| 2.1  | Upsampling by zero-stuffing and filtering       | 19 |

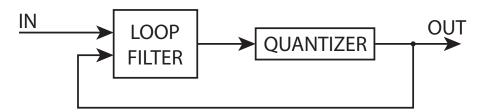

| 3.1  | Basic quantization error shaper                 | 25 |

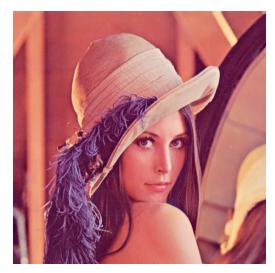

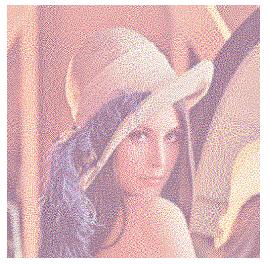

| 3.2  | Dither and noise shaping on images              | 26 |

| 3.3  | Common Delta Sigma modulator structures         | 30 |

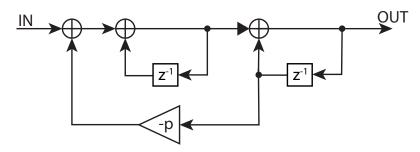

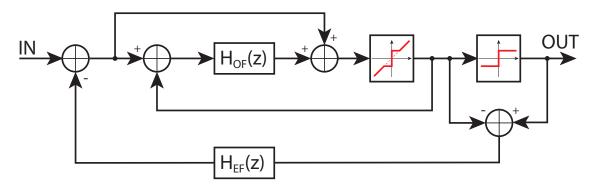

| 3.4  | Unity STF OF Delta Sigma modulator              | 32 |

| 3.5  | DAC error simplification for modeling           | 35 |

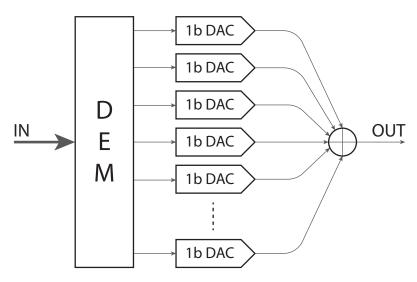

| 3.6  | Dynamic element matching                        | 37 |

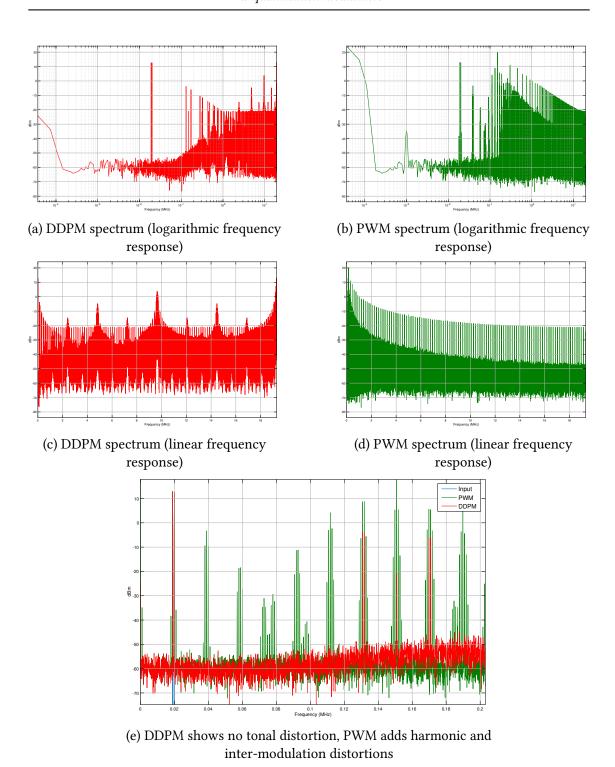

| 3.7  | PWM and DDPM spectra                            | 44 |

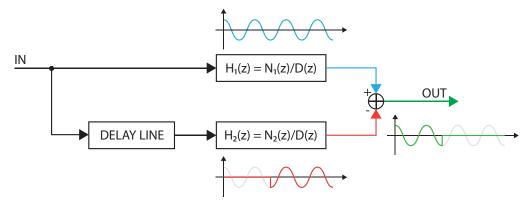

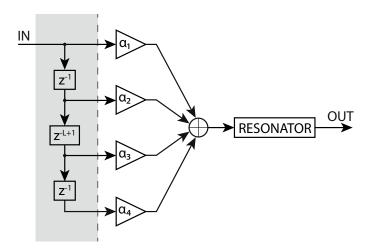

| 4.1  | Basic TIIR diagram                              | 46 |

| 4.2  | Digital resonator                               | 52 |

| 4.3  | Possible sinusoidal TIIR implementation         | 53 |

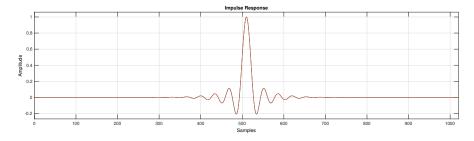

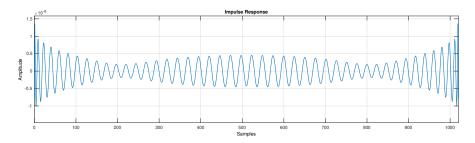

| 4.4  | Filter approximation impulse response           | 53 |

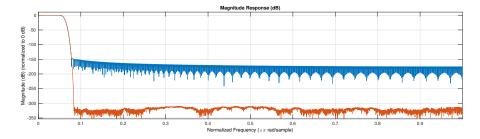

| 4.5  | Filter approximation error                      | 54 |

| 4.6  | Low-pass filter approximation                   | 54 |

| 4.7  | Upsampling by zero-stuffing and filtering       | 58 |

| 4.8  | Hybrid DCT-DST interpolation                    | 60 |

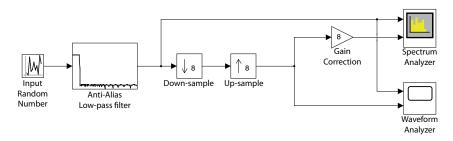

| 4.9  | Data generator for band-limited signal          | 62 |

| 4.10 | Frequency and time analysis of the input signal | 62 |

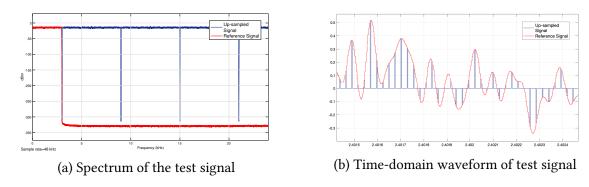

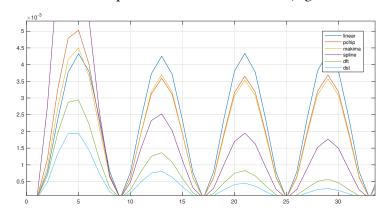

| 4.11 | RMSE comparison for different interpolation methods                 | 63  |

|------|---------------------------------------------------------------------|-----|

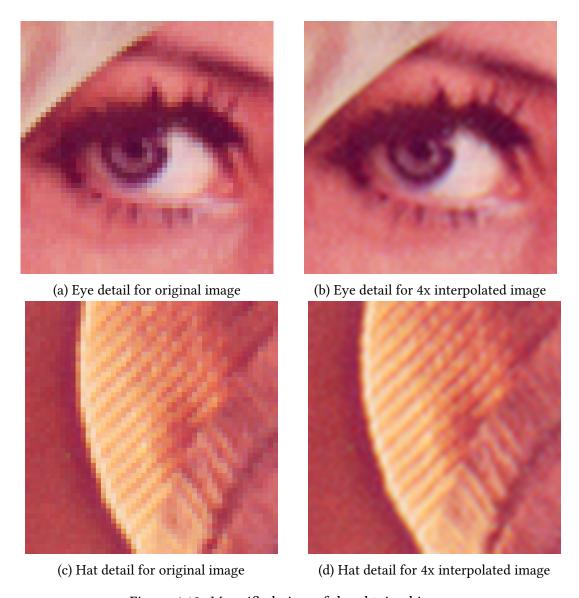

| 4.12 | Image interpolation with the proposed method                        | 65  |

| 4.13 | Magnified view of the obtained image                                | 66  |

| 5.1  | 1 bit DAC static error                                              | 70  |

| 5.2  | Multi-level DACs are composed by many two-levels contributions      | 71  |

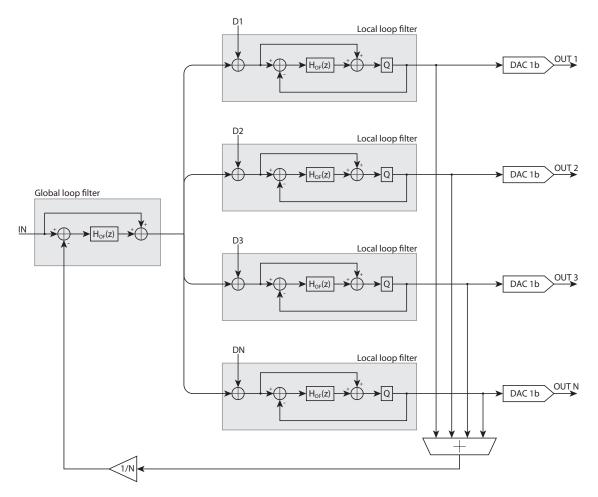

| 5.3  | Multi-level $\Delta\Sigma M$ with parallel branches                 | 74  |

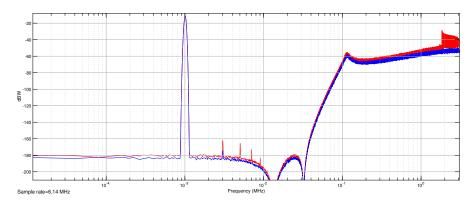

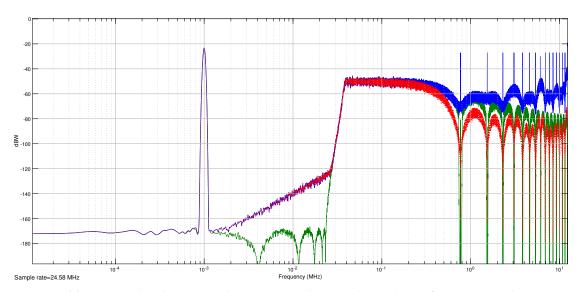

| 5.4  | Four-branches system output spectrum                                | 76  |

| 5.5  | Four-branches system output waveform                                | 76  |

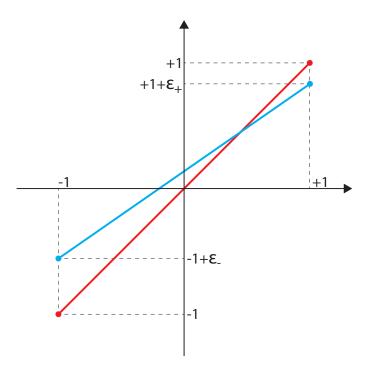

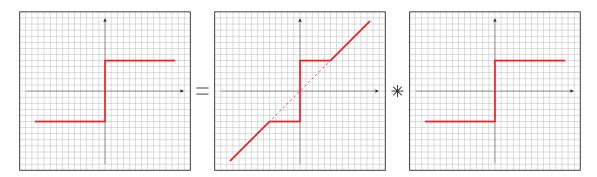

| 5.6  | A bounded quantizer can be split as an unbounded quantizer followed |     |

|      | by a saturation element                                             | 79  |

| 5.7  | Modified bounded quantizer                                          | 80  |

| 5.8  | Modified bounded quantizer                                          | 81  |

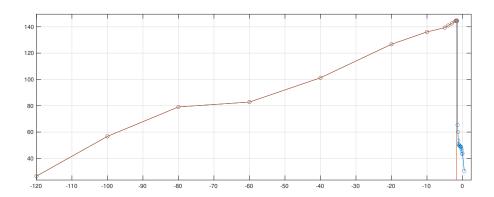

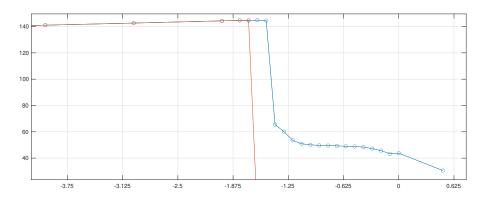

| 5.9  | SNR of proposed unconditionally stable modulator                    | 82  |

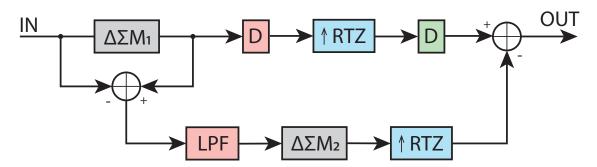

| 5.10 | Time-interleaved modulators block scheme                            | 87  |

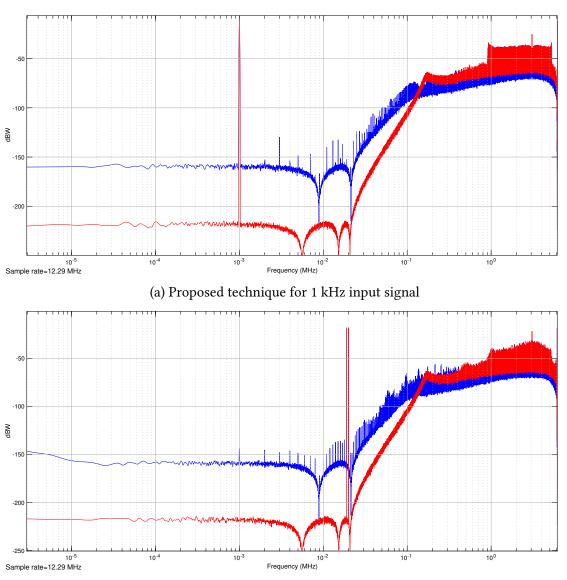

| 5.11 | Time-interleaved output spectra                                     | 89  |

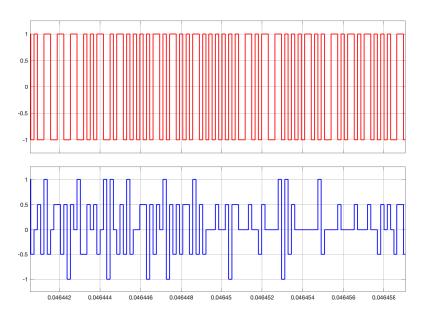

| 5.12 | DDPM structure                                                      | 92  |

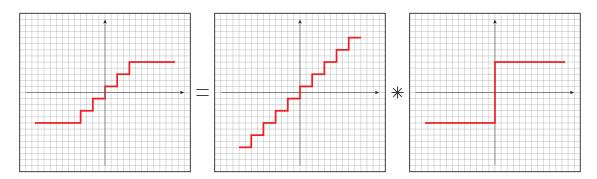

| 5.13 | Proposed system block scheme                                        | 95  |

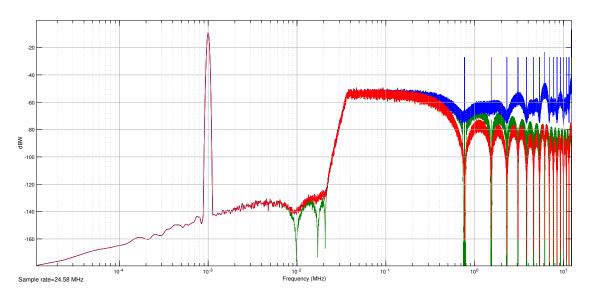

| 5.14 | DDPM with aggressive noise shaping                                  | 96  |

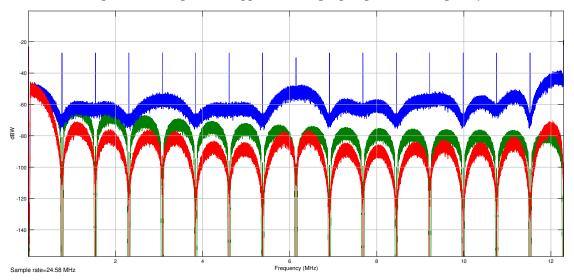

| 5.15 | DDPM with reduced noise shaping                                     | 97  |

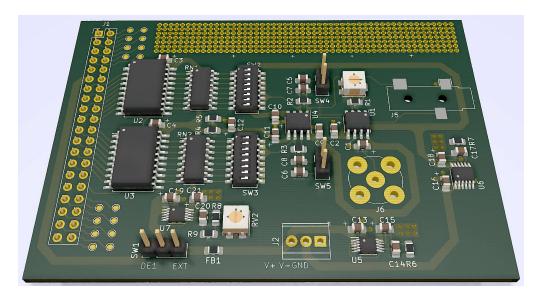

| 5.16 | Board for DDPM testing                                              | 98  |

| B.1  | I2S three-wire protocol                                             | 106 |

| B.2  | S/PDIF single wire protocol                                         | 107 |

## Acronyms

$\Delta \Sigma M$  Delta-Sigma Modulator

AAC Advanced Audio Coding

**ABC** Artificial Bee Colony

**ADC** Analog to Digital Converter

AI Artificial Intelligence

**AKM** Asahi Kasei Microdevices

**AoE** Audio over Ethernet

**AoIP** Audio over Internet Protocol

**AR** Asynchronous Reclock

**BBDFPWM** Base-Band Distortion-Free PWM

**BMC** Biphase Mark Code

CD-DA Compact Disk Digital Audio

CIC Cascade of Integrator-Comb

**CMOS** Complementary Metal–Oxide–Semiconductor

**CRC** Cyclic Redundancy Check

**CSE** Common Subexpression Elimination

**CU** Control Unit

**DAC** Digital to Analog Converter

DAT Digital Audio TapeDC Direct Current

**DCT** Discrete Cosine Transform

**DDPM** Dyadic Digital Pulse Modulation

**DEM** Dynamic Element Matching**DFT** Discrete Fourier Transform

DNN Deep Neural Network

DSD Direct Stream Digital

DSP Digital Signal Processing

DST Discrete Sine Transform

DWA Data Weighted Averaging

DXD Digital eXtreme Definition

**EF** Error-Feedback

**FFT** Fast Fourier Transform

**FIFO** First-In First-Out

**FIR** Finite Impulse Response

**FPGA** Field-Programmable Gate Array

**GA** Genetic Algorithm

**HDL** Hardware Description Language

**HDMI** High-Definition Multimedia Interface

**HiFi** High-Fidelity

**HRA** High Resolution Audio

**HS** Harmony Search

**I2S** Inter-IC Sound Interface

IC Integrated Circuit

IF Input-Feedforward

IIR Infinite Impulse ResponseILD Interaural Level DifferenceIMD Intermodulation Distortion

ISI Inter-Symbolic InterferenceITD Interaural Time Difference

KCL Kirchhoff Current LawKVL Kirchhoff Voltage Law

LSB Least Significant Bit

LTI Linear Time-Invariant

LUT Look-Up Table

MAF Moving Average FilterMASH Multistage Noise-shapingMCM Multiple Constant Elimination

MP Matching Pursuit

MP3 MPEG-1 Audio Layer III

MQA Master Quality Authenticated

MSB Most Significant Bit

**NLS** Non-linear Least Square

NOS Non-OverSampling

NRZ Non-Return-to-Zero

**NTF** Noise Transfer Function

OAM Overlap-Add Method

OF Output-Feedback

OOB Out-Of-Band

OSM Overlap-Save Method

OSR OverSampling Ratio

**PCB** Printed Circuit Board

**PCHIP** Piecewise Cubic Hermite Interpolating Polynomial

**PCM** Pulse-Code Modulation

**PGM** Pulse Group Modulation

PLL Phase-Locked Loop

**PSO** Particle Swarm Optimization**PSRR** Power Supply Rejection Ratio

**PWM** Pulse-Width Modulation

**RMSE** Root-Mean-Square Error

RTZ Return-to-Zero

**S/PDIF** Sony/Philips Digital Interface Format

**SA** Simulated Annealing

SDR Single Data Rate

SH Sample-And-Hold

SMASH Sturdy MASH

SMC Sliding Mode ControlSNR Signal to Noise RatioSoC System-on-Chip

**STF** Signal Transfer Function

**TOSLINK** Toshiba Link

**TPDF** Triangular Probability Density Function

**TWS** True Wireless Stereo

**USB** Universal Serial Bus

**VLSI** Very-Large Scale Integration

VQ Vector Quantizer

**ZOH** Zero-Order Hold

## Chapter 1

## Introduction

Digital audio reproduction may seem a trivial procedure for those unskilled in the art. This introductive chapter aims to get a better insight into what is required to build a true state-of-the-art, high-fidelity Digital to Analog Converter (DAC) for audio applications. At a first sight, the main problems that arise when developing an audio DAC are related to the analog front-end. A plethora of issues haunt this very delicate part of the system. Through the years, researchers spent a great amount of time and resources to exploit very clever Digital Signal Processing (DSP) techniques in the digital domain to shift the analog errors contribution in the ultrasonic range of the spectrum, the Out-Of-Band (OOB) zone, in a process called error shaping.

High Fidelity audio is a journey towards perfection. Many people spend thousands of dollars in the pursuit of the ultimate reproduction system. This thesis proposes some novel ways to reach the state-of-the-art for audio reproduction, even in presence of analog sources of error.

At first a brief overview of the human hearing system, the audio signal and its digital version will be analyzed in this introductory chapter. Then, after presenting the structure of a modern Digital to Analog Converter (DAC), the features of some elements of the digital section will be discussed individually in Chapters 2 and 3. Once the underlying limitations and drawbacks of existing methods have been explained, the rest of the work will propose some novel contributions. The first part, Chapter 4, is focused on efficient and high-quality interpolation methods. The first contribution, Section 4.1, is about a novel way to implement sliding window FIR filters as the sum of truncated IIR filters

with a sinusoidal impulse response. The second contribution, Section 4.2, deals with a novel trigonometric interpolation with reduced transform-related artifacts.

The second part, Chapter 5, works on some ideas presented in Chapter 3 that have not been analyzed yet in literature. In particular, Section 5.1 shows a way to implement a multi-level signal as the sum of 1 bit contributions by better exploiting noise compensation between branches. Then, in Section 5.2, a simple way to guarantee 1 bit quantizer unconditional stability is presented by separating the quantization and the saturation non-linearities. Next, Section 5.3 exploits time-interleaved  $\Delta\Sigma M$  streams to increase output signal quality. Eventually, Section 5.4 enhance the DDPM technique with a noise shaper and an output FIR DAC.

#### The human hearing system

The human auditory system is a complex organ made by the physical transducers, the ears, and a powerful signal processing system, the brain [1, 2]. The ear is composed by three main parts, the outer ear, the middle ear and the inner ear. The outer ear collects the external medium pressure variation and it is tuned to approximately 4 kHz. The middle ear, composed by small bones called the hammer, the anvil and the stirrup, converts the large eardrum displacement to a small but high-force displacement for the cochlea. This mechanism also mechanically matches the impedances of the air and the cochlear fluid to minimize the energy loss. The cochlea is a spiral-shaped tunnel filled with a liquid that oscillates following the eardrum input. The vibrations excite the auditory nerves at different frequencies along the length of the cochlea. The high frequencies are detected at its beginning part, while the far neurons are excited by lower frequencies. This is often called a "frequency-space" transformation. A young human listener at its peak auditory performance is able to hear in the 20 Hz to 20 kHz range. Outside this range, the hearing system filters out the excess vibrational energy like a steep high order filter. This process is nonlinear, so the loudest sounds are less amplified than the quietest ones. Also, due to a non-uniform frequency equalization, different frequencies are perceived as equally loud even if of different physical intensity. The total resolvable audio dynamic range in humans is about 130 dB, a very wide range.

Most of the hearing magic is carried inside the brain [3]. The incoming signal is processed to reconstruct a stereo mapping resorting to complex neural networks. They exploit the difference in time of arrival between the ears, the Interaural Time Difference (ITD), and the difference of sound intensity, the Interaural Level Difference (ILD) [4]. This makes possible to detect the origin of a sound and differentiate sound sources thanks to sound transients, sudden variations in sound intensity and non-stationary waveforms. Due to the frequency-based nature of the ear, most of the transient detection is carried out by the brain. Human hearing is particularly sensible to transient timing for evolutionary purposes and this affects also music enjoyment. Using high-quality audio systems, the listener is able to detect and resolve the sound stage instruments disposition with a great accuracy.

The field that studies the relationship between the human hearing sensations and the external auditory inputs is called psychoacoustics. This science lead to many interesting discoveries, like the equal-loudness non-linear curves, the hearing threshold in quiet and the important masking phenomena that are extensively used for music compression [2].

Music is the art form that exploits sound as the medium. It is generated predominantly by musical instruments, physical or digitally synthesized, and human voice, but it is possible to integrate almost any sound source in this category. Each listener has a different subjective musical taste, which complicates the definition of what can be considered music. In this thesis the focus will be on the audio range, nominally a stereo signal that occupies the 20 Hz to 20 kHz band with about 130 dB of dynamic range.

#### The audio signal

Fortunately, it is possible to capture the physical sound using transducers, called microphones, to convert the physical vibrations to an electric signal. This analog signal can be processed in the analog domain or digitized with an Analog to Digital Converter (ADC) to build a more useful representation. In the digital domain, it is easy to have exact and repeatable signal processing without worrying about noise and component tolerances. At the same time, digital signal can also be stored and transmitted with ease.

Figure 1.1: Simplified view of a typical audio recording and reproduction chain, from the source to the listener

Depending on the previous equipment accuracy, the digitized signal can carry an High-Fidelity (HiFi) replica of the sound captured by the microphone. Regarding music, many sound sources can be processed separately and mixed together by an audio engineer. Once a digital track is consolidated, it needs to be converted back to the analog domain, using a DAC, where it can be amplified and reproduced on the apposite transducer, the loudspeaker.

Figure 1.1 shows a schematic view of the recording and reproduction chain.

#### Digital audio

The Whittaker–Nyquist–Shannon sampling theorem [5] clearly states that the loss-less reconstruction of a band-limited time-continuous signal requires a sampling frequency greater than two times the signal bandwidth. For audio, taking into account the upper hearing frequency of 20 kHz, this translates to about 40 kHz. This is the minimum sampling frequency that can accomodate the audible audio spectrum. In the real world, where brick-wall anti-imaging filters can only be approximated, it is safer to extend this frequency to at least 44.1 kHz, the Compact Disk Digital Audio (CD-DA) sampling frequency [6], or 48 kHz, the Digital Audio Tape (DAT) one [7].

These two sampling frequencies are the baseline for all the digital audio formats, with a word-width of 16 or 24 bits. Starting from this point, many digital audio formats have been proposed, with varying sampling frequencies and bit-width. They usually feature sampling frequencies that are integer power-of-two multiples of these two basic ones to reduce filter requirements and enable advanced signal processing algorithms.

As explained before, humans rely on the transient timing accuracy between the ears

Figure 1.2: The ideal brick-wall filter requires a sinc(x) time-domain realization

to correctly reconstruct the sound stage. Using the minimum Nyquist sampling frequency, the transient timing is hidden between samples, even if mathematically all the information is still contained in the signal. The original time-continuous signal would theoretically be reconstructed by an ideal brick-wall linear-phase low-pass filter, but unfortunately it is not possible to practically realize it. This filter shows an infinite time-domain impulse response as  $\operatorname{sinc}(x) = \frac{\sin(x)}{x}$  (the *Sine Cardinal* function), shown in Figure 1.2. It can only be approximated over a finite duration, for example by the Tukey-windowed low-pass filter [8], which retains the *sinc* function in the middle part of its kernel and then decays to zero to avoid filtering artifacts near the borders. Higher sampling rates would help relaxing this filter constraints, leading to a less complex system and a more life-like sound. In fact, by measuring the sound emitted by various instruments, it is possible to notice that their spectrum occupy a broader frequency range than the human maximum perceived frequency [9]. This is due to transients, as the narrower they are in the time domain, the wider will be their frequency response. The effective psycho-acousic response on human listeners is still under debat, yet a higher reconstruction accuracy in time domain can not pose any harm on the reproduction chain. It is then safe to state that already a mild oversampling (for example 96 or 192 kHz) helps reducing the requirements of the various filtering stage without adding too much complexity. These operational frequencies are still very low for modern digital circuits, and they effectively enhance the time-domain signal reconstruction accuracy.

In contrast, using even higher sampling rate, it is possible to exploit the available excess spectral space to reduce the output signal bit resolution. This will be better explained in the rest of the thesis, as this is extensively used in audio ADCs and DACs.

The digital audio signal can be stored and transmitted either uncompressed or compressed. The uncompressed version consists on raw audio signal coded as uniformly sampled Pulse-Code Modulation (PCM), with linearly uniform quantization levels [10, 11]. This digital signal can be easily processed with linear algebra through the digital part of the signal chain. It depends on two parameters, the sampling rate and the bit depth. The basic versions are the CD (16 bit at 44.1 kHz) and the DAT (16 bit at 48 kHz), but also others flavors are available and encouraged, as explained before. These signals forms the High Resolution Audio (HRA) family, with their main representative being the Digital eXtreme Definition (DXD) (24 bit at 352.8 kHz or 384 kHz [12]) and the Direct Stream Digital (DSD) (1 bit at 2.822 MHz [13, 14]). Due to some restrictions of the original DSD [15], other DSD-related formats have been proposed which either can increase the sampling rate (double-rate, quad-rate and octuple-rate DSD) and the bit depth (DSD wide [16], at 8 bit). There are still some debates about the best format, both for psycho-acoustic and implementative points of view, in particular about the required total bandwidth and the filtering complexity [17, 18].

Digital audio can be compressed, but it must be de-compressed before entering the DAC as a raw audio signal. Compression can be either lossless or lossy. Complex encoding schemes can dramatically shrink the file size at the expense of signal quality. The two most known lossy formats are the MPEG-1 Audio Layer III (MP3) and Advanced Audio Coding (AAC) [19–21]. They exploits perceptual models to decide which parts of the original raw signal can be safely discarded while retaining an acceptable output quality for a human listener. The main psychoacoustic feature employed is the frequency-domain masking, but they are also able to render transients with high fidelity using optimized adaptive time-domain overlapped window functions for filtering. Other techniques like non-uniform quantization, error shaping and the Huffman coding algorithm further enhance quality at high compression ratios.

There are many other lossy compression schemes available, but one of them seems more promising for high fidelity, the Master Quality Authenticated (MQA) technology [22]. This encoding scheme smartly compresses part of the information that usually would resides in the ultrasonic range of a HRA signal in the intrinsic noise of a 24 bit low-sampling-frequency signal (44.1 kHz or 48 kHz). Due to ADCs and hearing limitations, in digital audio only about 21 bits of the signal carry effective information, the rest of

the word consists on noise. In MQA, these lower bits are filled by information that can be decoded by apposite MQA-enabled players, reconstructing the high-resolution signal. The same file can be played on a legacy player that will interpret it as a classic raw uncompressed audio signal, without resolving the additional information. There has been much debate on the effectiveness of this closed format, both for the acoustic point of view and pricing. It is important to stress out that the added high-frequency content has just a subtle effect on the hearing system but it is nevertheless useful to reduce the interpolation filter requirements.

## 1.1 Anatomy of an audio DAC

As the name states, a Digital to Analog Converter is composed of two main parts, the digital back-end, and the analog front-end, as shown in Figure 1.3. Analog circuitry is noise-sensitive, so it has to be electrically decoupled from the noisy digital section and usually requires a dedicated low-noise power supply. Often, externally to the DAC, a precision crystal oscillator is present. It is needed to clock both the digital and the analog parts. Usually, an internal Phase-Locked Loop (PLL) is used to derive different clock domains to accommodate the various digital stages, but the final analog stage demands a clock with high-accuracy, low-noise, and low-jitter to correctly work as desired. This section describes the most common building blocks in a modern audio DAC system.

#### 1.1.1 Digital Back-End

The digital back-end is the core of the system. Here the digital audio signal is processed with numeric methods to preemptively compensate for the analog stage errors. The natural way to analyze the DAC structure is to follow the input signal propagation to focus on each block.

Figure 1.3: Block scheme of a digital to analog converter

#### **Control unit**

The whole digital part is coordinated by a Control Unit (CU). The CU usually also acts as an interface between the DAC and the user, receiving commands, performing actions, and returning status information. It can be built in various ways depending on the required features, like programmability, size and speed.

#### Audio receiver interface

The audio digital serial interface receives the uncompressed digital audio signal. The two main used consumer interfaces are the Inter-IC Sound Interface (I2S), a synchronous

interface with a dedicated clock wire [23], and the Sony/Philips Digital Interface Format (S/PDIF), which embeds the clock in the signal thanks to a Biphase Mark Code (BMC) technique [24]. The latter requires a lower amount of wires, is standardized and is more difficult to handle as it sends also metadata and various information in the serial stream, codified in 32 bit wide frames. These two important interfaces are better described in Appendix B. Apart from these two protocols, it is possible to transmit uncompressed audio also over Universal Serial Bus (USB) or using Audio over Ethernet (AoE) or Audio over Internet Protocol (AoIP) [25] by suitably coding the audio stream in the payload of the selected interface. S/PDIF has also a professional version called AES/EBU, developed by the Audio Engineering Society (AES) and the European Broadcasting Union (EBU). Other multimedia interfaces can be used for uncompressed audio, like High-Definition Multimedia Interface (HDMI), but they are less used in consumer audio-only equipment.

#### Preprocessing

After the stream is successfully received and decoded, it is internally converted to a parallel PCM signal. The parallel stream may enter a First-In First-Out (FIFO) memory that acts as a synchronization buffer to decouple the DAC from the signal source. DSD stream can be used instead of PCM, as DSD is just a low bit-width, high-frequency PCM with an aggressive noise-shaping applied. DSD can be reproduced "as is" on a suitable reproduction system or re-converted to standard PCM for easier handling and processing. For example, it is not possible to digitally modify the amplitude of a DSD-codified signal, only an analog attenuation is possible.

Next, some first basic digital processing is done exploiting the fact that usually this is the section of the DAC that has the lowest sampling frequency and the highest bit depth. Usually, digital volume control, soft muting and basic filtering are performed at this stage. The digital volume control simply linearly modifies the amplitude level of the signal, often resorting to a soft time-based function that avoids abrupt level changes. The main drawback of this operation is that it degrades the SNR because the final noise floor remains more or less constant while the signal amplitude is here reduced. The soft mute has the same working principle, by zeroing the signal amplitude. Basic filtering can then be needed to pre-compensate issues that will arise in the next stages and

to apply specific DSP functions, like pre-emphasis, equalization, harmonic distortion pre-compensation or cross-over filtering. Ideally, from the digital signal point of view, the best place to apply these functions would be just before the modulator, but the higher sampling frequency requires more computations and so usually this is performed in this part of the DAC, just before the re-sampling filter.

#### Interpolation

The next part of a modern DAC is the re-sammpling filter (also called the interpolation filter), that increases the sampling rate to a frequency that can be used to exploit noise-shaping and, thus, reduce the analog requirements. This process, called oversampling, is a critical part of the reproduction chain and will be better discussed in Chapter 2. Its complexity is often neglected by manufacturers because a high time-resolution interpolation requires long and complex linear-phase filters. HRA streams have less stringent requirements, as the high-quality filtering should have been carried off-line by the recording studio. Multiple designs are based on this assumption, yet it is not always ensured. Often, the minimum length filter that achieves the desired interpolation is used to reduce computations, as traditionally the frequency response is considered more important than the time response. As stated before, the *sinc* function would be the optimum filter to reconstruct the signal in the time domain but, due to its infinite-support nature, it has to be approximated for a practical implementation. Usually, a multistage filter is employed: the required sampling frequency is reached in more than one step by using a cascade of simpler filters.

#### **Delta-Sigma Modulator**

Once the signal is interpolated to the required frequency, it can be processed by the digital  $\Delta\Sigma$  modulator, which will be better discussed in Chapter 3. The modulator has the important duty of lowering the digital word width by forcing the produced quantization error to occupy mainly the OOB zone, freeing the audio baseband. This stage is the core of modern audio DACs as its output is what makes it possible to use only a small number of analog levels, reducing the analog stage requirements. With

today's Complementary Metal-Oxide-Semiconductor (CMOS) transistor technology, high-frequency digital circuits with a very high integration density can be easily engineered and built. Complex and precise digital circuits can be integrated into a small silicon area. The implemented functions would be unrealizable in the analog domain, due to a lack of accuracy and noise contamination.

Most of the time  $\Delta\Sigma$  modulators are realized as closed-loop feedback systems, more rarely as look-ahead structures. The former ones are straightforwardly implemented like digital filters. The latter ones, instead, require more computations as they have to look in the possible future horizon what will be the stream of output words that will lead to the lowest error in the base-band, while avoiding instability. The number of computations grows exponentially with respect to the look-ahead time window so it is difficult to fully exploit this technique in real-time circuits. Look-ahead ensures that the obtained signal is the best one achievable in that time window. It is usually performed off-line by software implementations, often approximated by relying on different heuristics. Some DSD tracks are encoded resorting to look-ahead modulation [26].

A common problem that afflicts  $\Delta\Sigma$  modulators is the loop feedback stability because a non-linear saturation operator is part of the loop. Most of the high-SNR modulators are only marginally stable, which means that a control system is needed to avoid catastrophic system instabilities.

Currently, there are no analytical ways to predict a high-order delta-sigma modulator stability and so the designer has to resort to extensive simulations to ensure the correct behavior of the modulator. Even if it seems stable after simulations, it is important to still add instability detection and compensation techniques to be sure of its behavior on the field. This negatively affects the SNR, as the recirculating error is tamed by reducing the noise shaper capability to a lower performance one with increased stability. Due to the nature of audio signals, which present low average amplitudes and often a spread-spectrum behavior, the instabilities should happen rarely. The best-case scenario is a system free of instabilities, because the stability compensation techniques tend to ruin the output signal quality by changing dynamically the shape of the modulator noise. This compensation, in turns, creates unwanted intermodulation artifacts in the signal band. Additionally, compensation is difficult to ensure without limiting the maximum amplitude of the modulator input signal, either by attenuation or by signal clipping.

This is the main reason why DSD signals have a -6 dB maximum allowed amplitude under the equivalent theoretical PCM full-scale amplitude.

The digital in-band noise floor, after modulation, can reach a very low value. It is possible to design noise shapers whose limitation is the numeric precision of the digital loop filter. On the contrary, the noise floor after the analog stage, in particular due to mismatch errors and thermal effects, can get as low as -150 dB in very accurate DACs and this can be difficult to measure. These measurements require very accurate and expensive audio analyzers, usually found only in specialized laboratories. A modulator with a total in-band digital error lower than the one achievable by the physical analog stage can be said to perform well enough to be considered sonically transparent for the high-end audio sector.

As stated before, the time-domain response of the modulator is as important as the frequency-domain one in order to reproduce the transient as accurately as possible. A problem with feedback modulators like  $\Delta\Sigma$  ones is that the error is corrected in a sample-by sample basis. Look-ahead modulators, on the contrary, predict the path that minimize the error, effectively starting to compensate its effect as soon as possible. It would thus be important to employ some look-ahead techniques for the best time-domain signal reconstruction but this is very difficult to achieve in real-time.

Another issue in the modulation part of a modern DAC is the correlation between the input signal and the quantization noise. The quantizer is often modeled as an additive source of Gaussian noise to exploit linear techniques, even if often turns to be a poor assumption. In particular, this is not a good model for a two-levels quantizer [15]. A random noise can be applied before the quantizer in a process called dithering [27] to partially de-correlate the quantization error from the input signal. If this random source is inserted in the noise shaper loop just before the quantizer, its contribution will be shaped alongside the quantization noise. The problem with 1 bit quantizers is that the required level of dither to de-correlate the quantization error from the input signal would overload the quantizer, leading to a dangerous instability, while severely limiting the input signal dynamic extension. Only partial dithering can be applied, which means that for 1 bit modulators it is not possible to completely de-correlate the quantization noise from the signal with linear additive dither. It is thus not possible to completely remove unwanted signal-related audible artifacts (in particular harmonic distortion

and spurious tones). This issue can be solved by using multi-level modulators, but unfortunately the two-levels modulator is the only one inherently linear in the analog domain implementation.

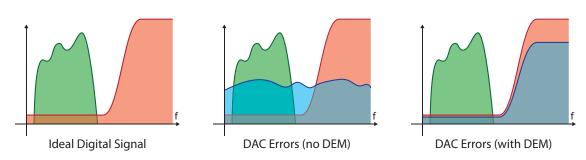

#### Dynamic element matching

If a multi-level modulator has been used in the previous stage, an additional stage is needed to reduce the multi-level to a sum of (possibly weighted) 1 bit contributions to make the signal transfer function as linear as possible. This part of the system is called scrambler or Dynamic Element Matching (DEM) block [28–36]. DEM is performed in the digital domain by resorting to specialized functions. The basic scrambler aims to de-correlate each two-levels noise output, so that the error contribution due to subsequent analog mismatches becomes just an additive random noise. Higher complexity DEM techniques try to shape the error associated to each element to move the noise in the OOB zone. Basic DEMs take into account only the static analog error, while advanced algorithms are able to also cope with dynamic errors, in particular ISI mismatch. These DEMs still work on maintaining the static mismatch shaping, but they also try to decorrelate from the signal the average number of transitions between the two available levels, applying noise shaping on this source of error when possible. The final goal is to have each unary (two-level) element carry the signal constructively with respect to the others and shaped errors (digital quantization plus analog static and dynamic mismatches) destructively, or at least make them as uncorrelated as possible. In other words, each element has to be treated as an idividually constrained 1 bit delta-sigma modulator. This can be done efficiently, in particular in applications when the shaping of ISI error is neglected, using algorithms like Data Weighted Averaging (DWA). For example, it can be employed efficiently when dealing only with noise, whose harmonic distortion consists on other attenuated noise. Other DEM noise shaping techniques are possible using vector quantizers [37] but, like high-order delta-sigma modulators, they tend to suffer from instability issues. Some DACs use segmentation to reduce total quantization noise: instead of only equally-weighted unary elements, it is possible to employ also heterogeneous elements if the input signal is split in the right way. Usually, the best scheme is to have the principal elements to carry only the signal

and use smaller elements only to compensate for the noise generated by the first stage, but it is also possible to have the smaller elements carry part of the input signal, if needed.

#### 1.1.2 Analog Front-End

Once the previous stage has generated the stream of unary-weighted contributions, it is time to convert it from a logic digital representation to the actual analog signal. If the implemented DEM technique performed good enough to create streams relatively insensitive to analog mismatch, it is possible to directly convert them to an electric signal. Otherwise calibration methods are needed to ensure the signal accuracy in the analog domain. Calibration is a cumbersome and delicate procedure that can be carried off-line, when the system is not used, or on-line, while the system is in use. Even with constant on-line calibration, it is difficult to match the SNR result of DEM-enhanced DACs, but a rough calibration can still help improve the output signal quality. In fact, DEM is only a palliative that, on average, removes the error from the audio signal band to move it elsewhere, but if not applied properly it can generate other errors that can modulate back into the audio band.

The conversion from the digital domain to the analog domain is usually carried out by resorting to one of three types of discrete units of information: the electric charge (for switched-capacitor DACs), the current per clock cycle (for current-steering and resistor-ladder DACs) or voltage per clock cycle (for other exotic multi-level systems, usually for direct digital power amplification or power inverters). Currents and charges are much easier to sum under the Kirchhoff Current Law (KCL) principle. Voltages, which exploit the Kirchhoff Voltage Law (KVL), are more difficult to handle. The two former methods are preferred, in particular when dealing with integrated circuits. Switched-capacitor circuits are easily integrated on silicon as they are based on the ratio of capacitance between elements, not their absolute value. They are less sensitive to dynamic errors like ISI and jitter so they are usually preferred for integration, yet they are affected by the issue that each clock cycle the capacitors have to be recharged. For switched-capacitor circuits is not possible to resort directly to techniques like Pulse-Width Modulation (PWM) to reduce the global transition rate. On the other hand, current-based analog implementations are better suited to handle PWM-like signals and higher OSR modulators,

as, usually, their operation can be faster than the switched-capacitor counterpart. For discrete implementations, this is the preferred technology because high-precision current sources or high-precision discrete resistors are cheaper and easier to manufacture than high-precision reactive components like capacitors and inductors.

The analog front-end is severely affected by the noise coming from the digital part of the circuit, so it is important to have electrical separation of the two parts. The clock jitter directly affects the quality of the signal as any jitter will be inter-modulated in the base-band due to non-linear effects. This part requires the best precision clock available, directly coming from a high-quality crystal oscillator instead than from a PLL circuit. The PLL can be safely used to clock the digital part but a synchronization mechanism (usually a chain of flip-flops) is needed before entering the analog domain. To avoid the supply-related noise it is possible to employ differential circuits. If well implemented, this error can be greatly reduced as it will act as a common-mode noise over a differential signal.

Switched-capacitors and current-steering circuits usually rely on operational amplifiers to make sure that the output signal behaves as a stable low impedance voltage source. A high-quality, low noise operational amplifier is needed to ensure the best output possible.

### 1.2 Oversampling and error shaping

The theoretical background behind Delta-Sigma re-quantization method will be briefly explained in this section, but a more in-depth explanation can be found in [38]. Instead of using the minimum sample rate dictated by the Nyquist-Shannon sampling theorem, it is possible to *oversample* the signal at a higher frequency, which usually is a power-of-two-times the basic frequency to ease the interpolation and the decimation processes. The memory elements inside the filters are needed to exploit the time as an additional degree of freedom, to compensate the intrinsic quantizer error in a sample-by-sample basis. A coarser quantization is necessary because analog ADCs and DACs are limited to only a few bits of linearity due to element matching. Just a 0.1% of mismatch error drops the system linearity to about 10 bits of effective resolution. This technique can also be used in the digital domain to reduce the bit-width of operands, shrinking the

Figure 1.4: Oversampling reduces the mean quantization error  $\epsilon_q$

total required logic at the expense of a higher operational frequency.

The oversampling is needed to create a free spectral space where the excess quantization error can be stuffed. Even without noise-shaping, this error tends to occupy the whole available spectrum, as shown in Figure 1.4, reducing the average value compared to the non-oversampling case. This translates to a higher signal-to-noise ratio even without a noise shaper, but a much higher SNR can be achieved if one is used.

By defining the OverSampling Ratio (OSR) as the ratio between the actual sampling frequency and the non-oversampling *Nyquist* frequency (two times the signal bandwidth B),

$$OSR = \frac{f_s}{2f_R},\tag{1.1}$$

the quantization noise power, compared to the one in the Non-OverSampling (NOS) case, will be reduced on average by a factor equal to the OSR. The SNR will thus increase as the square root of OSR. For example, an OSR of 256 will lead to a SNR gain of 16 dB, about 4 bits of resolution, over the whole spectrum. With noise shaping it is possible to increase the in-band SNR even further at the expense of an OOB noise increase.

Another effect of oversampling is that the images of the signal, periodic repetitions in the frequency domain created by the sampling process, will be well separated. The requirements of the filters dedicated to anti-alias and anti-image can then be relaxed. Additionally, oversampling ADCs show the interesting property of capturing also parts of the signal that are out of the nominal baseband, in the ultrasonic range. It can be useful to correctly reproduce transients without time-domain smearing.

If not needed, this upper part of the spectrum can be effectively filtered out by digital

filters, as they can be built with a much higher accuracy and selectivity than the analog ones. Using NOS ADCs, the unfiltered OOB signal can show as an alias in the baseband, degrading the resulting performances. To avoid this, steep analog filters would be required and they usually show a poor phase response, degrading the signal timing. Symmetrically, in NOS DACs the periodic images have to be filtered out to remove high-frequency content that could harm the rest of the reproduction chain and ruin the accuracy of transients. Also this would require precision analog filters, with the same drawbacks of anti-aliasing filters.

Overall, oversampling is a very useful tool when the final frequency is not prohibitive to be dealt with and the excess error can be efficiently removed. This is the audio case, where even an OSR of 1024 means a working frequency of about 50 MHz, which is not too difficult to be processed by modern CMOS digital designs. At such high OSR it is possible to extend the noise-free band and use it as a *guard band* to increase the cut-off frequency of the reconstruction filter, improve transient fidelity and reduce the problems related to the implementation of the modulator and the filters.

## **Chapter 2**

## Re-sampling filters

Re-sampling filters are often the most resource-consuming part of the DAC structure. Due to oversampling, the input sampling rate must be increased and adapted to the master clock frequency used by the analog section. Integer factor sampling rate converters are easier to build and this is why many high-end DACs are equipped with two high-quality crystal oscillators. One is to cope with the CD sampling frequency, namely 44.1 kHz, and the other with the DAT sampling frequency, 48 kHz. This is a sub-optimal solution as two different clock domains are difficult to handle and route, and the master clock can be one of the most expensive parts of the system, as it usually is the highest precision component. DACs often rely on the fact that this component is very accurate to reduce the requirements of the other analog circuit components. It would be thus better to accurately re-sample the source to adapt it to a unique clock frequency, not vice-versa. A non-integer re-sampling factor is otherwise difficult to handle directly (for example with the structure proposed by Farrow in [39]) but can be well approximated when oversampling the input signal.

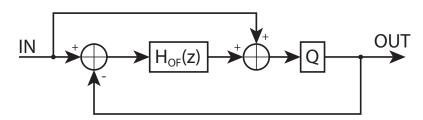

Now that is clear that oversampling is the answer to many analog and some digital problems, it is useful to review the upsampling and interpolation scheme used by almost all oversampling DACs. The first step is to upsample the signal by inserting an integer number of zeros between adjacent samples to increase the sampling rate. This process, called *zero-stuffing*, can be performed explicitly or implicitly, like in the polyphase filter case that will be later described. This operation does not modify the baseband signal spectrum but creates periodic replicas of it to fill the newly available spectral space.

Figure 2.1: Upsampling by zero-stuffing and filtering

The second step in integer factor re-sampling is to get rid of the spectral images created by the previous step. For an audio signal, that occupies a baseband near to DC¹, it is sufficient to employ a low-pass filter called anti-image filter. Figure 2.1 illustrates this process for a power-of-two oversampling. This step is not mandatory but the high-frequency components created by the upsampling process can be problematic. They can harm the stability of the rest of the system and fold back into the audio band due to unwanted non-linear processes. It is thus important to filter them out. This filter is often called *reconstruction filter* as it recovers the original signal shape in the time domain, in particular the transient-related information used by the human hearing to accurately reconstruct the recorded track. This filter can be implemented with a filter with only zeroes in its transfer function, called Finite Impulse Response (FIR) filter, or with an

<sup>&</sup>lt;sup>1</sup>The 0 Hz frequency bin is usually called Direct Current (DC)

Infinite Impulse Response (IIR) filter, which adds recursion to exploit the versatility of the transfer function poles [40]. The FIR filters are usually longer than IIR filters but they can realize exact linear-phase interpolation, which is important for proper time-domain signal reconstruction. FIR filters are commonly built without recursive structures so there are no recirculating quantization and overflow errors. If an error is made by an FIR filter, it will extinguish its contribution in a finite time thanks to its finite inpulse response property. On the contrary, IIR filters usually show lower latency due to a lower group delay, but a worse signal reconstruction fidelity due to phase non-linearity. IIR filters should be used only when the higher computational cost or the higher latency of a linear-phase FIR can not be tolerated. In this case, it is still adviseable to use filters with an enhanced phase linearity.

To reduce the implementation complexity of linear-phase filters, many efficient structures have been proposed, for example:

#### Polyphase filters [41-46]

This is a powerful and often exploited technique. Instead of using a single long interpolation filter working at the final sampling frequency, it is possible to avoid the upsampling-related zero-padding and directly work with a cascade of slower and shorter filters. Each stage usually performs an integer factor re-sampling, so it is possible to factorize the required OSR value to obtain the needed chain of filters.

#### Half-band and Nyquist filters [46-51]

These filters are very useful for integer factor interpolation as many coefficients are zeros, thus requiring no calculations when performing the convolution. The main problem with this family of filters is that the fixed -3 dB cutoff point is placed at the Nyquist frequency. They thus cannot completely eliminate aliasing or images, they have to be employed carefully. For example, if a polyphase structure is used, the first interpolation filter should not be a half-band filter to correctly remove the nearest upsampling image. Half-band filters work on half the spectrum, while Nyquist filters (also called M-th band filters) with higher integer factors.

#### **DFT-Based Convolution** [52-57]

These filters work in the frequency domain, thanks to the Discrete Fourier Transform (DFT). They return more than one sample per computation with a lighter computational workload compared to explicit FIR filtering, thanks to the Fast Fourier Transform (FFT) algorithm. The main problem is that in the frequency domain it is possible to perform only *cyclic* convolution but an FIR filter requires *linear* convolution. The border results have to be discarded accordingly to avoid cyclic convolution-related artifacts. This method is often called Overlap-Save Method (OSM) or Overlap-Add Method (OAM).

Interpolation can be also carried out efficiently in the frequency domain by zero-padding the high-frequency zone with additional zeroed bins and then performing the inverse Fourier transform. This will add a null high-frequency contribution, but the number of samples per block will be increased while leaving the original signal spectrum intact.

#### Interpolated FIR [58-63]

The IFIR method aims to make narrowband FIR filters as the cascade of an upsampled FIR (which has many coefficients equal to zero) with one or more image-rejecting filters. The complexity is lower than a direct implementation but still high. The resulting filter is usually not optimized for frequency response, limiting the quality of the resulting equivalent filter.

#### Sharpened CIC filters [64-69]

Cascade of Integrator-Comb (CIC) filters are a particular case of FIR filters that resort to pole-zero cancellation to null the effect of a recursive structure. The basic CIC filter performs the *moving average* operation, which is a simple linear-phase low-pass filter with poor frequency response. By cascading differently weighted CIC filters it is possible to enhance the frequency response of the total structure, while maintaining the simple basic CIC structure. This type of filter is called *Sharpened CIC* filter.

The CIC often needs a fixed-point implementation to ensure the correct pole-zero cancellation and it is robust against overflow errors thanks to the modular wrap-around property of two's complement algebra implementation. CIC is often used

as the last stage of a polyphase filter, where the images are already well separated frequency-wise, and its amplitude error (compared to the ideal low-pass filter) can be compensated in previous stages.

## Reduced-coefficient-width FIR [70-75]

This type of filter exploits noise-shaping to re-quantize the filter coefficients and/or the input signal to reduce the word length of operands. The OOB noise generated by this method has to be compensated, for example using a CIC filter. The noise-shaping has the same issues of  $\Delta\Sigma$  modulators, so it has to be approached carefully due to non-linear effects. Theoretically, it is possible to realize also unary coefficient filters, which have only 1 bit coefficients, and build very fast multiplication-free filters.

### Shared coefficients FIR [76-80]

There are some cases in which filters present some shared coefficients. In particular, linear-phase filters have the property of *symmetry* or *anti-symmetry* in the coefficients around half the filter length. If the filter order is odd with even symmetry it is called *Type I.* If the filter order is even with even symmetry it is a *Type III* filter. If the filter order is odd with odd symmetry it is a *Type III* filter. If the filter order is even with odd symmetry it is a *Type IV* filter. Low-pass filters used in interpolation are of type I or II. By exploiting symmetry it is possible to trade half the filter multiplications with an equal number of additions. This is useful to decrease the filter area and its power consumption.

### Other multiplication-free techniques [81–85]

It is possible to factorize and quantize the multiplicative coefficients to trade multiplications for sums-of-shifts (which do not require any active logic but it is only a matter of wiring adders). Common Subexpression Elimination (CSE) and Multiple Constant Elimination (MCM) algorithms can efficiently group operands to reduce the number of adders, leading to a smaller filter implementations. This is a rather inflexible structure, it is not possible to change the filter kernel without a full re-design.

### Truncated IIR [86-88]

this is a particular class of filters that implements an FIR as a sum of two IIR filters,

presented in [86]. The second filter is used to null the time-domain response of the first filter after a certain time delay. This is a powerful technique because it merges the advantages of an IIR filter (small size, low memory and resource-consuming) to the FIR ones (in particular phase linearity). The main problem is that this structure is subject to recirculating errors. They can exponentially grow if the IIR poles are outside the unit circle, which is mandatory for the linear-phase filter design techniques proposed in the original paper. Two TIIR filters can be used in parallel and resetted alternatively to periodically reset the recirculating error but the exponential nature of this filter limits in practice the achievable filter length. An important advantage of TIIRs is that they require only two input samples per output update, whilst the other non-recursive FIR implementations require a tapped delay line of the same length as the filter kernel. TIIRs can be implemented with a single circular buffer acting as a FIFO buffer, hence it is possible (and convenient) to use a much simpler and slower memory to store the entire delay line.

Other non-linear interpolation techniques have been proposed in the literature, which do not follow Fourier and Nyquist-Shannon theories. This is the case of *wavelet* or *spline* interpolation techniques. They try to build a good reconstruction of the signal but can affect the phase linearity [89]. It is also possible to try to enhance the interpolation with techniques labeled *super-resolution*. They guess the signal content also in the OOB zone, violating the Nyquist-Shannon sampling theorem. Recent advancements in Artificial Intelligence (AI) led to good results but it is not possible to truthfully reconstruct the original signal with this method, it will always add some artifacts. Also, due to the excessive computation required, it is difficult to perform super-resolution in real time.

# **Chapter 3**

# Re-quantization modulators

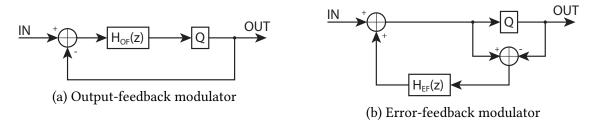

In audio applications, it is difficult to ensure the required audio quality through a low sample rate, high-resolution Digital to Analog stage. The human hearing system is very sensitive to harmonic distortion and correlated processes. Analog mismatches between elements limit the effective resolution and linearity achievable. It is then useful to employ some oversampling and re-quantization schemes to overcome these limits. Re-quantization is performed with an error-shaping algorithm, like the Output-Feedback (OF) Delta-Sigma modulator schematized in Figure 3.1, to increase the in-band SNR. Quantization error shaping is employed when the output signal word width is smaller than the input one, for example when converting a studio-quality master track to the CD format, for Analog to Digital recording, or Digital to Analog reproduction.

#### Error de-correlation by dithering

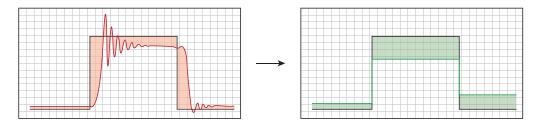

Each re-quantization stage adds some noise to the signal, so it is important to minimize the number of times this process is applied to reduce signal degradation. Quantization is a non-linear operation that introduces non-linear distortion. It is then important to linearize this operation to help the noise shaper remove as much error as possible. This can be achieved by a technique called *dithering*. The dither is an uncorrelated random signal that is added before quantization to make the quantizer behave more linearly, at the expense of total output signal noise. Triangular Probability Density

Figure 3.1: Basic output-feedback quantization error shaper ( $\Delta\Sigma$  modulator)

Function (TPDF) noise with an amplitude of 2 times the Least Significant Bit (LSB) can de-correlate up to the second moment of the quantization error [27, 90]. Digital artifacts like harmonic distortion and spurious tones are then reduced, but the dither signal can harm the stability of the modulator and reduce the maximum allowed signal amplitude. Figure 3.2 visually shows the effect of re-quantization with and without dither for an image. The same concept can be applied to a discrete-time signal (like digital audio).

#### The $\Delta\Sigma$ Modulator

The feedback part of the noise shaper is traditionally called Delta-Sigma Modulator  $(\Delta \Sigma M)$  because, in the classical OF implementation, it takes the *difference* (Delta) between the input and the output signals and employs some integrators (Sigma) to analyze and correct the quantization error in a sample-by-sample basis. The signal and the shaped error are then superposed and quantized. The new output value is fed back to the Delta stage. This is called a negative feedback system in the Automation field. The quantization error can be de-correlated and treated like an additive gaussian source of error that has to be compensated with a closed-loop solution. This simplified linear model often offers a poor assumption of the quantizer nonlinear effects. It is possible to build both recursive and non-recursive linear filter structures but there are two main rules to observe: the first sample of the Noise Transfer Function (NTF) impulse response must be equal to one and the loop must present at least one delay. Delay-free loops are not causal and they cannot be realized in practice. In the OF topology, this means that the first sample of the noise shaper filter impulse response must be equal to zero. This severely limits the filter design possibilities. At the same time, high-order filters are more prone to quantizer overload, hence it is notably difficult to build stable high-performance  $\Delta\Sigma$ Ms.

(a) Original image, 24 bits per pixel

(b) Image quantized to 3 bits per pixel, without dither

(c) Image quantized to 3 bits per pixel, with dither

(d) Image quantized to 3 bits per pixel, with dither and noise-shaping

Figure 3.2: Visual example of the effects of dither and noise-shaping on quantization

## **Stability**

A major problem for the  $\Delta\Sigma M$  is that there is a limit to noise-shaping achievable: the re-quantization can be seen as a two-stage system, the cascade of an unbounded quantizer and a saturation element. The quantizer is just a source of noise and this does

not affect the stability of the system. The saturation is what makes the problems arise. It can drive the system to instability as it prevents the feedback from correctly compensate the error accumulated by the noise shaper. Various possible solutions to this issue have been proposed in the literature, but they all require some active observation of the noise shaper status to apply non-linear compensation mechanisms. For example, it is possible to saturate or reset the values stored in the loop filter integrators to temporarily reduce the filter order to a stabler noise-shaping function, as explained in [91]. In this case the tradeoffs are a lower performance noise-shaping and complex stabilization systems for an extended input range stability.

The stability of a  $\Delta\Sigma$ M is difficult to predict exactly and extensive simulations are required to evaluate the effective design performances. If the modulator is not dithered sufficiently, the quantization noise cannot be treated as simple additive noise. The modulator will generate spurious tones and harmonic distortion. This is particularly problematic for low-resolution quantizers, for which also small dither signals can drive the quantizer to overload and the whole system to instability. The two-levels quantizer is the worst-case scenario as it is not possible to apply the required amount of dither without causing instability. The signal transfer function needs to be linearized in other ways, for example by using signal-dependent dither and instability correction schemes. Unfortunately, the two-levels quantizer is the only one guaranteed linear in the analog domain as there can be no mismatch in a single element DAC. This is why multi-level DACs are usually decomposed to a sum of many two-levels elements by DEM techniques. When designing a  $\Delta\Sigma$ M there are various rules-of-thumb developed by heuristically observing the structure of known stable modulators or by simplifications of the  $\Delta\Sigma M$ model. Some rules dictate the sufficient conditions for a guaranteed stable modulator but they are often very conservative [92, 93]. They can mark a higher performance modulator as "possibly unstable" even if the simulations show it to be perfectly stable. The majority of modulators are stable only for a limited input signal range and only if the overload range is crossed for a limited amount of time.

One of the most common stability tests is to feed the  $\Delta\Sigma M$  with an input value with constant amplitude, starting from zero and rising gradually this value at each iteration. If that constant input does not give rise to instability in a given amount of simulation time, the modulator is considered stable for that particular input DC value and the next

simulation step will be performed with a higher constant input. At a certain point, the re-circulating noise created by the bounded quantizer will overload the quantizer input, making the system unstable. Due to the nature of the integrators used by  $\Delta\Sigma$ Ms, at a first sight the DC input could seem to be the worst-case scenario but it is not always the case due to the negative feedback loop effect. Particular input signals can force the  $\Delta\Sigma$ M into instability, as explained in [38]. It is not easy to predict which input pattern would make the instability rise. It is thus mandatory to simulate many possible input signals to validate the modulator behavior and always exploit stabilization techniques.

$\Delta\Sigma$ M design is an art. It takes a lot of time and many efforts to finely tune the parameters for stability and SNR. The loop filter is usually designed starting from the desired NTF by considering the system as linear and then simulating it. If the system does not meet the required specifications it has to be re-designed with a less aggressive NTF.

Other advanced techniques employ non-linear control schemes like Sliding Mode Control (SMC) [94] or look-ahead techniques [26]. SMC is suitable for real-time modulation as it does not need a much higher computation effort compared to classic Delta-Sigma schemes. Look-ahead modulators, instead, can be effectively employed for mastering purposes but they cannot be easily used for real-time applications if more than a couple of look-ahead samples are required.

## Multi-level quantizer features

Multi-level (or multi-bit) quantizers offer many advantages. Unlike the two-levels counterpart, the quantizer gain is better defined, it is easier to linearize and to ensure stability [95]. It is also possible to apply the right amount of dither without overloading the quantizer. The quantization error shows a lower correlation with the input signal due to the smaller quantizer step sizes and the presence of multiple transition regions. Multi-bit re-quantization is ideal for digital signal manipulation but there are problems with the analog stages in ADCs and DACs, as it is not possible to map a multi-level digital value to an analog level without adding static and dynamic errors. This will