# POLYTECHNIC UNIVERSITY OF TURIN

DOCTORAL SCHOOL - 33<sup>RD</sup> CYCLE

DISSERTATION FOR THE DOCTORAL PROGRAM IN:

ELECTRICAL, ELECTRONICS AND COMMUNICATIONS ENGINEERING WITH CURRICULUM IN "ELECTRONIC DEVICES"

# Enhanced Electrical and Reliability Testing of Power Semiconductor Devices

Author:

Davide CIMMINO

Supervisor:

Prof. Candido Pirri

Co-Supervisor:

Prof. Sergio Ferrero

Thesis Sponsorship:

Vishay Intertechnology, R&D Power Diodes Division, Borgaro, Italy

## Abstract

### Enhanced Electrical and Reliability Testing of Power Semiconductor Devices

by Davide Cimmino

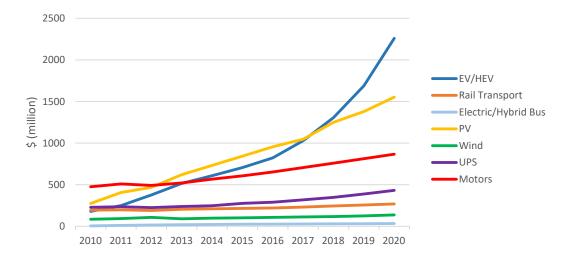

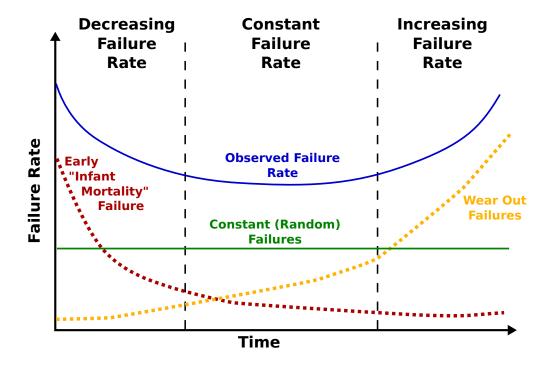

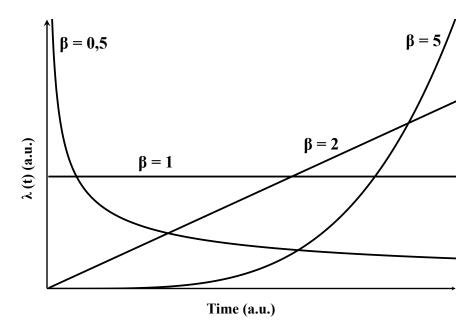

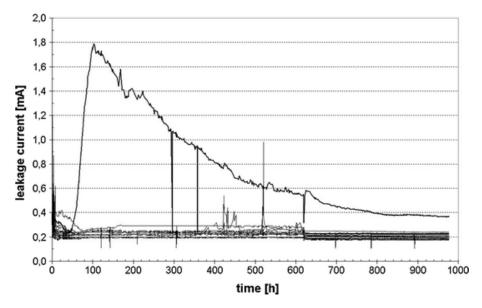

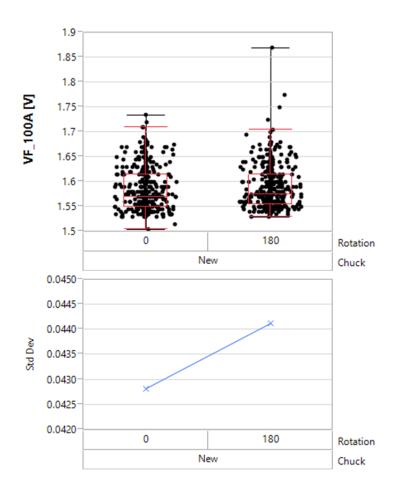

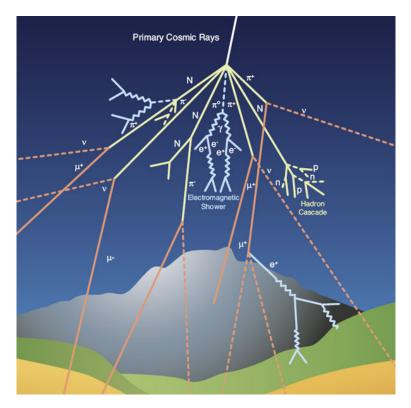

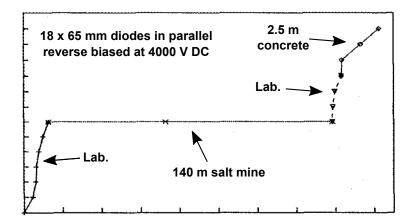

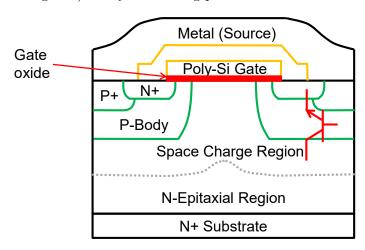

Before the last two decades, power electronics was strictly related to electrical engineering, and relegated to applications ranging from medium to high powers, such as industry drives, railway traction and power supplies. But with the increasing demand for electricity and the diffusion of modern consumer products related to power management, the whole grid comprehending generation, transmission, distribution and use of electric energy, gained remarkable visibility along with the engineering field of power electronics, with the goal of maximizing the efficiency, versatility and reliability of the supply chain, as well as the integration of renewable power sources into this continuously evolving organism. This PhD thesis, carried out at the Polytechnic of Turin and sponsored by a Vishay Intertechnology Inc. scholarship, focuses on the performance and lifetimes of power semiconductor devices, when electrical and environmental testing conditions apply high stress to the devices beyond current standards, especially in terms of reliability. Part I gives a brief introduction on the major definitions in the field of reliability testing, focusing on the terms involved in the following sections, along with an overview of current and possible future trends in the field of reliability testing. In part II, the standard High Temperature High Humidity Reverse Bias (H3TRB) reliability test for power semiconductor devices, also known as Temperature Humidity Bias (THB) test, is performed at high voltage in order to investigate and analyze peculiar failure modes generated by the combination of high reverse bias voltage and humidity. The results led to the publication of 3 research papers during the doctoral program. The main topic of part III is the study and development of a high-current on-wafer Forward Voltage Drop (VF) drop measurements system for power semiconductor diodes. The methodology involves the design, characterization, evaluation and further improvement of a dedicated testing setup with the objective of performing measurements without inducing any degradation in the devices under test. Eventually, part IV is dedicated to the evaluation of the cosmic ray ruggedness of power semiconductor devices. The testing has been performed in agreement with the JEDEC standard JEP151, and the experimental work involved the development of dedicated testing boards, for the following test campaign at the "ISIS Neutron and Muon Source" of the "Rutherford Appleton Laboratory" in Didcot, United Kingdom.

# Acknowledgements

At the moment of writing this acknowledgment section, a lot of mixed feelings spiral inside my head as I conclude this doctoral program and my thesis manuscript. It is indeed a very complicated period of modern history. If I think about the difference from how everything changed from the beginning of these three years to the present, it really feels like a incredible amount of time. I have changed a lot as a person and as a professional, and I believe I owe most of what I have achieved to a multitude of individuals whose consciousness, presence, grit, determination, kindness, patience, charisma, friendship, involvement and love, have let me understand how much we need to grow up everyday as workers, students and human beings in order to evolve toward a better future, for us in our daily life, and for everyone else with our legacy.

First of all I want to say thanks to the two institutions that made my doctoral program possible, which are the Polytechnic University of Turin on the academic side, and Vishay as the company who issued the scholarship for my research. In particular I am grateful to my supervisor Prof. Candido Pirri from the Department of Applied Science and Technology (DISAT), and Rossano Carta from Vishay, head of the Power Diodes R&D group, who represented for me these two worlds during my daily experience. When I first arrived at the company to start my research, Rossano welcomed me and followed my first steps in a territory which was unknown to me, as I started my very first experience after the master degree. I can say that his dedication and resolution really helped in shaping my approach to research, my experience in a company and my attitude as a young professional.

I am sure I would never change my co-supervisor Prof. Sergio Ferrero to anyone else. He has seen me in the best and worst moments, and I am proud and grateful of the human relationship that we naturally formed. He successfully supported me through the complex world of research publications, as well as being my point of reference at the Polytechnic of Turin. I want to say thanks to all my colleagues at Vishay, from all the laboratories and departments, for the great support and effort they dedicated to me and my projects, in particular to Nabil El Baradai who became my supervisor at the company in the last year, for his knowledge, dedication and friendship, as we fought side by side to achieve our objectives. I am also grateful to Giovanni Richieri and Roberta Busca for the great synergy that we established together, in order to gave birth to two of the publications from this thesis, I would have never reached this goal without them.

In conclusion I would like to say thanks to my friends, family, my parents and in particular my brother and my girlfriend Roberta, for how much they have done for me in this period. Your encouragement, your strength and affection, have helped me in the hardest moments to reset and start again with all my enthusiasm, you are the foundations holding the temple of my spirit.

Davide Cimmino Turin, Italy March 15, 2021

# Table of Contents

| A        | bstra            | $\operatorname{ct}$ |                                                                                                               | iii  |

|----------|------------------|---------------------|---------------------------------------------------------------------------------------------------------------|------|

| Ta       | able o           | of Con              | itents                                                                                                        | ix   |

| Li       | $\mathbf{st}$ of | Figur               | es                                                                                                            | xiii |

| Li       | st of            | Table               | ${f s}$                                                                                                       | xvii |

| Li       | st of            | Abbre               | eviations                                                                                                     | xix  |

| Ι        | Int              | roduc               | tion                                                                                                          | 1    |

| 1        | Intr             | oducti              | ion                                                                                                           | 3    |

|          | 1.1              |                     | s Framework and Outline                                                                                       |      |

|          | 1.2              |                     | luction                                                                                                       |      |

|          |                  | 1.2.1               | Power Devices and Global Trends                                                                               | 4    |

|          |                  | 1.2.2               | Reliability: basics concepts and definitions                                                                  | 5    |

|          |                  | 1.2.3               | Mathematical Definitions                                                                                      | 7    |

|          |                  |                     | 1.2.3.1 Weibull Distribution                                                                                  |      |

|          | 1.3              | Overv               | riew of Power Semiconductor Reliability Testing                                                               |      |

|          |                  | 1.3.1               | Reliability Test Standards for Power Semiconductor Devices .                                                  |      |

|          |                  |                     | 1.3.1.1 High Temperature Reverse Bias test (HTRB)                                                             |      |

|          |                  |                     | 1.3.1.2 High Temperature Gate Stress (HTGS) Test                                                              |      |

|          |                  |                     | 1.3.1.3 Temperature Humidity Bias (THB) Test                                                                  |      |

|          |                  |                     | 1.3.1.4 High Temperature and Low Temperature Storage Temperature Cycling and Temperature Shack Test           |      |

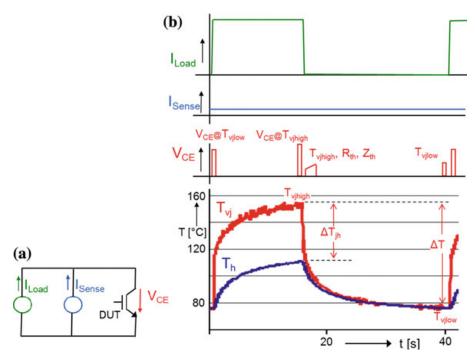

|          |                  |                     | <ul><li>1.3.1.5 Temperature Cycling and Temperature Shock Test .</li><li>1.3.1.6 Power Cycling Test</li></ul> |      |

|          |                  |                     | 1.3.1.7 Cosmic ray Testing                                                                                    |      |

|          |                  | 1.3.2               | Current and future challenges of reliability testing                                                          |      |

|          |                  | 1.0.2               | 1.3.2.1 Current approaches to enhanced reliability                                                            |      |

|          |                  |                     | 1.3.2.2 Future Challenges                                                                                     |      |

| тт       | TT               | ah Va               | oltomo Tomoronoturo II. miditu Diog (IIV TIID) Togt                                                           | 0.1  |

| 11       | П                | ign ve              | oltage Temperature Humidity Bias (HV-THB) Test                                                                | 21   |

| <b>2</b> | Hig              |                     | age Temperature Humidity Bias (HV-THB) Test                                                                   | 23   |

|          | 2.1              |                     | luction                                                                                                       |      |

|          | 2.2              |                     | w and state of the art of HV-THB                                                                              |      |

|          |                  | 2.2.1               | Introduction                                                                                                  |      |

|          |                  | 0.00                | 2.2.1.1 Current Normatives                                                                                    |      |

|          |                  | 2.2.2               | Comparison of Test Methodologies                                                                              |      |

|          |                  |                     | 4.4.4.1 Test bettub and I foredures                                                                           | Z(i) |

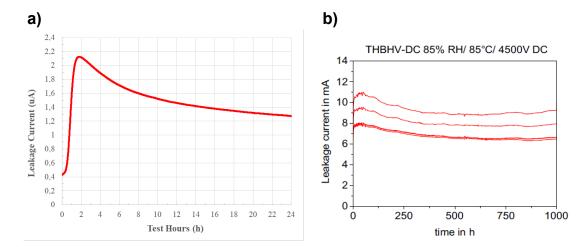

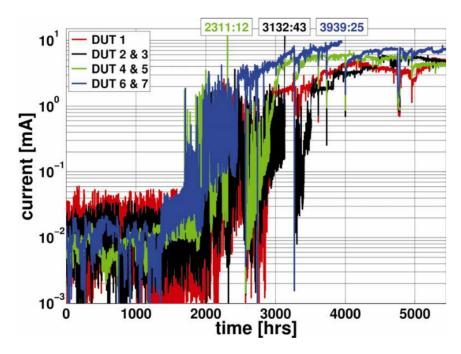

|    |                        |                                                                                                                                                | 2.2.2.2 Leakage Current Monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                                       |

|----|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

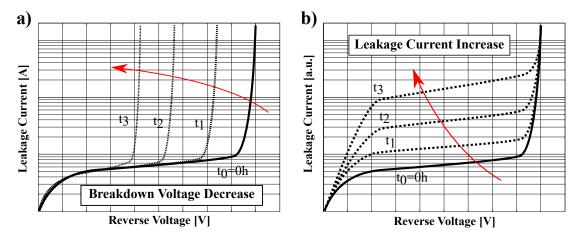

|    |                        |                                                                                                                                                | 2.2.2.3 Intermediate Testing and Electrical Degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                                       |

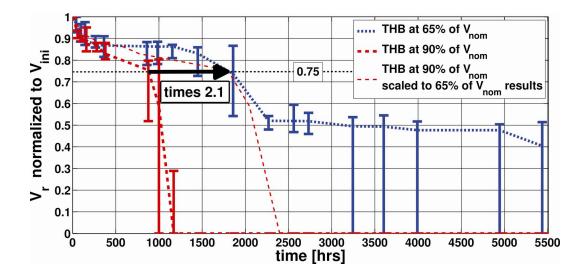

|    |                        |                                                                                                                                                | 2.2.2.4 Accelerated Test Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                                                                                       |

|    |                        | 2.2.3                                                                                                                                          | An overview of the failure modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                                                                                                       |

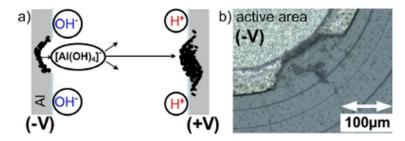

|    |                        |                                                                                                                                                | 2.2.3.1 The Corrosion Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31                                                                                                       |

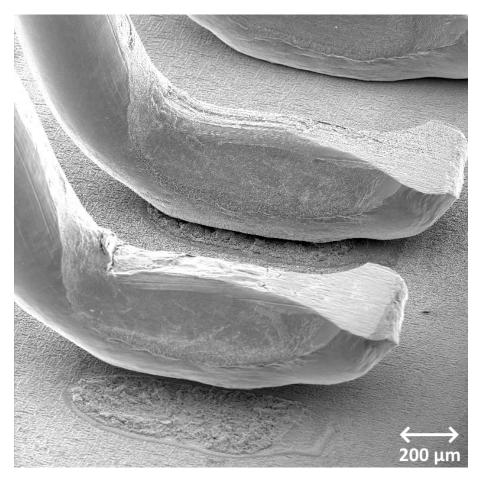

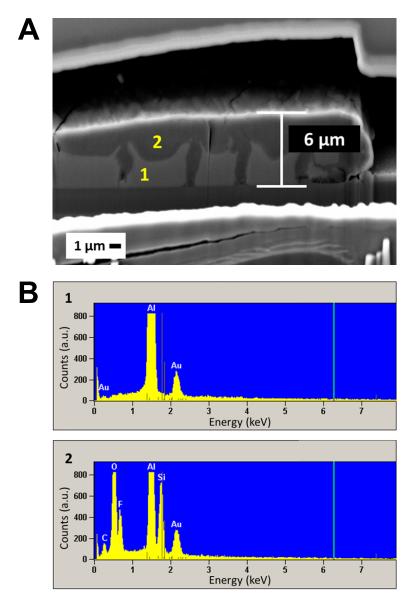

|    |                        |                                                                                                                                                | 2.2.3.2 Aluminum Corrosion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31                                                                                                       |

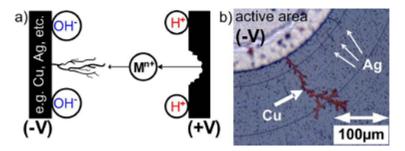

|    |                        |                                                                                                                                                | 2.2.3.3 Electrochemical Migration (ECM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                       |

|    |                        |                                                                                                                                                | 2.2.3.4 Device Failure Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                                                                       |

|    |                        | 2.2.4                                                                                                                                          | Materials and Accelerated Testing Performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34                                                                                                       |

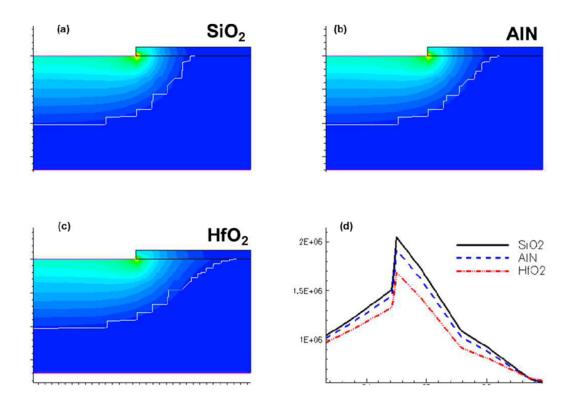

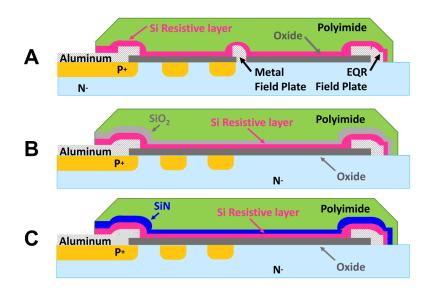

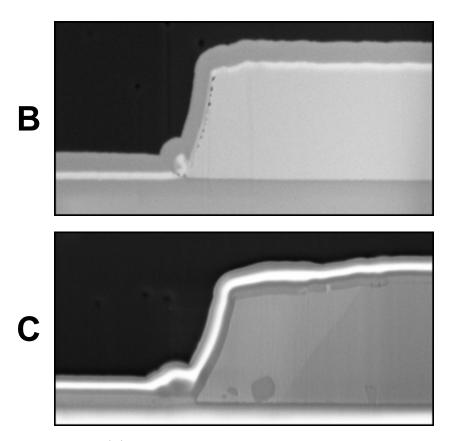

|    |                        |                                                                                                                                                | 2.2.4.1 Passivation and Termination Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                                                       |

|    |                        |                                                                                                                                                | 2.2.4.2 Silicon Nitride as a Passivation Material                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36                                                                                                       |

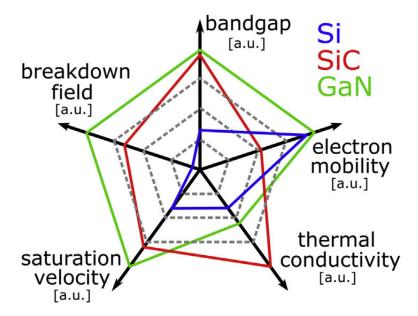

|    |                        |                                                                                                                                                | 2.2.4.3 Silicon Carbide Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                                                                       |

|    |                        | 2.2.5                                                                                                                                          | Review Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                                       |

|    | 2.3                    | Metho                                                                                                                                          | odology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39                                                                                                       |

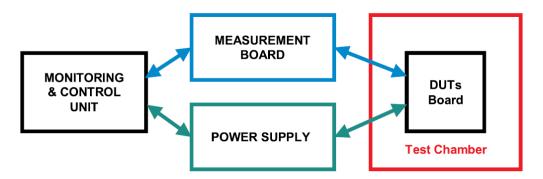

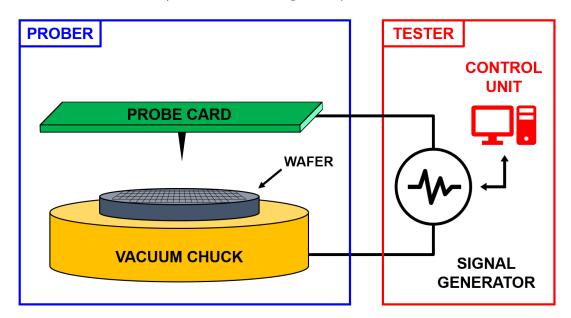

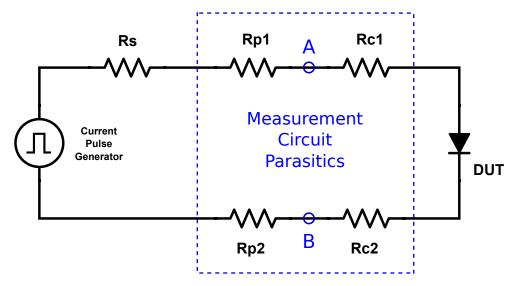

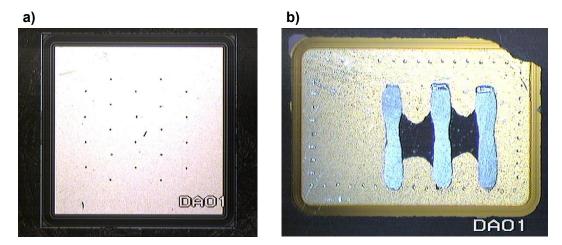

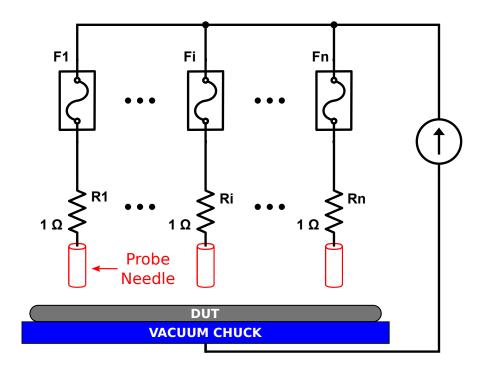

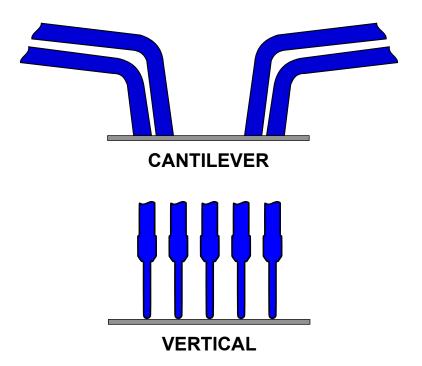

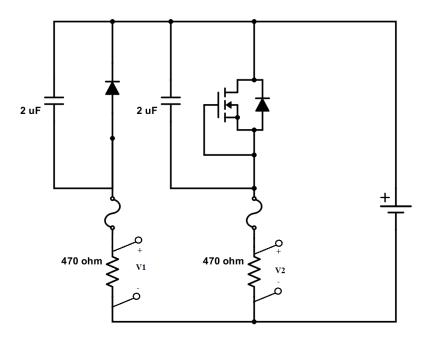

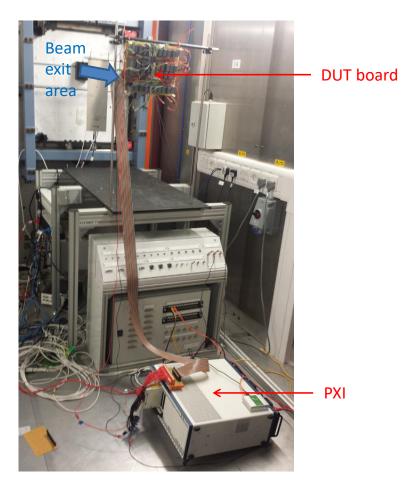

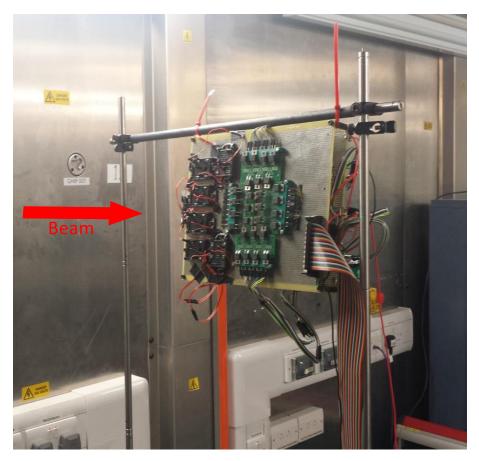

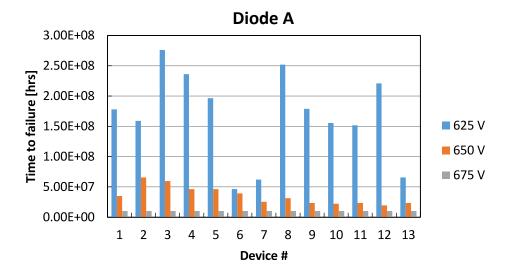

|    |                        | 2.3.1                                                                                                                                          | Design of the measurement system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                                                       |

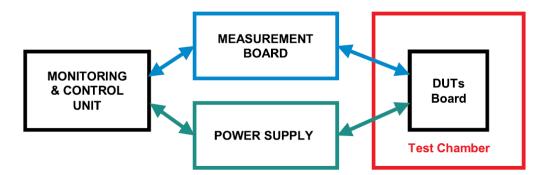

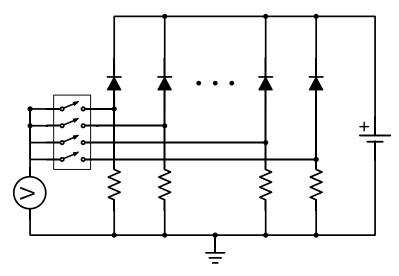

|    |                        |                                                                                                                                                | 2.3.1.1 System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                       |

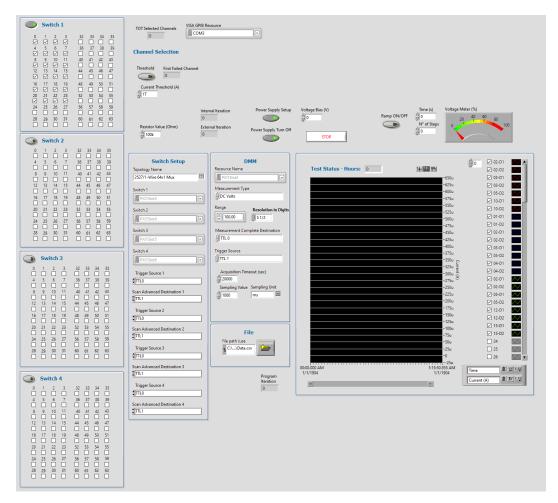

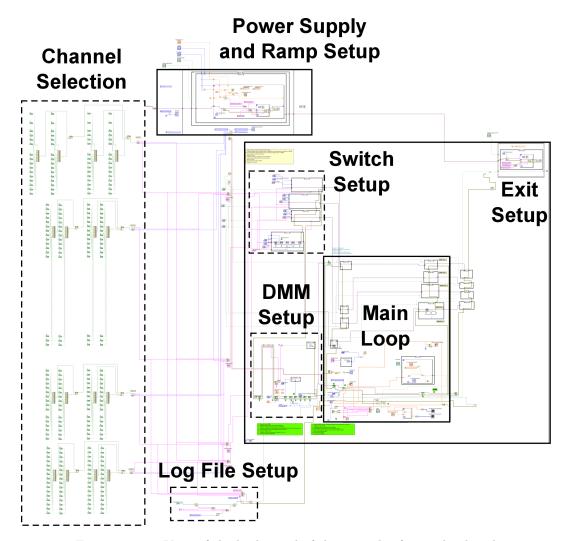

|    |                        |                                                                                                                                                | 2.3.1.2 Programming of the Control System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                                                                                       |

|    |                        |                                                                                                                                                | 2.3.1.3 Test conditions and DUTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44                                                                                                       |

|    |                        | 2.3.2                                                                                                                                          | System Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                       |

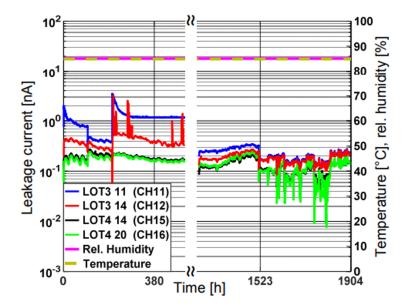

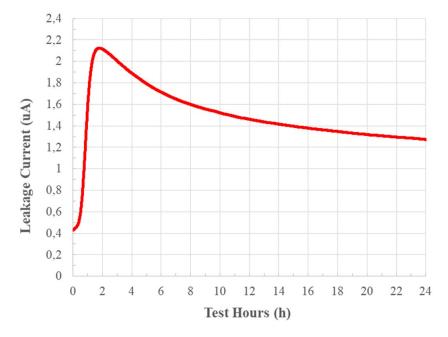

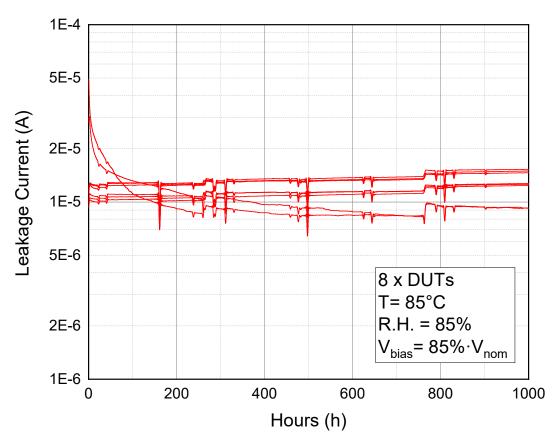

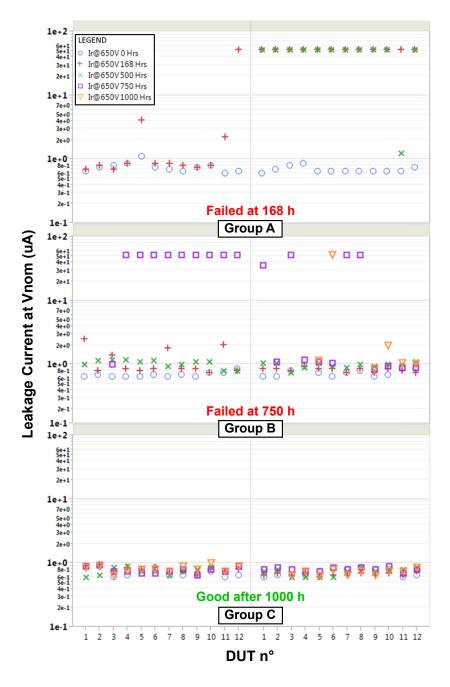

|    |                        |                                                                                                                                                | 2.3.2.1 Monitoring of the leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                       |

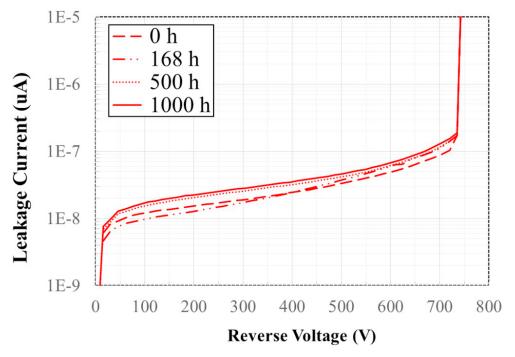

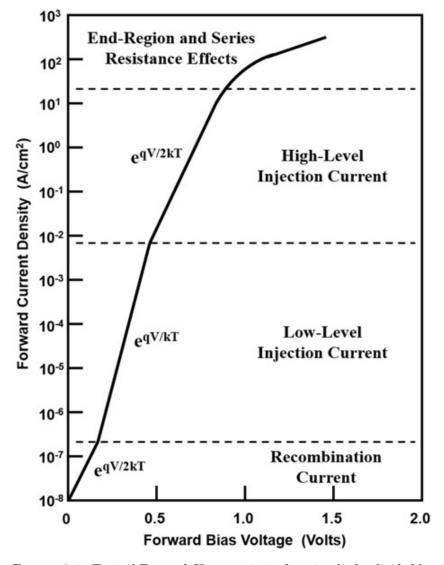

|    |                        |                                                                                                                                                | 2.3.2.2 Curvetracer analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47                                                                                                       |

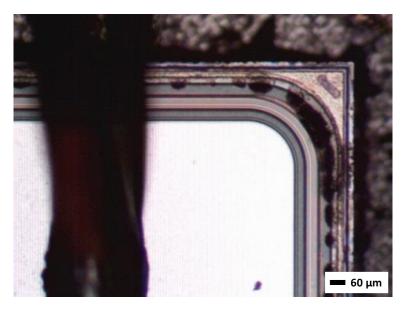

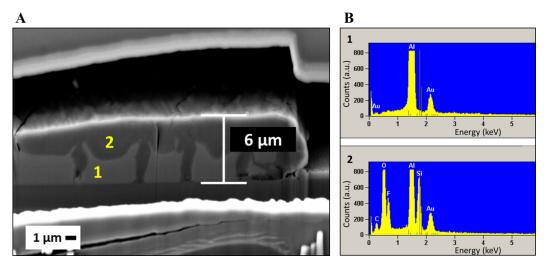

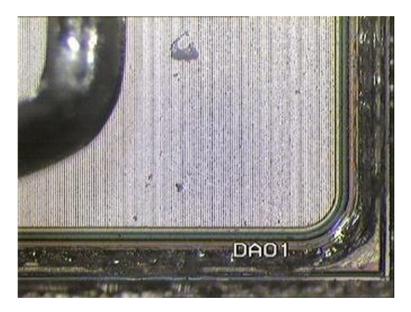

|    |                        |                                                                                                                                                | 2.3.2.3 Device Failure Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                                                                                                       |

|    |                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |

| II | 2.4<br>I C             |                                                                                                                                                | $egin{array}{lll} egin{array}{lll} egin{arra$ | 54<br>of                                                                                                 |

|    | I C                    | )n-Wa                                                                                                                                          | ${f G}_{f C}$ fer High Current Forward Voltage Drop $(V_F)$ Test ${f G}_{f C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

|    | I C<br>ower            | )n-Wa<br>Semi                                                                                                                                  | ${f G}$ fer High Current Forward Voltage Drop $(V_F)$ Test ${f G}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{of}$                                                                                            |

| P  | I C                    | On-Wa<br>Semi<br>Wafer                                                                                                                         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | of<br>55                                                                                                 |

| P  | I C<br>ower<br>On-     | On-Wa<br>Semi<br>Wafer                                                                                                                         | Ifer High Current Forward Voltage Drop $(V_F)$ Test conductor Diodes  High Current $V_F$ Test of Power Semiconductor Diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | of<br>55<br>57                                                                                           |

| P  | I C<br>ower<br>On-     | On-Wa<br>Semi<br>Wafer<br>Introd                                                                                                               | ${f Current \ Forward \ Voltage \ Drop \ (V_F) \ Test \ conductor \ Diodes}$ ${f High \ Current \ V_F \ Test \ of \ Power \ Semiconductor \ Diodes}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | of<br>55<br>57<br>57                                                                                     |

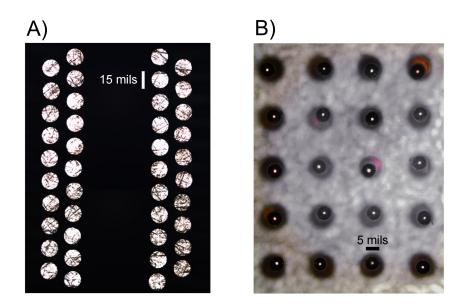

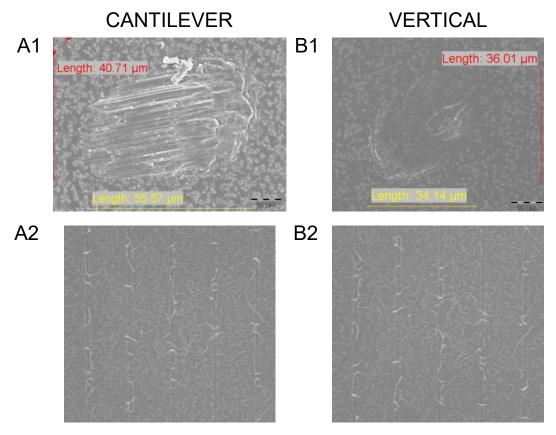

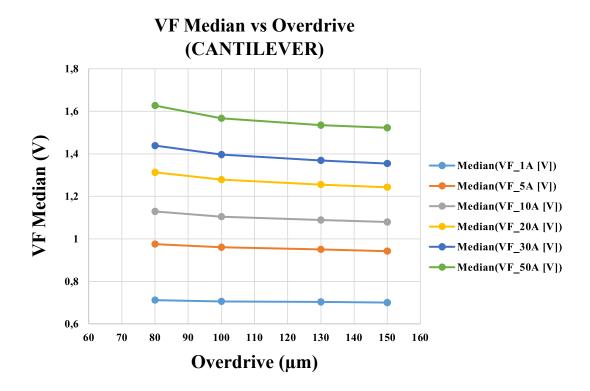

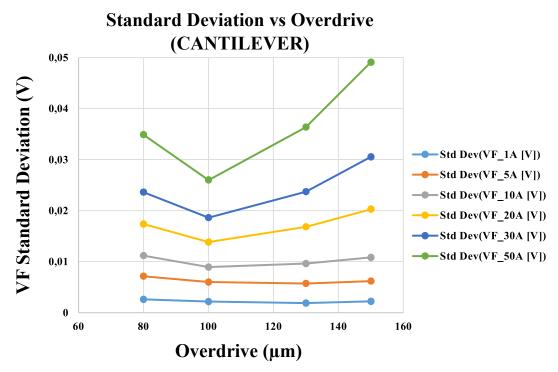

| P  | I C<br>ower<br>On-     | On-Wa<br>Semic<br>Wafer<br>Introd<br>3.1.1<br>3.1.2                                                                                            | Ifer High Current Forward Voltage Drop $(V_F)$ Test conductor Diodes  High Current $V_F$ Test of Power Semiconductor Diodes luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | of<br>55<br>57<br>57<br>57                                                                               |