# POLITECNICO DI TORINO Repository ISTITUZIONALE

Hardware and Software Optimizations for Accelerating Deep Neural Networks: Survey of Current Trends, Challenges, and the Road Ahead

Original

Hardware and Software Optimizations for Accelerating Deep Neural Networks: Survey of Current Trends, Challenges, and the Road Ahead / Capra, M.; Bussolino, B.; Marchisio, A.; Masera, G.; Martina, M.; Shafique, M. - In: IEEE ACCESS. - ISSN 2169-3536. - ELETTRONICO. - 8:(2020), pp. 225134-225180. [10.1109/ACCESS.2020.3039858]

Availability:

This version is available at: 11583/2859026 since: 2020-12-25T19:22:35Z

Publisher:

Institute of Electrical and Electronics Engineers Inc.

Published

DOI:10.1109/ACCESS.2020.3039858

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

Received October 23, 2020, accepted November 8, 2020, date of publication November 24, 2020, date of current version December 30, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3039858

# **Hardware and Software Optimizations for Accelerating Deep Neural Networks: Survey of Current Trends, Challenges, and the Road Ahead**

MAURIZIO CAPRA<sup>101</sup>, (Graduate Student Member, IEEE), BEATRICE BUSSOLINO<sup>1</sup>, (Graduate Student Member, IEEE), ALBERTO MARCHISIO 2, (Graduate Student Member, IEEE), GUIDO MASERA<sup>101</sup>, (Senior Member, IEEE), MAURIZIO MARTINA<sup>101</sup>, (Senior Member, IEEE), AND MUHAMMAD SHAFIQUE<sup>[D]</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical, Electronics, and Telecommunication Engineering, Politecnico di Torino, 10129 Torino, Italy

Corresponding author: Maurizio Capra (maurizio.capra@polito.it)

This work was supported in part by the Ph.D. College Resilient Embedded Systems which is run jointly by TU Wien's Faculty of Informatics and FH-Technikum Wien.

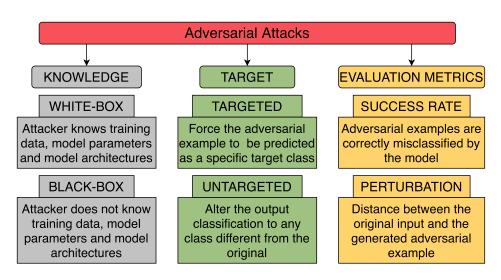

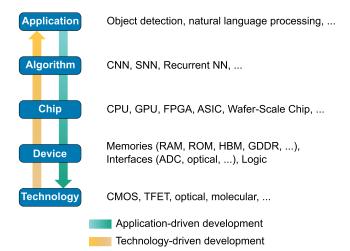

**ABSTRACT** Currently, Machine Learning (ML) is becoming ubiquitous in everyday life. Deep Learning (DL) is already present in many applications ranging from computer vision for medicine to autonomous driving of modern cars as well as other sectors in security, healthcare, and finance. However, to achieve impressive performance, these algorithms employ very deep networks, requiring a significant computational power, both during the training and inference time. A single inference of a DL model may require billions of multiply-and-accumulated operations, making the DL extremely compute- and energy-hungry. In a scenario where several sophisticated algorithms need to be executed with limited energy and low latency, the need for cost-effective hardware platforms capable of implementing energy-efficient DL execution arises. This paper first introduces the key properties of two brain-inspired models like Deep Neural Network (DNN), and Spiking Neural Network (SNN), and then analyzes techniques to produce efficient and high-performance designs. This work summarizes and compares the works for four leading platforms for the execution of algorithms such as CPU, GPU, FPGA and ASIC describing the main solutions of the state-of-the-art, giving much prominence to the last two solutions since they offer greater design flexibility and bear the potential of high energy-efficiency, especially for the inference process. In addition to hardware solutions, this paper discusses some of the important security issues that these DNN and SNN models may have during their execution, and offers a comprehensive section on benchmarking, explaining how to assess the quality of different networks and hardware systems designed for them.

**INDEX TERMS** Machine learning, ML, artificial intelligence, AI, deep learning, deep neural networks, DNNs, convolutional neural networks, CNNs, capsule networks, spiking neural networks, VLSI, computer architecture, hardware accelerator, adversarial attacks, data flow, optimization, efficiency, performance, power consumption, energy, area, latency.

#### I. INTRODUCTION

Artificial intelligence (AI) has become a fundamental pillar in many applications and systems in recent years. It is transforming the way we interact with technology, to the point

The associate editor coordinating the review of this manuscript and approving it for publication was Shiping Wen ...

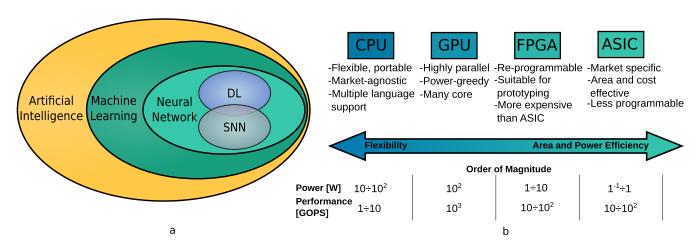

that, very often, we use it without even realizing it. Many techniques fall under the domain of AI, while one in particular raised among all, the Machine Learning (ML). In the last two decades, ML has been extensively employed in various application domains, thanks to the wide range of flexible and easy to learn statistical patterns. ML further consists of several subtopics, as shown in Figure 1. The most popular ones are the

<sup>&</sup>lt;sup>2</sup>Institute of Computer Engineering, Technische Universität Wien (TU Wien), 1040 Vienna, Austria

<sup>&</sup>lt;sup>3</sup>Division of Engineering, New York University, Abu Dhabi, United Arab Emirates

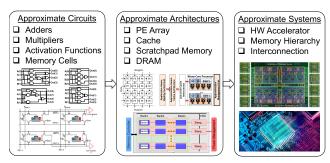

FIGURE 1. a) Artificial intelligence overview. b) Hardware platforms comparison [1].

brain-inspired models such as the Neural Networks (NNs), including the Spiking Neural Networks (SNNs) and the Deep Learning (DL) with Deep Neural Networks (DNNs).

DL shows superior accuracy, even claimed to exceed the human one in certain cases, e.g., in image classification and other problems of computer vision [2]. This is mainly enabled because of the two factors: (1) the computational power of the latest generation processors, and (2) the enormous amount of available data for training, from which DL can learn different patterns and can effectively derive certain predictions, using deeper and complex models. The larger the training dataset, the more and better the DL algorithms can learn and cover corner cases, achieving the performance never seen before. Since the training is a time-consuming task, effective hardware solutions are required to provide ready-to-use models within a reasonable time. This article mainly focuses on the hardware solutions related to those Deep Neural Networks (DNNs) that have captured much of the attention in the recent years, discussed in Section II. This article will also provide a brief overview of work on SNNs, which are becoming increasingly popular due to their similarities to the human brain and their energy-efficient computations. The applications that are already DL-based are numerous, and cover many key areas:

- Computer Vision: It is fundamental to extract meaningful features from video and pictures. Such tasks include object localization [3], image classification [4], and image segmentation [5]. Their use is valuable for controlling web traffic [6] or for example, video surveillance [7].

- **Business and Finance**: Financial techs deploy such models to forecast market behavior [8], including insurance [9] and lending [10].

- **Healthcare**: DL is widely used in cancer detection such as lung cancer [11], brain cancer [12], skin cancer [13], and many others are continuously rising. Moreover, there is also a wide applicability of DL techniques in the

- IoT-Healthcare use cases and Wearables, for instance, to derive short-term and long-term health predictions.

- **Robotics**: In robotics, DNNs served in a wide range of use cases like autonomous vehicles [14], humanoid robots [15], assistive robots [16], swarms [17], and drone control system [18].

- Smart Energy Management: DL can also be used to preserve valuable resources such as electricity. Indeed both managing [19] and forecasting [20] the required amount of energy consumption can lead to significant savings.

DNNs learn intelligent activities without the explicit hand-crafted guidelines of experts. Although DNNs, particularly CNNs and RNNs, represent the state-of-the-art in a wide range of applications, their increasing complexity demands for powerful hardware. Indeed, both inference and training processes require tens of billions of multiply-and-accumulate (MAC) operations that make these models extremely compute-intensive. Moreover, for each MAC, at least two input elements must be fetched from memory. As a result, performing these algorithms with minimal latency entails an additional critical constraint over the memory bandwidth.

For the reasons stated above, in many cases CPUs are not enough, therefore GPUs are one of the most appealing alternative to execute such complex models. However, today's trend is driven by the Internet-of-Things (IoT) [21] applications that require more computation capability near the sensors. This process of moving resources towards the IoT nodes is also known as edge computing [22]. This has become possible for two main reasons. Firstly the cost per silicon area has fallen to such an extent that the production of large scale devices to embed in IoT nodes is not an impediment anymore. Secondly, by performing on-site operations, it is no longer necessary to transmit the data to a central server, thus distributing the computing capacity reduces both latency and the large amounts of energy required for transmission,

as well as preserving the privacy of data of edge nodes. The mesh of these nodes is subjected to strict power constraints, indeed, many of them are battery-powered or rely on energy harvesting systems [23]. Therefore, the integration of a highend GPU into such a system is unfeasible since the required power would go far beyond the power envelope of the IoT-edge platforms.

In this scenario, DL algorithms need to be accelerated with alternative technologies such as low-power FPGAs, that are flexible and can be reprogrammed, or specialized accelerators in form of ASIC-IPs that are highly optimized and tailored for the application use case. This is also justified by the recent trend of integrated systems to move towards heterogeneous multicore systems (or heterogeneous multi-processor system on chip, MPSoCs) [24], which embed a mix of low-power general-purpose cores and specialized hardware accelerators. The flexibility of FPGA and ASIC designs (Figure 1b) opens up a whole series of possible hardware optimizations, analyzed in the following, that are required for energy-efficient acceleration of DL models. This work analyzes several hardware aspects that different platforms (CPU, GPU, FPGA, and ASIC) provide for the acceleration of DNN models with a comprehensive focus on dedicated accelerators. The latter, as explained before, gained much attention in recent years, thanks to their low-power and cost-effectiveness processing profile. Having a broad overview of the latest state-of-theart concepts and methodologies can be very valuable for designers.

Table 1 lists the acronyms used in this paper for a better understanding.

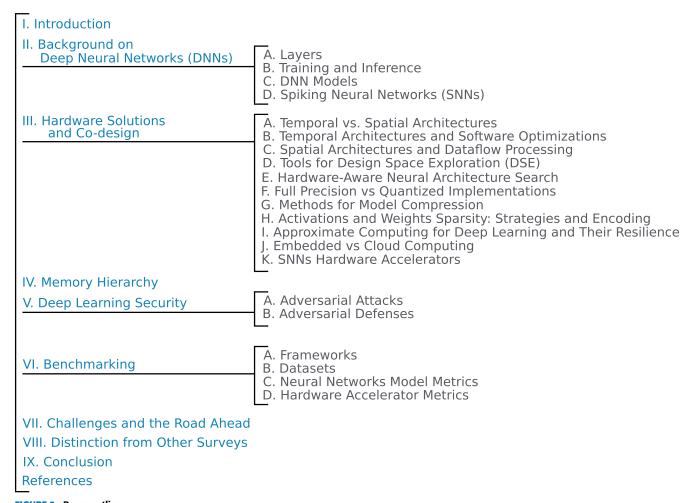

Paper organization: this survey paper is organized systematically in different sections and sub-sections, as depicted in Figure 2. Section II describes the background of DNNs and SNNs, describing the evolution of networks over the years and providing examples of DNN architectures considered the milestones of the DL. Section III analyses different co-design techniques to translate and map an efficient dataflow onto the hardware. Section IV outlines the characteristics of the memory hierarchy, being this an extremely power-greedy element. Section V presents the security issues related to ML models, providing examples on how to handle them. Section VI identifies the most important DL frameworks besides the datasets and the essential metrics to characterize both models and hardware devices. Section VII provides some hints about the research trends and future directions of ML and DL. Section VIII provides a description of related survey works, and our distinction. Finally, Section IX is reserved for the conclusion and summary.

#### **II. BACKGROUND ON DEEP NEURAL NETWORKS (DNNs)**

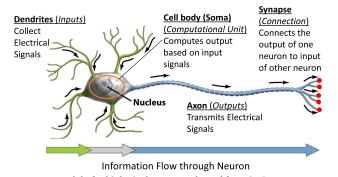

The constituent element of a neural network is the *neuron*, also called *perceptron*, a computational block that attempts to model the behavior of a biological neuron, which is shown in Figure 3.

A biological neuron consists of the cell body (soma), the dendrites and an axon [25]. The dendrites and the axon

**TABLE 1. List of Acronyms.**

| A    | Activation                                |  |

|------|-------------------------------------------|--|

| ΑI   | Artificial Intelligence                   |  |

| ASIC | Application Specific Integrated Circuit   |  |

| BC   | Binary Connect                            |  |

| BLAS | Basic Linear Algebra Subroutines          |  |

| BN   | Batch Normalization                       |  |

| BNN  | Binarized Neural Network                  |  |

| BWN  | Binary Weight Net                         |  |

| CIS  | Compressed Image Size                     |  |

| CNN  | Convolutional Neural Network              |  |

| Conv | Convolutional                             |  |

| CP   | Canonical Polyadic                        |  |

| CPU  | Central Processing Unit                   |  |

| CSC  | Compressed Sparse Column                  |  |

| CSR  | Compressed Sparse Row                     |  |

| DL   | Deep Learning                             |  |

| DNN  | Deep Neural Network                       |  |

| DRAM | Dynamic Random Access Memory              |  |

| FC   | Fully Connected                           |  |

| FFT  | Fast Fourier Transform                    |  |

| FM   |                                           |  |

| FPGA | Feature Map Field Programmable Gate Array |  |

|      | Generative Adversarial Network            |  |

| GAN  | Gradient Descent                          |  |

| GD   |                                           |  |

| GLB  | Global Buffer                             |  |

| GeMM | General Matrix Multiplication             |  |

| GPU  | Graphic Processing Unit                   |  |

| IFM  | Input Feature Map                         |  |

| IoT  | Internet-of-Things                        |  |

| LIE  | Loss                                      |  |

| LIF  | Leaky-Integrate-and-Fire                  |  |

| LIM  | Logic-in-Memory                           |  |

| MAC  | Multiply-and-Accumulate                   |  |

| ML   | Machine Learning                          |  |

| MSE  | Mean Squared Error                        |  |

| NAS  | Neural Architecture Search                |  |

| NN   | Neural Network                            |  |

| NoC  | Network-on-Chip                           |  |

| NPU  | Neural Processing Unit                    |  |

| OFM  | Output Feature Map                        |  |

| OS   | Output Stationary                         |  |

| PE   | Processing Element                        |  |

| QWN  | Quatized Neural Network                   |  |

| ReLU | Rectified Linear Unit                     |  |

| RF   | Register File                             |  |

| RLC  | Run Length Coding                         |  |

| RS   | Row Stationary                            |  |

| SIMD | Single-Instruction Multiple-Data          |  |

| SIMT | Single-Instruction Multiple-Threads       |  |

| SNN  | Spiking Neural Network                    |  |

| SRAM | Static Random Access Memory               |  |

| STDP | Spike Time Dependent Plasticity           |  |

| TPU  | Tensor Processing Unit                    |  |

| TTFS | Time To First Spike                       |  |

| TWN  | Ternary Weight Net                        |  |

| VLSI | Very Large Scale Integration              |  |

| W    | Weight                                    |  |

| WS   | Weight Stationary                         |  |

|      |                                           |  |

are filaments; the former receive stimuli, that are then processed by the soma, while the latter takes the neuron output signal to other neurons. Neurons are electrically excitable; when the input voltage exceeds a certain threshold, a pulse, called *action potential*, is generated on the axon. The neuron's response is *all-or-none*, i.e., the neuron can only have no response or full response depending on the input voltage value. The computational model adopted in artificial neural

FIGURE 2. Paper outline.

FIGURE 3. Model of a biological neuron, adapted from [25].

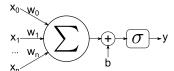

networks has been modified in time [26], [27] until reaching the configuration now adopted (Figure 4). In essence, it performs a weighted sum of all its inputs (Eq. 1), to which a bias term b is added to include a possible offset. The output of the neuron is then obtained applying a non-linear function  $\sigma(\cdot)$  (Eq. 2).

$$g(\mathbf{x}) = \sum_{n=0}^{N-1} \mathbf{x}[n]\mathbf{w}[n]$$

(1)

$$y = \sigma \left( g(\mathbf{x}) + b \right) \tag{2}$$

FIGURE 4. Model of an artificial neuron.

Artificial neural networks are constructed as directed graphs whose nodes represent the neurons. If the graph is acyclic, the network is a *feedforward* NN. If the graph is cyclic, the network is *recurrent* and has a temporal dynamic behavior.

As shown in Figure 5, the nodes are organized in layers: in a feedforward NN, each neuron of layer l receives its inputs from layer l-1 and sends its activation to the neurons of layer l+1. The inputs to the network form the *input layer*, and there is at least one layer that processes the input, which is called *output layer*. All the layers inserted between the input and output layers are defined as *hidden layers*. The number of hidden layers determines the *depth* of a neural network. If there are more than three hidden layers, the neural network is typically called a *Deep Neural Network*

a) Feedforward NN

b) Necurrent MM

FIGURE 5. Examples of (a) a feedforward NN and (b) a recurrent NN.

```

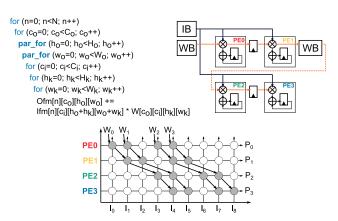

for (n=0; n<N; n++)

for (c<sub>0</sub>=0; c<sub>0</sub><C<sub>0</sub>; c<sub>0</sub>++)

for (c<sub>i</sub>=0; c<sub>i</sub><C<sub>i</sub>; c<sub>i</sub>++)

O[n][c_0] += I[n][c_i] * W[c_0][c_i]

```

FIGURE 6. Pseudocode of an FC layer.

FIGURE 7. Example of an FC layer (left) and of how it can be modeled by a vector-matrix multiplication (right).

(DNN) [28]. An NN learns how to solve different problems by finding the optimal values for the weights and the biases of its neurons, that can be organized and connected in different ways, as discussed in the following section.

#### A. LAYERS

## 1) FULLY CONNECTED (FC) LAYERS

In a Fully Connected layer, each neuron of layer l receives as inputs all the activations of layer l-1, therefore, each output neuron performs a weighted sum of all the input neurons:

$$\mathbf{O}[c_o] = \sum_{c_i=0}^{C_i-1} \mathbf{W}[c_o, c_i] \mathbf{I}[c_i] + \mathbf{b}[c_o]$$

$$0 \le c_o < C_o, \quad 0 \le c_i < C_i$$

where  $C_i$  and  $C_o$  are the number of neurons of layers l-1 and l respectively. Figure 6 shows the pseudocode that implements an FC layer. In Figure 6 N is the *batch size*, where a *batch* is a collection of inputs that can be processed in parallel.

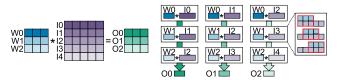

From the equation and the pseudocode that describes it, it is possible to see that an FC layer is a vector-matrix multiplication with the weights arranged in a  $C_i \times C_o$  matrix (see Figure 7).

Since  $C_i$  and  $C_o$  can assume high values, the number of parameters of an FC layer is potentially huge. However, it is not always necessary for an output neuron to receive information from all the input neurons. For this reason, Convolutional layers have been introduced.

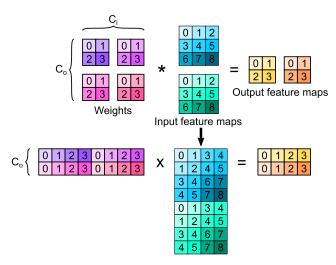

#### 2) CONVOLUTIONAL (CONV) LAYERS

FC layers are not well suited for tasks like object detection and recognition since their high degree of connectivity leads to an explosion of the number of parameters required to deal with high-resolution images. Moreover, FC layers treat inputs that are close together or far apart equivalently, ignoring the spatial structure present in images. To overcome these two problems, in 1998 a new architecture was proposed [29], known as Convolutional Neural Network (CNN), that includes Conv layers and exploits the ideas of local receptive fields and shared weights. The idea of local receptive fields has its biological counterpart in the study of David H. Hubel and Torsten Wiesel [30] on the visual cortex of a cat. They demonstrate that some neurons are activated when the cat is visually exposed to vertical lines, while different neurons respond to lines oriented along different angles. There are thus locally sensitive neurons that are sensitive to a small portion of the visual field and higher-level neurons that are sensitive to larger portions and therefore analyze more complex patterns. Adapting the same idea to a neural network, the neurons are organized in a 2D grid, i.e., a *feature map*, and a neuron of layer l does not receive all the activations of the layer l-1, but it is instead connected to a small receptive field of dimension  $[H_k \times W_k]$ . The size of the receptive field and consequently of the weight matrix is commonly referred to as kernel size and the distance between adjacent receptive fields is defined by a stride parameter S. Applying the idea of shared weights, all the neurons of layer l have the same matrix of weights, detecting the same feature in different locations of layer l-1. To detect multiple features, a Conv layer has multiple channels, i.e., there are multiple feature maps.

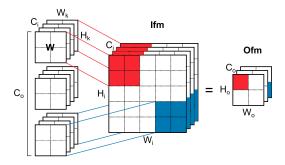

The computations performed in a Conv layer involve an *input feature map* **Ifm** of size  $[C_i \times H_i \times W_i]$ , the *weights* **W** of size  $[C_i \times C_o \times H_k \times W_k]$ , and a *bias term* **b** of size  $[C_o]$ . The result of the computation is an *output feature map* **Ofm** of size  $[C_o \times H_o \times W_o]$ , computed as follows:

$$\mathbf{Ofm}[c_{o}, h_{o}, w_{o}] \\

= \sum_{c_{i}=0}^{C_{i}-1} \sum_{h_{k}=0}^{H_{k}-1} \sum_{w_{k}=0}^{W_{k}-1} \\

\times \left( \mathbf{W}[c_{i}, c_{o}, h_{k}, w_{k}] \mathbf{Ifm}[c_{i}, Sh_{o} + h_{k}, Sw_{o} + w_{k}] + \mathbf{b}[c_{o}] \right) \\

0 \le c_{o} < C_{o}, \quad 0 \le h_{o} < H_{o}, \quad 0 \le w_{o} < W_{o} \\

0 \le h_{k} < H_{k}, \quad 0 \le w_{k} < W_{k}$$

Figure 8 shows the pseudocode of a Conv layer, and Figure 9 gives a graphical representation.

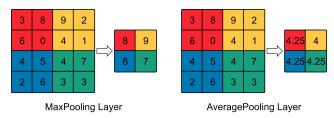

#### 3) POOLING LAYERS

Pooling layers are commonly placed after a Conv layer. Pooling layers have receptive fields, similarly to Conv layers. For the group of neurons in each receptive field, they return a single value that contains a statistic of the group, e.g., the maximum or the average value, as shown in Figure 10.

```

\begin{split} &\text{for } (n=0; \, n < N; \, n + +) \\ &\text{for } (c_0 = 0; \, c_0 < C_0; \, c_0 + +) \\ &\text{for } (c_i = 0; \, c_i < C_i; \, c_i + +) \\ &\text{for } (h_0 = 0; \, h_0 < H_0; \, h_0 + +) \\ &\text{for } (w_0 = 0; \, w_0 < W_0; \, w_0 + +) \\ &\text{for } (h_k = 0; \, h_k < H_k; \, h_k + +) \\ &\text{for } (w_k = 0; \, w_k < W_k; \, w_k + +) \\ &\text{Ofm}[n][c_0][h_0][w_0] \ += \\ &\text{Ifm}[n][c_i][h_0 + h_k][w_0 + w_k] \ ^* \, W[c_0][c_i][h_k][w_k] \end{aligned}

```

FIGURE 8. Pseudocode of a Conv layer.

FIGURE 9. Graphical representation of the convolution operation in a Conv layer. A sub-tensor of Ifm (red) is multiplied by a sub-tensor of W and the results are accumulated to produce a single value (red) of the Ofm.

FIGURE 10. Examples of MaxPooling (left) and AveragePooling (right) layers.

The stride parameter is usually set equal to the dimension of the receptive field to have non-overlapping windows.

Pooling layers reduce the number of activations of a layer, and consequently decrease the memory requirements and the number of computations to be performed after. Moreover, pooling layers achieve invariance to small local translations. The outputs of Conv layers depend heavily on the position of the input, so even for minor variations of the inputs, there are significant variations of the outputs. Pooling layers downsample the outputs, making them more robust to small input variations.

#### 4) NORMALIZATION LAYERS

The inputs to neural networks are usually preprocessed to have a normal distribution, i.e., zero mean and unit variance. Normalization is beneficial because it keeps different inputs in the same range of values, making them easier to analyze by the same model. Also, as will be seen in the following paragraph, layers sometimes use saturating non-linear functions, such as Sigmoid or Softmax. So having values centred on

zero avoids early-saturation of activations. To apply the same normalization constraint that applies to the inputs to internal activations, Normalization layers are inserted between Conv and FC layers. It must also be noted that activations normalization speeds up the training, as the layers do not need to adapt to different distributions at each training step.

The commonly adopted normalization method is Batch Normalization (BatchNorm) [31] (Eq. 3). The operation performed by the BatchNorm layer is standardization:

$$y = \frac{x - E[x]}{Var[x] + \epsilon} \cdot \gamma + \beta \tag{3}$$

where E[x] and Var[x] are the mean and standard deviation of the input tensor x, respectively.  $\epsilon$  is a value necessary for numerical stability, and  $\gamma$  and  $\beta$  are two trainable parameters for the integration of the BatchNorm layer in the training process.

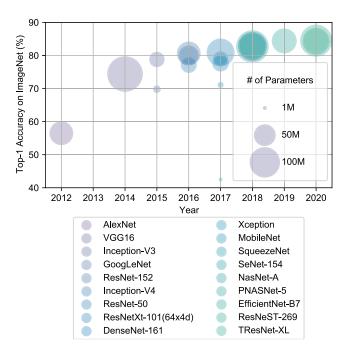

#### 5) NON-LINEAR ACTIVATION FUNCTIONS

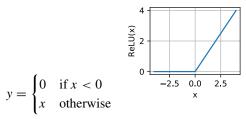

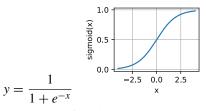

Without a non-linear activation function, the NN would be a simple cascade of linear algebra operations, unable to solve complex non-linear problems. For this reason, different non-linear functions are applied to the weighted sum of the inputs of a neuron. Some of the most popular functions are:

• Rectified Linear Unit (ReLU) function forces the activations to be greater than or equal to zero. It is prevalent as it is computationally efficient since it requires a simple comparison between x and 0.

There are some variants of the ReLU function, such as Leaky-ReLU or  $Exponential\ Linear\ Unit\ (ELU)$ . The former has a negative slope for values x < 0; the latter uses a log curve when x < 0. These variants have been introduced to solve the  $dying\ ReLU$  problem, i.e., since the slope of the ReLU for x < 0 is zero, the neurons in this region are not trained. Moreover, Leaky-ReLU and ELU are more balanced towards zero if compared to ReLU, and this helps to speed up the training.

• Sigmoid function normalizes the output in the range (0, 1). Contrarily to the ReLU function, it is computationally expensive, as it can be seen from its equation:

• Hyperbolic Tangent function (TanH) is the equivalent of Sigmoid function to bound activations in the range

(-1, 1), to model outputs that can assume negative values too.

• Softmax function is also know as normalized exponential function. It receives a vector of N numbers as an input: each number is normalized in the range (0, 1) and the sum of all N numbers is equal to 1. This function is used mainly in output layers if the outputs represent the classification probabilities.

$$y_i = \frac{e^{x_i}}{\sum_{j=0}^{N-1} e^{x_j}}$$

for  $i = 0, 1, ..., N-1$

#### **B. TRAINING AND INFERENCE**

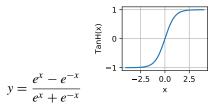

A neural network can learn to solve a problem by determining the correct values of the weights and biases of its layers: this process is referred to as *training*. Using a trained NN, with pre-learned weights and biases, is referred to as *inference*. There are different ways of training a NN (see Figure 11):

**Supervised learning:** It requires a set of labeled inputoutput pairs, i.e., a set of inputs (*data*) with the corresponding expected output (*labels*). This set of pairs is called a *training set*. During the supervised learning, the model receives a labeled input and updates its parameters based on the discrepancy between the expected output and the actual output. Supervised learning is predominantly used today in a wide range of applications, in the big-data era, thanks to the immense availability of datasets and its good performances.

**Unsupervised learning:** It is performed when only non-labeled data are available. It lies in finding common patterns in the data. An example of unsupervised learning is *clustering*, that clusters data based on their shared attributes. Neural networks that apply unsupervised learning are, for example, *autoencoders* and *Generative Adversarial Networks* (GANs).

Reinforcement learning: Reinforcement learning is the third main type of learning and, similar to the unsupervised learning, it does not need labeled data. The aim of reinforcement learning is the creation of autonomous agents able to make decisions in a given environment. The training scenario is composed of the agent who takes actions in an environment. There is then an interpreter who evaluates the agent's actions in terms of a reward, which is then fed back to the agent. The goal of the agent is to maximize the reward.

A supervised-learning algorithm commonly used for the training of DNNs is *gradient backpropagation*, where the input samples are fed into the network, and the outputs are computed using weights **W**. The network's outputs and

FIGURE 11. Features, achievable tasks and applications of the three existing ways of training (supervised, unsupervised, and reinforcement).

expected outputs are compared, and a loss (L) is calculated with a loss function, such as Euclidean distance or Mean Squared Error (MSE). To perform the learning process, the weights are updated by a quantity proportional to the partial derivative of the loss with respect to the weights themselves, i.e., the gradient. The gradients are efficiently computed with the backpropagation algorithm, which is the *chain rule* of calculus applied to calculate the derivative of the loss starting from the output of the network and going up to the input layer.

The learning actually takes place by updating the weights and biases of the network, which can be done with different *optimization algorithms*. The simplest optimization algorithm is gradient descent (GD), shown in Eq. 4, where  $\theta$  is a parameter of the network and  $\eta$  is a scaling factor referred to as *learning rate*. Other algorithms are, e.g., GD with momentum [32], Nesterov accelerated gradient [33], Adagrad [34], Adadelta [35] and Adam [36].

$$\theta^{t+1} = \theta^t - \eta \frac{\partial L}{\partial \theta^t} \tag{4}$$

During the training of neural networks it is common to encounter the problem of *overfitting*, i.e., if a model is complex and has many parameters, it is possible that it fits the data of the training set too accurately. The model therefore "memorizes" the correct result for each input rather than learning to generalize, and has a poor performance on the inputs that are never seen before. The solutions to the overfitting problem are either the transition to a simpler model or employing different *regularization techniques*. L1 and L2 [37] are common regularization techniques, both require adding a regularization term to the loss function, which has the effect of reducing

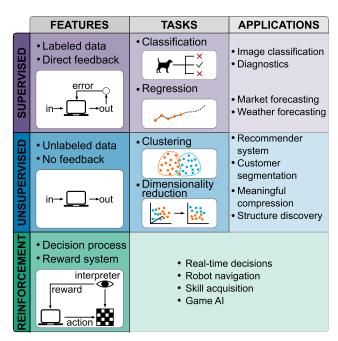

FIGURE 12. Timeline of significant neural networks models with the accuracies achieved on the ImageNet dataset [39] and the number of parameters.

the value of the weights. This results in a compressed and simpler model. Another technique that gives good results is *dropout* [38], i.e., at each iteration some neurons are randomly selected and removed from the model.

#### C. DNN MODELS

Over the years, many CNNs models have been proposed to achieve better to the best-possible performance for a given task. Figure 12 shows a timeline of significant neural network models with their classification accuracy in the image classification task on the ImageNet dataset [39] and number of parameters. These models will be discussed in the following paragraphs and compared in Table 2.

#### 1) LeNet [29] (1998)

It has been one of the first neural network trained by back-propagation with a convolutional structure and has been the inspiration for the following research on CNNs. It was designed for the recognition of handwritten digits represented on  $32 \times 32$  pixels images. LeNet-5 is a version consisting of five layers, of which the first two are convolutional layers, and the last three are FC layers. The Conv layers have  $5 \times 5$  kernels and are both followed by  $2 \times 2$  average pooling layers. All the layers use hyperbolic tangent (tanh) as the activation function, except the output layer that applies the softmax function.

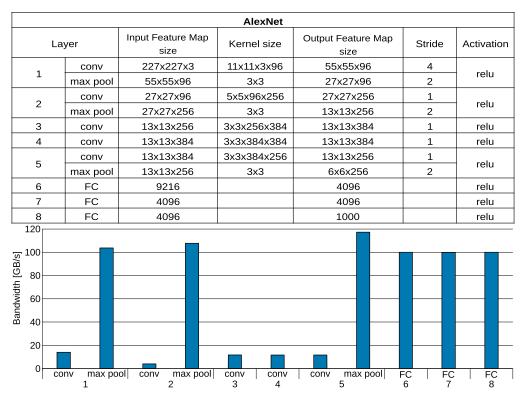

# 2) AlexNet [40] (2012)

It is a CNN built for the ImageNet dataset [39], a database of more than 1.3M of high-resolution  $256 \times 256$  pixels images divided into 1000 classes. It is the first (deep) CNN

TABLE 2. Comparison of the models presented in Section II-C.

| M - J - 1                   | <b>X</b> 7 | C4:14:                        |  |  |  |

|-----------------------------|------------|-------------------------------|--|--|--|

| Model                       | Year       | Contribution                  |  |  |  |

| LeNet [29]                  | 1998       | -First popular CNN            |  |  |  |

| AlexNet [40]                | 2012       | -First CNN winner of ILSVRC   |  |  |  |

| Alexinet [40]               |            | -Introduction of ReLU         |  |  |  |

| VGG16 [42]                  | 2014       | -Smaller kernels              |  |  |  |

| GoogLeNet [43]              | 2015       | -Inception block              |  |  |  |

| ResNet [44]                 | 2016       | -Skip connections             |  |  |  |

| . ,                         | 2010       | -Residual learning            |  |  |  |

| ResNetXt-                   | 2017       | C                             |  |  |  |

| ResNetXt-<br>101_64x4d [45] | 2017       | -Grouped convolution          |  |  |  |

| DenseNet161 [46]            | 2017       | -Regular structure            |  |  |  |

| CapsNet [47]                | 2017       | - Capsules                    |  |  |  |

| Capsiver [47]               | 2017       | - Dynamic Routing             |  |  |  |

| SeNet154 [48]               | 2018       | -Dependencies between feature |  |  |  |

| Serven 34 [40]              |            | maps are exploted             |  |  |  |

| NasNet-A [49]               | 2018       | - Neural Architecture Search  |  |  |  |

| masmet-A [49]               |            | - Transfer learning           |  |  |  |

architecture to win the ImageNet Large Scale Visual Recognition Challenge 2012 (ILSVRC-2012) [41], achieving consistent accuracy improvements compared to the traditional non-convolutional networks winners of the previous editions. AlexNet follows the architecture of LeNet, stacking more Conv layers; it consists of five Conv layers and three FC layers. AlexNet was the first NN to introduce Rectified Linear Units (ReLU) as the activation functions, reducing the training time significantly. Moreover, to overcome the limitations imposed by the memory size of the GPUs, AlexNet adopts a parallel solution, splitting the architecture on two GPUs. To reduce the communication bottleneck, the GPUs exchange data in two points of the network only.

#### 3) VGG [42] (2014)

Thanks to the availability of hardware resources supporting heavier computations, the initial trend in NN research has been the design of deeper and deeper architectures. VGG is a model that takes the structure of AlexNet and furtherly increases the number of Conv layers. In particular, VGG-16 has 13 Conv layers and three FC layers, while VGG-19, with a total of 19 layers, was the winner of ILSVRC-2014.

#### 4) GoogLeNet [43] (2015)

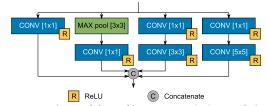

It is based on the intuition of finding a dense structure, i.e., an inception module, and then building the network by stacking these modules. An inception module (see Figure 13) captures features at various scales and concatenates them at the output, passing to the next layer different levels of information. The increase of the depth of the NNs has allowed to improve their accuracy but has however led to the appearance of the *vanishing gradient problem*. Since during backpropagation the gradients are computed with the chain rule and the values are often in the range [0, 1] or [-1, 1], the magnitude of the gradients decreases exponentially with the depth of the network. In the earlier layers, the gradients can become so small that they prevent the correct training. To overcome

FIGURE 13. Inception Module used in GoogLeNet [43]. Convolutions are performed in four parallel branches and the four outputs are concatenated to produce the single output of the Inception module.

FIGURE 14. Skip connection modules used in Residual Networks [44]. Three convolution are performed in series and a parallel connection is added. In the parallel connection, it is possible to choose between a 1  $\times$  1 convolution (left) or the identity function, i.e., no operation (right). The results of the two branches are summed.

FIGURE 15. Dense blocks used in DenseNets [46]. The output and input of each blue block, that is the series of two convolutions, are concatenated.

this problem, GoogLeNet has two additional classifiers used for training only that take the activations at earlier stages of the network, and therefore increase the magnitude of their gradients. GoogLeNet successors are Inception-v3 [50] and Inception-v4 [51].

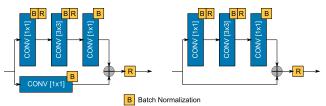

#### 5) ResNet [44] (2015)

To work around the vanishing gradients problem, Residual Networks (ResNets) have adopted and made popular *skip connections*, shown in Figure 14, that run in parallel to a series of Conv layers and avoid excessive degradation of the gradients during backpropagation. Moreover, ResNets are the first architectures to use batch normalization layers. Based on ResNet architecture, different models with higher accuracies have been proposed over the years, such as ResNetXt [45], ResNeST [52], or TResNet [53].

#### 6) DenseNet [46] (2016)

Given the success of skip connections, DenseNets adopt a regular and therefore simpler connection pattern. As shown in Figure 15, in a Dense Block, every layer receives in input a concatenation of the activations of all the preceding layers. A DenseNet is then built by stacking Dense Blocks of different depth, interleaved by Conv and Pooling layers for dimensionality reduction.

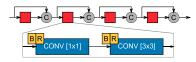

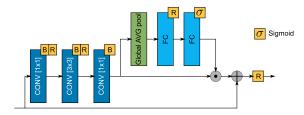

# 7) SENet [48] (2017)

Squeeze-and-Excitation Networks (SENets) modify traditional layers, e.g., Conv layers, or blocks, e.g., incep-

FIGURE 16. Residual module as modified in Squeeze-and-Excitation Networks [48]. A skip connection is inserted in parallel to a pooling and two FC layers, and the output of the two branches are multiplied. As in traditional residual modules, a skip connection runs in parallel to the whole block.

FIGURE 17. Capsule Network [47].

tion or residual modules, to model the relationship between the different channels of the feature maps. Figure 16 shows how a residual module is modified following the SE approach. SENet-154 is the NN winner of ILSVRC-2017, which is built integrating SE blocks in a version of ResNetXt [45].

#### 8) CAPSULE NETWORK (2017)

The Capsule Networks were created in a try to solve some of the problems of CNNs, such as the loss of data caused by pooling layers or the high sensitivity to input shifts or rotations. The idea of *capsules* was introduced in [54] and the first network model was proposed in [47]. In [47], the neurons are replaced by capsules, i.e., a vector of neurons. Each element of the vector encodes an instantiation parameter of an entity, e.g., the width or the rotation, and the length of the vector represents the instantiation probability of the entity. Since the length of the vector represents a probability, its value must be in the range [0, 1]. For this reason, the *squash* function (Eq. 5) is used as non-linear activation function in the capsule layers.

$$\vec{y} = \frac{|\vec{x}|^2}{1 + |\vec{x}|^2} \frac{\vec{x}}{|\vec{x}|} \tag{5}$$

Moreover, in Capsule Networks, the pooling layers are substituted by a *dynamic routing algorithm* that strengthens the connections between capsules of adjacent layers if relevant entities are detected. Figure 17 shows the Capsule Network model as proposed in [47]. The work in [55] proposes instead a model in which the values of the capsules are arranged in matrices, and the dynamic routing is substituted by the *EM routing*.

# 9) NASNet [49] (2018)

NASNet is the first popular neural network model obtained with neural architecture search. The approach of NasNet is the search of a cell for a simple dataset in a small search

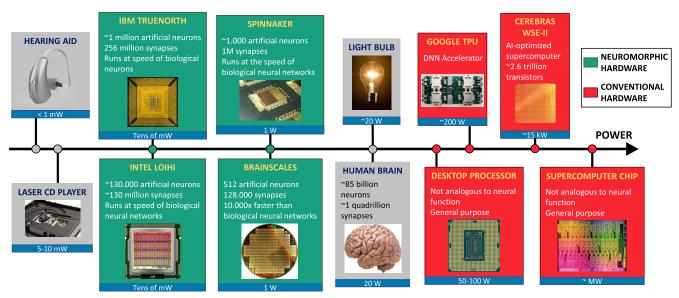

FIGURE 18. Comparison of power consumption between conventional hardware architectures and neuromorphic architectures.

space. The cells can then be stacked to work on more complex datasets. Other models resulting from neural architecture search are PNASNet-5 [56] and EfficientNet [57].

#### D. SPIKING NEURAL NETWORKS (SNNs)

Recently, Spiking Neural Networks (SNNs), considered as the third generation of neural networks [58], have received an increasing interest in the fields of deep learning and neuroscience, because of their extremely energy-efficient nature. SNNs, in contrast to the traditional DNNs, base their computational models much closer to that of the biological neurons, with a spike-based communication mechanism [59]. Due to their bio-inspired computations, SNNs bear a high potential to be the most promising solution for bridging the energy efficiency gap between the artificial machines and the human brain. A custom SNN hardware support is provided by neuromorphic computing, a relatively novel branch of computer architecture. The underlying goal is to reproduce in hardware the same computations that are executed in the human brain. Some examples of state-of-the-art neuromorphic designs, like IBM TrueNorth [60], SpiNNaker [61], BrainScale [62] and Intel Loihi [63], will be discussed in Section III-K. Figure 18 compares several hardware architectures, showing how efficient in terms of power consumption are neuromorphic solutions, compared to conventional designs [64]. Moreover, another energy efficiency benefit in the neuromorphic research comes from the new sensor data formats. For instance, the event-based sensors such as the dynamic vision sensor (DVS) cameras [65] resemble the behavior of the human retina, in such a way that spikes are generated only when movements of the recorded subjects are detected.

#### 1) SPIKING NEURON MODELS

Modeling a spiking neuron is a challenging task. These models must be at the same time biologically accurate and computationally simple. When an input spike arrives to the

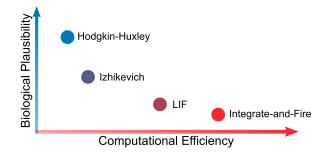

FIGURE 19. Comparison of different spiking neuron models.

neuron, the associated synaptic weight  $w_i$  is integrated on the membrane and, consequently, the neuron membrane potential  $V_m$  is increased. When the membrane potential overcomes a threshold  $V_t$ , the neuron fires, emitting a spike at the output, and its membrane potential is reset to a value  $V_R$ . Moreover, the membrane potential decreases continuously through time due to a leakage, according to a leak rate  $\tau_m$  between spikes.

Different spiking neuron models have been proposed in the literature. Figure 19 shows the trade-off between biological plausibility and complexity of these models. The Hodgkin-Huxley model [66] is very biologically-plausible, but extremely computational intensive. The Izhike-vich model [67] is slightly less complex, but still very computational intensive. On the other end, the Integrate-and-Fire is too simple and not very accurate in terms of biological plausibility. The most commonly adopted model is the Leaky-Integrate-and-Fire (LIF) [68], which is relatively simple and also takes into account the membrane leakage.

## 2) SPIKE ENCODING

In order to provide input spikes and to collect the resulting output spikes of the SNN, the information has to be properly

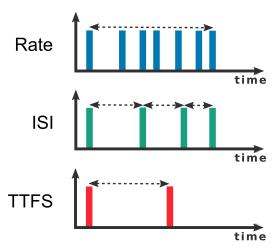

FIGURE 20. Comparison between Rate, Inter-spike interval (ISI), and Time to first spike (TTFS) encoding techniques for SNNs.

coded using spikes. Different approaches used to obtain such a conversion [69] are shown in Figure 20:

- **Rate coding**: the information is coded as the mean firing rate of the generated spikes in a defined observation period.

- Inter-spike interval (ISI): the intensity of the activation is coded as the precise delay between consecutive spikes.

- Time to first spike (TTFS): the information is encoded in the latency that goes from the beginning of the stimulus to the time of the first output spike. This solution enables a very fast information processing, carrying enough information.

#### 3) SNN TRAINING

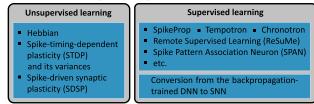

Regarding the SNN training algorithm, the different possibilities have been explored are summarized in Figure 21. For unsupervised learning, the possible algorithms are Hebbian Learning [70], the **Spike-Time-Dependent Plasticity** (**STDP**) [71], [72], and the Spike-Driven Synaptic Plasticity (SDSP) [73]. The most widely adopted method is the STDP, which is based on temporal relations between the *presynaptic* spikes (at the input of the neuron) and the *postsynaptic* spikes (at the output of the neuron). Basically, the synaptic weight is tuned accordingly to the temporal correlation between the presynaptic and postsynaptic spikes. The STDP algorithm can be optimized through the FSpiNN framework [74], for executing energy-efficient SNNs on edge devices.

For supervised learning, a fundamental challenge arises, because the traditional learning method, i.e., the backpropagation, cannot be applied due to the non-differentiability of the SNN loss function [75]. Hence, two different procedures can be adopted to solve or bypass the problem, thereby achieving supervised learning for SNNs:

1) Approximate the derivative of the spike trains. This solution has been extensively studied in the works of [76], [77] [78], [79] [80], [81] [82], [83] [84], [85], which provide different types of approximations.

#### **Training in Spiking Neural Networks (SNNs)**

FIGURE 21. Training techniques for SNNs.

The advantage is that the network can learn based on the temporal information of the spikes. For example, DECOLLE [86] introduces a local learning rule for continuous SNN learning. On the other hand, with this approach it is challenging to match the consolidated state-of-the-art high accuracy results of the DNNs.

2) Train a DNN offline and convert it to SNN. This approach [87] allows to use the most advanced training policies and techniques for DNNs. An efficient conversion [88] requires a comprehensive study of different conversion parameters to adapt the DNN-to-SNN conversion process to the neuromorphic hardware platform. The main drawback is that a certain accuracy drop is encountered during the conversion. To overcome this, the recent work of [89] proposed a hybrid approach consisting of converting the DNN to SNN ad then incrementally training the SNN with an approximated backpropagation. Moreover, the max pooling operations cannot be implemented with spike rates [90]. Therefore, max pooling layers are replaced by average pooling, which is easy to implement but shows an accuracy drop.

#### III. HARDWARE SOLUTIONS AND CO-DESIGN

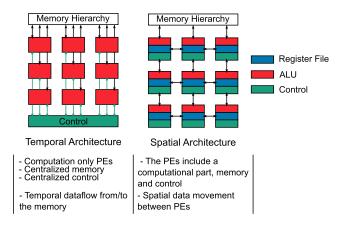

#### A. TEMPORAL VS SPATIAL ARCHITECTURES

Neural networks are a class of algorithms with an inherent parallelism. Two types of parallelism can be identified [91]. The neuron and consequently the FC and Conv layers have a *topological parallelism* since the Multiply-and-Accumulate (MAC) operations that they perform have no data dependencies and can be executed in parallel. Moreover, the training sets consist of a large number of samples, that rather than being processed one at a time can be fed into the network in batches (*operational parallelism*).

The intrinsic parallelism of the layers can be exploited using parallel computing paradigms to increase the performance of the hardware implementations of NNs. Among the various solutions for parallel computation, temporal and spatial architectures [92] are distinguished. Both the architectures consist of a large number of Processing Elements (PEs) that perform operations in parallel on the same or different data. In temporal architectures, the PEs can only access data from the central memory, the control is centralized, and there are no inter-PEs connections. In spatial architectures, on the contrary, each PE can also have its control

FIGURE 22. Basic models of temporal (left) and spatial (right) architectures.

logic and one or more local memory locations. Most importantly, in spatial architectures, the PEs are interconnected to exchange data with each other, creating a processing array. Figure 22 shows the differences between temporal and spatial architectures.

In the following, subsections III-B and III-C describe temporal and spatial architectures in detail respectively, and how to efficiently deploy neural networks on them.

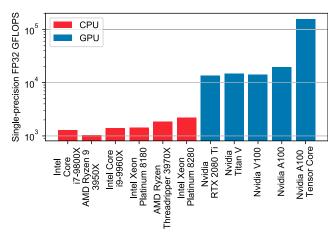

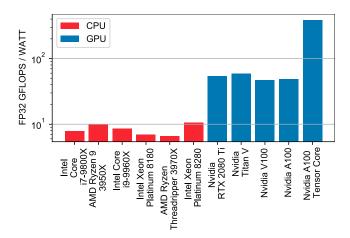

# B. TEMPORAL ARCHITECTURES AND SOFTWARE OPTIMIZATIONS

Temporal architectures are commonly adopted in generalpurpose platforms, such as CPUs and GPUs. CPUs can nowadays be realized as vector processors (e.g., Intel's Xeon Phi x200 and Skylake-X CPUs) with an ability of working with multiple data elements simultaneously rather than with a single data at a time. Vector processors have multiple Arithmetic Logic Units (ALUs) that work synchronously and perform an instruction on a vector of data. Therefore, vector processors use the Single-Instruction-Multiple-Data (SIMD) technique. Among the available hardware platforms, CPUs are often the least used for DNNs inference or training, as they provide lower FLOPS and FLOPS/WATT performance (see Figures 23 and 24). However, manufacturers have recently undertaken measures to accelerate the deployment of NNs on CPUs. For example, at the instruction level, Intel has added the AVX-512 Vector Neural Network Instructions (AVX-512 VNNI) to the AVX-512 Instruction Set [93] to accelerate CNNs. In addition, Intel announced that the next generation of Cooper Lake and Sky Lake processors will support Brain Floating Point (bfloat16) operations [94]. bfloat16 is a floating-radix-point format on 16 bits with a dynamic range comparable with the dynamic range of the 32-bit IEEE 754 floating-point format. *bfloat16* is also supported by ARMv8.6-A and AMD's ROCm library. Intel has also created BigDL [95], an ML library for the distributed acceleration of DNN algorithms on CPU clusters.

GPUs are manycore architectures with up to thousands of cores that are specifically designed for parallel computation

FIGURE 23. GFLOPS comparison between different CPUs and GPUs.

FIGURE 24. GFLOPS/WATT comparison between different CPUs and GPUs.

(e.g., 5120 cores in Nvidia V100 GPU [96]). Similarly to vector CPUs, GPUs adopt the Single-Instruction-Multiple-Thread (SIMT) execution model, first introduced by Nvidia. The SIMT model executes a single instruction simultaneously on multiple cores. Each core receives a different data that belongs to multiple threads running in parallel. GPUs are the real workhorses for DNNs training in particular, and in certain cases for inference as well. Among the various GPU manufacturers, Nvidia has put a lot of emphasis on GPU hardware and software optimization for DL. Most DL frameworks support the execution on Nvidia GPUs, e.g., Pytorch [97], Tensorflow [98], or Caffe [99]. One of the great advantages of Nvidia GPUs is cuDNN [100], a highly optimized library of primitives for DNNs. cuDNN is not the only library for DL, rather all Nvidia libraries for DNN/ML are collected in CUDA-X AI [101]. In the latest high-end GPUs, Nvidia has combined traditional CUDA Cores with Tensor Cores [96], which are optimized for large matrix operations. Tensor Cores can also support mixed-precision operations. In the new Nvidia A100, the Tensor Cores support a new format, the Tensor Format (TF32), with which performance is 10x higher when compared to the performance of the

FIGURE 25. Discontinuity in memory accesses when performing convolution on a matrix stored by rows.

FP32 format on the V100 architecture [102]. In addition, Nvidia A100's Tensor Cores can also take advantage of the sparsity of tensors, very common in DNNs, to achieve up to 2x higher performance.

At the software level, several libraries have been created to optimize *Basic Linear Algebra Subroutines* (BLAS) on both CPUs (e.g., AMD Core Math Library (ACML), Intel Math Kernel Library (Intel MKL) or OpenBLAS) and GPUs (e.g., Nvidia cuBLAS or Intel cIBLAS). Among the numerous subroutines implemented, the BLAS also include element-wise matrix multiplication, matrix-vector multiplication and matrix-matrix multiplication, also called General Matrix Multiplication (GeMM). For what concerns neural networks the BLAS come in hand for the FC layer that, as explained in Section II-A, can be seen as a vector-matrix multiplication or as a matrix-matrix multiplication in case of batched computation.

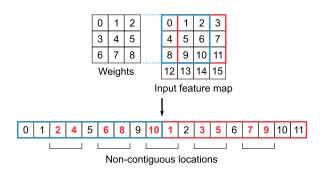

Optimizing the computation of the Conv layers is a more challenging task. The operations between a weight kernel and the subsets of the input feature maps are simple point-wise multiplications of matrices, but the memory access pattern is complex. Figure 25 shows how, if an input feature map is stored by rows, it is necessary to perform accesses to noncontiguous locations of memory.

Several computational transforms have been proposed to apply the optimized BLAS to Conv layers. Many of the software libraries mentioned above lower the convolution into a GeMM as proposed in [103], [104] and shown in Figure 26. A 4D-tensor of weights is flattened to a 2D matrix, while the data in the input feature maps are duplicated and rearranged following a pattern that leads to the correct result of a convolution by performing a matrix multiplication. This method is very efficient since the GeMM routine is highly optimized. However, it requires data to be duplicated up to  $H_k \times W_k$  times, with the dimension of the input feature maps moving from  $C_i \times H_i \times W_i$  to  $C_i H_k W_k \times H_o W_o$ . This approach, therefore, requires a large memory for temporary allocation.

The GeMM method for convolution can further be optimized by applying the Strassen algorithm [105], [106] that reduces the number of necessary multiplications by partitioning the matrices. The number of multiplications is reduced

FIGURE 26. Convolution lowering: mapping a convolution to a matrix-matrix multiplication by rearranging the matrices.

of 1/8 at each partition, at the cost of a higher number of additions.

A different approach consists of transforming both the input feature maps and the weights from the space domain to the frequency domain with the FFT algorithm [107]. In the frequency domain, the convolution operation becomes an element-wise multiplication of matrices. However, the FFT algorithm introduces a high computational overhead for the domain change, and its efficiency has only been proven valid for large weight kernels and unitary strides. Another approach often used is based on the Winograd algorithm [108], [109], which, unlike the FFT algorithm, is particularly efficient for small kernels.

Direct convolution can also be performed exploiting the parallel hardware solutions offered by modern CPUs and GPUs. In [110] and [111] it is shown how to rearrange the tensors to have more efficient memory accesses, and how to perform operations to take full advantage of Intel AVX-512 [93] vector instructions.

# C. SPATIAL ARCHITECTURES AND DATAFLOW PROCESSING

Spatial architectures are commonly implemented on FPGAs and ASICs, that allow for a design tailored on specific applications at the price of less flexibility. Neural networks are particularly suitable for this kind of hardware implementation since the type and order of operations of each layer is fixed and known a priori. Therefore, it is possible to develop specialized and highly optimized circuits.

The operations carried out in the neural networks are simple, mostly multiply-and-accumulate (MACs), but they must be performed on a large set of data. Therefore, the bottleneck is not caused by computation but by the memory accesses that are necessary to fetch and store the inputs and the results, respectively. Every MAC requires three data elements to be read from memory (input pixel, weight and partial

FIGURE 27. Energy breakdown of two state-of-the-art DNNs accelerators.

FIGURE 28. (left) General structure of a hardware accelerator for DNNs and (right) interconnection scheme.

sum) and one data element to be written (updated partial sum). It has been demonstrated that a DRAM access has an energy cost of  $\sim 2$  orders of magnitude higher than a MAC operation [112]. The enormous DRAM access energy cost compared to the computational energy has been observed in many state-of-the-art DNNs accelerators such as Dian-Nao [24] or Cambricon-X [113] (Figure 27).

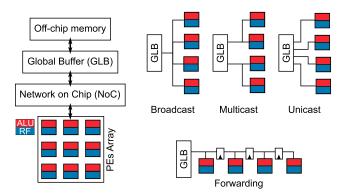

A typical hardware architecture of a DNNs accelerator (Figure 28 left) consists of:

- An off-chip memory (usually DRAM), to store the weights and the activations of the whole network. This level of memory can typically contain several GBs of data.

- An on-chip global buffer (GLB), large enough to hold the weights and inputs necessary to feed all the PEs. The energy needed to access the GLB can be two orders of magnitude lower than that of the DRAM [114].

- An array of hundreds of PEs, each containing an ALU

to perform MACs operations in parallel. The PEs usually

also include one or more Register Files (RFs) to locally

store data with an energy cost-per-access lower than that

of the GLB.

- The PEs are connected with each other and to the GLB by a Network-on-Chip (NoC). The data must be moved coordinately through the PEs to obtain the correct result, depending on how the operations are temporally scheduled and spatially distributed on the PEs. The NoC can then assume different configurations to implement various communication patterns, represented in Figure 28 right, depending on how data must be delivered.

Given the energy cost required by a DRAM access, the design of state-of-the-art DNNs accelerators focuses on

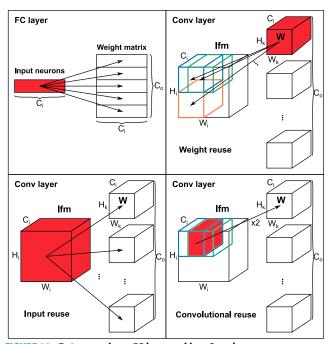

FIGURE 29. Data reuse in an FC layer and in a Conv layer.

the exploitation of *data reuse*, i.e., optimizing the architecture, the mapping of data on the PEs and the temporal scheduling of operations to maximize the reuse of data when they are stored in the lower-level memories such as the RFs or the GLB.

The different layers in an NN allow for taking advantage of various opportunities of data reuse, as explained in the following.

#### 1) FC LAYER

A FC layer can be described as a matrix-vector multiplication and it therefore presents an opportunity for *input reuse*, since the vector of the input neurons is dot-multiplied with each row of the matrix of weights (see Figure 29).

#### 2) CONV LAYER

The Conv layer has three different opportunities for data reuse (see Figure 29). To perform the convolution operation, a weight kernel is slid over the whole input feature map. There is an opportunity for *weight reuse* since the same weight kernel is multiplied for multiple subsets of the input feature maps. In particular, each of the  $C_o$  kernels is reused  $H_o \times W_o$  times.

There is an *input reuse* opportunity too, since the input feature maps are used  $C_o$  times to generate all the output feature maps. The last reuse opportunity is defined as *convolutional reuse* [114], and it exploits the sliding window mechanism, i.e., when computing two adjacent output pixels, there is usually an intersection between the two subsets of pixels of the input feature map used, as shown in Figure 29. The width and height of the intersection depends on the dimensions of the kernels  $(H_k \times W_k)$  and the horizontal and vertical strides

FIGURE 30. Spatial and temporal mapping of the Multiply-and-Accumulate (MACs) operations to the Processing Elements (PEs).

$(s_x, s_y)$ . The convolutional reuse combines both the weight reuse and the input reuse.

#### 3) POOLING LAYER

Pooling layers do not demand the use of weights. Therefore there are no opportunities of weight reuse. The stride parameter is usually set to have non-overlapping receptive fields, so it is not possible to exploit the sliding window mechanism for input reuse. These layers do not allow for any data reuse.

Given an array of PEs and all the MACs between weights and input feature maps that must be performed to calculate the output feature maps, each PE will execute a subset of MACs, and a number of MACs equal to the number of PEs will be executed in parallel. The MACs must, therefore, be *spatially* and *temporally mapped* to the PEs array (Figure 30). The mapping consequently defines how data must be loaded and stored from/to the memory hierarchy of the accelerator and how the NoC must be designed to correctly and efficiently deliver and collect the inputs, the weights and the partial sums. The spatial and temporal mapping of the operations is defined as *dataflow* [114].

Considering the high dimensions of the PEs array and the vast number of MACs to be computed, the space of possible mappings on a generic HW accelerator is enormous. Given the considerations on the energy consumption of the memory hierarchy, dataflows usually try to maximally exploit the opportunities of data reuse provided by the different layers of the NNs to minimize the accesses to the off-chip memory and the global buffer, and to use the data stored in the RFs as much as possible. Chen *et al.* [114] introduced a taxonomy to classify existing accelerators based on their dataflow and on how they exploit data reuse, that will be explained briefly in the following.

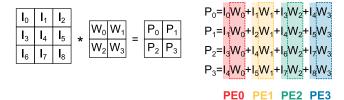

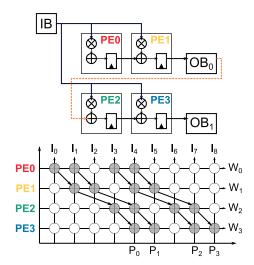

# 4) WEIGHT STATIONARY

The weight stationary dataflow aims at exploiting mainly the weight reuse to minimize the energy cost necessary to fetch the weights from the DRAM and the GLB. A subset of weights is read from the DRAM/GLB and stored in the RFs of the PEs. All the operations that involve a certain weight are then mapped to the PE where it is stored. Figure 31 shows how operations are mapped to an array of 4 PEs to perform a  $2 \times 2$  convolution on a  $3 \times 3$  input feature map.

Since the weights are kept stationary in the PEs, the inputs and the partial sums need to be coordinately moved through

FIGURE 31. Spatial mapping of the operations in a weight stationary dataflow.

FIGURE 32. (top) PEs array and (bottom) temporal-spatial mapping of the operations in a weight stationary accelerator with inputs broadcasting and outputs forwarding.

the array to optimize the data movement on the NoC too. A possibility consists of broadcasting a single input pixel of the input feature map to all the PEs and in storing each partial sum in a register then to pass it to the adjacent PE on the right. As shown in Figure 32, there are time steps in which some of the PEs perform operations that are not useful for the result (denoted in white). Moreover, the partial sums at the end of each row of processing elements needs to be stalled for  $W_i - W_k$  time steps before being passed to the next row of PEs. Therefore, all of these partial sums must be stored in the GLB. The nn-X accelerator [115] allocates instead  $H_k$  FIFOs at the end of each row, each of dimension  $W_i - W_k$ , to introduce the proper delay.

The input pixels can be moved with the forwarding scheme to take advantage of the convolutional reuse in addition to the weight reuse. The forwarding scheme consists of placing additional registers in the PEs to store the input pixel that they receive, and to then pass it to the neighboring PEs on the right (horizontally-sliding window). Figure 33 shows a dataflow with stationary weights and input forwarding. Both in [116] and [117],  $H_k$  rows of the input feature map are processed in parallel, and the partial sums of each row are then accumulated. The inputs are therefore stored in  $H_k$  buffers, and the pixels of the input feature map are moved from the (K-1) buffer to the 0 buffer (vertically-sliding window).

FIGURE 33. (top) PEs array and (bottom) temporal-spatial mapping of the operations in a weight stationary accelerator with inputs and outputs forwarding.

```

for (n=0; n<N; n++)

for (n=0; n<N; n++)

for (c_0=0; c_0< C_0; c_0++)

for (c_0=0; c_0< C_0; c_0++)

Loop

Reordering

for (c<sub>i</sub>=0; c<sub>i</sub><C<sub>i</sub>; c<sub>i</sub>++)

for (c<sub>i</sub>=0; c<sub>i</sub><C<sub>i</sub>; c<sub>i</sub>++)

for (h_0=0; h_0<H_0; h_0++)

par_for (h_k=0; h_k< H_k; h_k++)

for (w_0=0; w_0 < W_0; w_0++)

par_for (w_k=0; w_k< W_k; w_k++)

for (h_k=0; h_k< H_k; h_k++)

for (h<sub>0</sub>=0; h<sub>0</sub><H<sub>0</sub>; h<sub>0</sub>++)

for (w_k=0; w_k< W_k; w_k++)

for (w_0=0; w_0 < W_0; w_0++)

Ofm[n][c_O][h_O][w_O] +=

Ofm[n][c_O][h_O][w_O] +=

Ifm[n][c_i][h_O+h_K][w_O+w_K]

Ifm[n][c_i][h_O+h_k][w_O+w_k] *

W[c_0][c_i][h_k][w_k]

W[c_0][c_i][h_k][w_k]

```

FIGURE 34. Loop reordering of the 7-nested loops representation of the Conv layer.

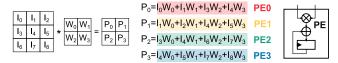

What characterizes the above-discussed dataflows is that all the operations along dimensions  $H_k$  and  $W_k$  are mapped to the 2D PE array and executed in parallel. This mapping operation is defined as *spatial unrolling* in [118]. From a software perspective this is equivalent to replacing the **for** loops in the 7-nested loop representation with parallel for loops (**par\_for**) as in Figure 34. In [118], the  $H_k|W_k$  syntax is adopted to denote which loops are parallelized. The stationarity of the weights is instead equivalent, from the software perspective, to a *loop reordering* operation of the **for** loops, as shown in Figure 34. Other architectures that adopt a  $H_k|W_k$  weight stationary approach are [119], [120] and [121].

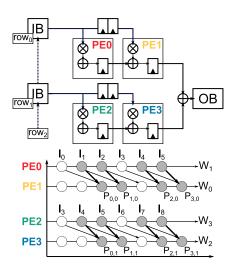

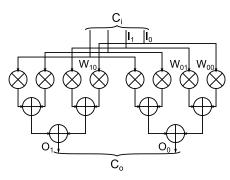

A different dataflow, but in which the weights are still stationary, is obtained by spatially unrolling the dimensions  $C_o$  and  $C_i$  ( $C_o|C_i$ ). As shown in Figure 35, the operations that must be performed are equivalent to a vector-matrix multiplication. It can be realized in hardware with a 2D systolic array. In essence, the weights are internally stored in the PEs, the inputs are horizontally forwarded, and the partial sums are accumulated along the vertical dimension. An example of  $C_o|C_i$ -weight stationary dataflow can be found in in the Tensor Processing Unit (TPU) [122] developed at Google. TPUs are deployed in datacenters, and it has therefore been possible to obtain statistics and metrics on real-life applications. It has

FIGURE 35. (top left) Reordered loops for a dataflow with weights stationary along dimensions  $C_i$  and  $C_0$ . (top right) Mapping the operations of a Conv layer to a matrix multiplication. (bottom) PEs array in a  $C_i | C_0$  weight stationary accelerator with input and output forwarding.

FIGURE 36. (left) Spatial mapping of the operations in an output stationary dataflow. (right) Modified PE for an output stationary

been observed that CNNs, on which the development of HW accelerators is focused, actually represent the 5% of all applications used in datacenters [122]. For this reason, Google designers decided to focus on the acceleration of FC layers, which are inherently vector-matrix operations and can, therefore, be directly mapped to the matrix-multiply unit that is the heart of the TPUs.

Because of its flexibility, the systolic array is often used in configurable architectures that must support various layer types [123], [124] [125]. This solution is also adopted for the acceleration of Capsule Networks [126], [127] [128], that consist of Conv layers, Conv layers of capsules and FC layers of capsules.

# 5) OUTPUT STATIONARY

The output stationary dataflow has the purpose of minimizing the data movement necessary to store and load the partial sums in the GLB. With the weight stationary dataflow of Figure 32, for example, the partial sum of a single output pixel must be stored and reloaded to/from the GLB  $(H_k-1) \times C_i$  times. In the output stationary dataflow, the PEs are modified to have the possibility of locally accumulating the results of the MACs that they perform (Figure 36). Each PE is therefore responsible for the computations necessary to obtain an output pixel, whose partial sums are accumulated in a single RF.

FIGURE 37. (top left) Reordered loops for an output stationary dataflow. (top right) PEs array and (bottom) temporal-spatial mapping of the operations in an output stationary accelerator with input broadcasting and weight forwarding.

FIGURE 38. Data movements in ShiDianNao accelerator [129].

Similarly to the weight stationary dataflow, it is possible to spatially unroll the  $H_o$  and  $W_o$  loops to get an output stationary dataflow. The input pixels and the weights can then be read from the GLB and moved to the PEs array in different ways. It is, for example, possible to broadcast the input pixels to all the PEs and to forward the weights, as shown in Figure 37.

A popular accelerator that adopts an output stationary dataflow with  $H_o|W_o$  spatial unrolling is ShiDianNao [129]. Being an output stationary dataflow, each PE in the 2D grid of ShiDianNao processes a pixel of an output feature map, and all the results are then collected and stored in the global buffer. A single weight is broadcasted to all the PEs at every operation cycle. The PEs can read the input pixel either from the GLB, from their right neighbor or their lower neighbor. The PEs have a RF for the partial sum accumulation and two FIFOs to store input pixels for inter-PEs communication. Figure 38 schematizes data movement in ShiDianNao for a  $2 \times 2$  array of PEs.

Computing the output pixels in parallel along the dimensions  $H_o$  and  $W_o$  is not the only possible solution to get an output stationary dataflow. Origami accelerator [130], for example, spatially unrolls three loops ( $H_k$ ,  $W_k$  and  $C_o$ ) and computes all the pixels along the output channel  $C_o$  in parallel, dedicating an accumulator to each one. In a compromise between [129] and [130], in [131] the output pixels along

FIGURE 39. Different solutions [129], [131] [130] to spatially unroll the computations in an output stationary dataflow.

FIGURE 40. Operations mapping in a row stationary dataflow.

dimensions  $H_o$  and  $C_o$  are computed in parallel. Figure 39 graphically shows how [129], [131] and [130] spatially unroll the computation of the output pixels.

It is important to notice that spatially unrolling the dimensions  $C_i$  and  $C_o$  can either lead to a weight stationary or an output stationary dataflow. Beyond what data is kept stationary,  $C_i|C_o$  dataflow is very common because it performs a vector-matrix or matrix-matrix multiplication, and therefore, it allows to easily map both a convolutional and a fully-connected layer to the same array of PEs.

# 6) ROW STATIONARY

The row stationary dataflow is introduced in [114] and used by the Eyeriss accelerator [132]. It has the purpose of maximizing the reuse of inputs, weights and partial sums all together, in contrast to weight and output stationary dataflows that focus on a single type of data reuse.

In the row stationary dataflow all the MACs necessary to perform a row of the convolution (1D convolution) are mapped to a single PE. A PE has a RF to keep stationary a row of the weight kernel while the inputs are streamed in the PE exploiting the sliding window mechanism. To perform a whole 2D convolution, it is necessary to have a 2D array of  $H_k \times H_o$  PEs. Each column of the array computes the  $H_k \times W_o$  partial sums that contribute to a row of the output feature map, that are therefore accumulated. Figure 40 shows how a 2D convolution with a 3  $\times$  3 weight kernel is mapped to a row stationary dataflow, and how the partial sums are accumulated along the columns of the PEs array.

From Figure 40 it is also possible to see the different types of reuse obtained by the row stationary dataflow. The optimization of data reuse is multi-objective, i.e., a row of PEs shares the same weights, the input pixels are diagonally reused, and the partial sums are vertically accumulated.

#### 7) NO LOCAL REUSE

The memory elements with higher energy efficiency are those with a low storage capacity, but they are less efficient in terms of area occupation (area/bit). Therefore, a RF has a

FIGURE 41. No local reuse dataflow.

higher area/bit compared to a scratchpad memory or a SRAM. The no local reuse dataflow maximizes the area dedicated to storage by removing register files from the PEs and allocating all the on-chip memory in the global buffer. Having no local reuse in the PEs, the traffic from and to the GLB on the NoC will be higher.

Which dimension is spatially unrolled on the PEs is not relevant for the no local reuse dataflow. Two accelerators that adopt this dataflow are [24], [133] and [134], which execute the loops along the dimensions  $C_i$  and  $C_o$  in parallel. In [133],  $C_i \times C_o$  multipliers are allocated to multiply the inputs and the weights, and the  $C_o$  outputs are then computed with adder trees. An input pixel is multicasted to  $C_o$  multipliers (see Figure 41), while each multiplier reads a different weight from the global buffer.

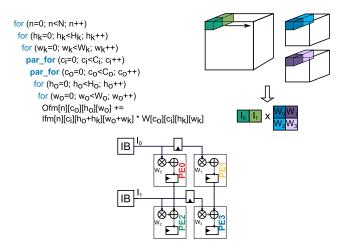

A critical aspect of the dataflow definition and accelerator design has not yet been mentioned. Usually, the global buffer size is not sufficient to fully contain the input feature maps, kernel weights and output feature maps. For this reason, it is necessary to apply the *loop tiling* technique, which consists of partitioning the larger tensors into smaller tensors that can be contained in the buffer. The **for** loops of the 7-nested loops representation of the convolutional layer are therefore split into multiple loops, as shown in Figure 42. The tiling factors  $(TC_o, TC_i, TH_o, TW_o)$  define the size of the innermost loops and consequently of the global buffer size. In contrast, the permutations of the outermost loops determine the off-chip memory accesses and how the data are reused.

Due to the wide variety of layer types and sizes in DNNs models, recently the reconfigurable accelerators that allow to efficiently map different types of layers on the same hardware have gained importance. For example, in [135], there are two 16 × 16 arrays, whose PEs are divided into general PEs and super PEs. The former are used to map the Conv and FC layers, while the latter are used for the activations functions, Pooling layers, and RNN layers. The arrays can also be partitioned to process multiple layers in parallel and the accelerator supports 8- or 16-bit operations. Another example of a reconfigurable accelerator is the NPU that is at the heart of Project Brainwave [136], the real-time AI FPGA used in Microsoft's servers. The Project Brainwave NPU is a spatially distributed architecture with efficient matrix-

```

for (n=0; n<N; n++)

Off-chip memory

for (c_{oe}=0; c_{oe}< C_o; c_{oe}+=TC_o)

access pattern

for (c_{ie}=0; c_{ie}< C_i; c_{ie}+=TC_i)

for (h<sub>oe</sub>=0; h<sub>oe</sub><H<sub>o</sub>; h<sub>oe</sub>+=TH<sub>o</sub>)

for (w_{oe}=0; w_{oe}<W_o; w_{oe}+=TW_o)

for (c<sub>o</sub>=c<sub>oe</sub>; c<sub>o</sub><c<sub>oe</sub>+TC<sub>o</sub>; c<sub>o</sub>++)

On-chip computation

for (c_i=c_{ie}; c_i< c_{ie}+TC_i; c_i++)

for (h_o=h_{oe}; h_o< h_{oe}+TH_o; h_o++)

for (w_o=w_{oe}; w_o< w_{oe}+TW_o; w_o++)

for (h_k=0; h_k< H_k; h_k++)

for (w_k=0; w_k < W_k; w_k++)

Ofm[n][c_o][h_o][w_o] +=

[fm[n][c_i][h_o + h_k][w_o + w_k] * W[c_o][c_i][h_k][w_k]

```

FIGURE 42. Loop tiling technique applied to the 7-nested loops representation of the Conv layer. The outermost loops describe off-chip memory accesses, and the innermost loops determine the dataflow.

vectors multipliers for the operations between tensors and multifunction units that implement a wide variety of functions. MAERI [137] obtains reconfigurability through the interconnections. The multipliers are arranged in a 1D structure and the inputs are delivered with a flexible distribution network that can be set to implement different dataflows. Similarly, the outputs of the multipliers are collected with an Augmented Reduction Tree of adders. A similar approach is adopted in SIGMA [138], in which the flexible distribution and reduction networks allow to perform vector dotproducts of different sizes simultaneously. Cerebras Wafer Scale Engine is the largest chip ever built, and it is optimized for DL applications. The engine consists of a large amount of flexible cores that target tensor operations but support general operations too. The memory has a high capacity, in the order of gigabytes, and is distributed on-chip. Huawei has released the DaVinci AI core [139], which is completely high-level programmable and consists of a vector engine and a 3D Cube engine for matrix computations. Two or more DaVinci cores can be combined to work in parallel, as in the Huawei Ascend 910 and 310 AI processors.

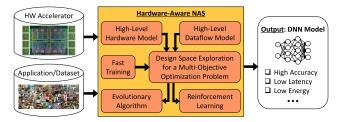

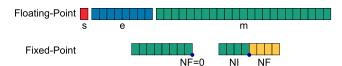

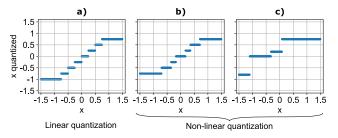

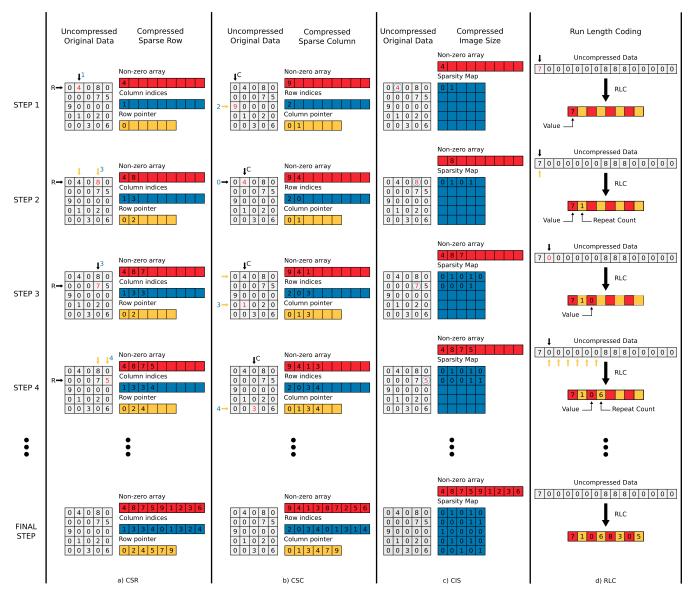

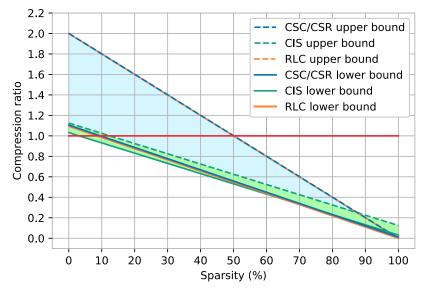

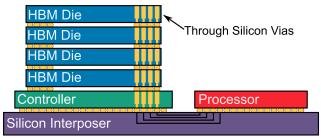

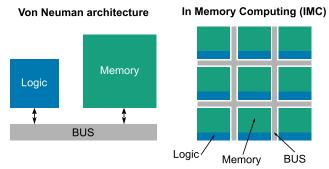

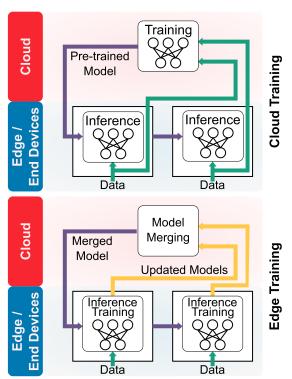

#### D. TOOLS FOR DESIGN SPACE EXPLORATION (DSE)