# Doctoral Dissertation Doctoral Program in Computer and Control Engineering (32nd cycle)

# Cyber-security for embedded systems: methodologies, techniques and tools

## Sebastiano Fabrizio Finocchiaro

\* \* \* \* \* \*

## Supervisor

Prof. Gianpiero Cabodi

#### **Doctoral Examination Committee:**

Prof. Aurelien Francillon, Referee, EURECOM

Prof. Joao Marques Silva, Referee, University of Toulouse

Prof. Pietro Laface, Politecnico di Torino

Prof. Luciano Lavagno, Politecnico di Torino

Prof. Silvio Ranise, Fondazione Bruno Kessler

Politecnico di Torino 2020 This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Sebastiano Fabrizio Finocchiaro Turin, 2020

# Summary

The last two decades have produced an enormous change in technical systems that revolutionized the way how people live their lives, organizations conduct business and even the notion of society itself. This tendency is far from ending soon, rather the future will be ubiquitously connected by computing environments that pervade our whole life. These environments (not merely hardware/software systems, but they are inherently designed for the cyberspace, and perhaps in the future will be integrated also in the human body) are now termed as Cyber-Physical Systems (CPSs). CPSs are made up by a heterogeneous set of subsystems: embedded computers, actuators, distributed sensors, physical processes are integrated together over a communication network. It has been anticipated that CPSs are likely to take over traditional computing systems thanks to adaptability, safety, robustness, efficiency, and reliability. The level of predominant presence of such systems will dictate the development of intuitive and intelligent user interfaces, some of them manually operated and others autonomously controlled. The interfaces will provide service delivering and communication effectively and efficiently, thus enabling sophisticated ambient intelligence systems. Today, CPSs are typically deployed in manufacturing, medical devices, civil infrastructure, smart grids, transportation, industrial environments and so on. As society employs more and more ubiquitous computing technologies, individuals, organisations and companies are increasingly depending on them. It is already challenging and it will be even more to orient oneself among the extensive amounts of services and information. On one hand, this trend will lead to an increase of sensitive and critical operations. On the other hand, its very ubiquity (almost imperative presence in every aspect of society) will entice people to expect a comforting nature from it, making people forget about security requirements yet especially crucial.

Nowadays, the use of CPSs in some strategic areas of our society, where human life is directly affected, is of vital importance: from medicine to traffic control to stock exchange markets and international finance. We are progressively relying on such systems, even depending in some cases, yet a question raises concerns: *Do we trust enough these systems to let them manage our lives?*. This question hides the growing need for new and more effective security approaches in embedded systems and it is the motivation of this work.

Historically, security research and development were born in the IT area. Traditional IT security methods use the notions of confidentiality, integrity and availability. They, too, can be applied to CPSs security. However, they do not cover the full spectrum of CPSs security, hence new challenges are open to be solved.

In particular, the effort has been devoted to verification techniques and methodologies. The main focus of this work is on formal verification of security properties that guarantee confidentiality, integrity and availability. Starting from state-of-theart formal verification techniques (model checking, equivalence checking, etc.) we developed new approaches for security-critical systems. We defined a portfolio of Taint properties and provided experimental results for hardware systems that employ root of trust support and remote attestation. From the experience of applying Taint properties on real architectures we realised that this class of properties is able to capture some specific behaviors of a system, neglecting others. We therefore proposed a new class of properties called Path properties that are able to capture information flow behaviors. A portfolio of this properties has been presented and experimental results have been provided to support our claim. Eventually we thought that a combined approach would be useful, so we presented a verification approach to verify both Taint properties and Path properties in a standard model checker. Ground breaking attacks such as Spectre and Meltdown made us wonder whether it would be possible to verify hardware designs against this kind of attacks. We then proposed a novel verification approach towards out-of-order speculative execution microprocessors that are prone to side channel attacks like Spectre and Meltdown. Our verification methods rely on widely known abstraction and reduction techniques for large designs, but they have been paired with the application of a information flow verification approach.

# Acknowledgements

I would like to acknowledge whoever supported me in any possible way throughout this journey. My gratitude firstly goes to my supervisor Gianpiero Cabodi. I would also like to acknowledge Prof. Paolo Camurati and Prof. Stefano Quer. My colleagues with whom I shared ups and downs: Francesco, Danilo, Denis, Marco, Paolo, Evelina, Federica, Federica, Alberto.

After all I would like to thank every person, friend or not, who smiled at me.

# $Alla\ mia\ famiglia.$

# Contents

| Li | st of                | Tables | 5                            | XII |

|----|----------------------|--------|------------------------------|-----|

| Li | List of Figures XIII |        |                              |     |

| 1  | Intr                 | oducti | on                           | 1   |

| 2  | Bac                  | kgrour | nd                           | 7   |

|    | 2.1                  | Securi | ty features                  | 7   |

|    |                      | 2.1.1  | Spoofing                     | 7   |

|    |                      | 2.1.2  | Tampering                    | 8   |

|    |                      | 2.1.3  | Repudiation                  | 8   |

|    |                      | 2.1.4  | Information Disclosure       | 9   |

|    |                      | 2.1.5  | Denial of Service            | 9   |

|    |                      | 2.1.6  | Elevation of Privileges      | 9   |

|    | 2.2                  | Forma  | l methods                    | 10  |

|    |                      | 2.2.1  | Benefits Of Formal Models    | 12  |

|    |                      | 2.2.2  | Weaknesses Of Formal Methods | 12  |

|    | 2.3                  | Forma  | l Specification              | 13  |

|    |                      | 2.3.1  | Formal logic                 | 14  |

|    | 2.4                  | Forma  | l verification               | 15  |

|    |                      | 2.4.1  | Theorem proving              | 16  |

|    |                      | 2.4.2  | Equivalence checking         | 17  |

|    | 2.5                  | Model  | checking                     | 18  |

|    |                      | 2.5.1  | Modeling                     | 20  |

|    |                      | 2.5.2  | Specification                | 21  |

|    |                      | 2.5.3  | Verification                 | 22  |

|   | 2.6  | Modelling Concurrent systems                               | 23 |

|---|------|------------------------------------------------------------|----|

|   |      | 2.6.1 Transition systems                                   | 23 |

|   |      | 2.6.2 System invariants                                    | 24 |

|   | 2.7  | Linear Time Temporal Logic                                 | 25 |

|   | 2.8  | Branching Time Temporal Logic                              | 26 |

|   | 2.9  | CTL*                                                       | 27 |

|   | 2.10 | $\omega$ -automata                                         | 28 |

|   | 2.11 | Symbolic Model Checking                                    | 29 |

|   | 2.12 | Bounded Model Checking                                     | 30 |

| 3 | Secu | re Embedded Architectures: Taint Properties Verification 3 | 33 |

|   | 3.1  | Introduction                                               | 33 |

|   | 3.2  | Background                                                 | 35 |

|   |      | 3.2.1 Trusted Computing Base and root of trust             | 35 |

|   |      | 3.2.2 Remote attestation                                   | 36 |

|   |      | 3.2.3 SMART                                                | 37 |

|   |      | 3.2.4 SANCUS                                               | 36 |

|   | 3.3  | Related work                                               | 11 |

|   | 3.4  | Adversarial Model                                          | 12 |

|   | 3.5  | Security Requirements                                      | 13 |

|   | 3.6  | Security Model Abstraction                                 | 15 |

|   | 3.7  | Taint Properties Verification                              | 16 |

|   |      | 3.7.1 Temporal Operators                                   | 18 |

|   |      | 3.7.2 Key secrecy                                          | 50 |

|   |      | 3.7.3 Isolation                                            | 51 |

|   |      | 3.7.4 Availability                                         | 53 |

|   | 3.8  | Experimental results                                       | 54 |

|   |      | 3.8.1 Model Checking Results                               | 55 |

|   |      | 3.8.2 Verification Strategies                              | 56 |

|   | 3.9  | Conclusions                                                | 56 |

| 4 | Secu | re Path Verification                                       | 59 |

|   | 4.1  |                                                            | 59 |

|   |      | 4.1.1 Contributions                                        | 30 |

|   | 4.2  | Related work                                                       |

|---|------|--------------------------------------------------------------------|

|   | 4.3  | Attacker Model                                                     |

|   | 4.4  | Model Abstraction                                                  |

|   | 4.5  | Security Properties Definition                                     |

|   | 4.6  | Security Properties Verification                                   |

|   | 4.7  | Experimental Results                                               |

|   | 4.8  | Conclusions                                                        |

| 5 | Em   | pedded Systems Secure Path Verification at the HW/SW In-           |

|   | terf | ace 7                                                              |

|   | 5.1  | Introduction                                                       |

|   |      | 5.1.1 Roadmap                                                      |

|   | 5.2  | System and threat model overview                                   |

|   |      | 5.2.1 Model abstraction and reduction                              |

|   |      | 5.2.2 Threat model                                                 |

|   | 5.3  | Definition of Security Properties                                  |

|   |      | 5.3.1 Confidentiality                                              |

|   |      | 5.3.2 Integrity                                                    |

|   |      | 5.3.3 Availability                                                 |

|   | 5.4  | Verification strategy                                              |

|   | 5.5  | Experimental Results                                               |

|   |      | 5.5.1 Use cases                                                    |

|   |      | 5.5.2 Bounded and Unbounded Model Checking comparison 9            |

|   | 5.6  | Conclusions                                                        |

| 6 | Mo   | del-Checking Speculation-Dependent Security Properties 98          |

|   | 6.1  | Introduction                                                       |

|   | 6.2  | Background and Related Works                                       |

|   |      | 6.2.1 Side channels                                                |

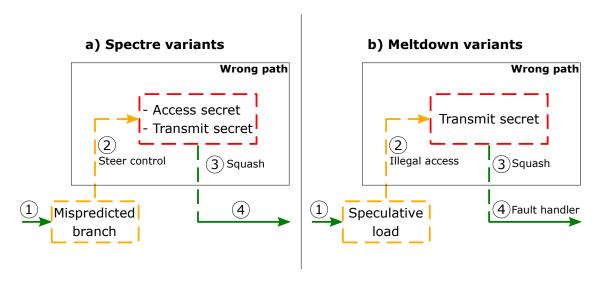

|   |      | 6.2.2 Spectre and Meltdown Attacks                                 |

|   |      | 6.2.3 Formal Verification of Microprocessors with Out-of-Order Ex- |

|   |      | ecution                                                            |

|   |      | 6.2.4 Verifying Cybersecurity by Tainting                          |

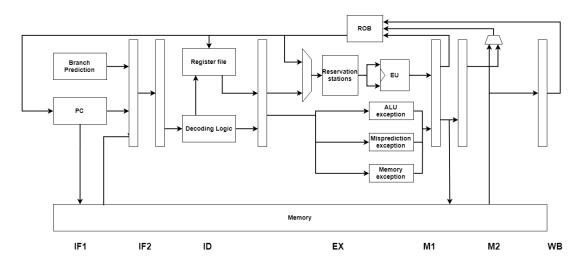

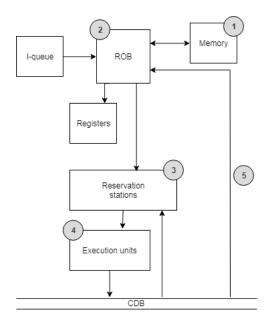

|   | 6.3  | Processor Model                                                    |

|    | 6.4 Attack Description |        |                                            | 109 |

|----|------------------------|--------|--------------------------------------------|-----|

|    |                        | 6.4.1  | Step One                                   | 111 |

|    |                        | 6.4.2  | Step Two                                   | 112 |

|    |                        | 6.4.3  | Step Three                                 | 112 |

|    | 6.5                    | Proof, | Verification                               | 113 |

|    |                        | 6.5.1  | Data Abstraction and Tainting              | 114 |

|    |                        | 6.5.2  | Combining Model Reduction with Abstraction | 119 |

|    |                        | 6.5.3  | Correctness of the Approach                | 121 |

|    | 6.6                    | Exper  | imental Results                            | 124 |

|    | 6.7                    | Conclu | usions and Future Work                     | 125 |

| 7  | Con                    | clusio | ns                                         | 127 |

| Bi | iblios                 | raphy  |                                            | 131 |

# List of Tables

| 2.1 | Security concerns with corresponding security threats suggested by |     |  |

|-----|--------------------------------------------------------------------|-----|--|

|     | the Security Development Lifecycle                                 | 10  |  |

| 3.1 | SMART and SANCUS: Abstract Model mapping                           | 47  |  |

| 3.2 | Unbounded Model Checking results SMART and SANCUS models .         | 55  |  |

| 4.1 | SMART and SANCUS: Abstract Model mapping                           | 67  |  |

| 6.1 | Concrete versus Abstract model transformation                      | 114 |  |

| 6.2 | Comparison of data evaluation and taint propagation between con-   |     |  |

|     | crete and abstract models                                          | 115 |  |

| 6.3 | Our model applied to a real use case: a basic implementation of    |     |  |

|     | Spectre/Meltdown                                                   | 118 |  |

| 6.4 | Pipeline evolution of the proposed attack                          | 118 |  |

# List of Figures

| 1.1 | Vulnerable components in traditional IT infrastructure and defense   |     |

|-----|----------------------------------------------------------------------|-----|

|     | strategies                                                           | 5   |

| 2.1 | Formal verification techniques                                       | 16  |

| 2.2 | The procedure of Theorem proving                                     | 17  |

| 2.3 | The procedure of Equivalence checking                                | 18  |

| 2.4 | The procedure of Model Checking                                      | 19  |

| 3.1 | An example of Remote Attestation protocol                            | 38  |

| 3.2 | Schematic of a SANCUS node with a software module loaded             | 40  |

| 3.3 | Secure Abstraction Model                                             | 47  |

| 3.4 | Taint Property Example                                               | 49  |

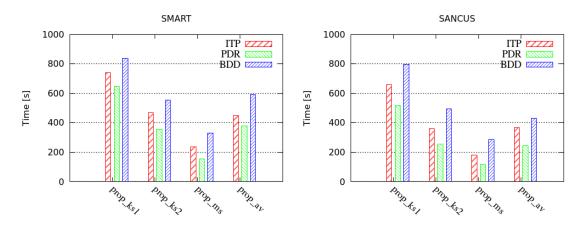

| 3.5 | Pdtrav verification strategies results for SMART and SANCUS          | 57  |

| 4.1 | Secure Abstraction Model                                             | 66  |

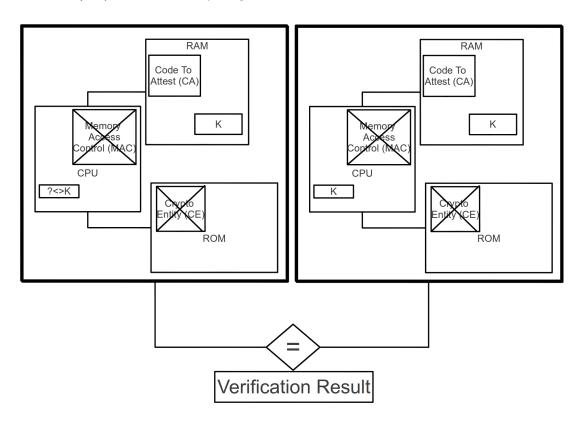

| 4.2 | Secure Path Verification                                             | 74  |

| 4.3 | Verification time for SMART architecture                             | 76  |

| 4.4 | Verification time for SANCUS architecture                            | 76  |

| 5.1 | Verification time for SMART and SANCUS architectures                 | 94  |

| 6.1 | Spectre vs Meltdown attack classes                                   | 102 |

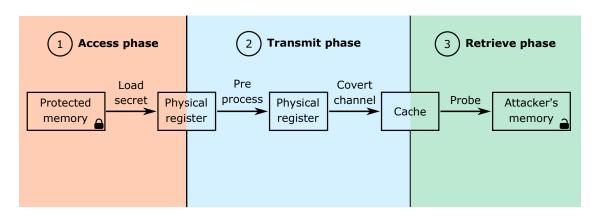

| 6.2 | Three phases of speculative execution attacks                        | 103 |

| 6.3 | The 7-stage pipelined processor model                                | 109 |

| 6.4 | Taint propagation from source (memory read) to sink (reorder buffer) |     |

|     | in our abstract model                                                | 117 |

# Chapter 1

# Introduction

The last two decades have produced an enormous change in technical systems that revolutionized the way how people live their lives, organizations conduct business and even the notion of society itself. The term cyberspace describes this trend: the networked universe where part of our daily routines live. It is so extremely interconnected that even a small ripple on this sea is propagated widely through other parts of the cyberspace. This tendency is far from ending soon, rather the future will be ubiquitously connected by computing environments that pervade our whole life. The mutual dependency will be stronger than ever and data plays the most important role in it. These environments are not merely hardware/software systems, but they are inherently designed for the cyberspace. Indeed they are now termed as Cyber-Physical Systems (CPSs) [1].

CPSs are made up by a heterogeneous set of subsystems: embedded computers, actuators, distributed sensors, physical processes are integrated together over a communication network. It has been anticipated that CPSs are likely to take over traditional computing systems thanks to adaptability, safety, robustness, efficiency, and reliability [2].

CPSs are and will be capable of providing several degrees of computational power for different needs. CPSs are very helpful for our daily life but they all will be bounded to the most crucial aspect: data and the transmission of huge quantity of it. All this traffic is organized into different networking schemes, CPS tend not to be operate alone but in structured organizations. The schemes vary from dynamic ad-hoc peer-to-peer networks to the standard client-server architectures,

including a diversified heap of hybrids in between. The level of predominant presence of such systems will dictate the development of intuitive and intelligent user interfaces, some of them manually operated and others autonomously controlled. The interfaces will provide service delivering and communication effectively and efficiently, thus enabling sophisticated ambient intelligence systems.

Today, CPSs are typically deployed in manufacturing [3], medical devices, civil infrastructure [4], smart grids, transportation [5], industrial environments [6, 7] and so on. As society employs more and more ubiquitous computing technologies, individuals, organisations and companies are increasingly depending on them. It is already challenging and will be even more to orient oneself among the extensive amounts of services and information. On the one hand, this trend will lead to an increase of sensitive and critical operations. On the other hand, its very ubiquity (almost imperative presence in every aspect of society) will entice people to expect a comforting nature from it, making people forget about security requirements yet especially crucial [8, 9].

Nowadays, the use of CPSs in some strategic areas of our society, where human life is directly affected, is of vital importance: from medicine to traffic control to stock exchange markets and international finance. We are progressively relying on such systems, even depending in some cases, yet a question raises concerns:

"Do we have enough confidence in computer systems that we let them handle our most valuable goods, namely our life and money?" [10].

The term confidence translates to the notion of dependability, of which a useful definition has been provided by [11]:

"Dependability of a computing system is the ability to deliver service that can justifiably be trusted."

This definition underlines two aspects that affect the design, the implementation and our reasoning about system "correctness":

- Dependability does not explicitly preclude systems faults. Rather, it requires that the application service, i.e., the functionality required by the end user of the system, is delivered as specified.

- Delivery of service is only required to the extent covered by the specification. The term *justifiably* means that the delivery of service is correct up to the

specification. This point is crucial because otherwise the system developer/designer could never prove the correctness. Moreover, the service is only as good as the requirements: the specification document should reflect the user understanding on how the system should behave. As a consequence, the specification phase has become the most critical phase of the whole system development life cycle.

Although the definition of *Dependability* is ambiguous, some contributions have tried to formalize it. For instance, the authors in [11] identify four attributes to characterize the dependability:

- safety: absence of catastrophic consequences on the user and the environment

- security: preservation of confidentiality and integrity of information

- availability: readiness for correct service

- reliability: continuity of correct service

The above attributes are directly related to vulnerabilities: the primary cause of adversarial attacks or unexpected system behaviours. This demands an effort by design engineers to satisfy security requirements while preserving functional ones. As we will see these two needs are now generally enforced as a conjunct approach during the design steps. The concept of cybersecurity has been changing through time, reflecting the demands from the involved parties: users, companies, organizations, scientific community, etc. Traditionally, cybersecurity has been viewed as protection of resources:

- Confidentiality: prevention of unauthorized disclosure of information

- Integrity: modification or destruction of information

The concept now goes beyond that and embodies also the notion of availability: the whole system as well as its parts (data, software, services, etc.) must be usable whenever they are needed by the authorized users.

Moreover, cybersecurity carries also additional tasks: gather evidence of, prevent or detect illegal activities in cyberspace, from acts of terrorism [12] to articulated web-based investment frauds [13].

Cybersecurity is a very complex task: it is expensive, both in terms of money and time, it has to be comprehensive, it requires certain knowledge, it has to be coordinated with other efforts. Therefore, it is often misinterpreted or incorrectly implemented, making room for threats, vulnerabilities and attacks. For example, industrial control systems are prone to cyberattacks with possible catastrophic consequences, as showed by the Stuxnet worm [14]. In 2015 a group of researchers demonstrated that an attack to control an entire vehicle is already viable [15], while Meltdown and Spectre attacks [16, 17] showed that microarchitectural vulnerabilities can be exploited to retrieve sensitive data from almost the entire user and server computer market.

The literature is packed with surveys and assessments on cybersecurity or state of cybercrime [18, 19].

Securing a computing system is a complex task, there are a plethora of different approaches and methods, but they can be grouped in four general categories:

- the use of procedures to achieve a security requirement

- the integration of the system with additional functions or mechanisms

- the use of assurance techniques

- the use of intrusion detection systems.

Some security requirements prescribe that the user must follow a very specific procedure, i.e., an appropriate behavior when using the system. "The password must be at least 8 characters long" is an example of this approach. Enhancing the system security can also be achieved by adding functions or mechanisms (either hardware or software). Examples are hardware-accelerated security chips, access control, authentication mechanisms, and inference control. This solution is expensive though, it requires money for the hardware and time for software development. Combining this approach with some assurance techniques is a possible trade off. Assurance techniques are rigorous methods (either formal or non-formal) to increase security confidence towards the system. For example, formal functional verification is able to prove the system correctness under the system model and its specification.

Nonetheless, no matter how engineers implement security requirements in their systems, it is now generally accepted that cybersecurity can be obtained only

through systematic development, it can not be achieved through disorganized and improvised methods [20].

Historically, security research and development was born in the IT area. Traditional IT security methods use the notions of confidentiality, integrity and availability. They, too, can be applied to CPSs security. However, they do not cover the full spectrum of CPSs security, hence new challenges are open to be solved [21].

Although standard notions of security are quite effective on the software side, they tend to provide little to nothing solutions in the hardware side of CPSs. As a consequence, information security approaches fail to discover unwanted behaviors under attacks that take advantage of hardware vulnerabilities.

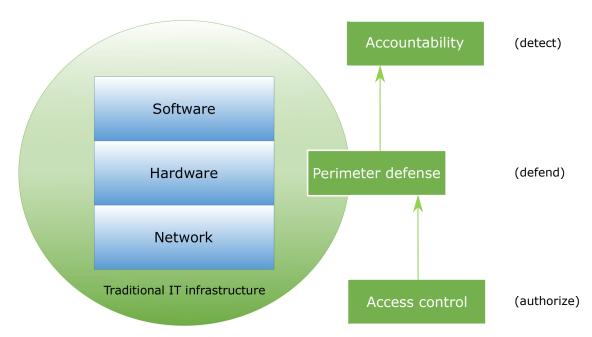

Figure 1.1: Vulnerable components in traditional IT infrastructure and defense strategies

In the IT world the security is mostly depicted as in Figure 1.1. The countermeasures are: accountability, perimeter defense, access control mechanisms. They serve to, respectively, authorise accesses, defend the secure area and detect unwanted behaviors. The scheme is well established and indeed works on most the IT architectures, but emerging threats in the CPS world compromise the trustworthiness of it. The biggest disadvantage of this approach is that, while it is efficient against attack from the *outside*, is useless against *inside* attacks, i.e., attacks that exploit system faults or design flaws.

And this is the point where formal methods come into play. Recall the four approaches to enhance the security of a system: one of them is to subject the system to rigorous assurance techniques. Among these techniques there are formal methods. None of these methods can provide a full assurance for secure systems, but they increase the security confidence more than other approaches.

The literature offers contributions on formal approaches over these systems: they range from the diverse family of formal languages called Process Calculi [22, 23], Timed Automata [24], Game Theory [25], Theorem proving [26]. Among other formal methods, Model checking is a formal technique used in the verification steps of the design lifecycle. To the best of our knowledge few results have been proposed to model check hardware/software designs: either they target specific systems (e.g., stochastic systems [27]) or require great manual effort in order to translate the original HDL-based model into a specialized algebra or calculus (e.g., Security Process Algebra [28], PROMELA [29]).

# Chapter 2

# Background

# 2.1 Security features

Security is a well established practice in Software Development Life Cycle. As mentioned in the previous Chapter, hardware development life cycle approaches often lack of support for security. As we intend to deal with security mainly with both hardware and software, we must first provide a general scheme (or threat model) to identify security features and threats. We will refer to this common lexicon throughout this work. Among other methodologies, STRIDE [30] is one of most common in the software area. STRIDE identifies six security features. Following STRIDE we cover every aspect of security with each category.

# 2.1.1 Spoofing

Spoofing is declaring a false identity (e.g., process spoofing) or pretending to be someone else (e.g., user spoofing).

Authenticity is what this category deals with.

Examples:

- In computer networks, man-in-the-middle attacks are often carried out with IP spoofing.

- A phishing attack attempts to gain credentials from the users.

Brute-forcing username/password credentials is one example of identity spoofing.

Typical countermeasures are proper authentication schemes.

## 2.1.2 Tampering

Tampering is about the malicious modification of data/processes. The modification may happen during the transmission of data, during the storage of data, or on processes.

Integrity is what this category deals with.

Examples:

- Injection attacks on the system processes, e.g., SQL injection.

- An attacker modifies data on the main memory/on secondary memory.

- An attacker alters data in transit by bit-flipping attacks.

Typical countermeasures are:

- Data protection mechanisms

- Validation of inputs and encoding of outputs.

- Minimize dependence to 3rd party libraries/dependencies.

- Integration with static code analysis tools.

## 2.1.3 Repudiation

Repudiation is about denying that an event has occurred.

Non-repudiation is what this category deals with.

Examples:

- Attackers usually hide their track by erasing log files.

- A destructive action (e.g., deleting an entire database) cannot be associated with a particular person.

Typical countermeasures are audit logging systems.

#### 2.1.4 Information Disclosure

Information Disclosure is about data leaks. The leak may happen during the transmission of data, during the storage of data, or on processes.

Confidentiality is what this category deals with.

Examples:

- An attacker reads sensitive data in a database.

- An attacker retrieves the encryption key.

- An attacker manages to gain confidential information on the system.

- An attacker is able to sniff in transit data over a communication channel.

Typical countermeasures are proper encryption schemes.

#### 2.1.5 Denial of Service

Denial of Service is about making a network resource or a service unavailable to its intended users.

Availability is what this category deals with.

Examples:

- The storage (i.e., disk, drive) is maliciously filled with data.

- An attacker floods the network (e.g., SYN flood attack).

- The encryption routine is continuously called thus preventing normal users to do so.

Prevention is generally not a feasible task for a plethora of reasons. Mitigation is the best tradeoff, for example by monitoring systems with Intrusion Detection Systems (IDS).

## 2.1.6 Elevation of Privileges

Elevation of Privileges, or Privilege escalation, is about exploiting a misconfiguration, a design flaw or a bug to gain access above one's clearances.

Authorization is what this category deals with.

#### Example:

- Attackers with limited permissions manage to elevate their clearances by crafting a special request or running a particular sequence of code (e.g., Meltdown [16] and Spectre [17] attacks).

- Elevation to root-level privileges by means of Buffer Overflow or Return Oriented attacks.

Typical countermeasures are:

- Proper access control.

- Security code analysis.

- Security by design.

All the features above are briefly summarized with their corresponding threat in Table 2.1.

| Security property | Security threat        |  |

|-------------------|------------------------|--|

| Authentication    | Spoofing               |  |

| Spoofing          | Tampering              |  |

| Non-repudiation   | Repudiation            |  |

| Confidentiality   | Information Disclosure |  |

| Availability      | Denial of Service      |  |

| Authorization     | Elevation of Privilege |  |

Table 2.1: Security concerns with corresponding security threats suggested by the Security Development Lifecycle

#### 2.2 Formal methods

Formal methods used in computing systems use mathematical techniques to provide frameworks within which we can describe, develop and verify hardware and software systems. Unlike other approaches, formal methods adopt mathematical proof and rigorous reasoning to ensure "correct" behavior. As systems are becoming larger and more complex, safety and security turn up to be a critical issue, therefore formal methods provide another level of assurance.

Traditionally the verification of "correct" behavior has been carried out by extensive testing and simulation, but these two techniques are limited to finite conclusions. It has been demonstrated that testing is able to provide guarantees only under the conditions where the system does not fail, that is they cannot provide any guarantee about situations outside the test scenario. In contrast, formal methods offer the mathematical guarantee that a certain property is always true. Moreover, conventional simulation approaches yield only partial results quickly but they hardly reach full coverage. Formal verification, on the other hand, is capable to attain completeness, at least in principle [31, 32].

Generally, formal design is divided into a three step process:

Formal Specification In this phase, the designer, using a modeling language, methodically describes the system. A modeling language is a predefined grammar intended to model complex systems by means of primitive types and constructs. This step is analogous to some software engineering techniques developed to translate natural language-defined specifications into formal/functional requirements. Both approaches help designers to clarify and settle their goals, problems, and solutions.

Verification As previously mentioned, formal methods are distinguished from other specification techniques by their heavy emphasis on provability and correctness. Since formal methods take advantage of rigorously defined logics, the engineer is therefore building a set of properties or theorems about the system. If the property is proven to be true, the corresponding requirement becomes always true, no matter the conditions. The complexity of proving a theorem has driven the verification community to developing automated theorem proving tools.

**Implementation** The last step is the implementation: translating the formal model into code. This *should* be the last step, but very often designers are forced, by time constraints, to implement the system and only after that

perform the verification.

#### 2.2.1 Benefits Of Formal Models

As already mentioned, formal methods offer the great insurance of provability.

- **Precision**: In contrast to other design approaches, formal methods require very rigorously defined goals and techniques. One of the greatest advantages of formal methods is the elimination of ambiguity. This is particularly relevant for safety critical and security critical systems, where ambiguity can be extremely dangerous.

- Discipline: Formal methods require rigor, this forces formal engineers to think thoroughly while designing the system. Specifically, a formal proof of correctness demands a formal specification of requirements. This approach has been demonstrated to be more effective in identifying faulty reasoning than in traditional design [33].

#### 2.2.2 Weaknesses Of Formal Methods

- Expense: Formal methods are usually more expensive than traditional approaches. Nonetheless, it is debatable how much this "more expensive" is for formal methods. Generally speaking, formal approaches are very costly at the beginning of the project, while becoming cheaper in time. This trend is exactly the opposite for standard development techniques. The expense varies from project to project, so the question arises: Is this large initial cost worth the effort?. Or in other words: Are the benefits of this formal approach greater than its disadvantages?.

- Usability: Modeling languages usually have the great strength to model anything and formal methods are extremely descriptive. Unfortunately, the same qualities require engineers to undergo through hard training and detailed skill acquisition. Moreover, formal methods generally have a steep learning curve.

• Scalability: Although there have been great efforts to improve scalability in formal methods, large designs are not quite feasible for most verification tools out there. The bright side is that the research in this field is still very active.

## 2.3 Formal Specification

A specification is a description of a system and of its desired properties. It is often used as higher level documentation alongside the implementation's documentation. Formal specification, in particular, describes the intended behavior of the system using a formal language, i.e., with mathematically-defined semantics and syntax. The great advantage of such language is that it provides an unambiguous method of description. This process, as already mentioned, helps uncover ambiguity and incompleteness.

The specification can be represented by two broad classes of formalisms:

- Logics: propositional, modal (temporal), first-order predicate, higher-order, etc.

- Automata/language theory: omega automata, finite state, etc.

They tend to have different pros and cons, making each one of those most suitable for a specific use case.

The desired behaviors are called *properties*. They can describe functional, safety or security correctness. Properties are generally divided in two classes:

- Safety property: it asserts that nothing bad happens, e.g., an error condition, or a deadlock state, or that A and B must not have simultaneous access to a shared resource. If false, it can be detected by finite sequences. For instance, confidentiality properties belong to this category.

- Liveness property: it asserts that something good eventually happens, e.g., a progress as in the opposite of starvation, if A is waiting to enter a critical section, it will eventually be allowed to do so. It can only be proved false by infinite sequences. For instance, availability properties belong to this category.

## 2.3.1 Formal logic

A logic is an organization of a set of symbols (called alphabet), a language over the alphabet to make statements, a set of rules that prescribe the construction of sentences (grammar or syntax rules) and a semantics (interpretations of sentences). Logics share some common characterizing properties:

- Consistency: all theorems can be true at the same time or that do not contradict each other.

- Validity: if the premises are true, it is guaranteed that the conclusions are also true.

- Completeness: every formula can be derived using the formal system, i.e., is a theorem of the system.

- Soundness: if and only if every formula that can be proved in the system is logically valid with respect to the semantics of the system, i.e., if any formula is a theorem of the system, it is true.

- Expressivity: the ability to express concepts in the system.

There are four types of Logic:

- Propositional logic: a formula is expressed by combining atomic propositions and logical connectives, e.g., traditional Boolean algebra

- Modal/temporal logics: modal logic affects the circumstances (the time in temporal logics) in which we deem an assertion to be true

- First-order logic (Predicate logic): uses quantified variables, e.g., there exists  $(\exists)$  and for all  $(\forall)$

- Higher-order logic: an extension of the first-order logic, includes also quantifiers over sets and functions (predicates)

The application of a logic to verification is as follows:

- The specification is expressed as a formula

- The implementation is expressed as a formula or as a semantic model

There are two possible cases:

- Formula: Verification of relationships (implications or equivalences) between the implementation and the specification. This is the case of theorem proving.

- $Model \models Formula$ : Verification of a semantic relation between a model and a specification formula (property). In this case both model checking and theorem proving can be used.

Finally we express the relations between the implementation (Imp) and the specification (Spec) in the following manner:

- $Imp \equiv Spec$ : the implementation is equivalent to the specification

- $Imp \implies Spec$ : the implementation logically implies the specification

- $Imp \models Spec$ : the implementation is a *semantic model* in which the specification is true

## 2.4 Formal verification

We are now going to talk more specifically about Formal Verification (FV). Let us remind some basic concepts.

"Formal Verification is the process of constructing a proof that a target system will behave in accordance with its specification."

In addition, FV has the following features:

- Mathematical reasoning is used in order to prove that the implementation satisfies the specification

- Correctness holds no matter the input values, i.e., the specification is always satisfied

- Formal verification implicitly covers all cases

- Must provide:

- A formal specification (high-level behavior or properties)

A formal description of the *implementation* (a model, functionally and observationally, equivalent to implementation or design at higher level of abstraction)

Full coverage makes formal verification an excellent alternative able to track down bugs that are not detected by standard verification techniques. Formal verification can even detect bugs earlier in the development process than other techniques. Although reliable and exhaustive, this approach still needs improvements and it is often used in conjunction with standard simulation-based systems. While FV performs *complete* verification of correctness but requires *partial* (abstract) models, simulation is able to run the *complete* model leading to *partial* verification.

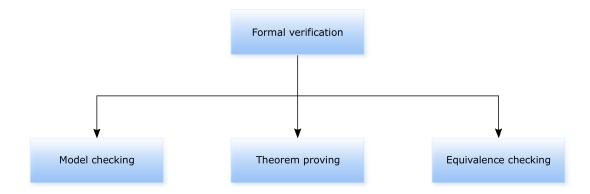

Formal verification techniques can be divided in three main classes, as depicted in Figure 2.1, and they are described in the following subsections.

Figure 2.1: Formal verification techniques

## 2.4.1 Theorem proving

Theorem proving is the process of constructing and verifying a proof using mathematical reasoning. If the theorem is proven it means that the implementation meets design requirements (or specifications). Logic is used for reasoning about the system under consideration, it can express complete proofs of correctness or of absence of failures.

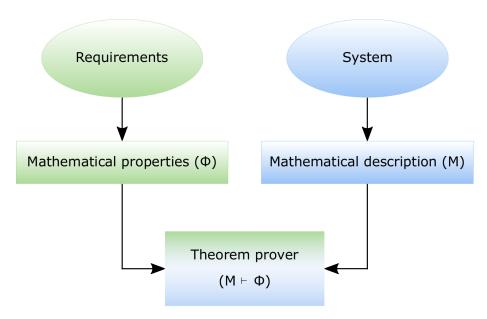

Theorem proving can be split in the following steps:

1. Using a formal mathematical logic, define mathematical definitions to create a model of the system.

- 2. From the definitions derive the properties that express some system's behaviours.

- 3. Properties and model are fed into a theorem prover to carry out the proof.

The same steps are depicted in Figure 2.2

Figure 2.2: The procedure of Theorem proving

#### 2.4.2 Equivalence checking

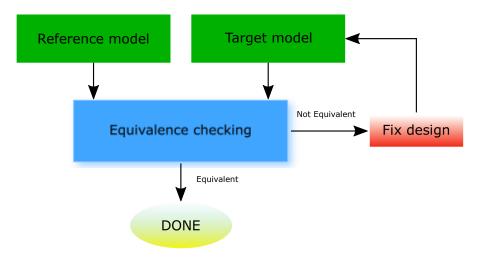

Equivalence checking is the process of verifying that two designs are functionally the same, that is: Given two designs, prove that for all possible input stimuli their corresponding outputs are equivalent. There are two variants of equivalence checking, they both verify that two models are functionally identical:

- At different levels of abstraction.

- At the same level of abstraction but with different implementations.

The process is depicted in Figure 2.3: select a reference model to be a role model and a target model to be the design under test, build the so-called *product machine* composed of the two models and a comparison circuitry for the outputs, provide the input stimuli and run the machine, eventually collect the binary output. If the

output is true, the two models are functionally equivalent, otherwise they differ and do not have the same behavior.

Figure 2.3: The procedure of Equivalence checking

# 2.5 Model checking

Model checking, also known as Formal property verification, is a state-based approach to formal verification. It is used to verify finite state concurrent systems. A big advantage of model checking is that the verification process can be automated through a proper model checking tool.

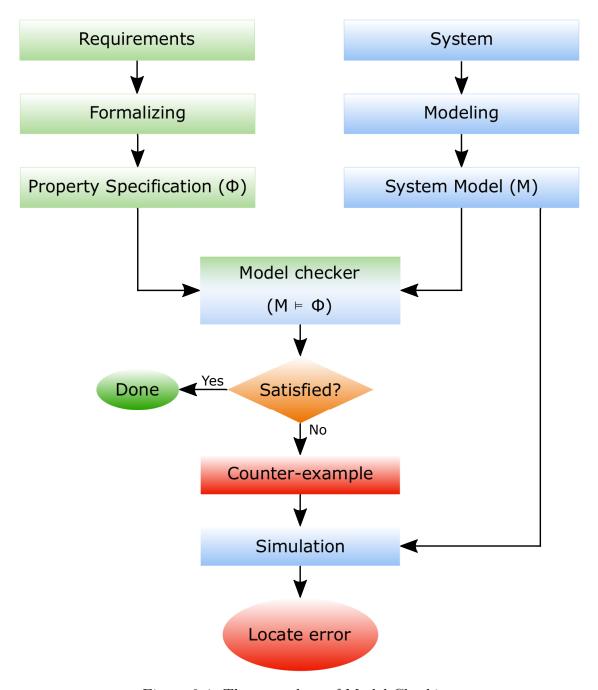

The essential idea behind model checking is depicted in Fig. 2.4:

- 1. Modeling: describe the system with a formal language. The design is usually modelled as a set of states and a set of transitions that define how the system evolves from a particular state to another in response to some stimuli. This step produces a formal system model M.

- 2. Specification: define the desired properties using a proper specification language (usually the same as in the previous step). This step produces a property  $\phi$  or a set of properties.

- 3. Verification: M and  $\phi$  are fed to a model checking tool (or *model checker*) that runs automatically. If the answer of the model checker is positive (true) then the model is proven to satisfy the property. Otherwise, the model checker

generates a counter-example, i.e., the stimuli that violate the property. The counter-example is then used to simulate the model M and find the unwanted behavior.

Figure 2.4: The procedure of Model Checking

Research over model checkers have brought significant enhancements in terms

of efficiency, automatism, supported languages, features, etc. A standard model checker nowadays is able to, given sufficient resources, terminate with a binary answer in reasonable time. There are some caveat though. Since the model checking tools usually perform an exhaustive search over the finite state space of the system, large designs represent a serious problem for model checkers for a problem called *state space explosion* which we are going to talk about below. The theory of computation provides limitations on the decidability of an algorithm. Notably, an important undecidable problem is the *halting problem*: it cannot exist an algorithm that decides if an arbitrary program eventually terminates. As a consequence, there are restrictions on what can be verified automatically.

### 2.5.1 Modeling

The first step is the conversion of the design into an abstract formal model accepted by a model checker. As the state space could be very large, the model should be as small as possible in order to minimize the size of the state space search. This step is sometimes performed automatically, for example for hardware systems. In the majority of cases, however, human effort and guidance is necessary. The input design could vary for its form and its nature, it could be hardware or software, it could represent a gate level description, a RTL description, a behavioral model, or even high level specifications. The choice of the formal language to describe is particularly relevant for efficiency, support, expressivity, etc. In some cases, even an ad-hoc and fine-tailored logic is used. The property specification (described in the next subsection) is usually performed with the same logic or language. Despite this variety, a generic design is commonly seen as a set of concurrent (i.e., interacting) systems. Each system is represented as a Finite State Machine (FSM) and has a finite number of states. Certainly there are systems with infinite states and the literature is plenty of contributions on this topic but they are out of scope for this work. When given an input, the FSM can change from one state to another. This is called *transition*. The set of states, the initial state and set of transitions characterize the FSM. Following this approach, the whole system can be seen as a FSM, which is the composition of the FSMs associated with each component. The process of modelization therefore consists of creating a complete FSM description of the system. Automata theory provides a plethora of methods to describe finite state automata: Pushdown automata (PDA), Linear bounded automata (LBA), Turing machines, Buchi automata, etc. Model checking methods generally model the behavior of the system by means of Kripke structures. A Kripke structure is a variation of a transition system and is essentially a node-labeled graph. System states are represented by the nodes of the graph and each node is labeled with binary information (i.e., atomic propositions described with the chosen logic) at that state. State transitions, that is the evolution of the system, are represented by the edges of the graph.

#### 2.5.2 Specification

This process involves the following question: What properties must the system design satisfy? This is the step where we define the key properties to be verified: they could describe a particular system's behavior or model a certain feature, e.g., the confidentiality of a secret key. Generally, the specification is expressed with the same formalism as the previous step. The class of temporal logics has been proven to be very useful because of their inherent capability to describe how the system evolves over time. Although the meaning of a statement is constant in time, its truth value may vary in time. Temporal logic always has the ability to reason about a timeline. In particular, time is implicitly built within the logic, without the need for an explicit definition. A common classification for temporal logics is between linear time logics (e.g., LTL) and branching time logics (e.g., CTL and CTL\*). The difference is whether time is assumed to have a linear or branching structure. In the last years, though, new types of temporal logics have been proposed to respond to specific problems. Key examples are HyperLTL and HyperCTL\* [34]: they have been proposed to provide support for a new class of properties, namely hyperproperties [35]. Overall, this process is particularly time consuming because of some crucial issues: for example, consistency (i.e., whether the given specification is consistent with higher level requirements) or completeness (i.e., whether the given specification cover all the behaviors of the system).

#### 2.5.3 Verification

In theory, the verification step is completely automatic. In practice, however, human effort is often needed. For instance, the analysis of the verification results can provide useful insights on the system specification and implementation. If the model does not satisfy the given property, the model checker generates a counter-example, i.e., an error trace that can be used to simulate the system. The simulation helps the engineer to track down where the error occurred. Once the bug is found, the engineer modifies the model and repeats the verification process. The verification process can also lead to false negatives and false positives, that can be introduced by:

- inconsistent specification

- incorrect formalization of the specification

- incorrect modeling of the system

The verification step could fail to terminate normally or not terminate at all. This is due to the size of the model, which leads to the state space explosion. The major limitation of model checking is the *state explosion problem*. The problem occurs when the whole model is computationally too big, that is composed of too many components or few large components. The composition of two FSMs, representing two concurrent components, is performed by taking the Cartesian product of the corresponding state spaces. This leads to an exponential grow, in the number of concurrent processes involved, of the overall state space of the system. An exhaustive search over this large state space may be unfeasible even for well-optimized linear-time algorithms. The verification community, in order to cope with this problem, has offered two approaches:

- Symbolic algorithms

- Partial order reduction

# 2.6 Modelling Concurrent systems

## 2.6.1 Transition systems

Transition systems are usually used to describe and model system behaviors. A transition system are represented as directed graphs: edges represent transitions (i.e., state changes), nodes model states. A state provide information on the system at a certain moment of time. The state for a traffic light, for example, is the current color of light. Likewise, the state for a sequential computer program is represented by the set of variables, their current values and the value of program counter. In the hardware field, a state is typically the set of registers and their current values. Transitions describe the evolution from state to another. A transition for the traffic light is the change of color. A transition for a program is the execution of an instruction and the corresponding change of variable values as well as the program counter. For hardware circuits, a transition is the change of registers and signals.

Regardless of the actual formalism employed for their specification, the (operational) semantics of reactive systems is fully described by the general framework provided by transition systems.

**DEFINITION 1.** A labeled transition system is a tuple  $\mathcal{T} = (S, I, E, \delta)$  composed of:

- a set S of states

- a subset  $I \subseteq S$  of initial states

- a set E of (action) labels

- a transition relation  $\delta \subseteq S \times E \times S$

A run of  $\mathcal{T}$  is an  $\omega$ -sequence  $\rho = s_0 \stackrel{e_0}{\Rightarrow} s_1 \stackrel{e_1}{\Rightarrow} \dots$  of states  $s_i \in S$  and labels  $e_i \in E$  such that  $s_0 \in I$  is an initial state and  $(s_i, e_i, s_{i+1}) \in \delta$  is a transition for all  $i \in N$ . A state  $s \in S$  is called reachable in  $\mathcal{T}$  if there exists some run  $s_0 \stackrel{e_0}{\Rightarrow} s_1 \stackrel{e_1}{\Rightarrow} \dots$  of  $\mathcal{T}$  such that  $s_n = s$  for some  $n \in N$ .

The goal of verification algorithms is to decide whether a transition system satisfies a given property. Properties represent system behaviors that verification engineers want to check. Some elementary binary (i.e., true or false) propositions form a property. This idea is behind Kripke structures, a variation of the transition system. Kripke structures extend a transition system by adding an interpretation of atomic propositions over states.

**DEFINITION 2.** Let AP be a set of atomic propositions. A Kripke structure  $K = (S, I, E, \delta, \lambda)$  extends a transition system by a mapping  $\lambda : S \to 2^{AP}$  that associates with every state  $s \in S$  the set of propositions true at state s. The runs of a Kripke structure are just the runs of its underlying transition system.

The labeling function  $\lambda$  maps any state s to a set  $\lambda(s) \in 2^{AP}$  of atomic propositions, this mean we can evaluate formulae of propositional logic built from the propositions in AP.

$\lambda(s)$  intuitively stands for exactly those atomic propositions  $a \in AP$  which are satisfied by state s. Given that  $\Phi$  is a propositional logic formula, then s satisfies the formula  $\Phi$  if the evaluation induced by  $\lambda(s)$  makes the formula  $\Phi$  true; that is:  $s \models \Phi \text{ iff } \lambda(s) \models \Phi$ .

#### 2.6.2 System invariants

Safety properties usually describe that "something bad should never happen". For example, a computer program should never go in deadlock. Or at most one process is in its critical section at any time. This particular type of properties states that a condition must always be true, that is  $s \models P$  holds for all reachable system states s. We call this a system invariant or simply invariant. Invariants are, as we showed, a special case of safety properties.

**DEFINITION 3.** A property  $P_{inv}$  over AP is an invariant if there is a propositional logic formula  $\Phi$  over AP such that

$$P_{inv} = \left\{ A_0 A_1 A_2 \dots \in (2^{AP})^{\omega} \mid \forall j \ge 0. \ A_j \models \Phi \right\}.$$

$\Phi$  is called an invariant condition of  $P_{inv}$ .

Model checking algorithms that decide whether a finite Kripke structure  $\mathcal{K}$  satisfies an invariant property P are conceptually easy: they can simply enumerate

the reachable system states and check that P holds true in every one of them. Termination is guaranteed by the finiteness of K.

## 2.7 Linear Time Temporal Logic

Given a Kripke structure K, we are sometimes interested in some properties, such as:

- Is it always possible to reach an initial state? In other words, can the system be re-initialized?

- Does K contain states that do not satisfy an invariant?

- Does K have "bad" states, such as deadlock states where only the  $\tau$  action is enabled?

- Does the system have livelocks (i.e., when the system is not in deadlock but some process is)? In other words, are there traces of  $\mathcal{K}$  such that, after some time, a certain action is never executed or a "good" state is never reached?

Temporal logic provides a language in which such properties can be formulated.

Temporal logics can be categorized for their syntactic features, or for their semantic structures. In particular, the underlying nature of time in temporal logics can be either linear or branching. If at each moment of time there is only one possible successor we are talking about linear time logic. On the contrary, if we have a tree-like time structure we say it is a branching time logic. This section describes Linear Temporal Logic (LTL).

Linear temporal logic has been introduced by Pnueli [36] as a tool for the specification and verification of reactive systems.

The syntax of LTL-formulae is made up by the following basic ingredients:

- atomic propositions  $a \in AP$  ( that corresponds to state label a in a transition system)

- Boolean connectives such as conjunction  $\wedge$  and negation  $\neg$

• basic temporal modalities () (pronounced "next") and U (pronounced "until")

Usually, the atomic propositions are assertions over control variables (e.g., the program counter or program variables such as " $x \geq y$ " or "x > 5"). The Omodality is a unary prefix operator and takes a LTL formula as argument. Formula  $\bigcirc \varphi$  holds at the current moment, if  $\varphi$  holds in the next "step". The U-modality is a binary infix operator and takes two LTL formulae as arguments. Formula  $\varphi_1 \cup \varphi_2$  holds at the current moment, if there is some future moment for which  $\varphi_2$  holds and  $\varphi_1$  holds at all moments until that future moment. LTL formulae over the set AP of atomic proposition are formed according to the following grammar:

$$\varphi ::= true \mid a \mid \varphi_1 \wedge \varphi_2 \mid \neg \varphi \mid \bigcirc \varphi \mid \varphi_1 \mathsf{U} \varphi_2$$

where  $a \in AP$ .

The U-modality lets us derive the temporal modalities  $\square$  ("always", from now on forever) and  $\lozenge$  ("eventually", sometimes in the future) as follows:

$$\Box \varphi \stackrel{\text{def}}{=} \neg \Diamond \neg \varphi \qquad \qquad \Diamond \varphi \stackrel{\text{def}}{=} true \cup \varphi$$

$\Box \varphi$  is satisfied if and only if it is not the case that eventually  $\neg \varphi$  holds. This is equivalent to the fact that  $\varphi$  holds from now on forever.  $\Diamond \varphi$  ensures that  $\varphi$  will be true eventually in the future. By combining the temporal modalities  $\Diamond$  and  $\Box$ , new temporal modalities are obtained as follows:

$$\Box \Diamond \varphi \text{ "infinitely often } \varphi$$

"

$$\Diamond \Box \varphi \text{ "eventually forever } \varphi$$

"

## 2.8 Branching Time Temporal Logic

Instead of relying on a linear notion of time (i.e., an infinite sequence of states), branching time temporal logic uses a branching notion of time (i.e., an infinite tree of states). Branching time is generally represented as an infinite tree of states because at each moment there may be several different possible futures. Branching time logic allows us to express properties of *some* or *all* computations starting

from a particular state. The support is provided by new path quantifiers, such as an universal path quantifier (denoted  $\forall$ ) and an existential path quantifier (denoted  $\exists$ ). For example, the property  $\exists \Diamond \Phi$  indicates that there exists a computation along which  $\Diamond \Phi$  holds. That is, it states that there is at least one possible computation in which a state that satisfies  $\Phi$  is eventually reached.

A notable branching time logic used in formal verification is Computation Tree Logic (CTL) and it has been introduced by Clarke and Emerson [37]. CTL formulae are classified into state and path formulae. The former are assertions about the atomic propositions in the states and their branching structure, while path formulae express temporal properties of paths. Given a set AP of atomic propositions, CTL state formulae are generated by the following grammar:

$$\Phi ::= true \mid a \mid \Phi_1 \wedge \Phi_2 \mid \neg \Phi \mid \exists \varphi \mid \forall \varphi$$

where  $a \in AP$  and  $\varphi$  is a path formula. CTL path formulae are generated by the following grammar:

$$\varphi ::= igcip \Phi \ \Big| \ \Phi_1 \ \mathsf{U} \ \Phi_2$$

where  $\Phi$ ,  $\Phi_1$ ,  $\Phi_2$  are state formulae.

## 2.9 CTL\*

CTL\* is an extension of CTL and it is a superset of both CTL and LTL. It allows path quantifiers  $\exists$  and  $\forall$  to be arbitrarily nested with linear temporal operators such as  $\Box$  and  $\forall$  as for CTL, CTL\* formulae are classified into state and path formulae. Given a set AP of atomic propositions, CTL\* state formulae are generated by the following grammar:

$$\Phi ::= true \mid a \mid \Phi_1 \wedge \Phi_2 \mid \neg \Phi \mid \exists \varphi$$

where  $a \in AP$  and  $\varphi$  is a path formula.

CTL\* path formulae are generated by the following grammar:

$$\varphi \, ::= \, \Phi \, \left| \, \varphi_1 \, \wedge \, \varphi_2 \, \right| \, \neg \varphi \, \left| \, \, \bigcirc \varphi \, \right| \, \varphi_1 \, \mathsf{U} \, \varphi_2$$

where  $\Phi$  is a state formula, and  $\varphi$ ,  $\varphi_1$ , and  $\varphi_2$  are path formulae.

#### 2.10 $\omega$ -automata

Transition systems, even if they are finite, usually generate an infinite set of runs, each of which is an infinite sequence of states.  $\omega$ -automata are usually used to specify behavior of systems that are not expected to terminate, such as control systems, operating systems, hardware systems. For example, we would like to verify, for such systems, a property that states "for every action, there eventually be a counter-action". A finite sequence of states cannot prove that the property is satisfied. This theory has been given notable contributions over the years (Büchi [38], Muller [39], Rabin [40], etc.) but we limit the discussion to Büchi automata.

**DEFINITION 4.** A Büchi automaton  $\mathcal{B} = (Q, Q_0, \Sigma, \delta, F)$  is given by:

- a finite set Q of states

- $a \ set \ Q_0 \subseteq Q \ of \ initial \ states$

- $\Sigma$  is an alphabet

- a transition function  $\delta: Q \times \Sigma \to 2^Q$

- a set  $F \subseteq Q$  of accepting (or final) states.

A run of  $\mathcal{B}$  over a sequence  $\sigma = a_0 a_1 \dots$  where  $a_i \in \Sigma$  is a sequence  $\rho = q_0 q_1 \dots$  of states  $q_i \in Q$  such that  $q_0 \in Q_0$  is an initial location and  $(q_i, a_i, q_{i+1}) \in \delta$  holds for all  $i \in N$ . The run  $\rho$  is accepting if it contains an infinite number of states  $q_k \in F$ .

Büchi automata, as we have defined them, operate on  $\omega$ -sequences of subsets of  $\Sigma$ , and this is in close correspondence with the interpretation of (linear time) temporal logic over Kripke structures. Indeed, any run  $s_0 \stackrel{e_0}{\Longrightarrow} s_1 \stackrel{e_1}{\Longrightarrow} \dots$  of a Kripke

structure  $\mathcal{K}$  can be identified with the corresponding sequence  $\lambda(q_0)\lambda(q_1)\dots$  where  $\lambda$  is the propositional valuation of states of  $\mathcal{K}$ . In this sense, propositional temporal logic formulae and Büchi automata operate over the same class of structures.

## 2.11 Symbolic Model Checking

The notions we have seen so far (transitions systems, Kripke structures, Büchi automata, etc.) are intrinsically based on states, thus model checking algorithms operate on states too. Efficient implementations of data structures manipulating states are therefore needed. Explicit enumeration (i.e., brute force) is not a viable approach since it only allows few millions of states. An efficient alternative that has been proposed is the symbolic representation of states, since this method would allow compact data structures and therefore more efficient algorithms that operate on them. The most prominent algorithms depend on a binary encoding of the states. Also switching functions have been targeted for performance optimization: ordered binary decision diagrams (BDD) are special structures designed to make them compact and efficient.

Originally proposed by Bryant [41], ordered BDDs perform a compactification of binary decision trees. The basic idea is to prune redundant fragments of a binary decision tree. For example, subtrees with all leaf nodes having the same value (i.e., constant subtrees) can be collapsed into a single node. Same for isomorphic subtrees.

BDDs are extensively used in the context of SAT-based model checking where the model-checking problem is reduced to the satisfiability problem for propositional formulae (SAT). BDDs have represented a technological breakthrough for the implementation of model checking algorithms. A major benefit of BDDs is that they provide canonical representation of sets, and therefore set equality can be decided by simple pointer comparison. Moreover, Boolean operations can be performed in polynomial time.

## 2.12 Bounded Model Checking

Even though BDDs are a powerful data structure used for the representation of Boolean functions, other techniques can be quite useful, especially when a complete verification is not feasible. SAT algorithms, for example, decide the satisfiability of formulae of (non-temporal) propositional logic. This approach is not based on canonical representations of Boolean functions, ruling out the calculation of fixed points. Bounded Model Checking (BMC) [42] algorithms attempt to find an execution of finite length that violates the property of interest. The maximum size of a potential counter-example can (at least in theory) be determined from the size of the model and the formula to be verified. For example, an invariant holds for a Kripke structure if it is true for all prefixes of runs whose length is at most that of the longest loop in the graph of  $\mathcal{K}$  (called the diameter of  $\mathcal{K}$ ).

Bounded Model Checking (BMC) [42] is an iterative search for counterexamples to prove false a desired property p up to a given bound k. The bound k greatly limits the state space size so that it can be used in some cases where other model checking techniques fail. On the contrary, the bound k has the disadvantage to make this approach not complete, that is BMC cannot prove the absence of errors. After a run with a certain k, if no counterexample is given then the user increases the bound until either some pre-known upper bound is reached, the problem becomes intractable or a bug is found.

The basic idea of BMC is to express all state paths of length k by unrolling k times a system transition relation T.

$$T^{k}(X^{0...k}) = \bigwedge_{i=0}^{k-1} T(X^{i}, X^{i+1})$$

(2.1)

Although BMC has become an effective approach in the verification process, even with large models, it can only guarantee the correctness of a property until a given bound, i.e., the verification method is not complete. This is where Unbounded Model Checking (UMC) comes into play. The main difference between BMC and UMC is scalability. Support for UMC has been improved over the years, with a number of techniques proposed. BDDs are now an established major approach for UMC and BDD-based tools are very efficient, often with large designs, but there

are other contributions. For instance, the ability to check reachability fix-points is crucial for UMC. Property Directed Reachability (PDR) aims to prove completeness for the circuit unrolling or backward, forward or mixed reachability analysis.

The industry nowadays typically uses both BMC and UMC as complementary methods. A typical approach is to use BMC first to find shallow bugs very quickly, the bound is incremented until the problem becomes intractable, then UMC is applied to prove that the property is correct. In other cases BMC and UMC run in parallel, as the first technique finds a solution, the other is aborted.

## Chapter 3

# Secure Embedded Architectures: Taint Properties Verification

The following chapter has been published as peer-reviewed article in [43].

#### 3.1 Introduction

A large number of assorted embedded systems nowadays constitute a rising trend in industry, forming the so-called Internet of Things (IoT). This direction will lead, analysts say, to billions of connected devices that enable new functionalities and services. The applications are everywhere: self-organizing devices connected in a common network (e.g., robot swarms), connected smart environments, industrial control systems. Most of these devices do not operate alone, their work is coordinated and parallel, so that the key feature is the interconnection between them. Whenever they send or receive sensitive or critical information using public networks or communications channels accessible to potential attackers, they should ideally provide basic security functions such as data confidentiality, data integrity, and user authentication. These basic security functions are the assumptions that underlie the paradigm of secure communications. Nowadays, most of the embedded systems use this paradigm in automotive, sensing, medical, financial, military and many other applications [44]. As a consequence, providing a proper security verification is a crucial task in this kind of environments, not only at the device level but also from the networking point of view, thus protecting them from a wide range of attacks [45, 46, 47, 48]. However, the major research focus is on verifying only the correctness of encryption algorithms and their implementation in software and hardware, neglecting the stream of data (i.e., information flow). Admittedly, our research has been guided by the following questions:

- Is there a way to read sensitive data from a specific location?

- Is there a way to *modify* sensitive data?

- Are there failure states that would compromise the security of the system?

Taking these questions as a starting base, we chose to address them with a specific information flow approach in security.

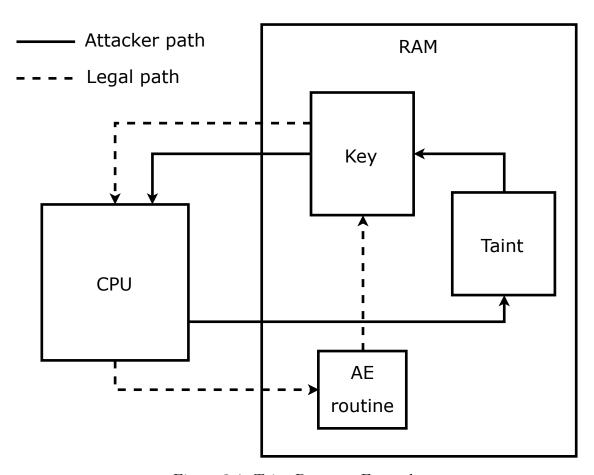

In [49] Taint properties are taken as a role model for expressing many security requirements that involve information flow and access control. A taint is a malicious seed that is injected into source, flows through the system until it reaches its sink. It is easy to notice that this is a natural way to capture confidentiality requirements as we will in Section 3.7. For instance, confidentiality can be verified by setting a hardware secret as the source and an untrusted identity, e.g., a user program location, as the destination. In a similar way if we set an untrusted identity as the source and a security-sensitive signal as the destination we are verifying integrity [50].

This chapter introduces a formal methodology to express generic security requirements as information flow properties in terms of Taint Properties. In details, our contributions are the following:

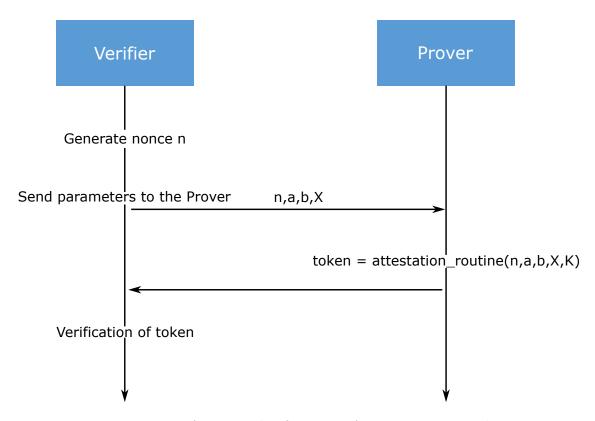

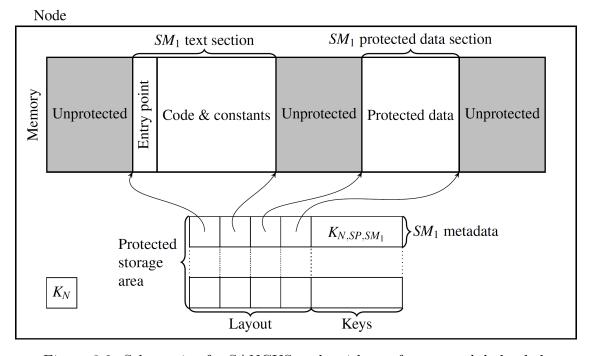

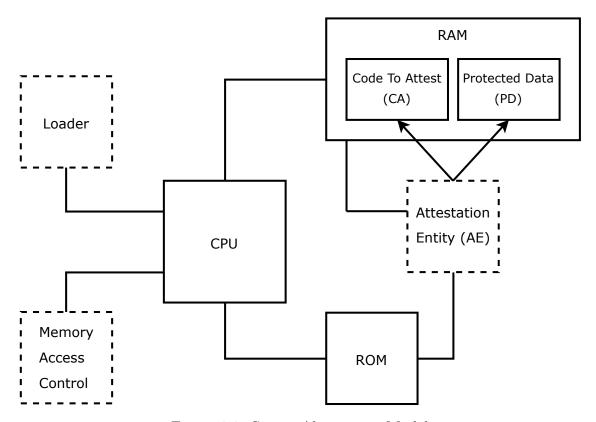

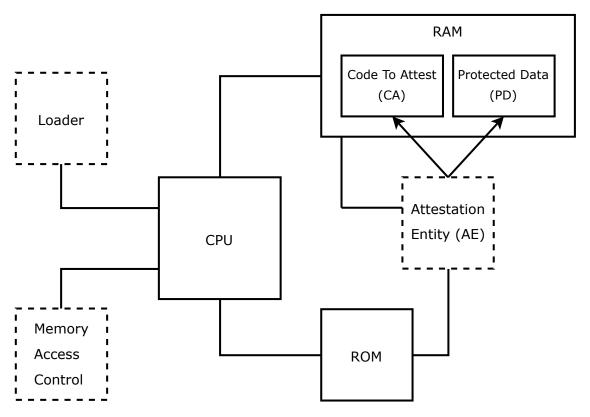

• we perform abstraction and refinement steps on two secure embedded architectures: SMART [51] and SANCUS [52]. They are two prominent representatives of Remote Attestation: a procedure to attest (i.e., check) the current internal state of an untrusted remote embedded device (*Prover*) by a trusted entity (*Verifier*) [53, 54]. SMART is a simple architecture that provides support for dynamic root of trust in a remote embedded device. It requires small changes and little cost as it is based on hardware/software co-design. SANCUS is a comprehensive framework for Remote Attestation and message authentication. It is module-based and it provides also a networking scheme for communications. It works with clusters (i.e., sets of microprocessor-based systems).

- we show how to express security requirements, such as confidentiality, integrity, key secrecy, isolation, etc., as Taint properties.

- we define a portfolio of Taint properties for the selected abstract models.

- we perform formal verification on the set of Taint properties and we present experimental results supporting our claim

Section 3.2 provides some background knowledge on the topics we use in this work. Section 3.3 recalls related works and compares them with our approach. Section 3.6 introduces a methodology to perform abstraction to extract an abstract model of the two selected architectures. Section 3.7 presents a set of Taint Properties and we provide a formal analysis for security requirements. We also show how to use them with a standard model checker. In Section 3.8 we offer experimental results that support our claim. Finally, Section 3.9 concludes the chapter with summarizing conclusions along with some remarks on future work.

## 3.2 Background

## 3.2.1 Trusted Computing Base and root of trust

There is plenty of empirical experimental evidence that conventional embedded systems are not secure. This simple assertion has become evident in the past and is nowadays an universally accepted truth. The ubiquity of flaws and secure-related issues makes this a pressing matter. Furthermore, reconciling after discovery of the issue or even after the public disclosure of an attack has been shown an inadequate approach to providing truly secure systems. Though there have been plenty of improvements over the years in terms of efficiency for verification methods, both formal and non-formal, to date there is no technique which is proved to be complete and sound for every CPS. Most of them, indeed, are not able to give the upmost assurance that all security vulnerabilities have been removed from the system. Therefore, the only sound approach to this end is deemed to be the so called security by design: security must be embedded into the system in the design phase. In other words, the fundamental proof that a system is secure must be focused, first, on the security analysis of its design and, eventually, on its implementation. Hence, a secure computer system must involve mechanisms that are sufficient

to guarantee its security in all circumstances, and it must be possible to provide compelling evidence that those mechanisms are entirely adequate to their task. Such trustworthy computing or, as it widely known, Trusted Computing requires a Trusted Computing Base (TCB), the core set of functionality that is assumed to be secure, to provide secure primitives to the system. The TCB typically comprises hardware and software components, e.g., hardware accelerated cryptographic engines, software libraries, secure OS services, etc. During an execution of the system, the chain of TCB involved in the computation forms the root of trust, a way to establish trust in the execution environment. So only an execution environment equipped with a root of trust is really "real" trusted. Efforts have been made to regulate this approach and led the Trusted Computing Group (TCG) to produce a standard, later accepted by ISO, In particular, TCG defines a Trusted Platform Module (TPM) as a specialized hardware with security enforced capabilities (e.g., encryption/decryption) and provides the foundation for the host root of trust. For further details, refer to the corresponding ISO standard [55].

#### 3.2.2 Remote attestation