# POLITECNICO DI TORINO Repository ISTITUZIONALE

# A 300mV-Supply Standard-Cell-Based OTA with Digital PWM Offset Calibration

# Original

A 300mV-Supply Standard-Cell-Based OTA with Digital PWM Offset Calibration / Pedro, Toledo; Aiello, Orazio; Crovetti, PAOLO STEFANO. - STAMPA. - (2019). (Intervento presentato al convegno 2019 IEEE Nordic Conference on Circuits and Systems (NorCAS) tenutosi a Helsinki (FI) nel 29-30 Ottobre 2019) [10.1109/NORCHIP.2019.8906958].

Availability:

This version is available at: 11583/2758513 since: 2020-04-22T16:07:52Z

Publisher:

**IEEE**

Published

DOI:10.1109/NORCHIP.2019.8906958

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

# Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A 300mV-Supply Standard-Cell-Based OTA with Digital PWM Offset Calibration

Pedro Toledo<sup>1,2</sup>, Orazio Aiello<sup>1,3</sup>, Paolo S. Crovetti<sup>1</sup>

<sup>1</sup>Department of Electronics and Telecommunications (DET), Politecnico di Torino,

<sup>2</sup>Graduate Program in Microelectronics (PGMICRO), Federal University of Rio Grande do Sul,

<sup>3</sup>Electronics and Computer Engineering (ECE), National University of Singapore (NUS).

Abstract—This paper introduces a fully digital pulse-width-modulation (PWM) based calibration technique intended to dynamically compensate the input offset voltage due to process and mismatch in Ultra Low Voltage (ULV) Digital-Based Operational Transconductance Amplifiers (DB-OTA). Post-layout simulations on a DB-OTA circuit in 180nm featuring the proposed calibration technique demonstrate that process and mismatch related offset voltage can be effectively compensated by varying the duty cycle of a square wave signal with minimum performance overhead. The proposed OTA consumes just 7.34nW while driving a capacitive load of 80pF with a Total Harmonic Distortion lower than 2.26% at 100mV input signal swing. The total silicon area is 1,700  $\mu \rm m^2$ .

Index Terms—Digital-Based OTA Circuit, Digital Offset Calibration, Process variability, Ultra-Low Voltage (ULV), Internet of Things (IoT).

#### I. INTRODUCTION

Mostly digital, standard cell-based implementations of analog and mixed-signal functions have been intensively investigated over the last years to achieve Ultra-low Voltage (ULV), Ultra-Low-Power (ULP) operation as required in present day Internet of Things (IoT) applications at very low cost and design effort [1], [2]. In this scenario, fully digital implementations of many circuit building blocks have been proposed [3–10], including digital-based Operational Transconductance Amplifiers (DB-OTAs) [10], [11].

While digital OTAs can be extremely power and area efficient, their operation can be impaired by process variations and mismatch, which easily result in unacceptable offset voltage and reduced yield. Aiming to mitigate the effects of process spreads and mismatch, standard cells in critical parts can be designed with a strength which is much larger than minimum leveraging Pelgrom's law [12], analog layout guidelines should carefully followed and/or weighted element calibration networks are included to fine-tune the parameters of critical devices [10], as routinely done in analog circuits calibration [13]. In all the cases, however, robustness against process variations comes at the cost of significantly increased area and design complexity, which offset the advantages of DB-OTAs.

In this context, a novel, digital in concept approach to compensate process- and mismatch- variations in a DB-OTA with minimum area and performance overhead is proposed in this paper. The novel approach, which consists in the activation of a calibration device with a controlled duty cycle,

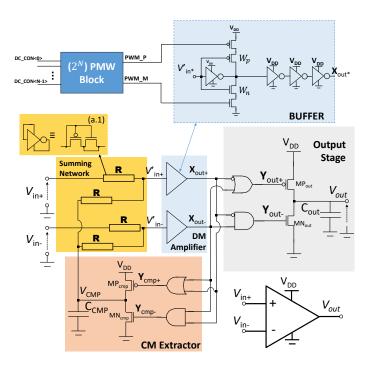

Fig. 1. DB-OTA schematic. N is the number of stages in the calibration inverter chain.

is demonstrated in a 300mV-power-supply standard-cell based OTA in 180nm CMOS on the basis of post-layout simulations.

The paper is organized as follows: in Section II, the DB-OTA operation is revised and the effects of process variations are highlighted. Then, the novel PWM calibration network is introduced in Section III and the effectiveness of the proposed calibration strategy is demonstrated in Section IV based on post layout simulations. In the same Section, the impact of the new calibration on the DB-OTA performance and power consumption is discussed and compared with other calibration approaches. Finally, in Section V, some concluding remarks are drawn.

# II. ULV DB-OTA CIRCUIT DESCRIPTION AND DESIGN

In this section, the operation principle of the DB-OTA first presented in [11] and then adopted in [10] to design an ULV OTA in 180nm is reviewed. Then, the network introduced in [10] to compensate process variations, which requires some custom analog design and layout effort, is focused and it is

replaced by a fully-synthesizable PWM modulator to make the digital OTA design fully compatible with a digital flow and to further reduce the overall design effort.

#### A. Digital-Based Differential Circuit Description

The schematic of a DB-OTA is shown in Fig. 1. The circuit is made up of a Differential-Mode (DM) amplifier, of a Common-Mode (CM) extractor loop, of a summing network and of an output stage, as in [11]. The main goal of this topology is to implement the same functionality of the classical CMOS differential stage with digital gates, i.e., to amplify the differential input signal  $v_d = (V_{\rm in+} - V_{\rm in-})$  while being insensitive to common mode input signal variations  $v_{\rm cm} = \frac{(V_{\rm in+} + V_{\rm in-})}{2}$ . To reach these goals, the DM Amplifier, which is formed by two digital buffers, is used to sense the level of the input voltages w.r.t. the buffers voltage tripping points  $(V_{\rm T})$  resulting in four possible logical outputs:  $(X_{\rm out+}, X_{\rm out-}) = (0,0), (1,1), (1,0), (0,1)$ .

Whenever  $(X_{\text{out+}}, X_{\text{out-}}) = (0, 1), (1, 0)$  the *output stage* is activated and  $V_{\text{out}}$  is increased/decreased depending on  $v_{\text{d}}$ . Otherwise, when  $(X_{\text{out+}}, X_{\text{out-}}) = (0, 0), (1, 1)$ , the *CM Extractor* is turned on to correct the input CM signal.

Once it is sensed that the CM input signal must be corrected, the transistor  $MN_{cmp}$  ( $MP_{cmp}$ ) is turned on and  $C_{CMP}$  is properly discharged (charged) and the generated  $V_{CM}$  signal is then subtracted from the input through the *summing network* ( $V'_{in+(-)} = 0.5(V_{CMP} + V_{in+(-)})$ ). On the other hand, when the CM input component is within the CM input range, the transistors  $MP_{out}$  and  $MN_{out}$  are operated depending on the sign of  $v_d$  so that to charge or discharge  $C_{OUT}$  according to the input differential signal. A detailed analysis of the circuit under dynamic conditions can be found in [11].

# B. Process Variations and Calibration

The operation of the ULV DB-OTA can be severely impaired by process variations and mismatch in the trip points  $V_{\rm T}$  of the first inverters of the *DM amplifier*, which result in an input offset voltage [11]

$$V_{OFF} = \Delta V_T + \frac{I_{OUT}}{C_{OUT}} \Delta t_D \tag{1}$$

where  $\Delta V_{\rm T} = V_{\rm T1} - V_{\rm T2}$  is the difference between positive and negative path trip points and  $\Delta t_D$  is the difference in the propagation delays of the two branches of the DM amplifier.  $I_{OUT}$  is the output stage current capability. For minimum-size devices, in particular, the offset predicted by (1) can be easily large enough to saturate the DB-OTA, thus fully impairing the DB-OTA operation.

Since the trip points  $V_T$  depend on the aspect ratios of the pull-up and pull-down devices as

$$V_{\rm T} = \frac{\frac{\kappa T}{q} \log \left( \frac{I_{\rm DOp} {\binom{W}{L}}_{\rm P}}{I_{\rm DO_N} {\binom{W}{L}}_{\rm N}} \right) + \frac{V_{\rm DD}}{n_{\rm P}}}{\frac{1}{n_{\rm P}} + \frac{1}{n_{\rm N}}}$$

(2)

where the parameters have their usual definitions [14], the effects of process variations can be in principle compensated

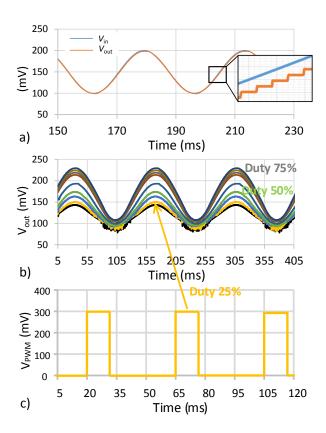

Fig. 2. a)  $V_{in}$  and  $V_{out}$  for  $C_{out} = 80 pF$ ,  $V_{amp} = 50 mV$  and  $f_{in} = 30 Hz$ . b)  $V_{in}$ ,  $V_{out}$  before calibration (black) and  $V_{out}$  after calibration (red) for  $C_{out} = 80 pF$ ,  $V_{amp} = 50 mV$  and  $f_{in} = 120 Hz$ . c) PWM calibration signal.

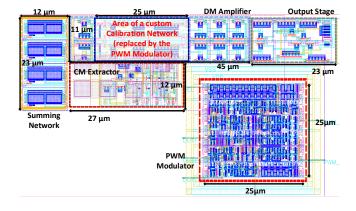

Fig. 3. DB-OTA layout. Total area of 1,700  $\mu$ m<sup>2</sup>.

by in post-fabrication calibration by tuning the aspect ratio of either the pull-up or the pull-down device.

With this aim, a calibration network consisting of pMOS (nMOS) devices with binary weighted width  $2^kW_0$ , to be connected in parallel to first stages of the DM amplifier depending on a calibration code, has been introduced in [10]. That calibration network, however, is not compatible with a pure digital flow and requires some extra analog design and layout effort. In view of these limitations, a different, all-digital

calibration approach is explored in this paper.

#### C. PWM Calibration Network

The proposed PWM calibration network consists of a calibration inverter driven by the input signals and connected in parallel to the first stage of each branch in the DM amplifier, as depicted in Fig.1. The pull-up (pull-down) network of the calibration inverter can be tied to the supply (to ground) through a pMOS (nMOS) power gating switch, as depicted in the figure. When the pMOS (nMOS) gating switch is on, the pMOS (nMOS) of the calibration inverter, with width  $W_n$  ( $W_p$ ) is enabled and connected in parallel to the nMOS (pMOS) device in the first stage of the DM amplifier, thus effectively increasing its width and significantly reducing (increasing) its trip point according to (2).

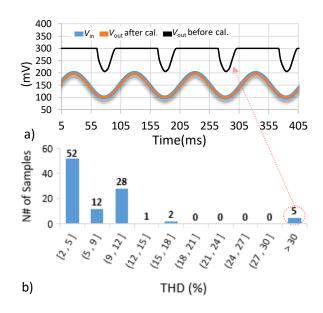

In the proposed calibration network, one of the power gating switches is driven by a square wave, N-bit digital pulse-width modulated (PWM) voltage with a duty cycle  $D = n/2^N$  that can be configured by the calibration code n as in Fig.2. As far as the PWM frequency is larger than 10X the DB-OTA GBW, it is observed that periodically enabling the nMOS (pMOS) network of the calibration inverter has the same net effect on the trip points of the DM amplifier gates as increasing the width of the DM amplifier devices by  $DW_n$  ( $DW_p$ ), as shown in Fig.2, where the DB-OTA output waveforms obtained with the same input signal under different PWM duty cycles of the enable signal for the pMOS and nMOS branches.

The proposed PWM calibration approach has been adopted in a DB-OTA designed as in [10] to compensate process variation and mismatch and its effectiveness will be discussed in the following on the basis of post-layout simulations.

#### III. POST-LAYOUT SIMULATIONS

In order to validate the proposed PWM calibration approach, a DB-OTA has been designed and laid out in 180nm CMOS. A 3-bit digital PWM modulator has been synthesized in a digital flow to generate the gating signals for the proposed PWM calibration. The overall layout, including the calibration network, occupies just 1,700  $\mu$ m<sup>2</sup> as shown in Fig. 3.

The proposed DB-OTA has been designed as in [10] to operate at  $V_{\rm DD}=300 {\rm mV}$  power supply driving up to 80pF capacitive load and its nominal performance, verified by post-layout simulations, are briefly summarized in what follows. Then, the possibility to replace the custom calibration network introduced in [10] by the PWM calibration described above is verified by post-layout MonteCarlo simulations.

### A. Performance under Nominal Conditions

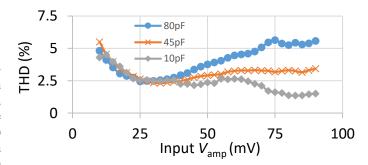

The input and output waveforms of the proposed DB-OTA under nominal process parameters, at  $V_{\rm DD}=300{\rm mV}$ , with sine wave input at 30Hz frequency, 50mV peak amplitude and  $C_{\rm out}=80\,{\rm pF}$  capacitive load are reported in Fig.2(a) and reveal the operation of the circuit as an opamp and less than 2% THD and 2nW power consumption. A zoom in the waveform shows the step-wise changes in  $v_{\rm out}$  resulting from digital operation. Fig.4 depicts THD versus the sinewave input

Fig. 4. THD (%) versus  $V_{amp}$  (nominal process parameters, no mismatch)

Fig. 5. ULV DB-OTA frequency response (nominal process parameters, no mismatch).

signal amplitude  $V_{\text{amp}}$  for three different values of the output capacitance  $C_{\text{out}} = 80,45,10\,\text{pF}$  keeping  $f_{\text{in}} = 120\,\text{Hz}$ .

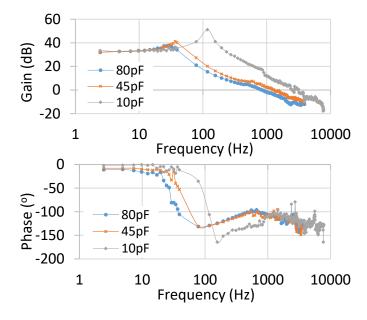

The frequency response of the DB-OTA, estimated as the ratio of the Fast Fourier Transform (FFT) component at the fundamental frequency  $f_0$  of the output and of the differential input voltage,  $A_{\rm d}(f) = \frac{V_{\rm out}(f)}{V_{\rm d}(f)}$  is reported in Fig.5 for different capacitive loads. Based on the figure, the DB-OTA shows 35dB DC gain and 0.85,1.3 and 2.48kHz Gain Bandwidth Product (*GBW*) with phase margin 76°,68.5° and 57° under  $C_{\rm out} = 80,45$  and 10 pF load, respectively.

#### B. Process Variations and PWM Calibration Validation

The DB-OTA without calibration has been tested under process variations for  $V_{\rm amp} = 50\,{\rm mV}$ ,  $C_{\rm out} = 80\,{\rm pF}$  and  $f_{\rm in} = 120\,{\rm Hz}$  by Montecarlo (MC) simulations on 100 samples. The histogram of the output THD is reported in Fig.2(c) and reveals a noticeable number of samples exceeding 10% THD due to the spread in the trip voltages of the *DM amplifier*  $\Delta V_{\rm T}$ , which in the worst cases (89% THD) results in the output voltage saturation, as shown in Fig.2(b).

TABLE I COMPARISON WITH THE STATE-OF-THE-ART ULTRA-LOW-VOLTAGE OPERATIONAL TRANSCONDUCTANCE AMPLIFIER

| Performance       | [15] <sup>+</sup> | [16] <sup>+</sup> | $[17]^{+}$ | $[18]^{+}$ | [19]* | [20]*<br>MC-OTA | [20]*<br>FFC-OTA |           | This work*                      |        |        | Unit             |

|-------------------|-------------------|-------------------|------------|------------|-------|-----------------|------------------|-----------|---------------------------------|--------|--------|------------------|

|                   |                   |                   |            |            |       |                 |                  | Typical   | Worst case mismatch and process |        |        |                  |

|                   |                   |                   |            |            |       |                 |                  | Condition |                                 |        | ocess  |                  |

|                   |                   |                   |            |            |       |                 |                  |           | No                              | Custom | PWM    |                  |

|                   |                   |                   |            |            |       |                 |                  |           | Calib.                          | Calib. | Calib. |                  |

| Technology        | 65                | 130               | 180        | 350        | 65    | 130             | 130              | 180       | 180                             | 180    | 180    | nm               |

| Supply<br>Voltage | 0.35              | 0.25              | 0.5        | 0.6        | 0.3   | 0.3             | 0.3              | 0.3       | 0.3                             | 0.3    | 0.3    | V                |

| DC Gain           | 43                | 60                | 52         | 69         | 60    | 46.2            | 49.8             | 35        | N/A                             | 27     | 26     | dB               |

| GBW               | 3600              | 1.88              | 1,200      | 11.4       | 70    | 2,450           | 9,100            | 0.85      | N/A                             | 0.59   | 0.47   | kHz              |

| Slew Rate         | 5600              | 0.7               | 2,890      | 14.6       | 25    | 2,400           | 3,800            | 0.5       | N/A                             | 0.38   | 0.39   | V/ms/%           |

| THD               | 0.6               | 0.2               | 1          | 0.08       | -     | -               | _                | 3         | 89                              | 2.6    | 2.26   | %                |

| Phase Margin      | 56                | 52.5              | _          | 65         | 53    | 52              | 76               | 76        | N/A                             | 70     | 67     | o                |

| $C_{ m out}$      | 3                 | 15                | 20         | 15         | 5     | 2               | 2                | 80        | 80                              | 80     | 80     | pF               |

| Power             | 17,000            | 18                | 110,000    | 550        | 51    | 1,800           | 1,800            | 2         | N/A                             | 1.64   | 7.34   | nW               |

| Area              | 5,000             | 83,000            | 26,000     | 60,000     | 3,000 | -               | -                | 1,426     | 1,426                           | 1,426  | 1,700  | $\mu \text{m}^2$ |

| $FOM_S$           | 19                | 29                | 0.11       | 0.18       | 2.05  | 81              | 303              | 1020      | N/A                             | 857    | 153    | $V^{-1}$         |

| $FOM_{\rm L}$     | 34.6              | 14.6              | 26.27      | 23.9       | 73.4  | 80              | 140              | 600       | N/A                             | 553    | 127    | -                |

+experimental; \*simulation;  $FOM_{\rm S} = 100 \frac{GBWC_{\rm OUT}}{I_{\rm DD}}$ ;  $FOM_{\rm L} = 100 \frac{SR_{\rm avg}C_{\rm OUT}}{I_{\rm DD}}$  where  $SR_{\rm avg} = \frac{SR_{+} + SR_{-}}{2}$  is the slew rates (averaged between negative and positive) and  $I_{\rm DD}$  is the RMS  $IOM_S = IOO \frac{G}{I_{DD}}$  current consumption.

a) output voltage of the worst sample with and without PWM calibration b) THD histogram of 100 montecarlo samples

In order to validate the proposed PWM calibration approach, the worst samples resulting form the above MC analysis have been considered. Even in these worst cases, a decent performance has been recovered by properly programming the digital PWM modulator with a 3-bit code so that to generate a PWM signal with 24µs period and with a convenient duty cycle, and to apply it either to the pMOS or to the nMOS enable switches in Fig.1. In Fig.6, in particular, the DB-OTA output voltage waveform for the worst sample, before and after PWM calibration, is reported.

The performance of the worst MC sample after PWM calibration has been compared with the performance of the same sample when calibrated by the traditional custom approach described in Section.IIb. The results reported in Tab.I reveal that the samples calibrated by the traditional and by the PWM approaches show comparable GBW, slew rate and gain and that the THD is even lower for the PWM calibration. The overhead in terms of power of the PWM calibration strategy is 5.34nW, i.e. the power consumption of the PWM modulator. The comparison with state of the art ultra-low voltage (ULV) OTAs reveal competitive performance also for the worst case samples after calibration.

#### IV. CONCLUSION

A fully digital dynamic calibration to compensate process and mismatch related offset in ULV DB-OTA has been presented. An opamp circuit featuring the proposed calibration technique in 180nm CMOS has been designed and verified by post-layout simulations, which demonstrates that process and mismatch variations can be effectively compensated in a fully digital way by varying the duty cycle of a square wave signal with minimum performance overhead. The proposed OTA consumes just 7.34nW while driving a capacitive load of 80pF with Total Harmonic Distortion lower than 2.26% at 100mV input signal swing. The total silicon area is 1,700  $\mu$ m<sup>2</sup>. The results demonstrate the feasibility of a fully synthesizable, technology portable and minimum design effort approach in DB-OTA calibration.

# ACKNOWLEDGMENT

This project has received funding from the European Union's Horizon 2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 703988 (ULPIoT project).

#### REFERENCES

- 1 Alioto, M., Enabling the Internet of Things from Integrated Circuits to Integrated Systems, 1st ed. Springer, 2017.

- 2 Crovetti, P. S., Musolino, F., Aiello, O., Toledo, P., and Rubino, R., "breaking the boundaries between analogue and digital," *Electronics Letters*, vol. 55, no. 12, pp. 672–673, 2019.

- 3 Crovetti, P. S., "A digital-based virtual voltage reference," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 62, no. 5, pp. 1315–1324, May 2015.

- 4 Aiello, O., Crovetti, P., Lin, L., and Alioto, M., "A pw-power hz-range oscillator operating with a 0.3–1.8-v unregulated supply," *IEEE Journal* of Solid-State Circuits, vol. 54, no. 5, pp. 1487–1496, May 2019.

- 5 Aiello, O., Crovetti, P., and Alioto, M., "A sub-leakage pw-power hzrange relaxation oscillator operating with 0.3v-1.8v unregulated supply," in *IEEE 2018 Symposia on VLSI Circuits (VLSI 2018)*, June 2018, pp. 119 – 120.

- 6 Aiello, O., Crovetti, P. S., and Alioto, M., "Wake-up oscillators with pw power consumption in dynamic leakage suppression logic," in 2019 Int. Symposium on Circuits and Systems (ISCAS2019), May 2019.

- 7 Aiello, O., Crovetti, P., and Alioto, M., "Fully synthesizable, rail-to-rail dynamic voltage comparator for operation down to 0.3v," in 2018 Int. Symposium on Circuits and Systems (ISCAS2018), May 2019.

- 8 Aiello, O., Crovetti, P. S., and Alioto, M., "Fully synthesizable low-area digital-to-analog converter with graceful degradation and dynamic powerresolution scaling," *IEEE Trans. on CaS I: Regular Papers*, vol. 66, no. 8, pp. 2865–2875, Aug 2019.

- 9 Aiello, O., Crovetti, P., and Alioto, M., "Standard cell-based ultra-compact dacs in 40nm cmos," *IEEE Access*, vol. 7, pp. 126479 – 126488, Aug 2019.

- 10 Toledo, P., Crovetti, P., Klimach, H., and Bampi, S., "A 300mv, 2nw, cmos digital-based ota driving 80pf load for iot interfaces," in 2019 Int. Conf. on Electronics, Circuits and Systems (ICECS2019), vol. 2019, Nov.

- 11 Crovetti, P. S., "A digital-based analog differential circuit," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 60, no. 12, pp. 3107–3116, Dec 2013.

- 12 Galup-Montoro, C., Schneider, M. C., Klimach, H., and Arnaud, A., "A compact model of mosfet mismatch for circuit design," *IEEE J. of Solid-State Circuits*, vol. 40, no. 8, pp. 1649–1657, Aug 2005.

- 13 White, D. J., Hoffman, M. W., and Balkır, S., "Digital offset cancellation for long time-constant subthreshold ota-c integrators," *IEEE Trans. on CaS II: Express Briefs*, vol. 62, no. 11, pp. 1038–1042, Nov 2015.

- 14 Braga, R. A., Ferreira, L. H., Coletta, G. D., and Dutra, O. O., "A 0.25-v calibration-less inverter-based ota for low-frequency gm-c applications," *Microelectronics Journal*, vol. 83, pp. 62 – 72, 2019. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S002626921830418X

- 15 Abdelfattah, O., Roberts, G. W., Shih, I., and Shih, Y., "An ultra-low-voltage cmos process-insensitive self-biased ota with rail-to-rail input range," *IEEE Tran. Circuits Syst. I: Reg. Papers*, vol. 62, no. 10, pp. 2380–2390, Oct 2015.

- 16 Ferreira, L. H. C. and Sonkusale, S. R., "A 60-db gain ota operating at 0.25-v power supply in 130-nm digital cmos process," *IEEE Tran. Circuits Syst. I: Reg. Papers*, vol. 61, no. 6, pp. 1609–1617, June 2014.

- 17 Chatterjee, S., Tsividis, Y., and Kinget, P., "0.5-v analog circuit techniques and their application in ota and filter design," *IEEE J. of Solid-State Circuits*, vol. 40, no. 12, pp. 2373–2387, Dec 2005.

- 18 Ferreira, L. H. C., Pimenta, T. C., and Moreno, R. L., "An ultra-low-voltage ultra-low-power cmos miller ota with rail-to-rail input/output swing," *IEEE Trans. Circuits Syst. II: Exp. Briefs*, vol. 54, no. 10, pp. 843–847, Oct 2007.

- 19 Veldandi, H. and Shaik, R. A., "A 0.3-v pseudo-differential bulk-input ota for low-frequency applications," *Circuits, Systems, and Signal Processing*, vol. 37, no. 12, pp. 5199–5221, Dec 2018.

- 20 Lv, L., Zhou, X., Qiao, Z., and Li, Q., "Inverter-based subthreshold amplifier techniques and their application in 0.3-v ΔΣ -modulators," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1436–1445, May 2019.