## POLITECNICO DI TORINO Repository ISTITUZIONALE

### A Unified Design Theory for Class-E Resonant DC-DC Converter Topologies

Original

A Unified Design Theory for Class-E Resonant DC-DC Converter Topologies / Pareschi, F.; Bertoni, N.; Mangia, M.; Rovatti, R.; Setti, G.. - In: IEEE ACCESS. - ISSN 2169-3536. - 7:(2019), pp. 83825-83838. [10.1109/ACCESS.2019.2922743]

Availability:

This version is available at: 11583/2780174 since: 2020-01-14T18:52:20Z

Publisher:

Institute of Electrical and Electronics Engineers Inc.

Published

DOI:10.1109/ACCESS.2019.2922743

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

Received June 6, 2019, accepted June 6, 2019, date of publication June 13, 2019, date of current version July 12, 2019.

Digital Object Identifier 10.1109/ACCESS.2019.2922743

# A Unified Design Theory for Class-E Resonant DC-DC Converter Topologies

FABIO PARESCHI<sup>©</sup>1,2, (Member, IEEE), NICOLA BERTONI<sup>©</sup>3, MAURO MANGIA<sup>©</sup>2,4, (Member, IEEE), RICCARDO ROVATTI<sup>©</sup>2,4, (Fellow, IEEE), AND GIANLUCA SETTI<sup>©</sup>1,2, (Fellow, IEEE)

Corresponding author: Gianluca Setti (gianluca.setti@polito.it)

**ABSTRACT** Resonant and quasi-resonant dc—dc converters have been introduced to increase the operating frequency of switching power converters, with advantages in terms of performance, cost, and/or size. In this paper, we focus on class-E resonant topologies, and we show that about twenty different architectures proposed in the last three decades can be reduced to two basic topologies, allowing the extension to all these resonant converters of an exact and straightforward design procedure that has been recently proposed. This represents an important breakthrough with respect to the state of the art, where class-E circuit analysis is always based on strong simplifying assumptions, and the final circuit design is achieved by means of numerical simulations. The potentialities of the proposed exact methodology are highlighted by realistic circuit-level simulations, where the desired waveforms are obtained in one single step without the need of a time-consuming iterative trial-and-error process.

**INDEX TERMS** Circuit theory, class-E converters, resonant dc-dc converters.

#### I. INTRODUCTION

Resonant and quasi-resonant dc-dc converters have been introduced with the aim of reducing switching loss impact at high frequencies. This allows a converter to operate with good efficiency at high frequency ranges (up to the VHF range  $30-300 \mathrm{MHz}$ ) thus increasing the system power density [1]–[7]. A higher switching frequency, in fact, paves the way to both size and cost reduction, as well as improved dynamic performance [2].

In this paper we focus on the Class-E converters [2], [5] that are based on the so-called *soft switching* technique and that are specifically designed to overcome the main drawback of conventional class-D (*hard-switching*) topologies given by the frequency dependent loss mechanisms. The soft switching technique has been proposed, to the best of authors' knowledge, by Sokal *et al.* in [1] as a way to improve performance in RF amplifiers [1], [2], [8]. The main concept is the introduction of additional reactive components in order to properly shape voltage and current waveforms.

The associate editor coordinating the review of this manuscript and approving it for publication was Derek Abbott.

The advantage is to lower (ideally, down to zero) the switching losses [7], [8] with beneficial effects also in terms of reducing EMI emission [7], [9] without the need of additional techniques like spread-spectrum clocking that are becoming popular for class-D converters [9]–[13].

In details, class-E dc-dc converters can be seen as composed of the cascade of a class-E inverter [1], [7], [8], [14] and a class-E rectifier [7], [15], both relying on a soft-switching approach. Sometimes they are called  $E^2$ converters [16]-[18] to distinguish them from converters relaying, as an example, upon a class-E inverter and a class-D rectifier [7]. Soft switching is achieved by ensuring that the voltage (or current) waveform of the controlled switch (in the inverter) and the uncontrolled one (in the rectifier) is smooth. Focusing on the inverter, we refer to Zero-Voltage Switching (ZVS) when the voltage across the main switching device is slowly increasing from zero after its turn-OFF instant, and slowly going to zero immediately before its turn-ON instant. Additionally, we refer to Zero-Voltage-Derivative Switching (ZVDS) if the voltage is approaching the zero level with zero-time-derivative. Zero-Current Switching (ZCS) and Zero-Current-Derivative Switching (ZCDS) are referred to

<sup>&</sup>lt;sup>1</sup>Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Torino, Italy

<sup>&</sup>lt;sup>2</sup>Advanced Research Center on Electronic Systems, University of Bologna, 40125 Bologna, Italy

<sup>&</sup>lt;sup>3</sup>Texas Instruments Design Center, 20089 Milan, Italy

<sup>&</sup>lt;sup>4</sup>Department of Electrical, Electronic, and Information Engineering, University of Bologna, 40136 Bologna, Italy

the current flowing into the main switch device. The same definitions can be applied to the rectifier, even if some authors prefer to indicate these conditions as low dv/dt and low di/dt [7], [19], [20].

Historically, the soft switching technique is known since many years [1], and the application to dc-dc resonant converters has been first introduced in the early '80s [2]. Nevertheless, the topic is still receiving attention in the Literature [18], [21]–[23]. Due to better performance, all recent papers are focused on the ZVS approach [7], [24]. A few of these works are also focusing on the proposal of new topologies aiming to improve efficiency or reduce device stress [25], [26]. Almost all of these contributions are interested in improving the converter control [27], [28] or the design methodology [14], [18], [25], [27], [29] in already known topologies.

This paper belong to the latter group, i.e., it aims at improving the state of the art in class-E converter design. In particular, we consider the exact and semi-analytic design methodology proposed in [29]. This represents an important step in class-E converters design theory with respect to state-of-the-art alternative methodologies which are based on the sinusoidal approximation typical of RF circuit design and on the subsequent refinement by means of additional, time-consuming SPICE simulations. With respect to [29], we make two important additional steps. First, we improve the methodology by simplifying the approach and by generalizing it, covering two different topologies, both featuring galvanic isolation. Then, we show that these two topologies are actually representative for a large number of class-E dcdc converters, either isolated or non-isolated. The similarity between the design approaches for many resonant topologies has been already observed in many works, as for example in [19]. The contribution of this work is to show that the innovative design methodology considered here can be actually applied as is to a number of different converters regardless of the actual circuit topology.

The paper is organized as follows. After a brief review of the class-E state-of-the-art (Section II), we present in Section III the two isolated class-E topologies that are referred to as *canonical* ones in this paper. The exact semi analytic design methodology is also provided. In Section IV the most commonly used non-isolated class-E topologies are presented and related to the canonical ones, showing that all of them share the same design equations (and so the design methodology). The approach is validated by means of realistic SPICE simulations that take into account many possible circuit non-idealities. Finally, we draw the conclusion.

#### II. STATE-OF-THE-ART

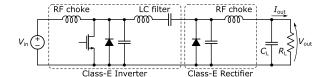

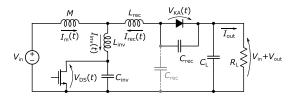

One of the first class-E dc-dc converter proposed in the literature is that depicted in Figure 1 and proposed by Kazimier-czuk *et. al.* in [5]. In the schematic, the distinction between the class-E inverter and rectifier stages, connected by means of a properly designed band-pass LC filter, is clearly visible.

FIGURE 1. Basic schematic of the class-E dc-dc converter proposed by Kazimierczuk et al. in [5].

The aim of [5] is to propose a design methodology to achieve ZVS and ZVDS at the MOS switch (ZVS at the diode, or low dv/dt, is always ensured in this topology), realizing the so-called Optimal Class-E Operation [8]. Indeed, due to the non-linearity and to the many reactive elements, the design procedure is quite complex and based on the well-known approximations used in RF circuits [1], [2]. In [5], the inverter design is achieved by assuming that the rectifier is a linear circuit with a given impedance. Then, the rectifier design is achieved by assuming that it is driven by an ideal sinusoidal current source at the same frequency  $f_s$ at which the MOS switch is turned ON and OFF. The purpose of the (high loaded quality factor) LC filter is to support these two assumptions and ensure adherence between the actual waveforms and the expected ones. Two large RF choke inductors are also employed to ensure the two additional assumptions of a constant current power source and a constant current load, that further simplify the converter analysis.

With these assumptions, a fully analytic model for the behavior of the converter can be readily obtained, and used to ensure the desired optimal class-E operation. Note that the behavior of resonant converters depends also on the load resistance or on the output current ( $R_L$  and  $I_{out}$  in Figure 1). In other words, ZVS and ZVDS can be achieved only for a given operating condition defined by a value of  $R_L$  or  $I_{out}$ . Coping with a variable load, or either with a non-precisely known  $V_{in}$ , is a complex task and requires a feedback such as a frequency control [2], [30] or an ON-OFF control [27], [31]. As an example, in [5], the converter is designed to achieve the optimal behavior at the maximum output power. At a lighter load, the switching frequency is increased to maintain the same output voltage, but the converter operates under suboptimum class-E conditions: in fact, the diode antiparallel to the MOS switch turns ON before the MOS is turned ON, thus ensuring ZVS operation, but ZVDS is not achieved anymore. Note that the antiparallel diode, in most of the cases, is just the parasitic body diode present in any discrete MOS, and does not turn ON when the optimal class-E condition is achieved. For the sake of simplicity, even if present as a parasitic device, we will not include the antiparallel diode anymore in the next schematics.

In this work we are interested in methodology ensuring ZVS and ZVDS for a specific operating condition, and we consider control methodologies to be out of scope. Once the class-E design is achieved (for an operating condition that could be, as in the above example, the one ensuring the maximum output power), it is always possible to apply any of the control methodologies presented in the literature.

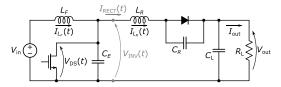

FIGURE 2. Schematic of the class-E boost converter proposed in [27].

So, in the following we will always assume that  $V_{\text{in}}$  and  $R_L$ , or  $I_{\text{out}}$ , are known and fixed.

The most recent efforts in class-E resonant converter design aimed at removing bulky elements such as the input RF choke inductor and the high-Q LC filter, or replacing them with smaller resonant counterparts. In this way, the converter component count is reduced, enabling overall size and cost reduction. As a consequence, the design methodology has been improved, and more complex design approaches has been proposed in the Literature to cope with the fact that using the sinusoidal approximation without any circuital solution supporting it, would lead to an increased difference between expected and actual waveforms.

To better explain the above considerations, let us consider a numerical example relying on the approach proposed in [27], that is one of the most advanced among those based on the sinusoidal approximation. The design approach has been developed for the boost converter of Figure 2, that can been directly obtained by that of Figure 1 by removing the LC filter, replacing the RF choke inductors with smaller resonant ones, and re-arranging the position of the elements in the rectifier. The analysis of the converter in [27] is based on the observation that the MOS and the diode are non-linear. Due to this, and even considering them as two ideal switching devices, i.e., either equivalent to an open circuit when in the OFF state or to a short circuit in the ON state, there are four different circuit configurations possible to be considered. Additionally, since the converter contains four reactive elements  $(L_F, C_E, L_R \text{ and } C_R)$ , the comprehensive mathematical description of the circuit requires four sets of fourth-order differential equations. This is further complicated by the fact that the switching instants of the diode are unknown. According to [27], deriving a complete set of closed-form equations to directly describe the converter is a "cumbersome and unfruitful task".

To cope with this, and following the original notation, the analysis starts from the assumption that the rectifier current is sinusoidal:

$$I_{\text{RECT}}(t) = I_{\text{AC}} \sin(2\pi f_s t + \phi_1) + \frac{P_{\text{out}}}{V_{\text{out}}}$$

(1)

Given this assumption, the system describing the inverter circuit evolution can be solved using the five unknown quantities  $\omega_0 = 1/\sqrt{L_F C_E}$ ,  $Z_0 = \sqrt{L_F/C_E}$ ,  $I_{AC}$ ,  $\phi_1$  and  $I_{L_F}(0)$ , defined as the current in  $L_F$  at the reference time t=0. By setting the three constraints: i) the inverter efficiency is 1, ii) the average voltage across  $L_F$  in one period is 0, iii) the average current through  $C_E$  in one period is 0, it is possible to get a non-linear system of three equations that, once numerically solved, gives

the optimal values of  $Z_0$ ,  $I_{\rm AC}$  and  $I_{L_F}(0)$  when the choice of the two degrees of freedom  $\omega_0$  and  $\phi_1$  has been made, and the design constraints  $V_{\rm in}$ ,  $V_{\rm out}$ ,  $P_{\rm out}$  and  $f_s$  are known. Note that conditions ii) and iii) ensure both steady-state behavior and ZVS.  $^1$  ZVDS is not considered at this step, but investigated later through the correct choice of the two degrees of freedom.

Once the design of the inverter is obtained, one can get the rectifier design starting on the assumption that its input voltage is sinusoidal and expressed as

$$V_{\text{INV}}(t) = V_{\text{AC}} \sin(2\pi f_s + \phi) + V_{\text{in}}$$

where  $V_{\rm AC}$  and  $\phi$  are computed from the inverter analysis as the amplitude and the phase of the first harmonic of the voltage  $V_{DS}(t)$  across the MOS. The analysis is based on four unknown quantities: the time instants  $t_{\rm ON}$  and  $t_{\rm OFF}$  when the diode turn ON and OFF, respectively,  $\omega_r = \sqrt{L_R/C_R}$ , and  $Z_r = \sqrt{L_R/C_R}$ . Similarly to the inverter case, these unknowns can be achieved by numerically solving the non-linear system one gets by considering the four constraints: i) the rectifier efficiency is 1, ii) the average voltage across  $L_R$  in one period is 0, ii) the phase of the fundamental component of  $I_{L_R}(t)$  is  $\phi_1$ , as constrained by (1).

The entire procedure is semi-analytic: all waveforms are expressed in a closed form (even if some coefficients, such as  $V_{AC}$  and  $\phi$ , are numerically obtained), but are linked via a system of non-linear equations that needs to be solved numerically. As an example, even if the authors of [27] does not provide any numerical example from applying the proposed methodology, one can follows the described methodology and assume  $V_{\rm in}=12\,\rm V$ ,  $V_{\rm out}=30\,\rm V$ ,  $P_{\rm out}=7\,\rm W$ ,  $f_s=75\,\rm MHz$ . By setting  $\omega_0=0.6\cdot 2\pi f_s$ , ZVDS is ensured for  $\phi_1=-0.5\,\rm rad$ . With this, the obtained numerical solution is  $L_F=594\,\rm nH$ ,  $C_E=21.0\,\rm pF$ ,  $L_R=134\,\rm nH$ ,  $C_R=23.5\,\rm pF$ . These values are aligned with the ones that can be inferred by looking at the design curves in [27].

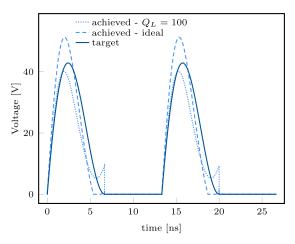

However, since the sinusoidal approximation is not supported anymore by a band-pass filter, the achieved solution requires to be refined by means of circuital simulation to perfectly fit the desired behavior. Figure 3 compares the achieved waveform of the voltage  $V_{DS}(t)$  across the MOS (dashed line) obtained from a SPICE simulation using ideal models for all devices (including MOS and diode), with the desired one featuring ZVS and ZVDS (solid line) obtained when the rectifier is replaced by the current generator assumed in (1). The difference is remarkable, and also present in the output power, that settles to 7.6 W. We want also to stress that the design methodology does not take into account any non-idealities. As an example, if we consider that  $L_F$  and  $L_R$  are lossy inductors with, say, a quality factor  $Q_L = 100$ ,

<sup>&</sup>lt;sup>1</sup>Since for any ideal capacitor I(t) = CdV(t)/dt, and considering that the voltage V(t) across the  $C_E$  at the beginning and at the end of one clock period is constrained to 0 by the MOS, the average value of I(t) is 0 only if V(t) has no discontinuities, including at the MOS turn ON instant.

<sup>&</sup>lt;sup>2</sup>The only example proposed in [27] is already refined by SPICE simulation, and no design without refinement is provided.

**FIGURE 3.** Comparison between the desired and the achieved shape of the  $V_{DS}(t)$  waveform for the converter of Figure 2 using the procedure proposed in [27].

the observed  $V_{DS}(t)$  is given by the dotted line of Figure 3, and the power delivered to the load drops to 5.9 W. From this example, it is clear that the procedure proposed in [27] can be effectively used only to get a reasonable starting point in the converter design, and that a refinement of the solution based on lengthy simulations is essential.

A major step forward in the design of class-E dc-dc converters has been made by Bertoni *et al.* in [29]. Authors proposed a suitable way to derive the complete set of closed-form equations that directly describe the converter evolution. As in [27], the entire procedure is semi-analytic, since the design is achieved as the numerical solution of a system of non-linear equations. However, the procedure introduces minor approximations only, and does not need any further refinement. Furthermore, major sources of non-idealities can be taken into account. The procedure is also dimensionless, and so independent of  $V_{\rm OUT}$ ,  $P_{\rm OUT}$  and  $f_s$ .

Starting from [29], we show in the following that the design methodology proposed there can be actually extended to a large class of resonant dc-dc converter topologies appeared in the literature in the last three decades. This allows us to propose a more general class-E converter design methodology that, with respect to any solution based on the sinusoidal approximation such as [27], presents three main advantages: i) it is dimensionless, i.e., can be applied regardless of the value, for example, of  $P_{\text{OUT}}$  and  $f_s$ , ii) can be applied to many different converter regardless of the actual topology, iii) can take into account of the main sources of non-idealities.

#### **III. CLASS-E ISOLATED TOPOLOGIES**

#### A. CANONICAL ISOLATED TOPOLOGIES

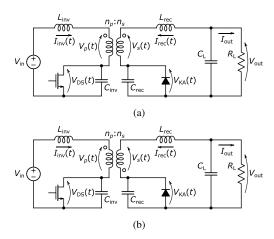

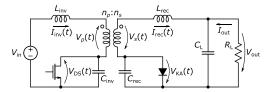

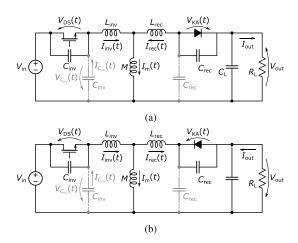

The two basic resonant converter topologies we will consider are shown in Figure 4. Both topologies consist of two meshes (the inverter and the rectifier one), coupled by means of a transformer to provide galvanic isolation. The inverter has a MOS switch that is externally turned ON and OFF at frequency  $f_s$  with duty-cycle D, while the rectifier embeds

FIGURE 4. Schematic of the canonical isolated class-E converter topologies considered in the paper. (a): in-phase coupling. (b): 180° out-of-phase coupling.

a diode as a non-controlled switch. The only difference between the two topologies is the coupling method: in the converter of Figure 4(a) the coupling is in-phase, while in that of Figure 4(b) there is a 180° out-of-phase coupling.

Both schematics feature all the characteristics of a class-E converter, as that of Figures 1 and 2. The two capacitors  $C_{inv}$ and  $C_{\text{rec}}$  are placed in parallel with the MOS switch and the diode, respectively, to ensure smooth waveforms. Furthermore,  $C_{\text{inv}}$  and  $C_{\text{rec}}$  can also embed the parasitic capacitance of the two switches and, as long as the actual capacitances are much larger with respect to the parasitic ones, can mask both the non-linearity and the non-perfect knowledge of the latter. This ensures that the parasitic of the two switches do not significantly alter the circuit behavior. The inductors  $L_{inv}$ and  $L_{rec}$  can also embed (or mask) the leakage inductance of the transformer. Along with  $C_{inv}$  and  $C_{rec}$ , they also set the two resonant frequencies of the inverter and of rectifier meshes, respectively. Note that, since the transformer can be actually seen as an additional (coupled) inductor, and since only two inductances are actually necessary along with the two capacitances to set the resonance properties, one among  $L_{\rm inv}$  and  $L_{\rm rec}$  can be removed from the circuit. This will become clearer in the next section. To further improve the design approach in [29], we include both the schemes of Figure 4 in the proposed analysis for the maximum generality and flexibility.

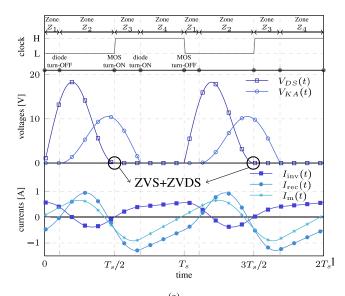

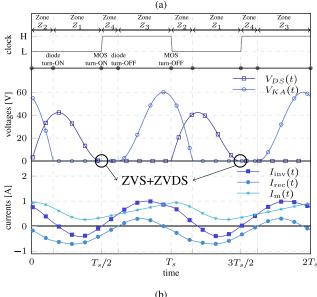

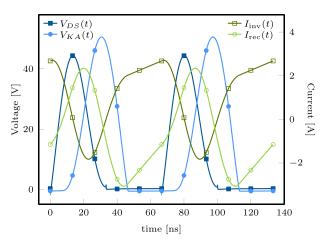

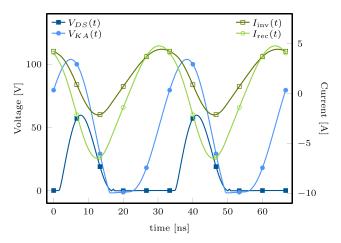

The evolution, obtained by means of SPICE simulation, of the considered circuits when designed to achieve optimal class-E operation (i.e., ZVS and ZVDS) is shown in Figure 5(a) for the in-phase coupled and in Figure 5(b) for the 180° out-of-phase coupled circuit. The figures show the most important voltage and current signals of the circuit, i.e.,  $V_{DS}(t)$  across the MOS switch,  $V_{KA}(t)$  across the diode,  $I_{\text{inv}}(t)$  flowing into the inverter mesh,  $I_{\text{rec}}(t)$  of the rectifier mesh, and the transformer magnetizing current defined as  $I_{\text{m}}(t) = I_{\text{inv}}(t) + I_{\text{rec}}(t)$  for the in-phase coupling and  $I_{\text{m}}(t) = I_{\text{inv}}(t) - I_{\text{rec}}(t)$  for the 180° out-of-phase coupling. In both cases the  $V_{DS}(t)$  mildly reaches the zero level, at the MOS

**FIGURE 5.** Resonant class-E converter typical voltage and current waveforms. (a): In-phase coupling  $(\Phi=+1)$ . (b): 180° out-of-phase coupling  $(\Phi=-1)$ .

turn-ON instants (that are, in the figure,  $t = T_s/2$  and  $t = 3 T_s/2$ , with  $T_s = 1/f_s$  is the clock period length). The most remarkable difference between the two evolutions is that  $V_{KA}(t)$  is lagging  $V_{DS}(t)$  in Figure 5(a), and leading it in Figure 5(b).

The two circuits are not new and, actually, each one represents more a class of dc-dc converters than a single circuit. For example, it is clear that changing the order of the elements in a mesh does not alter the overall behavior: the rectifier of Figure 6 is perfectly equivalent to that of Figure 4(b). We refer to the two topologies in Figure 4 as *canonical* ones for the two identified classes.

The 180° out-of-phase coupling configuration is sometimes referred to as the class-E fly-back, due to similarities with the commonly used class-D (i.e., hard-switched) fly-back converter that can be simply obtained from that of

FIGURE 6. Alternative implementation of the inverter loop for the 180° out-of-phase coupling of Figure 4(b).

Figure 4(b). once resonant elements  $L_{inv}$ ,  $L_{rec}$ ,  $C_{inv}$  and  $C_{rec}$  are removed.

By introducing the schematics of Figure 4, we aim to:

- enhance the design methodology provided in [29], by considering a more general approach. Here, both  $L_{\rm inv}$  and  $L_{\rm rec}$  are explicitly taken into account, and both the in-phase coupling and the 180° out-of-phase coupling for the transformer are considered;

- show that the 180° out-of-phase coupling converter has similarities with a lot of other resonant (or quasiresonant) circuits proposed in the last three decades, each one presented with a different analysis and design methodology. All of them could be actually designed by applying the approach proposed here.

For example, in [32] a ZVS fly-back with  $180^{\circ}$  out-of-phase coupling, more precisely with the coupling as in Figure 6 but without  $L_{\rm rec}$  is considered. In [33] some different ZVS converter topologies are analyzed and compared, including that of Figure 4(b) in both configurations where either  $L_{\rm inv}$  or  $L_{\rm rec}$  is removed. In [34] an analysis of an isolated buck/boost converter with  $180^{\circ}$  out-of-phase coupling without  $L_{\rm rec}$  is provided. In [35] a circuit composed by two interleaved ZVS fly-back circuits as that of Figure 4(b), again without  $L_{\rm rec}$ , are considered and analyzed.

#### **B. CIRCUITS ANALYSIS**

The aim of this section is to describe and enhance the innovative design methodology proposed in [29]. More precisely, while trying to keep the notation as close as possible with respect to the original paper, we introduce a major change in the transformer model. This allows us to simplify the analysis, since considering the equivalent circuit to the primary side is not necessary anymore, and also to cope both with in-phase and with the 180° out-of-phase coupling methods of Figure 4 using a single equations set.

For the sake of simplicity, we neglect at this time all circuit losses, and take them into account only in Section III-D. We consider active devices (the MOS switch and the diode) as ideal switches, i.e., equivalent either to a short circuit or to an open circuit depending on their ON/OFF state. All passive elements are considered ideal, with an infinite quality factor.

In [29], the equivalent circuit at the primary side of the transformer is considered by scaling all elements at the secondary side using the turns ratio  $n_p/n_s$ . Instead of using this model (defined by the parameters  $n_p/n_s$ , the coupling coefficient k and the total inductance at the primary side  $L_p$ ), we adopt here the coupled inductors model where, referring

to Figure 4, the two transformer voltages can be written in matrix form as

$$\begin{pmatrix} V_p(t) \\ V_s(t) \end{pmatrix} = \begin{pmatrix} L_p & \Phi M \\ \Phi M & L_s \end{pmatrix} \frac{d}{dt} \begin{pmatrix} I_{\text{inv}}(t) \\ I_{\text{rec}}(t) \end{pmatrix}$$

(2)

where  $\Phi = \pm 1$  is the coupling constant, equal to +1 for in-phase coupling and -1 for 180° out-of-phase coupling, M is the mutual inductance, and  $L_p$  and  $L_s$  represent the inductance at the primary and secondary side, respectively. Switching between the two models is possible by considering that  $k = M/\sqrt{L_pL_s}$  and  $n_p/n_s = \sqrt{L_p/L_s}$ .

This alternative notation allows a quite simply analysis of the converter. The Kirchhoff voltage laws at the inverter and rectifier meshes are written as

$$V_{\rm in} = (L_{\rm inv} + L_p) \frac{dI_{\rm inv}(t)}{dt} + \Phi M \frac{dI_{\rm rec}(t)}{dt} + V_{DS}(t) \quad (3a)$$

$$V_{\text{out}} = \Phi M \frac{dI_{\text{inv}}(t)}{dt} + (L_{\text{rec}} + L_s) \frac{dI_{\text{rec}}(t)}{dt} + V_{KA}(t) \quad (3b)$$

that, by defining  $I_{\rm m}(t) = I_{\rm inv}(t) + \Phi I_{\rm rec}(t)$ , can also be rewritten as

$$V_{\rm in} = (L_{\rm inv} + L_p - M) \frac{dI_{\rm inv}(t)}{dt} + M \frac{dI_{\rm m}(t)}{dt} + V_{DS}(t) \qquad (4a)$$

$$V_{\text{out}} = (L_{\text{rec}} + L_s - M) \frac{dI_{\text{rec}}(t)}{dt} + \Phi M \frac{dI_{\text{m}}(t)}{dt} + V_{KA}(t)$$

(4b)

where (4b) holds since  $\Phi = \pm 1$ , so  $I_{rec}(t) = \Phi^2 I_{rec}(t)$ .

Equations (3a) and (3b) are a system of ordinary differential equations (ODEs) that, along with the equations regulating  $V_{DS}(t)$  and  $V_{KA}(t)$ , can be used to get the system evolution as in Figure 5. The missing equations depend on the ON/OFF state of the switching devices. For example, in the inverter loop, when the MOS is ON, the  $I_{\text{inv}}(t)$  is all flowing trough it, with  $V_{DS}(t)$  equal to zero. When OFF, the  $I_{\text{inv}}(t)$  is flowing trough  $C_{\text{inv}}$  and it is integrated by it thus setting  $V_{DS}(t)$ . Since there are four possible combinations of the active devices ON/OFF states, we can identify four different working *zones*, referred to as  $Z_j$ ,  $j=1,\ldots,4$ .

**Zone**  $Z_1$ : the MOS is OFF, while the diode is ON. The  $I_{inv}(t)$  current is flowing through the  $C_{inv}$  while the rectifying diode forces the  $V_{KA}(t)$  to zero, so

$$\begin{cases} I_{\text{inv}}(t) = C_{\text{inv}} \frac{dV_{DS}(t)}{dt} \\ V_{KA}(t) = 0 \end{cases}$$

(5a)

The ODE system is a third order one in the variables  $I_{inv}(t)$ ,  $I_{rec}(t)$  and  $V_{DS}(t)$ .

**Zone Z<sub>2</sub>**: both the MOS and the diode are in the OFF-state. The  $I_{inv}(t)$  and  $I_{rec}(t)$  are flowing, respectively, through  $C_{inv}$  and  $C_{rec}$ , so that

$$\begin{cases} I_{\text{inv}}(t) = C_{\text{inv}} \frac{dV_{DS}(t)}{dt} \\ I_{\text{rec}}(t) = C_{\text{rec}} \frac{dV_{KA}(t)}{dt} \end{cases}$$

(5b)

Equations (3a) and (3b) along with (5b), make a forth-order ODE system in  $I_{inv}(t)$ ,  $I_{rec}(t)$ ,  $V_{KA}(t)$  and  $V_{DS}(t)$ .

**Zone Z<sub>3</sub>**: the MOS is externally turned ON, while the diode is OFF, so

$$\begin{cases} V_{DS}(t) = 0 \\ I_{rec}(t) = C_{rec} \frac{dV_{KA}(t)}{dt} \end{cases}$$

(5c)

As in zone  $Z_1$ , we are dealing with a third-order ODE system. The variables in this case are  $I_{inv}(t)$ ,  $I_{rec}(t)$  and  $V_{KA}(t)$ .

Zone Z<sub>4</sub>: both active devices are ON, leading to

$$\begin{cases} V_{DS}(t) = 0 \\ V_{KA}(t) = 0 \end{cases}$$

(5d)

The associated ODE system is a second-order one in  $I_{inv}(t)$  and  $I_{rec}(t)$ .

Any of the four considered systems can be written in matrix form as  $\mathbf{x}'(t) = A\mathbf{x}(t) + \mathbf{b}$ , where the size of  $\mathbf{x}(t)$ , A and  $\mathbf{b}$  ranges from 2 to 4 (more precisely, from  $2 \times 2$  to  $4 \times 4$  for the matrix A). The solution of this system is known, and given by the linear combination of terms  $e^{\lambda_j t}$ , where the  $\lambda_j$  are the eigenvalues of A. In this way, we get an *analytic* expression, even if eigenvalues (and eigenvectors) have to computed numerically for a system whose order is higher than 2. Hence, one can get the converter evolution if:

- the succession of zones is given. Note that this depends on many factors: for example, while the MOS is externally turned ON and OFF with the desired frequency and the desired duty cycle, the diode turn-ON and turn-OFF instants have to be computed, respectively, as the time instants when the  $V_{KA}(t)$  turns non-positive and when the  $I_{\rm rec}(t)$  turns non-negative. A numerical computation is required; however, turn-ON and turn-OFF instants can be used as constant in the analytic expressions found. The succession of zone observed in the simulation results of Figure 5 is clearly indicated; interestingly, the in-phase coupled converter and the  $180^{\circ}$  out-of-phase one show different successions.

- the continuity of all state variables is ensured when switching from one zone to another one. As an example, referring to the in-phase coupling, we can set the reference time t=0 at the beginning of  $Z_1$ , with  $V_{DS}(0)=0$  and  $V_{KA}(0)=0$  due to circuit constraints, and where  $I_{\rm inv}(0)=I_{\rm inv}^{(0)}$  and  $I_{\rm rec}(0)=I_{\rm rec}^{(0)}$  are unknown variables. Assuming that  $Z_1$  ends at  $t_1$ , we get  $V_{KA}(t_1)=0$  due to circuit constraints, and non-null values of  $V_{DS}(t_1)$ ,  $I_{\rm inv}(t_1)$  and  $I_{\rm rec}(t_1)$ . These values are to be used as initial conditions for computing the evolution in  $Z_2$ . Following a similar procedure also for  $Z_3$  and  $Z_4$ , it is possible to get the (semi-)analytic evolution in a clock period as a function of circuit parameters and of the unknown variables  $I_{\rm inv}^{(0)}$  and  $I_{\rm rec}^{(0)}$ .

The advantage of this approach with respect to that in [27] is twofold. First, no approximations have been used to get the evolution of the system. Second, by using a normalized time  $\theta = 2\pi f_s t$ , and by introducing the dimensionless

parameters

$$q_{i} = \frac{I_{\text{out}}}{2\pi f_{s} C_{\text{inv}} V_{\text{out}}}, \ q_{r} = \frac{I_{\text{out}}}{2\pi f_{s} C_{\text{rec}} V_{\text{out}}}, \ q_{m} = \frac{2\pi f_{s} M I_{\text{out}}}{V_{\text{out}}}$$

$$k_{i} = \frac{M}{L_{\text{inv}} + L_{p}}, \ k_{r} = \frac{M}{L_{\text{rec}} + L_{s}}$$

$$(6)$$

and the normalized voltage and current signals  $\mu = V_{\rm in}/V_{\rm out}$ ,  $v_{DS}(\theta) = V_{DS}(2\pi f_s t)/V_{\rm out}$ ,  $v_{KA}(\theta) = V_{KA}(2\pi f_s t)/V_{\rm out}$ ,  $i_{\rm inv}(\theta) = I_{\rm inv}(2\pi f_s t)/I_{\rm out}$  and  $i_{\rm rec}(\theta) = I_{\rm rec}(2\pi f_s t)/I_{\rm out}$ , we get the dimensionless system

$$\mu = \frac{q_m}{k_i} \frac{d i_{\text{inv}}(\theta)}{d \theta} + q_m \Phi \frac{d i_{\text{rec}}(\theta)}{d \theta} + (1 - m^{\text{ON}}) v_{DS}(\theta)$$

$$1 = q_m \Phi \frac{d i_{\text{inv}}(\theta)}{d \theta} + \frac{q_m}{k_r} \frac{d i_{\text{rec}}(\theta)}{d \theta} + (1 - d^{\text{ON}}) v_{KA}(\theta)$$

$$i_{\text{inv}}(\theta) = \frac{1}{q_i} \frac{d v_{DS}(\theta)}{d \theta} \quad \text{if } m^{\text{ON}} = 0 \quad (Z_1 \text{ and } Z_2 \text{ only})$$

$$i_{\text{rec}}(\theta) = \frac{1}{q_r} \frac{d v_{KA}(\theta)}{d \theta} \quad \text{if } d^{\text{ON}} = 0 \quad (Z_2 \text{ and } Z_3 \text{ only}) \quad (7)$$

where the two boolean variables  $m^{ON}$  and  $d^{ON}$  are accounting, respectively, for MOS and diode ON/OFF state.<sup>3</sup>

Considering (7), we get a solution that is independent of the quantities  $f_s$ ,  $V_{\rm in}$ ,  $V_{\rm out}$  and  $I_{\rm out}$ , and that can be denormalized and applied to any converter identified by the same voltage ratio  $\mu$  and duty cycle D.<sup>4</sup> This will be clarified by the two examples of the following section.

#### C. DIMENSIONLESS CIRCUIT DESIGN

The ODE system in (7) can be solved to get the evolution of the converter in one period (i.e., the expressions for  $i_{inv}(\theta)$ ,  $i_{rec}(\theta)$ ,  $v_{DS}(\theta)$  and  $v_{KA}(\theta)$  for  $0 \le \theta \le 2\pi$ ) as a mathematical function of the nine dimensionless quantities

$$\mu, D, k_i, k_r, q_i, q_m, q_r, i_{inv}^{(0)}, i_{rec}^{(0)}$$

.

where  $i_{\rm inv}^{(0)}$  and  $i_{\rm rec}^{(0)}$  are the normalized counterparts of  $I_{\rm inv}^{(0)}$  and  $I_{\rm rec}^{(0)}$ . Assuming that  $\mu$  and D are given as design specifications, the other seven quantities can be considered variables to tune in order to ensure the optimal class-E operation. The desired behavior is achieved if we can ensure that

- 1) ZVS:  $v_{DS}(\theta) = 0$  immediately before the time instant when the MOS is turned ON;

- 2) ZVDS:  $dv_{DS}(\theta)/d\theta = 0$  immediately before the time instant when the MOS is turned ON;

- 3) stationary condition: to ensure that the stationary condition is achieved, one must have  $i_{\rm inv}(2\pi)=i_{\rm inv}^{(0)}$  and  $i_{\rm rec}(2\pi)=i_{\rm rec}^{(0)}$ . Furthermore, neglecting a possible (stationary) output ripple,  $V_{\rm out}$  is constant, i.e., the filter capacitance  $C_L$  has a zero-mean current. This condition is considered by imposing that the average value of

$I_{\text{rec}}(t)$  is  $-I_{\text{out}}$  or, in the dimensionless model, that the average value of  $i_{\text{rec}}(\theta)$  is -1, i.e.:

$$\frac{1}{2\pi} \int_0^{2\pi} i_{\text{rec}}(\theta) d\theta + 1 = 0$$

(8)

Following this procedure, five mathematical equations must be satisfied by the correct choice of seven unknowns. This is an underdetermined system: two unknowns can be considered free variables to be set by the designer, while the other five are set by this design procedure. Note that it is convenient to allow the procedure to set  $i_{\rm inv}^{(0)}$  and  $i_{\rm rec}^{(0)}$ , since their values are not directly related to any circuit element. Conversely,  $q_i$ ,  $q_r$ ,  $q_m$ ,  $k_i$  and  $k_r$ , once properly denormalized, set the values of  $C_{\rm inv}$ ,  $C_{\rm rec}$ , M,  $L_{\rm inv}$  and  $L_{\rm rec}$ , respectively.

A natural choice is to allocate  $k_i$  and  $k_r$  as degrees of freedom, since constraints on inductors are usually tighter with respect to those on capacitors. One could also opt to remove either  $L_{\rm inv}$  from the inverter loop (hence  $k_i=1$ ) or  $L_{\rm rec}$  from the rectifying loop ( $k_r=1$ ) for economical or space reasons. The two degrees of freedom can also be used to tune aspects of the circuit behavior that have been not considered in the optimization. As an example, one can sweep them to look for a minimum in the RMS inverter or rectifier currents for improving the converter efficiency. Another example is the investigation of the duty cycle of the diode, that has not been considered in the optimization, and that should be set to reasonable values (i.e., far enough from 0% or 100%) for optimal performance.

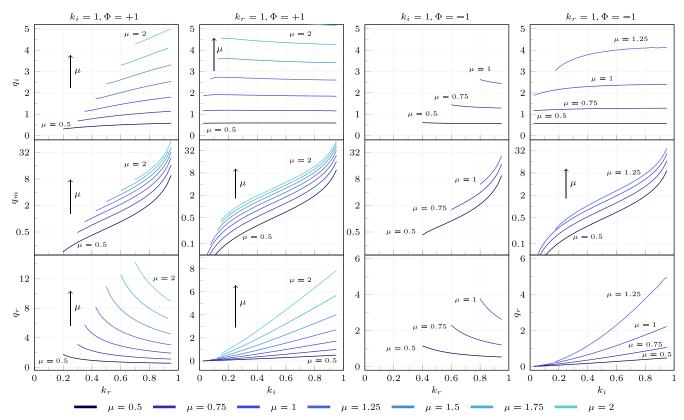

Once  $k_i$  and  $k_r$  are set, one can get the dimensionless design solution (i.e., the value of  $q_i$ ,  $q_m$  and  $q_r$ ) and then, denormalize it exploiting (6) using the actual value of  $V_{\text{out}}$ ,  $I_{\text{out}}$  and  $f_s$ , to get the  $L_{\text{inv}} + L_p$ ,  $L_{\text{rec}} + L_s$ , M,  $C_{\text{inv}}$  and  $C_{\text{rec}}$  required to ensure optimal class-E operation. The full set of design solutions for both canonical topologies ( $\Phi = +1$  and  $\Phi = -1$ ), considering different values of  $\mu$  and the two corner cases  $k_i = 1$ ,  $k_r < 1$ , and  $k_i < 1$ ,  $k_r = 1$ , is shown in Figure 7.

Two design examples are now presented with the aim of clarifying the procedure. Both are based on ideal elements, including a perfectly coupled transformer with a 1 : 1 turn ratio, for which  $L_p = L_s = M$ . Examples including realistic models of circuit elements will be presented in the next section.

Design Example 1: Let us consider a dc-dc converter designed according to the class-E topology of Figure 4(a) (i.e.  $\Phi = 1$ ) operating at 15 MHz and D = 0.5, with  $V_{\rm in} = 5$  V,  $V_{\rm out} = 3.3$  V and  $P_{\rm out} = 1$  W (so  $I_{\rm out} = 303$  mA). This is a step-down converter with  $\mu = 1.51$ . Let us also assume the constraints  $L_{\rm inv} = 3M$  and  $L_{\rm rec}$  not present in the circuit, so  $L_{\rm rec} = 0$ . In terms of dimensionless quantities, we have  $k_i = 0.25$  and  $k_r = 1$ . The values of  $q_m$ ,  $q_i$ , and  $q_r$  ensuring optimal class-E operation can be retrieved from the design curves in Figure 7 with  $k_r = 1$ ,  $\Phi = +1$ , resulting in  $q_m = 0.65$ ,  $q_i = 3.65$ ,  $q_r = 0.75$ . By using (6) we get the denormalized values for the transformer inductance  $L_p = L_s = M = 75$  nH, the inverter loop

$<sup>^3</sup>$ We set  $m^{\rm ON}(d^{\rm ON})=1$  when the MOS (diode) is ON and 0 when OFF. Also, please note that the parameter  $q_m$  replaces what in [29] authors indicated as  $q_x$ .

<sup>&</sup>lt;sup>4</sup>Despite being usually set to D = 0.5, we would like to stress that D can actually be considered a degree of freedom in the converter design.

**FIGURE 7.** Class-E resonant converter design curves when considering ideal circuital elements and with D=0.5, for different values of  $\mu$ ,  $k_i$  and  $k_r$ . From left to right: In-phase coupling, with  $L_{\text{rec}}=0\,\text{H}$  ( $k_j=1$ ,  $\Phi=+1$ ); in-phase coupling, with  $L_{\text{inv}}=0\,\text{H}$  ( $k_r=1$ ,  $\Phi=+1$ ); 180° out-of-phase coupling, with  $L_{\text{inv}}=0\,\text{H}$  ( $k_f=1$ ,  $\Phi=-1$ ); 180° out-of-phase coupling, with  $L_{\text{inv}}=0\,\text{H}$  ( $k_f=1$ ,  $\Phi=-1$ ).

inductance  $L_{\rm inv}=225$  nH, and the capacitors  $C_{\rm inv}=267$  pF and  $C_{\rm rec}=1.3$  nF. The waveforms shown in Figure 5(a) have been achieved from a SPICE simulation using these values.

Design Example 2: Let us consider a 12 V-to-18 V ( $\mu=0.667$ ) step-up dc-dc converter operating at 75 MHz and D=0.5 with 4.2 W output power ( $I_{\rm out}=233$  mA). Let us also consider a 180° out-of-phase topology (i.e.,  $\Phi=-1$ ) without  $L_{\rm inv}$  (so  $L_{\rm inv}=0$ ) and  $L_{rec}=M$ , hence  $k_i=1$  and  $k_r=0.5$ . According to the design curves in Figure 7 for  $k_i=1$ ,  $\Phi=-1$  we get  $q_m=0.84$ ,  $q_i=1.09$ ,  $q_r=1.98$ , that leads to  $L_{\rm rec}=M=137$  nH,  $C_{\rm inv}=25.2$  pF and  $C_{\rm rec}=13.9$  pF. These values have been used for the simulation shown in Figure 5(b).

#### D. LOSSY CIRCUIT DESIGN

It is possible to include major sources of losses in (7) as long as the device models are linear. Let us consider, for all elements in the circuit, a series resistance expressed by means of a quality factor for passive elements (inductors, capacitors, and transformer) or an on-state resistance for switches ( $R_{DS}^{\rm ON}$  for the MOS and  $R_{D}^{\rm ON}$  for the diode), and a voltage drop  $V_{D}^{\rm ON}$  for the diode, as summarized in Figure 8. Let us also refer to the quality factors of  $L_{\rm inv}$ ,  $L_{\rm rec}$ ,  $C_{\rm inv}$ , and  $C_{\rm rec}$  as  $Q_{L_{\rm inv}}$ ,  $Q_{L_{\rm rec}}$ ,  $Q_{C_{\rm inv}}$  and  $Q_{C_{\rm rec}}$ , respectively. With this, it is possible to recompute (7) as (9), as shown at the bottom of the next page, where we have set the additional dimensionless

$$\begin{split} & \bigvee_{I_{\rm L}(t)} I_{\rm C}(t) & \stackrel{I_{p}(t)}{\longrightarrow} I_{\rm p}(t) & \stackrel{n_{\rho}:n_s}{\longrightarrow} I_{\rm g}(t) \\ & \bigvee_{V_{\rm L}(t)} \bigvee_{V_{\rm p}(t)} (t) & \stackrel{I_{\rm p}(t)}{\longrightarrow} V_{\rm s}(t) & \stackrel{I_{\rm D}(t)}{\longrightarrow} V_{\rm DS}(t) & \stackrel{I_{\rm L}(t)}{\longrightarrow} V_{\rm KA}(t) \end{split}$$

$$& V_{L}(t) = L \frac{dI_{L}(t)}{dt} + L \frac{2\pi f_{s}}{Q_{L}} I_{L}(t) \\ & V_{C}(t) = \frac{1}{C} \int I_{C}(t) dt + \frac{1}{2\pi f_{s} C Q_{C}} I_{C}(t) \\ & \left( \begin{matrix} V_{p}(t) \\ V_{S}(t) \end{matrix} \right) = \begin{pmatrix} L_{p} & \Phi M \\ \Phi M & L_{s} \end{pmatrix} \frac{d}{dt} \begin{pmatrix} I_{p}(t) \\ I_{s}(t) \end{pmatrix} + 2\pi f_{s} \begin{pmatrix} L_{p}/Q_{L_{p}} \pm M/Q_{M} \\ \pm M/Q_{M} & L_{s}/Q_{L_{s}} \end{pmatrix} \begin{pmatrix} I_{p}(t) \\ I_{s}(t) \end{pmatrix} \\ & \begin{cases} V_{\rm DS}(t) = R_{\rm DS}^{\rm ON} I_{D}(t), & m^{\rm ON} = 1 \\ I_{D}(t) = 0, & m^{\rm ON} = 0 \\ \end{cases} \\ & \begin{cases} V_{\rm KA}(t) = -V_{D}^{\rm ON} + R_{D}^{\rm ON} I_{K}(t), & d^{\rm ON} = 1 \\ I_{K}(t) = 0, & d^{\rm ON} = 0 \end{cases} \end{split}$$

FIGURE 8. Device models used for including major sources of losses in the converter analysis.

factor

$$g_{DS}^{\mathrm{ON}} = \frac{V_{\mathrm{out}}}{I_{\mathrm{out}}} \frac{1}{R_{DS}^{\mathrm{ON}}}, \quad g_{D}^{\mathrm{ON}} = \frac{V_{\mathrm{out}}}{I_{\mathrm{out}}} \frac{1}{R_{D}^{\mathrm{ON}}}, \ v_{d}^{\mathrm{ON}} = \frac{V_{D}^{\mathrm{ON}}}{V_{\mathrm{out}}}$$

and where, for a more compact notation, we have defined

$$\frac{1}{Q_{\text{inv}}} = \frac{1}{L_{\text{inv}} + L_p - M} \left( \frac{L_{\text{inv}}}{Q_{L_{\text{inv}}}} + \frac{L_p}{Q_{L_p}} - \frac{M}{Q_M} \right)$$

$$\frac{1}{Q_{\text{rec}}} = \frac{1}{L_{\text{rec}} + L_s - M} \left( \frac{L_{\text{rec}}}{Q_{L_{\text{rec}}}} + \frac{L_s}{Q_{L_s}} - \frac{M}{Q_M} \right)$$

The only approximation used in computing (9) is to neglect the effects of the  $C_{\text{inv}}$  and of the  $C_{\text{rec}}$  when the MOS and the diode are ON, respectively.

By computing  $i_{\text{inv}}(\theta)$ ,  $i_{\text{rec}}(\theta)$ ,  $v_{DS}(\theta)$  and  $v_{KA}(\theta)$  using (9), and replacing the obtained expression in the approach described in Section III-C, it is possible to get a design that keeps into account many sources of losses in the circuit design. The examples considered in the next section are based on this approach.

Of course, this design approach holds as long as the model for the considered devices is valid. Taking into account some non-linear effects, a more complex model, or other effects (such as a non-negligible reverse recovery time for the diode, that can strongly affect the design at particularly high operating frequencies) is not possible. Indeed, we do not consider this a limitation of the approach, as it will affect in the same way any other design approach. Nevertheless, in presence of a strong non-linearity, this design strategy can be still be used to get a very good starting design point (i.e., better with respect to what can be obtained with any other design approach proposed in the Literature), to be refined by further SPICE simulations.

#### **IV. CLASS-E NON-ISOLATED TOPOLOGIES**

Despite being useful in many applications, galvanic isolation is not always required. In this case, a simpler and cheaper non-isolated implementation can be achieved by considering the architectures in Figure 4(a) and (b) and replacing the coupling transformer with an inductor whose inductance value is  $M = L_p = L_s$ , the quality factor  $Q_M = Q_{L_p} = Q_{L_s}$ , and the current flowing into it is  $I_m$ .

Even considering a possible different circuit layout, the design approach described in Section III can still be applied if

- the circuit evolution is still described by (7), or by (9) if the lossy design is to be taken into account;

- the constraints to achieve ZVS, ZVDS and the stationary condition are still expressed as in III-C.

In [29] this approach has been followed, and authors presented a non-isolated class-E dc-dc converter whose schematic is derived from that of Figure 4(a) by directly replacing the transformer with an inductor M. Yet, this approach has the disadvantage that, in the achieved circuit,

input and output voltages do not share the same ground reference.

In the following we present how to conveniently rearrange the two presented canonical topologies to obtain a resonant class-E buck-boost dc-dc converter with common ground reference. Similarly, we also show how the scheme of Figure 4(b) can be turned either into an equivalent buck (step-down) or boost (step-up) resonant converter. All these non-isolated topologies can be designed by means of the curves proposed in Figure 7.

In order to simplify the notation, it is convenient to define the quantity  $\nu$  computed as the average value of the normalized inverter mesh current

$$\frac{1}{2\pi} \int_0^{2\pi} i_{\text{inv}}(\theta) d\theta = \nu \tag{10a}$$

In a lossless converter, it is  $\nu=1/\mu$ , while it is  $\nu>1/\mu$  considering the lossy analysis of Section III-D. The average value of the  $I_{\rm inv}(t)$  (i.e., the converter input current for the topologies of Figure 4) can be denormalized as  $\nu I_{\rm out}$ . Note that  $\nu$  can also be used to compute the converter efficiency: for both topologies of Figure 4, the efficiency is given by  $\eta=V_{\rm out}I_{\rm out}/(\mu V_{\rm out}\nu I_{\rm out})=1/(\mu\nu)$ . Furthermore, since  $i_{\rm inv}(t)=i_{\rm inv}(t)+\Phi i_{\rm rec}(t)$ , we get

$$\frac{1}{2\pi} \int_0^{2\pi} i_{\rm m}(\theta) d\theta = \nu - \Phi \tag{10b}$$

so that the average value of the  $I_{\rm m}(t)$  can be denormalized as  $(\nu-\Phi)I_{\rm out}$ .

#### A. BUCK-BOOST CONFIGURATION

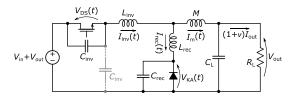

The circuit depicted in Figure 9(a) comes directly from that of Figure 4(a) when the transformer is replaced by M and circuit elements are rearranged (e.g., the MOS and the diode are connected to the input and the output node, respectively) to ensure a common ground reference for  $V_{\rm in}$  and  $V_{\rm out}$ . The drawback is that the MOS source terminal is not connected anymore to the ground reference, so either a N-MOS with a bootstrap circuit (as implicitly assumed), or a P-MOS device, is required. We refer to this topology as the non-inverting buck-boost, since it is capable to act either as a step-up  $(V_{\rm out} > V_{\rm in}, \mu < 1)$  or a step-down converter  $(V_{\rm out} < V_{\rm in}, \mu > 1)$ . However, it is worth noting that, once designed, the resonant converter is constrained to operate either in

$$\mu = \frac{q_m}{k_i} \frac{di_{\text{inv}}(\theta)}{d\theta} + \Phi q_m \frac{di_{\text{rec}}(\theta)}{d\theta} + \left(\frac{1 - k_i}{k_i} \frac{q_m}{Q_{\text{inv}}} + \frac{q_m}{Q_M} + \frac{\left(1 - m^{\text{ON}}\right) q_i}{Q_{C_{\text{inv}}}} + \frac{m^{\text{ON}}}{g_{DS}}\right) i_{\text{inv}}(\theta) + \Phi \frac{q_m}{Q_M} i_{\text{rec}}(\theta) + \left(1 - m^{\text{ON}}\right) v_{C_{\text{inv}}}(\theta)$$

$$1 = \Phi q_m \frac{di_{\text{inv}}(\theta)}{d\theta} + \frac{q_m}{k_r} \frac{di_{\text{rec}}(\theta)}{d\theta} + \Phi \frac{q_m}{Q_M} i_{\text{inv}}(\theta) + \left(\frac{1 - k_r}{k_r} \frac{q_m}{Q_{\text{rec}}} + \frac{q_m}{Q_M} + \frac{\left(1 - d^{\text{ON}}\right) q_r}{Q_{C_{\text{rec}}}} + \frac{d^{\text{ON}}}{g_D^{\text{ON}}}\right) i_{\text{rec}}(\theta)$$

$$+ \left(1 - d^{\text{ON}}\right) v_{C_{\text{rec}}}(\theta) - d^{\text{ON}} v_D^{\text{ON}}$$

$$i_{\text{inv}}(\theta) = \frac{1}{q_i} \frac{dv_{C_{\text{inv}}}(\theta)}{d\theta} \quad (Z_1 \text{ and } Z_2 \text{ only}), \quad i_{\text{rec}}(\theta) = \frac{1}{q_r} \frac{dv_{C_{\text{rec}}}(\theta)}{d\theta} \quad (Z_2 \text{ and } Z_3 \text{ only})$$

$$(9)$$

FIGURE 9. Comparison between buck-boost topologies. (a) non-inverting class-E resonant buck-boost converter. (b) inverting class-E resonant buck-boost converter.

buck or boost mode and, in order to preserve the desired ZVS/ZVDS behavior, the ratio  $\mu$  between the input and the output voltages should not change.

In this circuit the same inverter and a rectifier meshes as in the circuits of Figure 4 are clearly identifiable. Being  $I_{\rm m}(t)=I_{\rm inv}(t)+I_{\rm rec}(t)$ , the meshes are still described by the two equations in (4) assuming  $\Phi=+1$ . In conclusion, there is a perfect equivalence between the equations regulating the behavior of this circuit, and the one considered in Section III-B. Since it is easy to see that (8) still holds, this circuit can be designed through the curves in Figure 7, either with  $k_i=1$ ,  $\Phi=+1$  (when  $L_{\rm inv}=0$ ) or  $k_r=1$ ,  $\Phi=+1$  (when  $L_{\rm rec}=0$ ).

A buck-boost converter equivalent to the  $180^{\circ}$  out-of-phase coupling topology is depicted in Figure 9(b). Here,  $I_{\rm m}(t) = I_{\rm inv}(t) - I_{\rm rec}(t)$ , so  $\Phi = -1$ . This converter can be designed through the curves in Figure 7 with  $k_i = 1$ ,  $\Phi = -1$  (when  $L_{\rm inv} = 0$ ) or with  $k_r = 1$ ,  $\Phi = -1$  (when  $L_{\rm rec} = 0$ ) and it is actually an inverting buck-boost topology, since the output voltage node is at a negative potential with respect to the common ground reference.

Note that, in both schematics of Figure 9, both  $C_{\rm inv}$  and  $C_{\rm rec}$  can be connected either in their standard position (i.e., in parallel to the MOS and the diode), or in an alternative position directly connected to ground as shown in light gray the figure. Focusing on  $C_{\rm inv}$ , the current flowing into it when it is connected in the alternative position, under the assumption of an ideal model for the capacitor and a perfectly constant  $V_{\rm in}$ , can be computed with the MOS OFF as

$$I_{C_{\text{inv}}}(t) = C_{\text{inv}} \frac{dV_{C_{\text{inv}}}}{dt} = C_{\text{inv}} \frac{d(V_{DS}(t) - V_{\text{in}})}{dt} = C_{\text{inv}} \frac{dV_{DS}(t)}{dt}$$

that is the same current one get assuming that the  $C_{\text{inv}}$  is in the standard position. So, in both configurations, the contribution of  $C_{\text{inv}}$  to the  $I_{\text{inv}}(t)$  is the same.

Yet, when introducing a lossy model, the perfect equivalence is lost. Nevertheless, it is very easy to find capacitors with very high quality factors, so the difference between the

FIGURE 10. Waveforms in the non-inverting buck-boost design example proposed in Section IV-A.

two configurations is expected to be limited, and both of them are indeed found in the literature.

Design Example 3: let us consider the design of a 10 W, 12 V-to-15 V class-E converter with the buck-boost topology of Figure s-E converter with the buck-boost topology, operating at 15 MHz with D = 0.5. Let us also assume that  $L_{\text{inv}} = L_{\text{rec}} = M$  (so that  $k_i = 0.5$  and  $k_r = 0.5$ ). The design parameters are  $V_{\rm in}=12$  V,  $V_{\rm out}=15$  V, and  $\mu=0.8$ . Furthermore,  $I_{\text{out}} = 667 \,\text{mA}$ . Let us assume that  $Q_{L_{\text{inv}}} =$  $Q_{L_{rec}} = Q_M = 80$ , and that the capacitors  $C_{inv}$  and  $C_{rec}$  has an infinite quality factor.<sup>5</sup> Let us also choose a Si2392ADS MOS from Vishay (modeled with  $R_{DS}^{\rm ON}=0.1\,\Omega$ ) and a Nexperia PMEG6030ELP Schottky barrier rectifier diode (modeled with  $V_D^{\rm ON} = 0.55 \, {\rm V}$  and  $R_D^{\rm ON} = 0.1 \, \Omega$ ). The solution we get from the dimensionless system is  $q_i = 0.887$ ,  $q_r = 0.685$ and  $q_m = 0.314$ , that leads to  $L_{inv} = L_{rec} = M = 75 \text{ nH}$ ,  $C_{\text{inv}} = 420 \,\text{pF}$  and  $C_{\text{rec}} = 560 \,\text{pF}$ . Note that a straightforward application of (6) would lead to slightly higher values of  $C_{inv}$ and of  $C_{rec}$ ; the values proposed here have been decreased by 110 pF and 130 pF, respectively, to compensate the parasitic capacitance of the MOS and of the diode. The waveforms observed in a SPICE simulation that takes into account the semiconductor device models supplied by the producer can be seen in Figure 10. The optimal class-E operation is visibly achieved, and the output power, that is evaluated in 10.3 W, settles to a value very similar to the desired one.

#### **B. BUCK CONFIGURATION**

The circuit shown in Figure 11 is a resonant buck converter. Similar resonant or quasi-resonant topologies appeared many times in the recent literature. Authors in [32] proposed a ZVS buck converter with non-resonant rectifier (i.e., without  $C_{\rm rec}$ ) and where the  $L_{\rm rec}$  is not used. In [33] authors presented an overview of different ZVS converter topologies, including that of Figure 11 in the two alternatives where only one inductor among  $L_{\rm inv}$  and  $L_{\rm rec}$  is present. In [36] a buck converter is

<sup>5</sup>Ceramic capacitors with C0G dielectric ensure extremely high performance (quality factor > 1000) so that they can be assumed ideal.

FIGURE 11. Class-E resonant buck converter.

proposed based on the schematic of Figure 11 without the rectifier inductance  $L_{\rm rec}$ . In [30] a 15 MHz converter with the same schematic in the latter configuration is analyzed and designed.

Let us refer to the design of a companion converter according to the isolated canonical topology with 180° out-of-phase coupling (i.e.,  $\Phi = -1$ ), and let us indicate with  $V_{\rm in}$ ,  $V_{\rm out}$  and  $I_{\rm out}$  as the input voltage, output voltage and output current of this design. As clarified below, the behavior of the converter in Figure 11 is the same of the companion one assuming that we indicate with  $V_{\rm in} + V_{\rm out}$  its input voltage level, and with  $V_{\rm out}$  its output voltage level, with  $\mu = V_{\rm in}/V_{\rm out}$ . Note that, with this, the output voltage is compelled to be always smaller than the input one independently of  $\mu$ .

Then, as assumed in previous designs, capacitors  $C_{\rm inv}$  and  $C_{\rm rec}$  if large enough may mask, respectively, the parasitic capacitances of the MOS and the diode; M replaces the transformer with  $I_{\rm m}=I_{\rm inv}(t)-I_{\rm rec}(t)$  and  $L_p=L_s=M$ . Hence, if we consider the Kirchhoff voltage law at the outer mesh, we get

$$V_{\text{in}} + V_{\text{out}} = V_{DS}(t) + L_{\text{inv}} \frac{dI_{\text{inv}}(t)}{dt} + M \frac{dI_{\text{m}}(t)}{dt} + V_{\text{out}}$$

that is the same as (4a), while the equation of the rectifier mesh

$$V_{\text{out}} = V_{\text{KA}}(t) + L_{\text{rec}} \frac{dI_{\text{rec}}(t)}{dt} - M \frac{dI_{\text{m}}(t)}{dt}$$

is (4b). Finally, the output current of the converter of Figure 11 is given by the average value of  $I_m(t)$ . Let us indicate with  $I_{\text{out}}$  the output current of the companion converter, and assume that its design has been obtained using (8). According to (10b) the output current of the buck converter is given by  $(\nu + 1)I_{\text{out}}$ .

In conclusion, with the introduced notation, all equations regulating the evolution of the canonical topology with  $\Phi = -1$  hold also for the buck topology, that can be so designed by means of the curves in Figure 7.

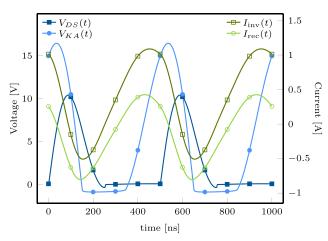

Design Example 4: let us consider a 2.5 W, 8 V-to-5 V class-E buck converter working at 2 MHz with D=0.5. We target a design where  $L_{\rm inv}=0$ , and  $L_{\rm rec}=M$ , so we set the two degrees of freedom  $k_i=1$  and  $k_r=0.5$ . Due to the buck topology, we have  $V_{\rm in}+V_{\rm out}=8$  V,  $V_{\rm out}=5$  V and  $(1+\nu)I_{\rm out}=500$  mA. In order to get the converter design, we should consider a companion  $180^\circ$  out-of-phase coupled converter with  $V_{\rm in}=3$  V,  $V_{\rm out}=5$  V and  $\mu=0.6$ , while  $I_{\rm out}$  is not know yet since we do not have an estimation of  $\nu$  yet. By considering  $Q_{L_{\rm rec}}=Q_{M}=40$ , assuming that the capacitors  $C_{\rm inv}$  and  $C_{\rm rec}$  have an infinite quality factors,

FIGURE 12. Waveforms in the buck design example proposed in Section IV-B.

FIGURE 13. Class-E resonant boost converter.

and that the MOS and the diode are a IRLML0030TRP from International Rectifier (modeled with  $R_{DS}^{ON} = 0.1 \Omega$ ) and a ES1B from Diodes Incorporated (modeled with  $V_D^{ON} =$  $0.75 \,\mathrm{V}$  and  $R_D^{\mathrm{ON}} = 0.15 \,\Omega$ ), the optimal design is achieved with the dimensionless parameters  $q_i = 0.456$ ,  $q_r = 0.635$ ,  $q_m = 0.552$ . The lossy dimensionless system has  $\nu =$ 2.61, that allows us to estimate the current of the canonical companion converter as  $I_{\text{out}} = 138 \,\text{mA}$ . Using these values, we can denormalize the solution in  $L_{rec} = M = 1.59 \,\mu\text{H}$ ,  $C_{\rm inv} = 4.8\,{\rm nF}$  and  $C_{\rm rec} = 3.5\,{\rm nF}$ . Being the  $C_{\rm inv}$  and  $C_{\rm rec}$ much larger than the MOS and the diode parasitic capacitances, no correction on their values have been applied. The observed waveforms from a SPICE simulation based on the semiconductor models developed by the producer can be seen in Figure 12, and show that the optimal class-E operation is well achieved. The output power is evaluated in 2.51 W.

#### C. BOOST CONFIGURATION

The circuit in Figure 13 represents a resonant boost converter. This topology, in the two alternative implementations with  $L_{\rm inv}=0$  or  $L_{\rm rec}=0$ , is actually one of the most commonly used in the literature due to its simplicity.<sup>6</sup> In their overview of different ZVS converter topologies in [33], authors included both implementations. In [37] a ZVS boost converter without  $L_{\rm rec}$  and with a non-resonant rectifier (i.e., without  $C_{\rm rec}$ ) is proposed. In [38] a particular circuit, indicated as  $\Phi_2$  converter, has been introduced. This is basically a boost converter like that in Figure 13 with  $L_{\rm inv}=0$ , whose peculiarity is to present an additional LC resonant

$<sup>^6\</sup>mathrm{As}$  an example, in the schematic of Figure 13 there is no need for any bootstrap circuit.

FIGURE 14. Waveforms in the boost design example proposed in Section IV-C.

circuit whose aim is to reduce the peak value of the voltage  $V_{DS}(t)$  across the main switch. The dc-dc converter in [39] is a boost circuit presenting a small variation with respect to that of Figure 13, where only the  $L_{\rm rec}$  is present. The converter proposed in [27] by Burkhart *et al.* is fully resonant boost converter featuring ZVS. The converter topology is that of Figure 13 where only the  $L_{\rm rec}$  has been considered, while  $L_{\rm inv}=0$ .

As in the previous case, also the boost converter of Figure 13 is perfectly described by the equations regulating the behavior of the canonical 180° out-of-phase coupled converter. To see this, let us indicate with  $V_{\rm in}$  the input voltage level and with  $V_{\rm in}+V_{\rm out}$  the voltage at the output node. Let also be  $I_{\rm out}$  the output current, and  $\mu=V_{\rm in}/V_{\rm out}$ . The capacitor  $C_{\rm rec}$ , either connected in canonical or in the alternative position, is capable to mask diode parasitic capacitance. Then, the equation regulating the inverter mesh

$$V_{\rm in} = M \frac{dI_{\rm m}(t)}{dt} + L_{\rm inv} \frac{dI_{\rm inv}(t)}{dt} + V_{DS}(t)$$

is (4a), while the equation of the outer mesh

$$V_{\text{out}} + V_{\text{in}} = V_{KA}(t) + L_{\text{rec}} \frac{dI_{\text{rec}}(t)}{dt} - M \frac{dI_{\text{m}}(t)}{dt} + V_{\text{in}}$$

is equal to (4b) under the assumption that  $\Phi = -1$  and  $L_p = L_s = M$ . Furthermore, according to the figure, we get  $I_{\rm m}(t) = I_{\rm inv}(t) - I_{\rm rec}(t)$ . Finally, the output current is given by the average value of  $-I_{\rm rec}(t)$ , and since (8) holds, is simply given by  $I_{\rm out}$ . In conclusion, as in the previous case, all equations regulating the behavior of the canonical circuit with  $\Phi = -1$  hold, so the circuit design can be achieved by means of the design curves in Figure 7.

Design Example 5: consider a 16 V-to-60 V class-E boost converter working at 30 MHz with D=0.5 and with a 25 W output power. We target a design where  $L_{\rm rec}=0$ , and  $L_{\rm inv}=M$ . To ensure this, the two degrees of freedom are set to  $k_i=0.5$  and  $k_r=1$ . Relying on a boost topology, we have  $V_{\rm in}=16$  V,  $V_{\rm in}+V_{\rm out}=60$  V. Parameters of the companion canonical system are  $\Phi=-1$  (i.e., 180° out-of-phase coupling),  $V_{\rm in}=16$  V,  $V_{\rm out}=44$  V and

$I_{\rm out}=417$  mA, with  $\mu=0.364$ . Here we consider  $Q_{L_{\rm inv}}=Q_{M}=70$  and that  $C_{\rm inv}$  and  $C_{\rm rec}$  have an infinite quality factor. The MOS is a STL4N10F7, and the diode a STPSC406, both from ST semiconductors, modeled with  $R_{DS}^{\rm ON}=50$  m $\Omega$ ,  $V_{D}^{\rm ON}=1.0$  V and  $R_{D}^{\rm ON}=0.5$   $\Omega$ . The solution of the dimensionless system is  $q_{i}=0.206$ ,  $q_{r}=0.102$ ,  $q_{m}=0.217$ , that can be denormalized in  $L_{\rm inv}=M=122$  nH,  $C_{\rm inv}=110$  pF and  $C_{\rm rec}=450$  pF. The values of  $C_{\rm inv}$  and  $C_{\rm rec}$  have been reduced by 130 pF and 40 pF in order to compensate the parasitic capacitance introduced by the MOS and the diode. The observed waveforms from a SPICE simulation based on the semiconductor models provided by ST can be seen in Figure 14. The output power in the simulation is evaluated in 23.9 W.

Note that this example is the most critical one, mainly due to the very high operating frequency. In particular, the adherence of the output power with the desired one is the lowest among all proposed examples. This is due to the fact that the lossy model assumed in Section III-D has reached its limit, since the non-linear parasitic capacitances of the active devices are not anymore negligible with respect to the  $C_{\rm inv}$  and  $C_{\rm rec}$ . Indeed, the simulation still shows more than acceptable performance.

#### **V. CONCLUSION**

In this paper many resonant and quasi resonant converter architectures proposed in the literature in the last three decades have been taken into account. We have shown that, despite presenting different implementation, and even different topologies (fly-back, buck-boost, buck or boost), all of them can be described by the same mathematical equations. As a result, all considered converters can be divided into two groups, one of them perfectly equivalent to an isolated topology with a transformer featuring in-phase coupling, and the other to the same isolated topology with 180° out-of-phase coupling. A comprehensive analysis and design theory for the two canonical topologies is provided, that can be considered as a unified design theory for the whole family of resonant architectures.

#### **REFERENCES**

- N. O. Sokal and A. D. Sokal, "Class E-A new class of high-efficiency tuned single-ended switching power amplifiers," *IEEE J. Solid-State Circuits*, vol. SSC-10, no. 3, pp. 168–176, Jun. 1975.

- [2] R. J. Gutmann, "Application of RF circuit design principles to distributed power converters," *IEEE Trans. Ind. Electron. Control Instrum.*, vol. IECI-27, no. 3, pp. 156–164, Aug. 1980.

- [3] R. Redl, B. Molnar, and N. O. Sokal, "Class E resonant regulated DC/DC power converters: Analysis of operations, and experimental results at 1.5 MHz," *IEEE Trans. Power Electron.*, vol. PE-1, no. 2, pp. 111–120, Apr. 1986.

- [4] K.-H. Liu, R. Oruganti, and F. C. Y. Lee, "Quasi-resonant converters-topologies and characteristics," *IEEE Trans. Power Electron.*, vol. PE-2, no. 1, pp. 62–71, Jan. 1987.

- [5] M. K. Kazimierczuk and J. Jozwik, "Resonant DC/DC converter with class-E inverter and class-E rectifier," *IEEE Trans. Ind. Electron.*, vol. 36, no. 4, pp. 468–478, Nov. 1989.

- [6] D. J. Perreault, J. Hu, J. M. Rivas, Y. Han, O. Leitermann, R. C. N. Pilawa-Podgurski, A. Sagneri, and C. R. Sullivan, "Opportunities and challenges in very high frequency power conversion," in *Proc. 24th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Feb. 2009, pp. 1–14.

- [7] M. K. Kazimierczuk and D. Czarkowski, Resonant Power Converters, 2nd ed. Hoboken, NJ, USA: Wiley, 2011.

- [8] M. K. Kazimierczuk, RF Power Amplifiers, 2nd ed. Hoboken, NJ, USA: Wiley, 2014.

- [9] F. Pareschi, R. Rovatti, and G. Setti, "EMI reduction via spread spectrum in DC/DC converters: State of the art, optimization, and tradeoffs," *IEEE Access*, vol. 3, pp. 2857–2874, 2015.

- [10] G. Setti, M. Balestra, and R. Rovatti, "Experimental verification of enhanced electromagnetic compatibility in chaotic FM clock signals," in *Proc. IEEE Int. Symp. Circuits Syst.*, vol. 3, May 2000, pp. 229–232.

- [11] F. Pareschi, G. Setti, and R. Rovatti, "A 3-GHz serial ATA spread-spectrum clock generator employing a chaotic PAM modulation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 10, pp. 2577–2587, Oct. 2010.

- [12] F. Pareschi, G. Setti, R. Rovatti, and G. Frattini, "Practical optimization of EMI reduction in spread spectrum clock generators with application to switching DC/DC converters," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4646–4657, Sep. 2014.

- [13] F. Pareschi, G. Setti, R. Rovatti, and G. Frattini, "Short-term optimized spread spectrum clock generator for EMI reduction in switching DC/DC converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 10, pp. 3044–3053, Oct. 2014.

- [14] M. Hayati, A. Lotfi, M. K. Kazimierczuk, and H. Sekiya, "Generalized design considerations and analysis of class-E amplifier for sinusoidal and square input voltage waveforms," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 211–220, Jan. 2015.

- [15] M. K. Kazimierczuk and J. Jozwik, "Class-E zero-voltage-switching and zero-current-switching rectifiers," *IEEE Trans. Circuits Syst.*, vol. 37, no. 3, pp. 436–444, Mar. 1990.

- [16] J. J. Jozwik and M. K. Kazimierczuk, "Analysis and design of class-E<sup>2</sup> DC/DC converter," *IEEE Trans. Ind. Electron.*, vol. 37, no. 2, pp. 173–183, Apr. 1990

- [17] H. Sekiya, J. Lu, and T. Yahagi, "Design of generalized class E<sup>2</sup> DC/DC converter," in *Proc. IEEE Int. Symp. Circuits Syst.*, vol. 3, May 2002, p. 3.

- [18] T. Nagashima, X. Wei, E. Bou, E. Alarcón, M. K. Kazimierczuk, and H. Sekiya, "Steady-state analysis of isolated class-E<sup>2</sup> converter outside nominal operation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 4, pp. 3227–3238, Apr. 2017.

- [19] M. K. Kazimierczuk and J. Jozwik, "Optimal topologies of resonant DC/DC converters," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 25, no. 3, pp. 363–372, May 1989.

- [20] A. Ivascu, M. K. Kazimierczuk, and S. Birca-Galateanu, "Class E resonant low dv/dt rectifier," *IEEE Trans. Circuits Syst. I. Fundam. Theory Appl.*, vol. 39, no. 8, pp. 604–613, Aug. 1992.

- [21] H. Sekiya, T. Ezawa, and Y. Tanji, "Design procedure for class E switching circuits allowing implicit circuit equations," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 11, pp. 3688–3696, Dec. 2008.

- [22] G. Chen, Y. Deng, Y. Tao, X. He, Y. Wang, and Y. Hu, "Topology derivation and generalized analysis of zero-voltage-switching synchronous DC–DC converters with coupled inductors," *IEEE Trans. Ind. Electron.*, vol. 63, no. 8, pp. 4805–4815, Aug. 2016.

- [23] J.-W. Yang and H.-L. Do, "Soft-switching dual-flyback DC–DC converter with improved efficiency and reduced output ripple current," *IEEE Trans. Ind. Electron.*, vol. 64, no. 5, pp. 3587–3594, May 2017.

- [24] K. J. Herman and R. E. Zulinski, "The infeasibility of a zero-current switching class-E amplifier," *IEEE Trans. Circuits Syst.*, vol. 37, no. 1, pp. 152–154, Jan. 1990.

- [25] J. M. Rivas, O. Leitermann, Y. Han, and D. J. Perreault, "A very high frequency dc-dc converter based on a class φ<sub>2</sub> resonant inverter," *IEEE Trans. Power Electron.*, vol. 26, no. 10, pp. 2980–2992, Oct. 2011.

- [26] A. Mediano and N. O. Sokal, "A class-E RF power amplifier with a flattop transistor-voltage waveform," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5215–5221, Nov. 2013.

- [27] J. M. Burkhart, R. Korsunsky, and D. J. Perreault, "Design methodology for a very high frequency resonant boost converter," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1929–1937, Apr. 2013.

- [28] S. Park and J. Rivas-Davila, "Duty cycle and frequency modulations in class-E DC-DC converters for a wide range of input and output voltages," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10524–10538, Dec. 2018.

- [29] N. Bertoni, G. Frattini, R. G. Massolini, F. Pareschi, R. Rovatti, and G. Setti, "An analytical approach for the design of class-E resonant DC-DC converters," *IEEE Trans. Power Electron.*, vol. 31, no. 11, pp. 7701–7713, Nov. 2016.

- [30] S. V. Mollov and A. J. Forsyth, "Design and evaluation of a multi-resonant buck converter at 15 MHz," in *Proc. 7th Int. Power Electron. Variable* Speed Drives, Sep. 1998, pp. 139–144.

- [31] Y. S. Lee and Y. C. Cheng, "A 580 kHz switching regulator using onoff control," *J. Inst. Electron. Radio Eng.*, vol. 57, no. 5, pp. 221–226, Sep./Oct. 1987.

- [32] W. A. Tabisz, P. M. Gradzki, and F. C. Y. Lee, "Zero-voltage-switched quasi-resonant buck and flyback converters-experimental results at 10 MHz," *IEEE Trans. Power Electron.*, vol. 4, no. 2, pp. 194–204, Apr. 1989.

- [33] M. Shoyama, K. Harada, H. Saen, and M. Moriya, "Voltage resonant buck-boost converter using multi-layer-winding transformer," in *Proc.* 20th Annu. IEEE Power Electron. Spec. Conf. (PESC), vol. 2, Jun. 1989, pp. 895–901.

- [34] H. Matsuo, H. Hayashi, F. Kurokawa, and T. Koga, "A general analysis of the zero-voltage switched quasi-resonant buck-boost type DC-DC converter in the continuous and discontinuous modes of the reactor current," in *Proc. 13th Int. Telecommun. Energy Conf. (INTELEC)*, Nov. 1991, pp. 472–479.

- [35] Z.-S. Ling, T.-J. Liang, L.-S. Yang, and T.-H. Li, "Design and implementation of interleaved quasi-resonant DC-DC flyback converter," in *Proc. Int. Conf. Power Electron. Drive Syst. (PEDS)*, Nov. 2009, pp. 429–433.

- [36] I. Barbi, J. C. O. Bolacell, D. C. Martins, and F. B. Libano, "Buck quasiresonant converter operating at constant frequency: Analysis, design, and experimentation," *IEEE Trans. Power Electron.*, vol. 5, no. 3, pp. 276–283, Jul. 1990.

- [37] T. Taufik, P. Luther, and M. Anwari, "Digitally controlled ZVS quasiresonant boost converter with m-type switch," in *Proc. Int. Conf. Intell.* Adv. Syst. (ICIAS), Nov. 2007, pp. 823–828.

- [38] R. C. N. Pilawa-Podgurski, A. D. Sagneri, J. M. Rivas, D. I. Anderson, and D. J. Perreault, "Very-high-frequency resonant boost converters," *IEEE Trans. Power Electron.*, vol. 24, no. 6, pp. 1654–1665, Jun. 2009.

- [39] E. Firmansyah, S. Tomioka, S. Abe, M. Shoyama, and T. Ninomiya, "A zero-current-switch quasi-resonant boost converter with transformer compensated clamp circuit," in *Proc. 13th Eur. Conf. Power Electron.* Appl. (EPE), Sep. 2009, pp. 1–8.

**FABIO PARESCHI** (S'05–M'08) received the Dr.Eng. degree (Hons.) in electronic engineering from the University of Ferrara, Italy, in 2001, and the Ph.D. degree in information technology from the University of Bologna, Italy, in 2007, under the European Doctorate Project (EDITH). He is currently an Assistant Professor with the Department of Electronic and Telecommunication, Politecnico di Torino. He is also a Faculty Member of ARCES, University of Bologna. His research

activity focuses on analog and mixed-mode electronic circuit design, statistical signal processing, compressed sensing, random number generation and testing, and electromagnetic compatibility. He has received the Best Paper Award from ECCTD 2005 and the Best Student Paper Award from EMC Zurich 2005. He was a recipient of the 2019 IEEE BioCAS Transactions Best Paper Award. He has served as an Associate Editor for the IEEE Transactions on Circuits and Systems Part II, from 2010 to 2013.

**NICOLA BERTONI** received the B.S. degree (cum laude) in information technology and the M.S. degree (magna cum laude) in electronic engineering and telecommunications from the University of Ferrara, Ferrara, Italy, in 2010 and 2013, respectively, and the Ph.D. degree in electronic engineering with ENDIF, University of Ferrara, in 2017. In 2015, he was a Visiting Scholar of the Italian Young Researchers Program with the Institute for Systems Research, University of Maryland, for

4 months. In 2017, he joined the Texas Instruments Design Center, Milan, where he is currently involved in high-frequency switching converters, advanced ZVS topology, and low-power dc-dc point of loads.

**MAURO MANGIA** (S'09–M'13) received the B.Sc. and M.Sc. degrees in electronic engineering and the Ph.D. degree in information technology from the University of Bologna, Bologna, Italy, in 2005, 2009, and 2013, respectively. He was a Visiting Ph.D. Student with the Ecole Polytechnique Federale de Lausanne, in 2009 and 2012. He is currently a Postdoctoral Researcher with ARCES, Statistical Signal Processing Group, University of Bologna. His research interests

include nonlinear systems, compressed sensing, the Internet of Things, ultra-wideband systems, and systems biology. He was a recipient of the 2013 IEEE CAS Society Guillemin-Cauer Award and the 2019 IEEE Bio-CAS Transactions Best Paper Award. He has received the Best Student Paper Award from ISCAS 2011. He was the Web and Social Media Chair of ISCAS 2018.

RICCARDO ROVATTI (M'99–SM'02–F'12) received the M.S. degree in electronic engineering and the Ph.D. degree in electronics, computer science, and telecommunications from the University of Bologna, Italy, in 1992 and 1996, respectively. He is currently a Full Professor of electronics with the University of Bologna. He has authored approximately 300 technical contributions to international conferences and journals and two volumes. His research interests include mathematical

and applicative aspects of statistical signal processing, and the applications of statistics to nonlinear dynamical systems. He was a recipient of the 2004 IEEE CAS Society Darlington Award, the 2013 IEEE CAS Society Guillemin-Cauer Award, and the 2019 IEEE BioCAS Transactions Best Paper Award. He has received the Best Paper Award from ECCTD 2005 and the Best Student Paper Award from EMC Zurich 2005 and ISCAS 2011. He has contributed to nonlinear and statistical signal processing applied to electronic systems.

**GIANLUCA SETTI** (S'89–M'91–SM'02–F'06) received the Ph.D. degree in electronic engineering and computer science from the University of Bologna, in 1997. From 1997 to 2017, he has been with the School of Engineering, University of Ferrara, Italy. Since 2017, he has been a Full Professor of analog electronics with the Politecnico di Torino, Italy. He is also a permanent Faculty Member of ARCES, University of Bologna. His research interests include nonlinear circuits,