Doctoral Dissertation Doctoral Program in Electrical, Electronics and Communication Engineering (31.st cycle)

# Motor Overvoltage and Power Losses Analysis in Industrial AC Drives Based on Si and SiC Devices

Riccardo Ruffo

Supervisors

Prof. Paolo Guglielmi Prof. Eric Giacomo Armando

## **Doctoral Examination Committee:**

Prof. Giacomo Scelba, Università degli Studi di Catania Prof. Luca Solero, Università degli Studi Roma Tre Prof. Keiji Wada, Tokyo Metropolitan University Prof. Toshihisa Shimizu, Tokyo Metropolitan University Prof. Bojoi Iustin Radu, Politecnico di Torino

> Politecnico di Torino July 1, 2019

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

.....

Riccardo Ruffo Turin, July 1, 2019

# Summary

In recent years, SiC based switches have become an attractive solution in the field of high-speed motors for replacing traditional Si based switches, mostly because of their higher switching frequency capability. The adoption of SiC devices in three-phase inverters has a series of advantages and drawbacks. The advantages include higher converter efficiency and the possibility to increase the switching frequency, which results in the reduction of heat sink size and inductive elements. The insulation stress on the electric machine due to the overvoltages caused by high dv/dt and long cables are the main drawbacks of the drive when SiC devices are used.

The research activity was sponsored by Fidia S.p.A, which is active in the realization of machine tools. The aim of the company was to realize an industrial inverter based on SiC devices controlled by an FPGA. A new converter was designed, built and tested. This converter offers the possibility to perform fair comparisons between different switch configurations: all-Si, Si-SiC and all-SiC. The comparison reveals remarkable losses reduction in all-SiC configuration however, serious problems at the motor terminals were found even with few meters of connecting cable.

In order to solve this problem, a detailed study of the drive was conducted and a more accurate model of the cable was derived. Using this model, formulae used for RL filter design were derived and a filter was designed, build and tested. A new issue emerged from the experimental results when RL filter was used in combination with all-SiC. An unpredicted additional motor overvoltage was detected which was due to the combination of the filter resistor parasitic inductance and the high dv/dt. The design formulae were readapted and then experimentally were validated. Finally, a circuital solution for the compensation of the resistor parasitic inductance issue was proposed.

To the memory of my father, Renato, who always believed in me.

# Acknowledgements

I would especially like to thank my mother and my loved future wife Chiara for the support and love given me in the difficult moments faced during my PhD. This accomplishment would not have been possible without them.

Special acknowledges are deserved for my supervisors, Professor Paolo Guglielmi for giving me the opportunity to get involved in this beautiful but intense experience and to Professor Eric Armando for the invaluable technical experience given in these years.

I would like to express my gratitude to FIDIA SpA, and in particular to Manlio Barolo and Marco Di Sciuva, for the significant support given during my research activity.

I would like to thank Professor Toshihisa Shimizu for giving me the opportunity to do a research period abroad at Tokyo Metropolitan University and for the invaluable technical advice that he had provided to me. I would like to express my most sincere gratitude to all the laboratory members that during the period abroad they made me feel at home.

I would like to acknowledge also the members of the jury of this dissertation for their contribution in the improvement of the manuscript.

During my journey, I had the opportunity to work with the colleagues of the group that we usually call "Wireless Power Transfer Group". I would like to thanks: Alessandro La Ganga, Michela Diana, Jacopo Colussi, Mojtaba Khalilian and Vincenzo Cirimele who are not only colleagues but also friends.

Last but not least, I would especially like to thank the colleagues and friends Fausto Stella, Paolo Pescetto, Simone Ferrari and Sandro Rubino who shared this PhD adventure with me.

# Contents

| Li | st of              | Tables                                            | XII           |  |

|----|--------------------|---------------------------------------------------|---------------|--|

| Li | List of Figures XI |                                                   |               |  |

| 1  | <b>Intr</b><br>1.1 | Poduction<br>Personal contribution                | $\frac{1}{3}$ |  |

|    | 1.2                | Thesis content                                    | 3             |  |

| 2  | Pow                | ver converter                                     | 5             |  |

|    | 2.1                | Introduction                                      | 5             |  |

|    | 2.2                | Standard power converters                         | 5             |  |

|    |                    | 2.2.1 XPOWER converters                           | 6             |  |

|    |                    | 2.2.2 Control board                               | 6             |  |

|    |                    | 2.2.3 Power boards                                | 8             |  |

|    | 2.3                | New converter: XP100-75-D                         | 11            |  |

|    |                    | 2.3.1 Hardware specification                      | 12            |  |

|    |                    | 2.3.2 Firmware specification                      | 12            |  |

|    | 2.4                | Conclusions                                       | 15            |  |

| 3  | Con                | verter design, realization, and preliminary tests | 17            |  |

|    | 3.1                | Introduction                                      | 17            |  |

|    | 3.2                | Dimensioning of the FPGA                          | 17            |  |

|    |                    | 3.2.1 Firmware                                    | 18            |  |

|    |                    | 3.2.2 FPGA choice                                 | 19            |  |

|    | 3.3                | Thermal sizing of the converter                   | 20            |  |

|    |                    | 3.3.1 Converter thermal design methodology        | 20            |  |

|    |                    | 3.3.2 Converter thermal sizing                    | 23            |  |

|    |                    | 3.3.3 Heat sink choice                            | 28            |  |

|    | 3.4                | IPM operational circuit                           | 31            |  |

|    |                    | 3.4.1 IPM power supply                            | 32            |  |

|    |                    | 3.4.2 IPM control signals                         | 33            |  |

|    | 3.5                | Converter capacitors                              | 34            |  |

|    |                    |                                                   |               |  |

|   | 3.6  | Measurement circuits                                                              |

|---|------|-----------------------------------------------------------------------------------|

|   |      | 3.6.1 Current measurement circuit                                                 |

|   |      | 3.6.2 Voltage measurement circuit                                                 |

|   |      | 3.6.3 Temperature measurement circuit                                             |

|   | 3.7  | PCB design                                                                        |

|   |      | 3.7.1 Components placement                                                        |

|   |      | 3.7.2 Wire routing issues                                                         |

|   | 3.8  | PCB and initial tests                                                             |

|   |      | 3.8.1 PCB                                                                         |

|   |      | 3.8.2 IPM fault when all-SiC is used                                              |

|   | 3.9  | Mounting process of the power converter                                           |

|   | 3.10 |                                                                                   |

|   | _    |                                                                                   |

| 4 |      | ses and thermal comparisons between all-Si, Si-SiC and all-SiC                    |

|   | devi |                                                                                   |

|   | 4.1  | Introduction                                                                      |

|   | 4.2  | Converter loss measurement methods                                                |

|   |      | 4.2.1 Double pulse test                                                           |

|   |      | $4.2.2  \text{Calorimetric method}  \dots  \dots  \dots  \dots  \dots  \dots  52$ |

|   |      | 4.2.3 Input and output power measurements                                         |

|   | 4.0  | $4.2.4 Opposition method \dots 53$                                                |

|   | 4.3  | AC losses measurement with opposition method                                      |

|   |      | 4.3.1 Measurement equivalent circuit                                              |

|   |      | 4.3.2 Opposition method methodology                                               |

|   |      | 4.3.3 Useful hints valid for the opposition method                                |

|   | 4.4  | The test bench                                                                    |

|   |      | 4.4.1 Post-process elaboration data                                               |

|   | 4.5  | Comparisons at the power converter nominal condition 62                           |

|   | 4.6  | Module AC power losses comparisons                                                |

|   |      | 4.6.1 Comparisons of conduction and switching losses                              |

|   |      | 4.6.2 Total power losses comparison                                               |

|   | 4.7  | Results summary                                                                   |

|   | 4.8  | Conclusions                                                                       |

| 5 | Driv | ve side effect comparisons between all-Si, Si-SiC and all-SiC                     |

| Ŭ | devi | - · · · · · · · · · · · · · · · · · · ·                                           |

|   | 5.1  | Introduction                                                                      |

|   | 5.2  | General background                                                                |

|   |      | 5.2.1 AC drive structure                                                          |

|   |      | 5.2.2 AC drive issues caused by high $dv/dt$                                      |

|   |      | 5.2.3 Motor issues caused by high $dv/dt$                                         |

|   |      | 5.2.4 EMI                                                                         |

|   |      |                                                                                   |

| all-Si, Si-SiC and all-SiC devices         5.3.1       Experimental setup                                 |

|-----------------------------------------------------------------------------------------------------------|

| 1 1                                                                                                       |

|                                                                                                           |

| 5.3.2 Inverter issues comparison                                                                          |

| 5.3.3 Motor issues comparison                                                                             |

| 5.3.4 EMI issues comparison $\ldots$                                                                      |

| Conclusions                                                                                               |

| tric Drive Modelling                                                                                      |

| Introduction                                                                                              |

| Two-conductor line                                                                                        |

| 6.2.1 Solution to transmission line equations                                                             |

| 6.2.2 Boundary conditions                                                                                 |

| Load overvoltage and generator overcurrent                                                                |

| 6.3.1 Cable connected to an open circuit                                                                  |

| 6.3.2 Impedance load major than cable surge impedance $\ldots$ .                                          |

| 6.3.3 Load overvoltage vs. generator voltage rise time                                                    |

| Multiconductor transmission line                                                                          |

| 6.4.1 Solution to transmission line equations                                                             |

| 6.4.2 Boundary condition                                                                                  |

| Electric drive model                                                                                      |

| $6.5.1  \text{AC/DC converter}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $          |

| 6.5.2 Three-phase inverter                                                                                |

| 6.5.3 Power cable                                                                                         |

| 6.5.4 Three-phase AC motor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |

| Motor overvoltage                                                                                         |

| 6.6.1 Formulation hypotheses and equivalent drive model                                                   |

| 6.6.2 Mathematical formulae                                                                               |

| 6.6.3 Differential mode propagation speed major than the common                                           |

| mode one                                                                                                  |

| 6.6.4 Common mode propagation speed major than the differential                                           |

| one                                                                                                       |

| 6.6.5 Differential mode propagation speed equal to the common                                             |

| mode one                                                                                                  |

| Conclusions                                                                                               |

|                                                                                                           |

|   |               | 7.3.1    | Experimental data and their processing                      | 141 |

|---|---------------|----------|-------------------------------------------------------------|-----|

|   |               | 7.3.2    | Power cable parameters identification                       | 143 |

|   |               | 7.3.3    | Motor parameters identification                             | 144 |

|   | 7.4           | Motor    | overvoltage simulation                                      | 145 |

|   |               | 7.4.1    | The experimental setup                                      | 145 |

|   |               | 7.4.2    | Drive parameters identification                             | 146 |

|   |               | 7.4.3    | Simulation issues                                           | 149 |

|   |               | 7.4.4    | New proposed model of transmission line                     | 149 |

|   |               | 7.4.5    | Simulations vs. experimental results                        | 151 |

|   | 7.5           | Conch    | usions                                                      | 154 |

| 8 | $\mathbf{RL}$ | filter f | for motor overvoltage mitigation                            | 155 |

|   | 8.1           |          | luction                                                     | 155 |

|   | 8.2           | Filters  | s for motor overvoltage mitigation                          | 156 |

|   |               | 8.2.1    | dv/dt filters                                               | 156 |

|   |               | 8.2.2    | Impedance matching filters                                  | 158 |

|   |               | 8.2.3    | Active filters                                              | 160 |

|   |               | 8.2.4    | Special filters for specific applications                   | 160 |

|   | 8.3           | Design   | n of RL filter                                              | 161 |

|   |               | 8.3.1    | RL filter formulae                                          | 161 |

|   |               | 8.3.2    | Simulations and design guideline                            | 163 |

|   | 8.4           | RL fil   | ter performance comparison when all-Si, Si-SiC and all-SiC  |     |

|   |               | device   | s are used                                                  | 164 |

|   |               | 8.4.1    | Laboratory test bench                                       | 164 |

|   |               | 8.4.2    | RL filter design                                            | 165 |

|   |               | 8.4.3    | Experimental comparison and filter issue                    | 166 |

|   | 8.5           | Origin   | n of the issue                                              | 169 |

|   |               | 8.5.1    | Electric drive modeling                                     | 169 |

|   |               | 8.5.2    | Resistor parasitic inductance effect                        | 170 |

|   |               | 8.5.3    | Resistor parasitic inductance vs. inverter $dv/dt$          | 174 |

|   |               | 8.5.4    | Important points                                            | 175 |

|   | 8.6           | New F    | RL filter design formulae                                   | 176 |

|   |               | 8.6.1    | Formulation hypotheses                                      | 176 |

|   |               | 8.6.2    | Low and high frequencies RL filter models                   | 177 |

|   |               | 8.6.3    | Load voltage peak formula caused by the second propagation  | 179 |

|   |               | 8.6.4    | Load voltage peak formula caused by the third propagation . | 182 |

|   |               | 8.6.5    | Formulae validation                                         | 184 |

|   |               | 8.6.6    | Filter design formulae                                      | 185 |

|   |               | 8.6.7    | The design guideline                                        | 186 |

|   | 8.7           | The e    | xperimental validation                                      | 187 |

|   |               | 8.7.1    | Formulae validation                                         | 187 |

|   |               | 8.7.2    | Second and third load reflected waveforms                   | 188 |

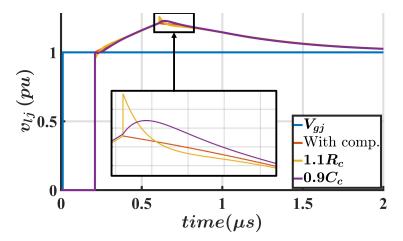

| 8.8    | RC/RL filter                          | 195 |  |

|--------|---------------------------------------|-----|--|

|        | 8.8.1 Theoretical analysis            | 196 |  |

|        | 8.8.2 RC/RL filter PSpice simulations |     |  |

|        | 8.8.3 Parameter sensitivity analysis  | 198 |  |

|        | 8.8.4 Compensation method evaluation  | 202 |  |

| 8.9    | Conclusions                           | 202 |  |

| 9 Co   | nclusions and future developments     | 205 |  |

| 9.1    | Conclusions                           | 205 |  |

| 9.2    | Final remarks                         | 207 |  |

|        | 9.2.1 all-Si vs. Si-SiC               | 207 |  |

|        | 9.2.2 all-Si vs. all-SiC              | 207 |  |

| 9.3    | Future developments                   | 208 |  |

| Publis | Published papers                      |     |  |

| Biblio | Bibliography 2                        |     |  |

# List of Tables

| 2.1 | XP100-75-A and XP50-30-D power converters technical data. Switch-<br>ing frequency <sup>1</sup> represents the maximum limit imposed by the heat<br>sink. Switching frequency <sup>2</sup> represents the maximum limit imposed |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | by digital control.                                                                                                                                                                                                             | 10  |

| 2.2 | New converter specifications. Switching frequency <sup>1</sup> represents the maximum limit imposed by the heat sink. Switching frequency <sup>2</sup>                                                                          |     |

|     | represents the maximum limit imposed by digital control                                                                                                                                                                         | 12  |

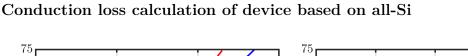

| 3.1 | Piecewise voltage drop of the switches present inside the PM75CL1A120                                                                                                                                                           |     |

|     | power module                                                                                                                                                                                                                    | 25  |

| 3.2 | Calculated conduction losses of Si IGBT and Si diode ( $M = 0.9$ ,                                                                                                                                                              |     |

|     | $cos\varphi = 0.9$ )                                                                                                                                                                                                            | 25  |

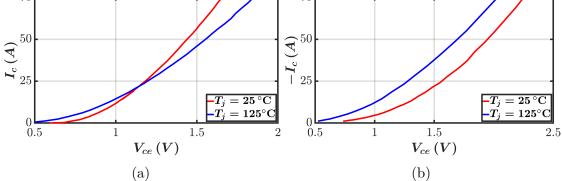

| 3.3 | Switching losses $(V_{dc} = 600 \text{ V}, f_{sw} = 8 \text{ kHz})$ .                                                                                                                                                           | 26  |

| 3.4 | Conduction, switching and total losses $(V_{dc} = 600 \text{ V}, M = 0.9,$                                                                                                                                                      |     |

|     | $\cos\varphi = 0.9$ and $f_{sw} = 8$ kHz).                                                                                                                                                                                      | 26  |

| 3.5 | Thermal resistances presented by all-Si power module (PM75CL1A120).                                                                                                                                                             | 30  |

| 3.6 | PCB layer stack-up.                                                                                                                                                                                                             | 39  |

| 4.1 | Power converter efficiencies at the nominal condition (30 A, 600 V                                                                                                                                                              |     |

|     | and 7.8 kHz).                                                                                                                                                                                                                   | 65  |

| 4.2 | Switching losses of all-Si, Si-SiC and all-SiC power modules.                                                                                                                                                                   | 71  |

| 5.1 | Inverter parameters vs. Insulation life.                                                                                                                                                                                        | 80  |

| 5.2 | Critical length vs. inverter rise times based on all-Si, Si-SiC and                                                                                                                                                             |     |

|     | all-SiC devices.                                                                                                                                                                                                                | 85  |

| 6.1 |                                                                                                                                                                                                                                 | 121 |

| 6.2 |                                                                                                                                                                                                                                 | 121 |

| 6.3 | Maximum phase-to-frame motor voltage: velocity of propagation                                                                                                                                                                   |     |

| 0.0 | presented by $\alpha$ and $\beta$ components is major than the velocity of prop-                                                                                                                                                |     |

|     |                                                                                                                                                                                                                                 | 126 |

| 6.4 | Maximum phase-to-phase motor voltage: velocity of propagation                                                                                                                                                                   | 120 |

| 0.4 | presented by $\alpha$ and $\beta$ components major than the velocity of prop-                                                                                                                                                   |     |

|     |                                                                                                                                                                                                                                 | 128 |

|     | agation of the 0 component $(U_{\alpha} > U_0)$                                                                                                                                                                                 | 120 |

| 6.5 | Maximum phase-to-frame motor voltage: velocity of propagation   |     |

|-----|-----------------------------------------------------------------|-----|

|     | presented by 0 component major than the velocity of propagation |     |

|     | of the $\alpha$ and $\beta$ components $(U_0 > U_\alpha)$       | 129 |

- 7.2 Motor parameters derived by using the least squares method. . . . 148

- 8.2 Peak line-to-line motor voltage  $(V_{ph,ph})$  comparison by changing the switch configuration when RL filter is used  $(R=23 \Omega, L=21 uH)$ . 168

# List of Figures

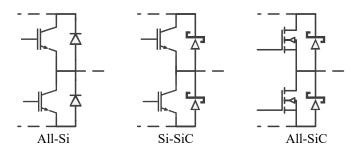

| 1.1  | Switch configurations using devices based on Si and SiC materials.   | 2  |

|------|----------------------------------------------------------------------|----|

| 2.1  | Cabinet of a computer numerical control (GTF)                        | 6  |

| 2.2  | A XPOWER converter: XP50-30-D with connected an FDIB4 con-           |    |

|      | trol board.                                                          | 7  |

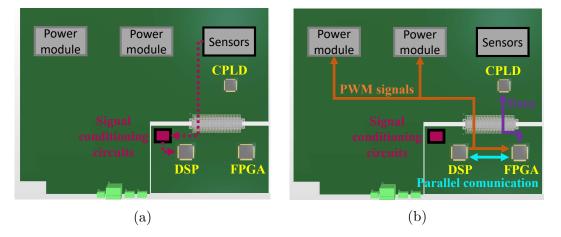

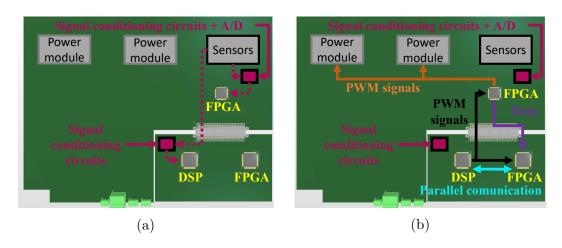

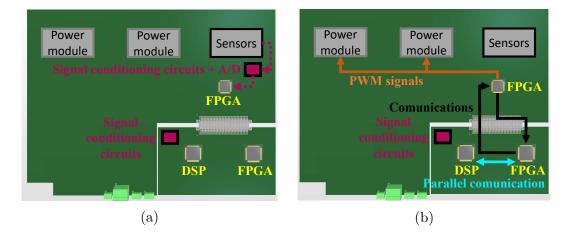

| 2.3  | Schematic converter operation of XPOWER converter family. (a)        |    |

|      | Measurement conditioning circuit, (b) PWM and communications         |    |

|      | signals                                                              | 7  |

| 2.4  | Control board: FDIB4                                                 | 8  |

| 2.5  | XPOWER converter model XP100-75-A.                                   | 9  |

| 2.6  |                                                                      | 10 |

| 2.7  | XPOWER converter model XP50-30-D.                                    | 11 |

| 2.8  | Schematic presentation of the control done by FIDIA to the new       |    |

|      | prototype                                                            | 13 |

| 2.9  | Schematic novel converter operation controlled in the standard way   |    |

|      | (a) Measurement conditioning circuit, (b) PWM and communication      |    |

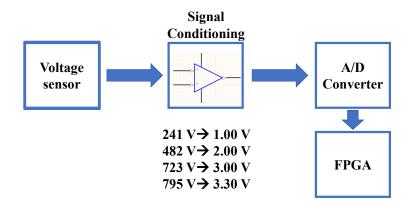

|      | signals                                                              | 14 |

| 2.10 |                                                                      |    |

|      | trol scheme shown in Fig. 2.8. (a) Measurement conditioning circuit, |    |

|      | (b) PWM and communications signals.                                  | 14 |

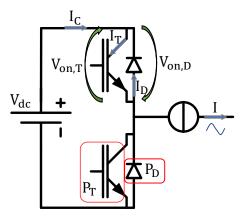

| 3.1  | Inverter leg based on all-Si configuration device.                   | 21 |

| 3.2  |                                                                      | 24 |

| 3.3  | ON voltage drops of the devices present inside the power module      |    |

|      | PM75CL1A120, where $T_i$ are the device junction temperatures. (a)   |    |

|      |                                                                      | 24 |

| 3.4  | Switching losses of the devices present inside the power module      |    |

|      | PM75CL1A120, where $T_i$ is the device junction temperature. (a)     |    |

|      |                                                                      | 26 |

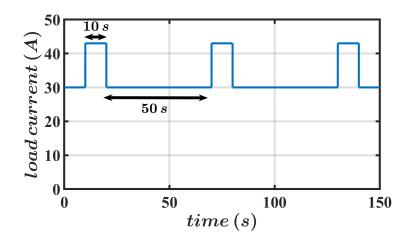

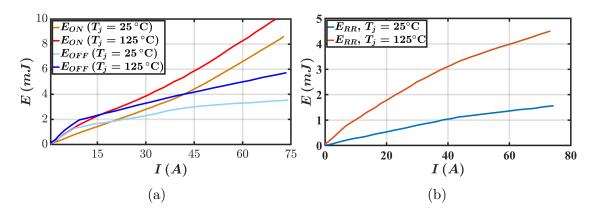

| 3.5  | Heat dissipated by two inverters when the load current profile is    |    |

|      |                                                                      | 27 |

| 3.6  | Equivalent thermal circuit of the converter. In the dashed rectangle |    |

|      | region, the components of each inverter are presented                | 28 |

|      |                                                                      |    |

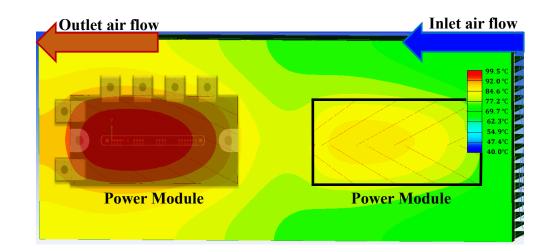

| 3.7  | Thermal simulation results: heat sink bottom view of the tempera-      |

|------|------------------------------------------------------------------------|

|      | ture profile when the peak temperature is reached                      |

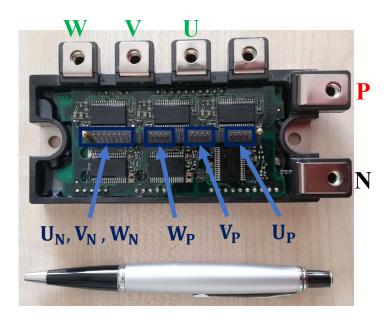

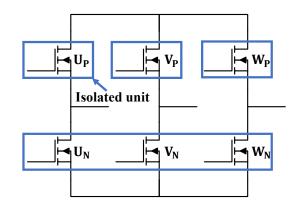

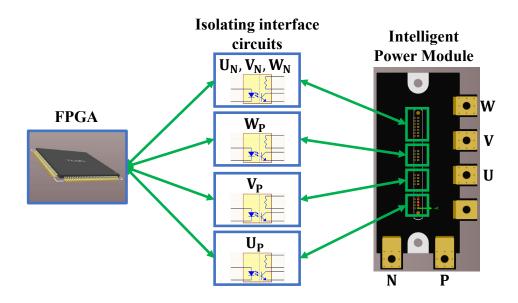

| 3.8  | Isolated units of the intelligent power module                         |

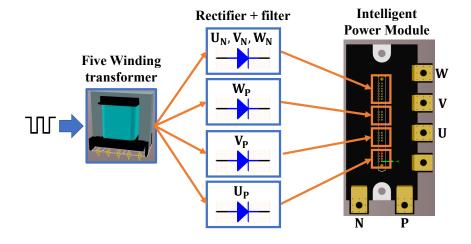

| 3.9  | Equivalent scheme of isolated power supplies used for the IPM          |

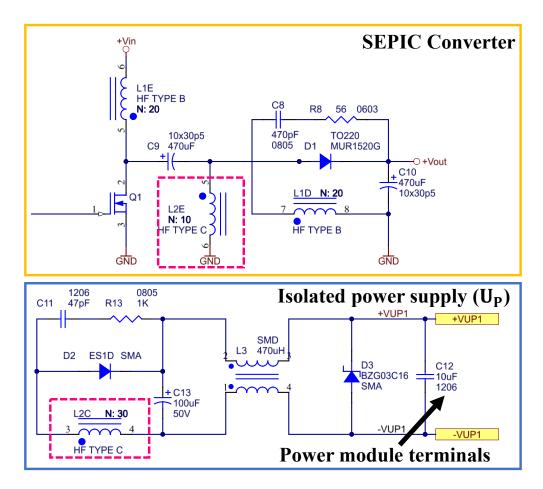

| 3.10 | Schematic representation of the SEPIC circuit used for the isolated    |

|      | power supplies of the power modules                                    |

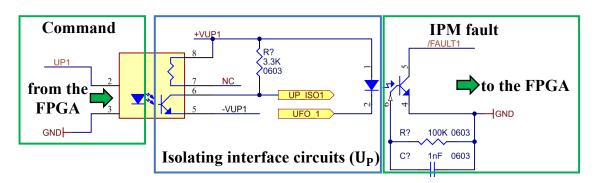

| 3.11 | Equivalent scheme of isolated control and fault circuits used for the  |

|      | IPM                                                                    |

| 3.12 | Schematic representation of the isolating interface circuit used for   |

|      | control purpose.                                                       |

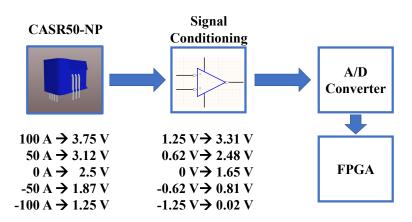

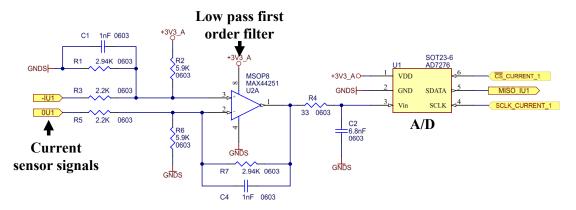

| 3.13 | Equivalent scheme of the current acquisition circuit.                  |

|      | Schematic representation of the circuit used for acquisition of the    |

|      | inverter current.                                                      |

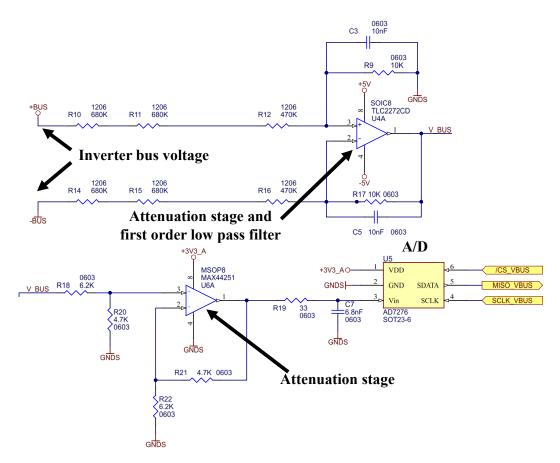

| 3.15 | Equivalent scheme of the voltage acquisition circuit                   |

| 3.16 | Schematic representation of the circuit used for acquisition of the    |

|      | bus voltage.                                                           |

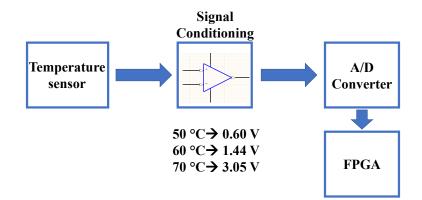

| 3.17 | Equivalent scheme of the temperature acquisition circuit.              |

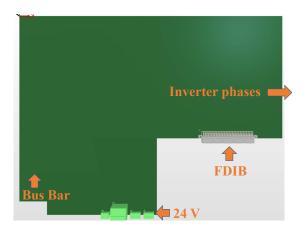

| 3.18 | Power converter: mechanical constraints of connections with the ex-    |

|      | ternal world                                                           |

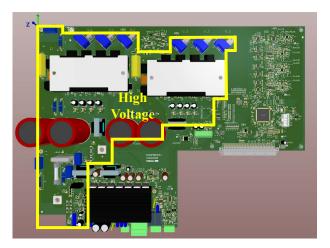

| 3.19 | High voltage room of the power converter is highlighted in yellow      |

|      | while the rest is considered low voltage circuit.                      |

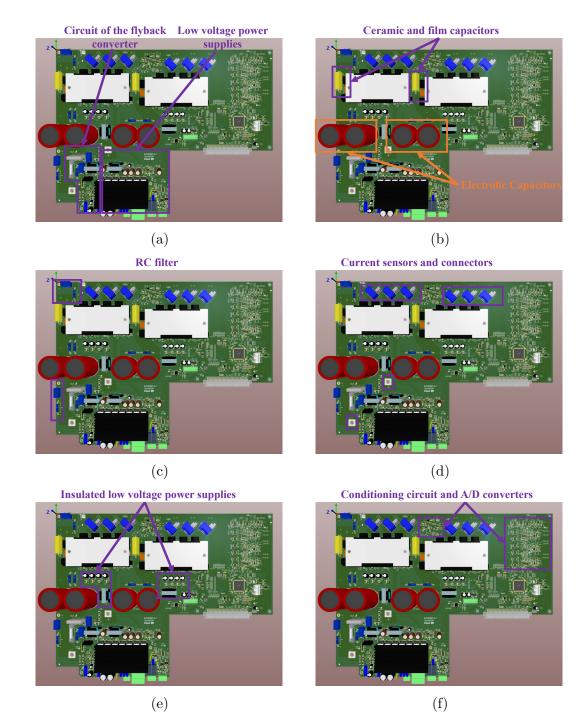

| 3.20 |                                                                        |

|      | supplies, (b) bus capacitors, (c) RC filters which connect the bus     |

|      | to the drive ground, (d) current sensors and connectors, (e) power     |

|      | module isolating power supplies and (f) sensor conditioning circuits   |

|      | are highlighted.                                                       |

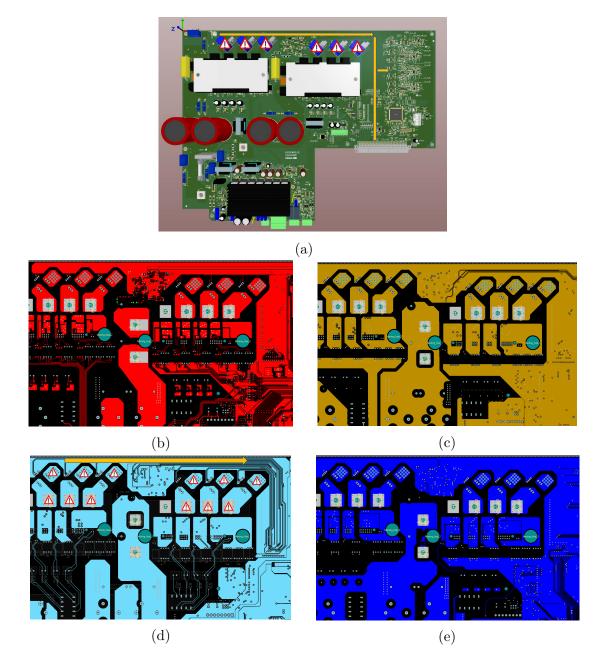

| 3.21 |                                                                        |

|      | inner layer 1, (d) inner layer 2 and (e) bottom layer                  |

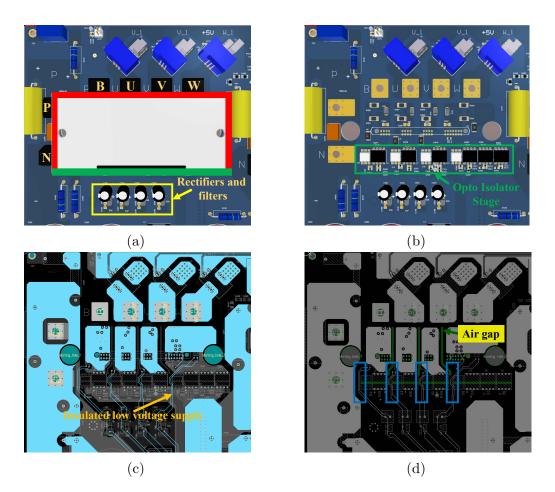

| 3.22 | IPM wire routing issue. (a) The rectifier and the filter of each power |

|      | supply are highlighted. (b) Components presented below the IPM         |

|      | power modules are highlighted. (c) Signal layer 2 and the insulated    |

|      | low voltage supply are highlighted. (d) The clearance holes are high-  |

|      | lighted                                                                |

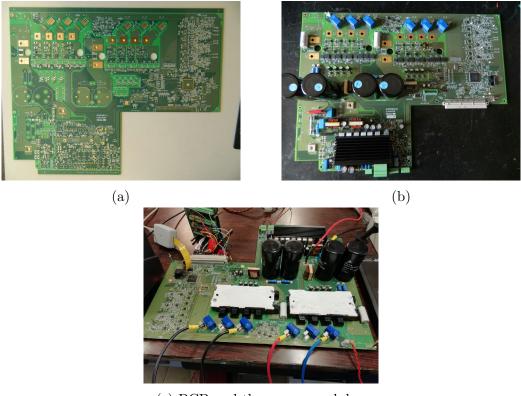

| 3.23 | Electronic components mounted on the PCB board                         |

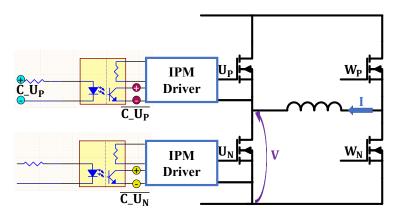

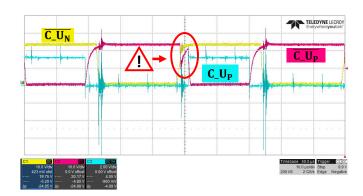

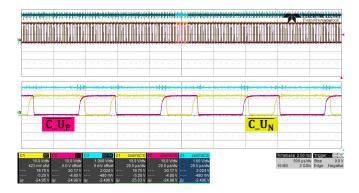

| 3.24 | IPM issue origin investigation: equivalent scheme of the experimen-    |

|      | tal setup where probes placement are highlighted.                      |

| 3.25 | Experiment results: voltages measured by the differential probes.      |

|      | Experiment results: voltages measured by fiber optically isolated      |

|      | probes                                                                 |

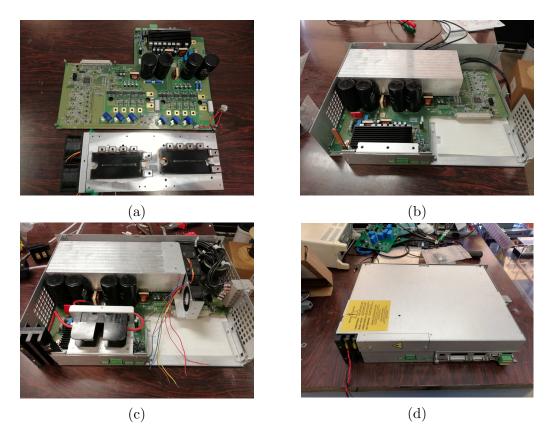

| 3.27 | Mounting process of the power converter: (a) PCB, power modules<br>and heat sink, (b) PCB, power modules and heat sink mounted inside<br>the mechanical box, (c) PCB, power modules, heat sink, fans and<br>common mode chokes mounted inside the mechanical box and (d) |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4 1  | final version of the power converter.                                                                                                                                                                                                                                    | 48 |

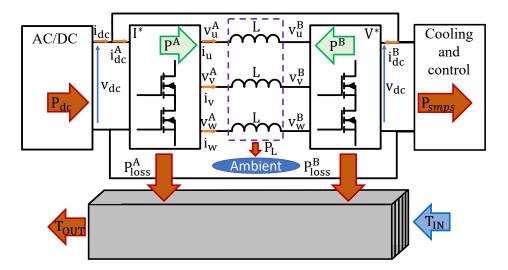

| 4.1  | Equivalent scheme of the opposition method applied to the designed power converter.                                                                                                                                                                                      | 54 |

| 4.2  | Opposition method phasor diagrams following the convention of the equivalent scheme shown in Fig. 4.1. (a) Case with a generic power factor. (b) Case with power factor imposed equal to "0" with high-                                                                  | •  |

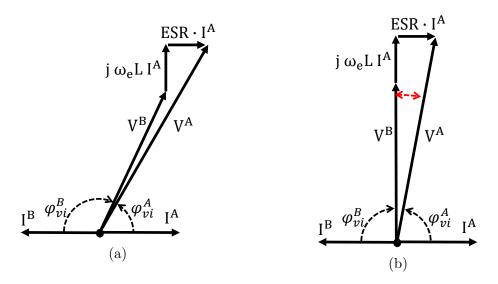

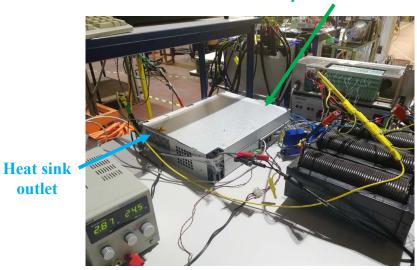

| 4.3  | lighted in red the phase error introduced by the ESR of the inductor.<br>Experimental setup composed of the measurement system, the power                                                                                                                                | 58 |

| 4.4  | converter, and the inductors                                                                                                                                                                                                                                             | 60 |

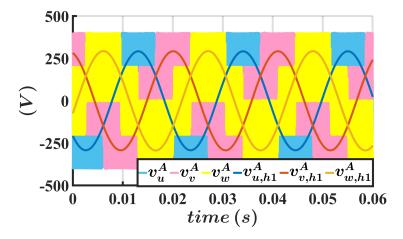

| 4.5  | surement points                                                                                                                                                                                                                                                          | 61 |

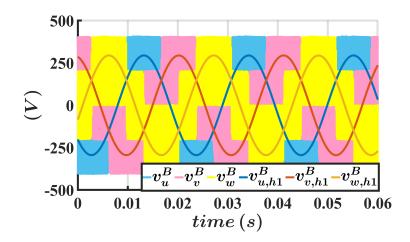

| 4.6  | 7.8 kHz). Inverter A: phase-to-neutral voltages and their first har-<br>monics                                                                                                                                                                                           | 62 |

| 4.0  | The periment results using an SIC ( $v_{dc} = 000$ v, $T = 50$ Å, $f_{sw} = 7.8$ kHz). Inverter B: phase-to-neutral voltages and their first harmonics.                                                                                                                  | 63 |

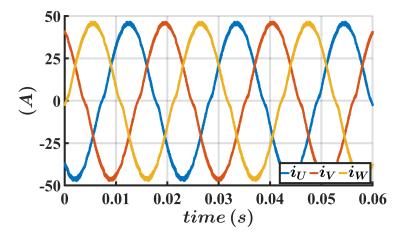

| 4.7  | Experiment results using all-SiC ( $V_{dc} = 600 \text{ V}$ , $I = 30 \text{ A}$ , $f_{sw} = 7.8 \text{ kHz}$ ). Inverter line currents.                                                                                                                                 | 63 |

| 4.8  | Experiment results using all-SiC ( $V_{dc} = 600 \text{ V}$ , $I = 30 \text{ A}$ , $f_{sw} = 7.8 \text{ kHz}$ ). Electrical variables of the phase "U".                                                                                                                  | 64 |

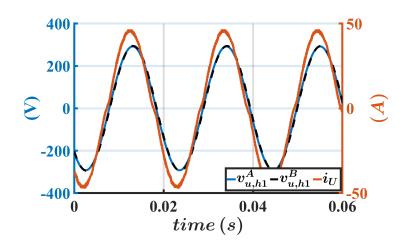

| 4.9  | Experimental results: thermal step response to the inverter power rating ( $V_{dc} = 600 \text{ V}$ , $I = 30 \text{ A}$ , $f_{sw} = 7.8 \text{ kHz}$ ). (a) Power dissipated by the heat sink for each technology and (b) measured phase current                        |    |

|      | of the inverter.                                                                                                                                                                                                                                                         | 65 |

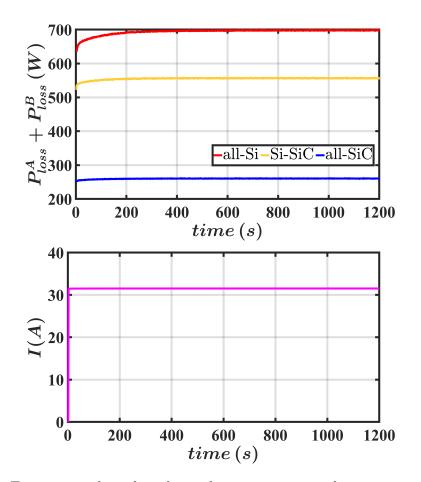

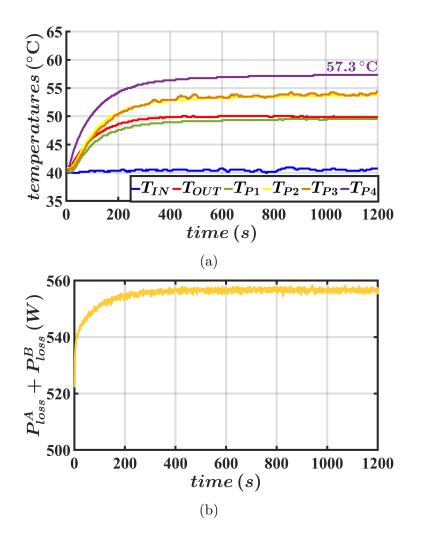

| 4.10 | Experimental results: thermal step response to the inverter power rating ( $V_{dc} = 600 \text{ V}$ , $I = 30 \text{ A}$ , $f_{sw} = 7.8 \text{ kHz}$ ). (a) Temperatures of the heat sink using all-Si device. (b) Power dissipated by the heat                         |    |

|      | sink for each technology.                                                                                                                                                                                                                                                | 66 |

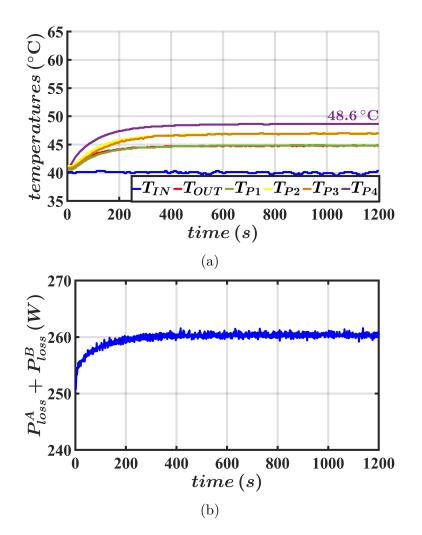

| 4.11 | Experimental results: thermal step response to the inverter power rating ( $V_{dc} = 600 \text{ V}$ , $I = 30 \text{ A}$ , $f_{sw} = 7.8 \text{ kHz}$ ). (a) Temperatures of the heat sink using Si-SiC device. (b) Power dissipated by the heat                         |    |

| 4.12 | sink for each technology                                                                                                                                                                                                                                                 | 67 |

|      | rating $(V_{dc} = 600 \text{ V}, I = 30 \text{ A}, f_{sw} = 7.8 \text{ kHz})$ . (a) Temperatures of the heat sink using all-SiC device. (b) Power dissipated by the heat sink for each technology.                                                                       | 68 |

|      |                                                                                                                                                                                                                                                                          | -  |

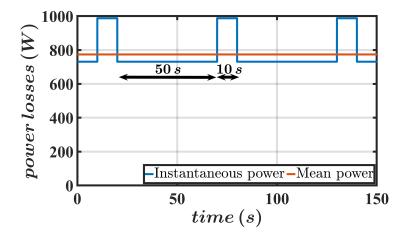

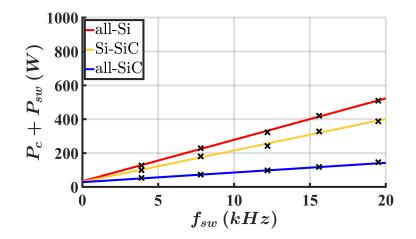

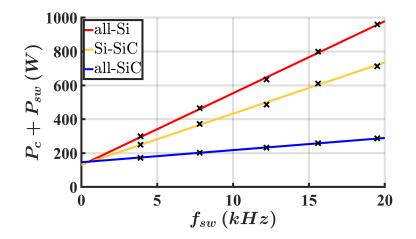

| 4.13 Experiment results: power module losses in function of the frequency                                                                                                                                                           |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

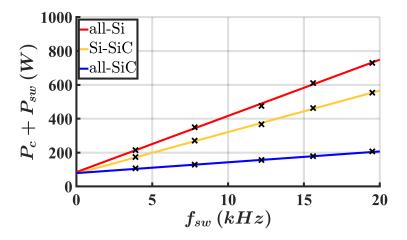

| fixing the current value ( $V_{dc} = 600 \text{ V}$ , $cos\varphi = 0$ , $M = 0.5$ , $I = 20 \text{ A}$ )<br>4.14 Experiment results: power module losses in function of the frequency                                              | 69        |

| fixing the current value ( $V_{dc} = 600$ V, $cos\varphi = 0$ , $M = 0.5$ , $I = 30$ A)                                                                                                                                             | 69        |

| 4.15 Experiment results: power module losses in function of the frequency fixing the current value ( $V_{dc} = 600 \text{ V}, \cos\varphi = 0, M = 0.5, I = 40 \text{ A}$ )                                                         | 70        |

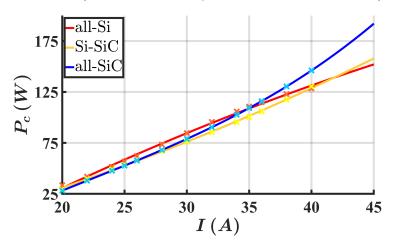

| 4.16 Mathematical elaboration: power module conduction losses as a                                                                                                                                                                  | 10        |

| function of the inverter current $(\cos\varphi = 0, M = 0.5)$                                                                                                                                                                       | 70        |

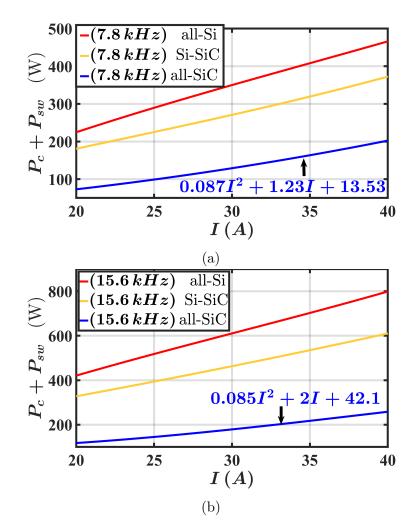

| 4.17 Experiment results: power module losses in function of the current $(V_{dc} = 600 \text{ V}, \cos\varphi = 0, M = 0.5)$ . (a) 7.8 kHz and (b) 15.6 kHz.                                                                        | 72        |

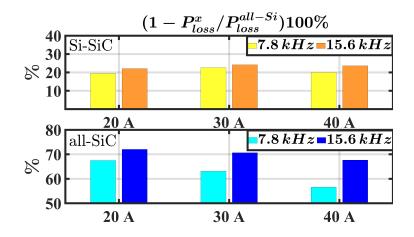

| 4.18 Per unit loss reductions using Si-SiC and all-SiC instead all-Si at                                                                                                                                                            |           |

| different load conditions ( $V_{dc} = 600 \text{ V}, \cos\varphi = 0, M = 0.5$ )                                                                                                                                                    | 73<br>76  |

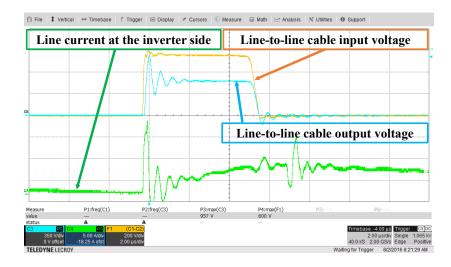

| <ul> <li>5.1 Schematic representation of a typical electric drive.</li> <li>5.2 Experimental results: inverter overcurrent and motor overvoltage of<br/>an industrial drive (with a nominal power of 20 kW) connected by</li> </ul> | 76        |

| $12.25 \mathrm{m}$ of power cable (AWG 8)                                                                                                                                                                                           | 77        |

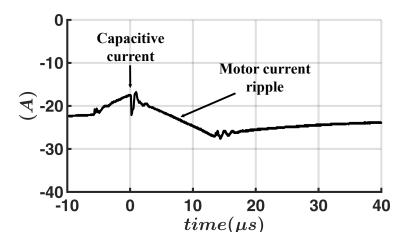

| 5.3 Experimental results: inverter capacitive current caused by the par-<br>asitic capacitance of the motor (with a nominal power of 20 kW).                                                                                        | 78        |

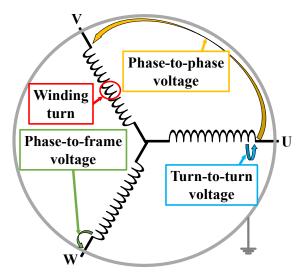

| 5.4 Schematic representation of all the overvoltages that can be present                                                                                                                                                            |           |

| in electrical motors.                                                                                                                                                                                                               | 79        |

| 5.5 Experimental results: motor voltage distribution when high $dv/dt$ inverter is connected to the motor (with a nominal power of 20 kW).                                                                                          | 81        |

| 5.6 Experiment results: (a) Scheme of the experimental setup, (b) com-<br>mon mode currents present in the drive (with a nominal power of                                                                                           |           |

| 20 kW).                                                                                                                                                                                                                             | 82        |

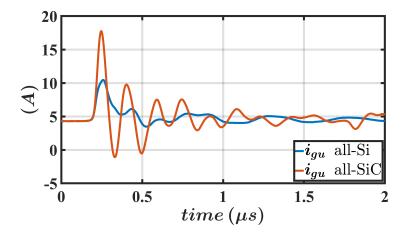

| <ul><li>5.7 Schematic representation of the experimental setup.</li><li>5.8 Experimental results: inverter and motor connected by 2 m of cable.</li></ul>                                                                           | 84        |

| Inverter phase current $(i_{qu})$ when all-Si and all-SiC devices are used.                                                                                                                                                         | 85        |

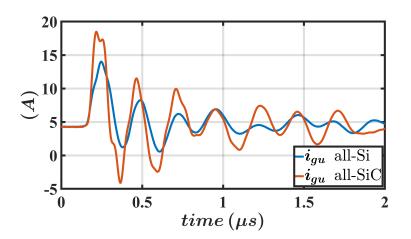

| 5.9 Experimental results: inverter and motor connected by 5 m of cable.                                                                                                                                                             | 00        |

| Inverter phase current $(i_{gu})$ when all-Si and all-SiC devices are used.                                                                                                                                                         | 86        |

| 5.10 Experiment results: inverter and motor connected by $2 \text{ m}$ of cable.                                                                                                                                                    |           |

| (a) Inverter and motor line-to-line voltages when all-Si is used. (b)                                                                                                                                                               | 07        |

| Inverter and motor line-to-line voltages when all-SiC is used 5.11 Experiment results: inverter and motor connected by 5 m of cable.                                                                                                | 87        |

| a) Inverter and motor line-to-line voltages when all-Si is used. b)                                                                                                                                                                 |           |

| Inverter and motor line-to-line voltages when all-SiC is used                                                                                                                                                                       | 88        |

| 5.12 Experiment results: inverter and motor connected by 2 m of cable.                                                                                                                                                              |           |

| Inverter common mode currents when all-Si and all-SiC devices are                                                                                                                                                                   |           |

| used                                                                                                                                                                                                                                | 89        |

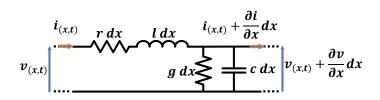

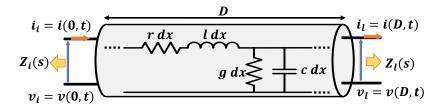

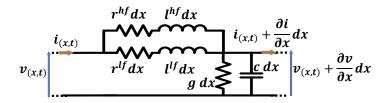

| 6.1 Schematic representation of an elementary component of transmis-<br>sion line.                                                                                                                                                  | 92        |

|                                                                                                                                                                                                                                     | $J\Delta$ |

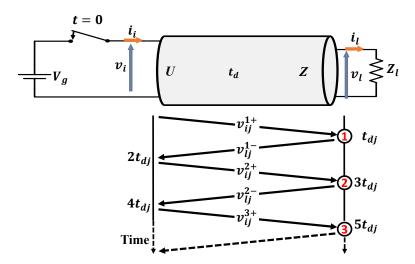

| 6.2  | Two-conductor transmission line: schematic details about the impedan<br>saw at the input and output cable terminations.                                                                                                  | ces<br>94 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 6.3  | Schematic representation of a transmission line connected to a volt-<br>age step generator with the corresponding Bewley lattice diagram.                                                                                | 95        |

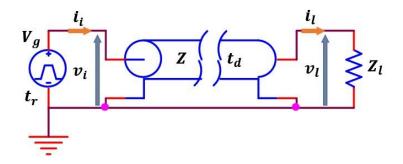

| 6.4  | PSpice schematic circuit.                                                                                                                                                                                                | 96        |

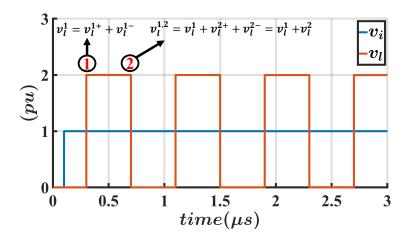

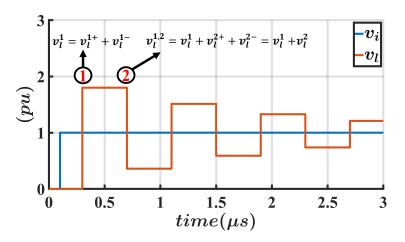

| 6.5  | Step response of a lossless line: input and output voltages ( $Z = 25 \Omega$ , $t_d = 200 \text{ ns}, Z_l = \infty$ and $\Gamma_l = 1$ ).                                                                               | 97        |

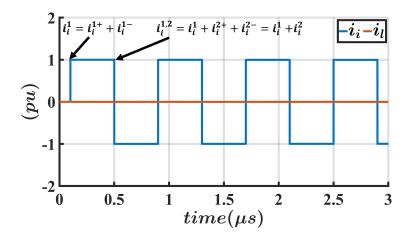

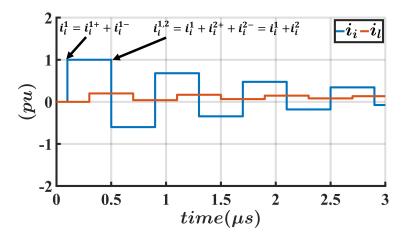

| 6.6  | Step response of a lossless line: input and output currents $(Z = 25 \Omega, t_d = 200 \text{ ns}, Z_l = \infty \text{ and } \Gamma_l = 1).$                                                                             | 97        |

| 6.7  | Step response of a lossless line: input and output voltages ( $Z = 25 \Omega$ , $t_d = 200 \text{ ns}, Z_l = 225 \Omega$ and $\Gamma_l = 0.8$ ).                                                                         | 98        |

| 6.8  | Step response of a lossless line: input and output currents ( $Z = 25 \Omega$ , $t_d = 200 \text{ ns}, Z_l = 225 \Omega$ and $\Gamma_l = 0.8$ ).                                                                         | 98        |

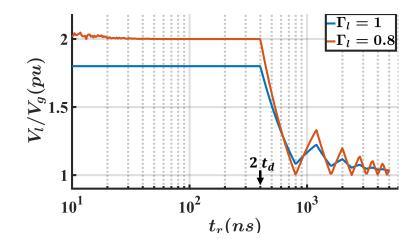

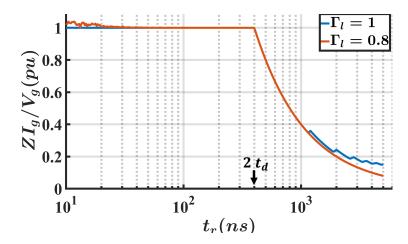

| 6.9  | Peak load voltage caused by the mismatching, as a function of the generator voltage rise time $(Z = 25 \Omega, t_d = 200 \text{ ns})$ .                                                                                  | 99        |

| 6.10 | Peak generator current caused by the cable, as a function of the                                                                                                                                                         |           |

| 6.11 | generator voltage rise time $(Z = 25 \Omega, t_d = 200 \text{ ns})$ Zoomed portion of Fig. 6.9: load surge voltage derived from simulations and formulae. Dotted lines represent the formulae and contin-                | 100       |

| 6 12 | uous lines are the simulations results $(Z = 25 \Omega, t_d = 200 \text{ ns})$<br>Four-conductor transmission line: schematic representation of an el-                                                                   | 101       |

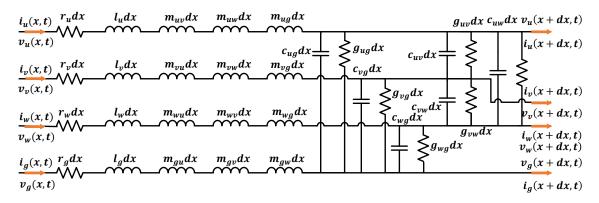

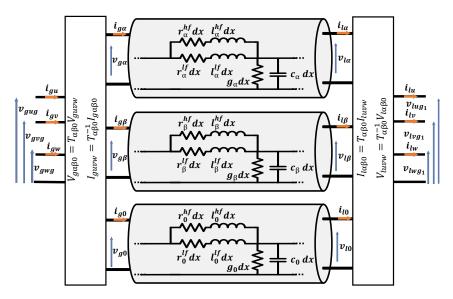

| 0.12 | ementary component of transmission line                                                                                                                                                                                  | 102       |

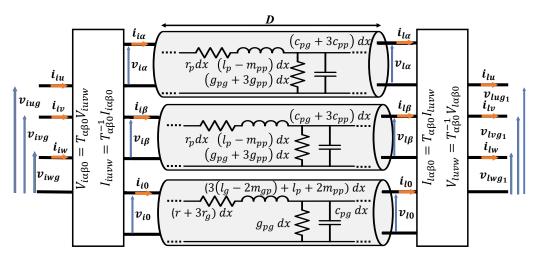

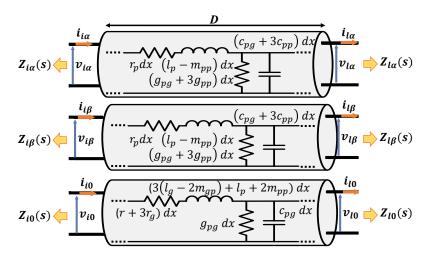

| 6.13 | Three decoupled transmission lines that represent a simplify three-<br>phase power cable with their equivalent parameters. " $p$ " phase pa-<br>rameter, " $pp$ " phase to phase parameter, " $pg$ " phase to ground pa- | -         |

|      | rameter                                                                                                                                                                                                                  | 108       |

| 6.14 | Four-conductor transmission lines: schematic details about the impeda<br>seen at the input and output cable terminations for each component                                                                              | nces      |

|      | obtained by means of the Clarke transformation                                                                                                                                                                           | 109       |

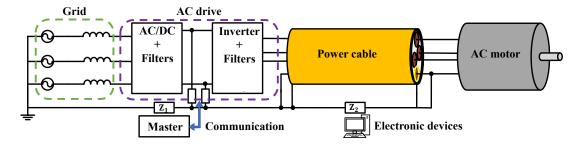

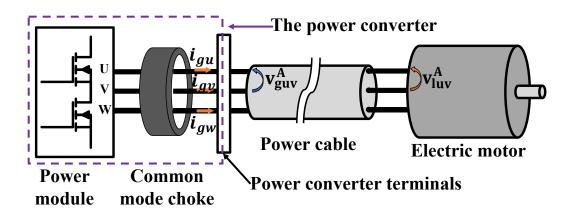

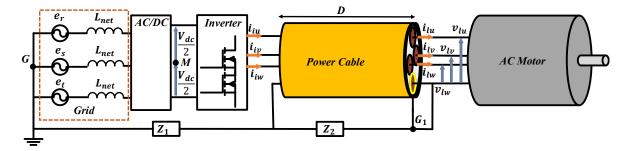

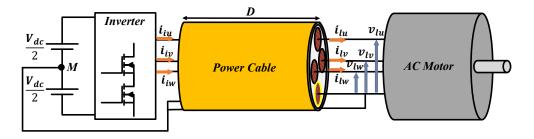

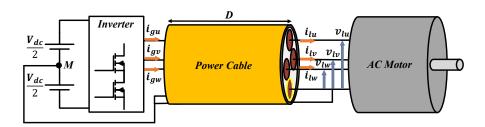

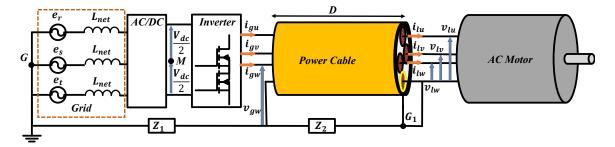

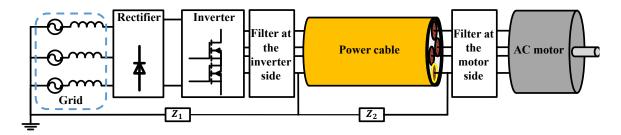

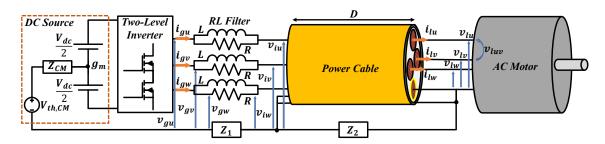

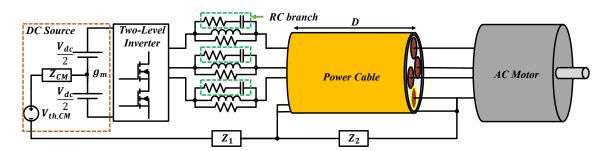

| 6.15 | Industrial three-phase electric drive representation with: power grid,                                                                                                                                                   |           |

|      | rectifier, inverter, cable and motor.                                                                                                                                                                                    |           |

|      | 1 0                                                                                                                                                                                                                      | 111       |

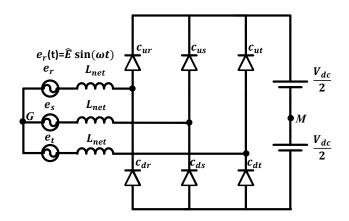

|      | Common mode equivalent circuit of a three-phase diode bridge rectifier                                                                                                                                                   |           |

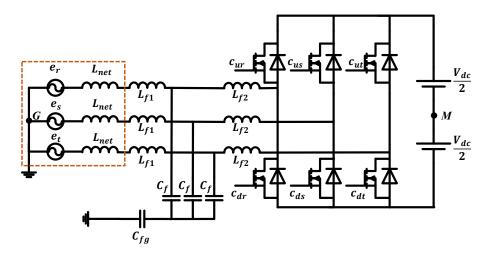

|      | Three-phase boost rectifier.                                                                                                                                                                                             | 112       |

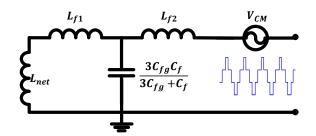

|      | Common mode equivalent circuit of a three-phase boost rectifier                                                                                                                                                          | 113       |

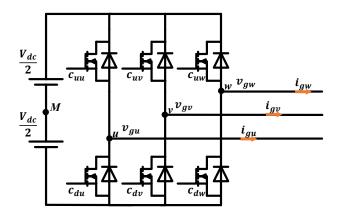

|      | Three-phase inverter                                                                                                                                                                                                     | 113       |

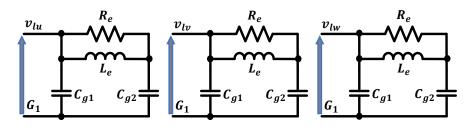

| 6.21 | rameter for AC motors                                                                                                                                                                                                    | 115       |

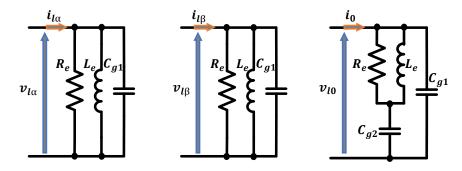

| 0.22 | Equivalent $\alpha$ , $\beta$ and 0 circuits of the high frequency motor lumped<br>parameter circuit shown in Fig. 6.21.                                                                                                 | 115       |

| 6.23 | Simplified motor equivalent circuits of the $\alpha$ , $\beta$ and 0 components.                                                                                                                                         | 116       |

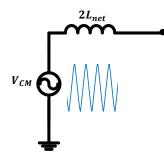

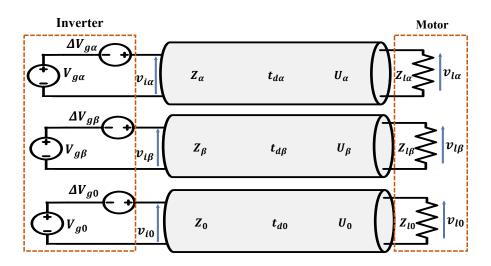

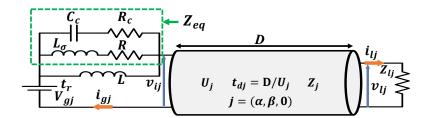

| 6.25 | Schematic representation of a drive, which presents the ground ref-<br>erence connected to the middle point of the DC bus Equivalent model of the drive used for study the motor overvoltages.                                                               | 117<br>118 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

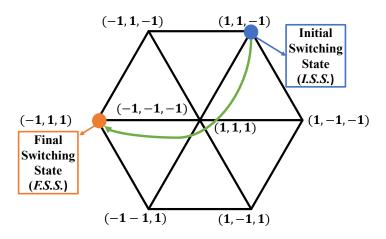

| 6.26 | Schematic representation of the initial and final inverter switching states.                                                                                                                                                                                 | 118        |

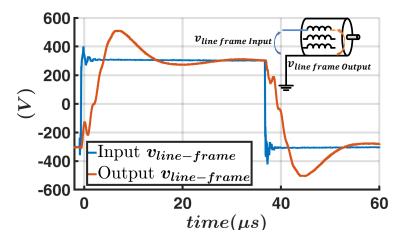

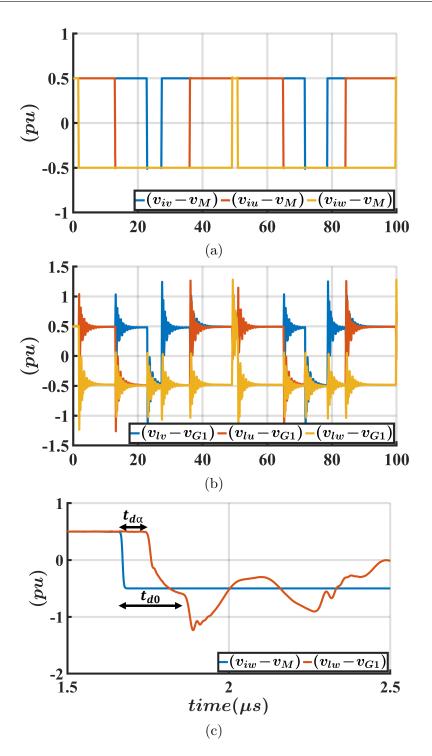

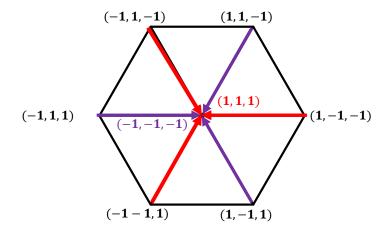

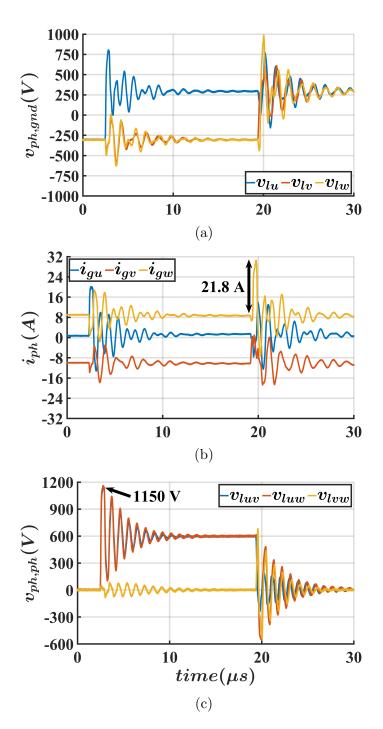

|      | Simulation results when the ground is connected to the middle point<br>of the DC bus: phase-to-ground voltages. (a) voltages at the input<br>terminals of the cable. (b) voltages at the output terminals of the<br>cable. (c) Zoomed portion of (a) and (b) | 123        |

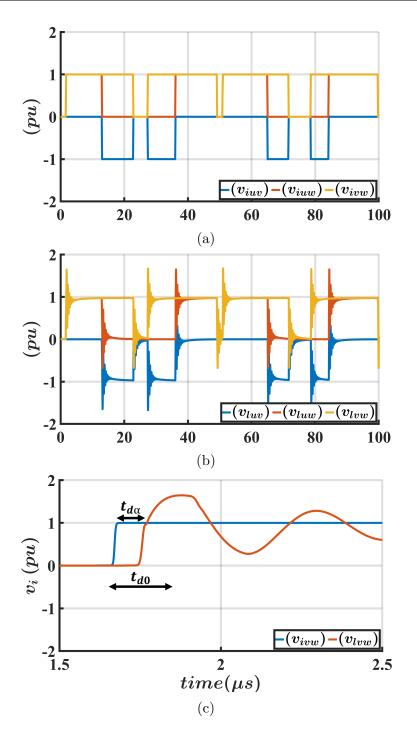

| 6.28 | Simulation results when the ground is connected to the middle point<br>of the DC bus: phase-to-phase voltages. (a) voltages at the input<br>terminals of the cable. (b) voltages at the output terminals of the<br>cable. (c) Zoomed portion of (a) and (b)  | 124        |

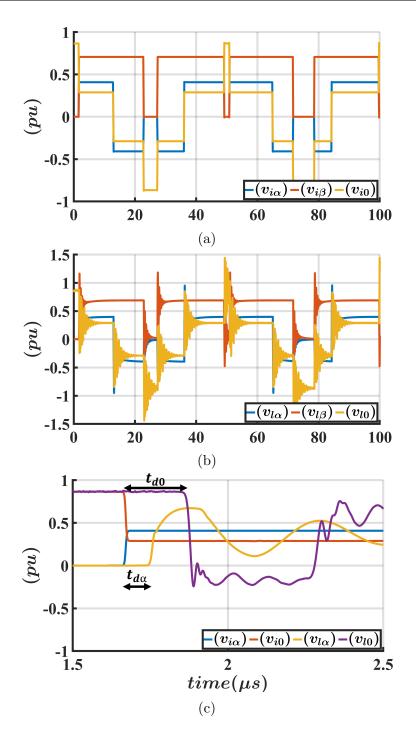

| 6.29 | Simulation results when the ground is connected to the middle point<br>of the DC bus: $\alpha$ , $\beta$ and 0 voltages. (a) voltages at the input termi-<br>nals of the cable. (b) voltages at the output terminals of the cable.                           |            |

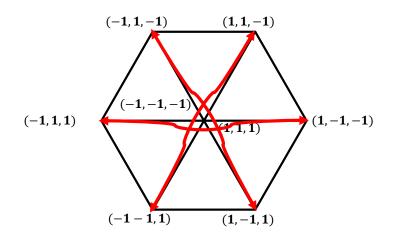

| 6.30 | (c) Zoomed portion of (a) and (b)                                                                                                                                                                                                                            | 125        |

| 6.31 | the 0                                                                                                                                                                                                                                                        | 127        |

|      | by the 0 component is major than the velocity of propagation of the $\alpha$ and $\beta$ components.                                                                                                                                                         | 129        |

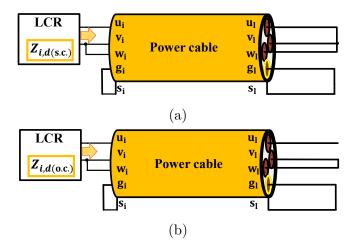

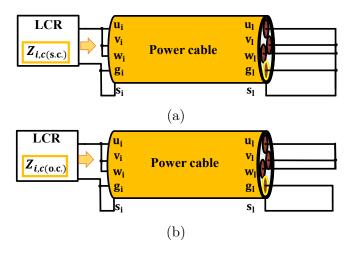

| 7.1  | Differential mode parameter measurements of the cable. (a) Short-<br>circuit configuration and (b) Open-circuit configuration.                                                                                                                               | 136        |

| 7.2  | Common mode parameter measurements of the cable. (a) Short-<br>circuit configuration. (b) Open-circuit configuration.                                                                                                                                        | 139        |

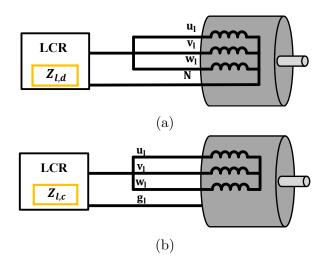

| 7.3  | Motor parameter measurement. (a) Phase-to-neutral and (b) phase-<br>to-ground.                                                                                                                                                                               | 140        |

| 7.4  | The experimental setup.                                                                                                                                                                                                                                      | 141        |

| 7.5  | Schematic representation of a drive, which presents the ground ref-<br>erence connected to the middle point of the DC bus.                                                                                                                                   | 141        |

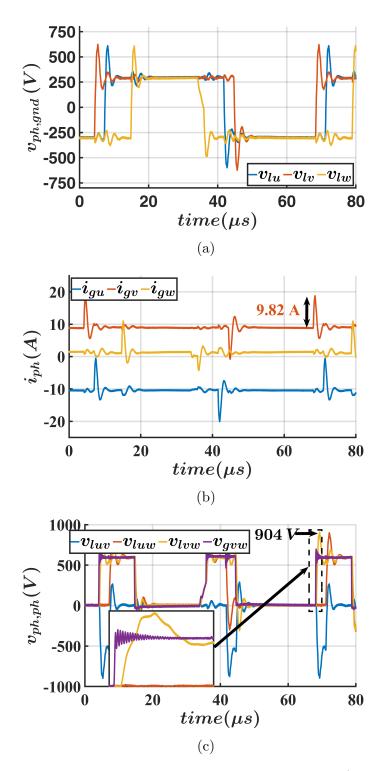

| 7.6  | Experimental results obtained from the drive shown in Fig. 7.4. (a) Line-to-ground motor voltage, (b) inverter currents and (c) line-to-                                                                                                                     |            |

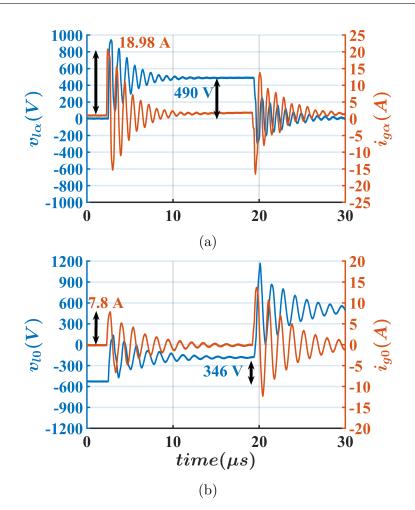

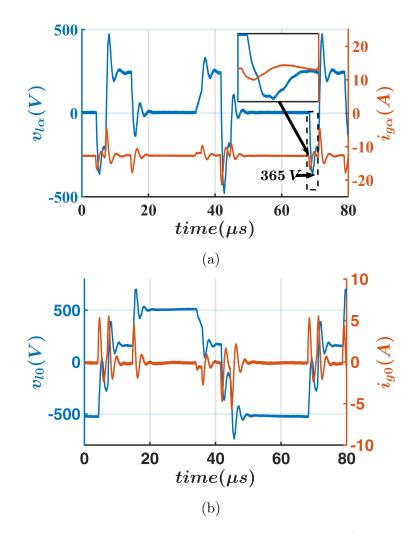

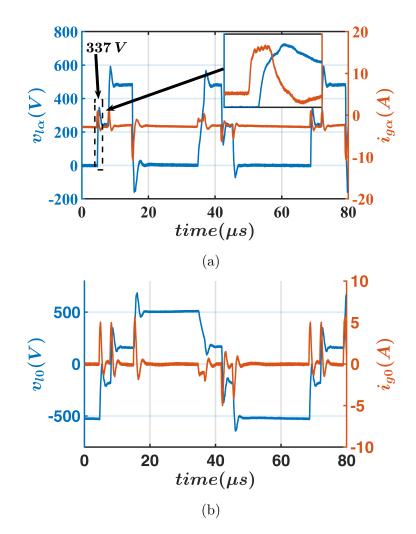

| 7.7  | line motor voltages                                                                                                                                                                                                                                          | 142        |

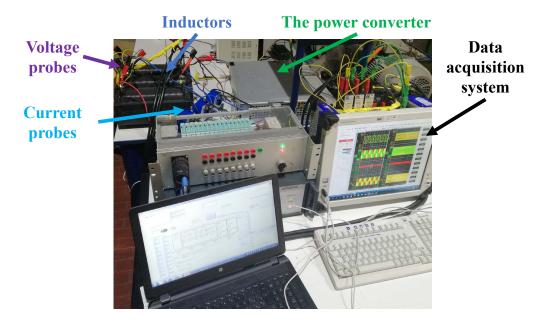

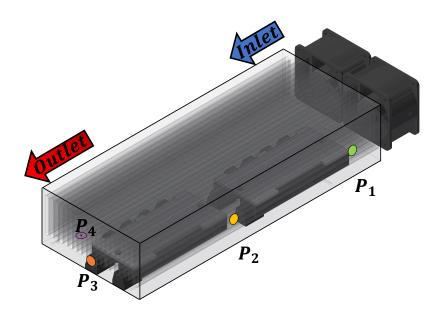

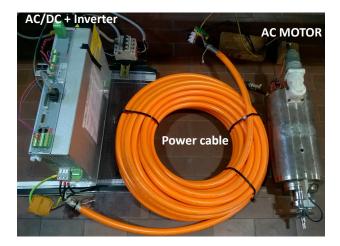

| 7.8  | (b) Inverter 0 component current and motor 0 component voltage<br>Laboratory test bench used for the comparison between experimental                                                                                                                         | 144        |

|      | measurements and proposed simulation results.                                                                                                                                                                                                                | 145        |

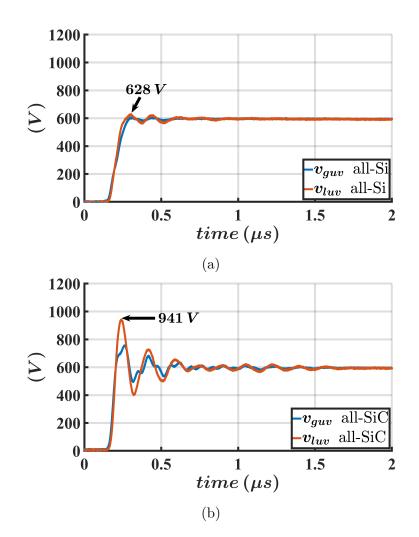

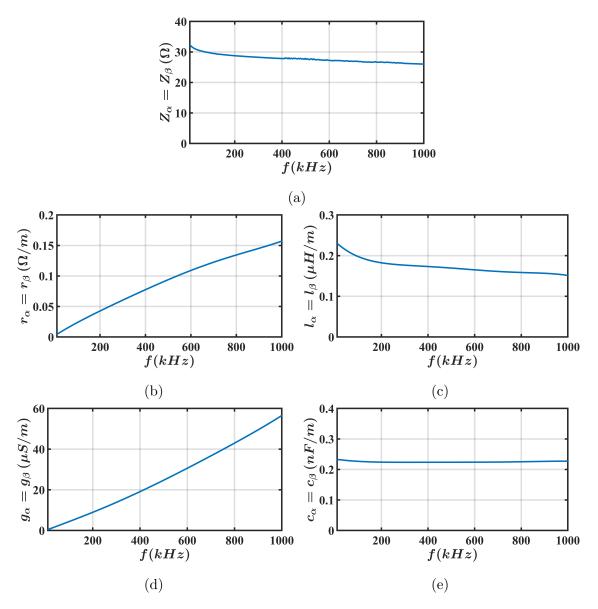

| <ul><li>7.9 Schematic circuital representation of the drive represented in Fig. 7.8</li><li>7.10 Measured parameters of the differential components in function of the frequency: (a) cable characteristic impedance, (b) per unit cable resistance, (c) per unit cable inductance, (d) per unit cable conduc-</li></ul> | .145       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

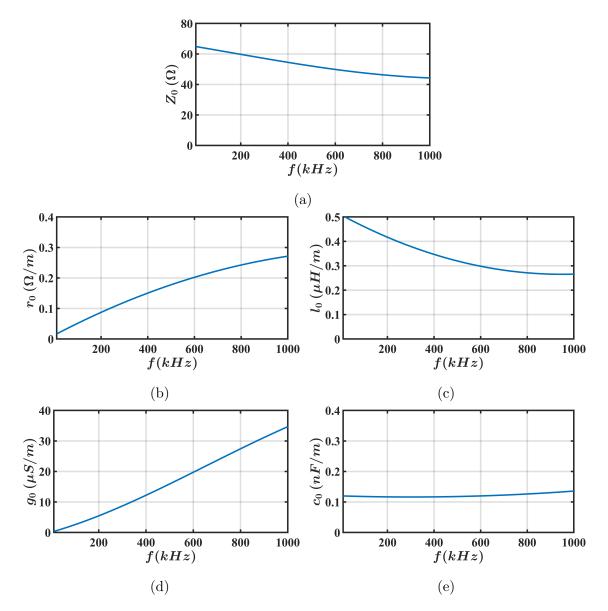

| 7.11 Measured parameters of the common mode component in function<br>of the frequency: (a) cable characteristic impedance, (b) per unit<br>cable resistance, (c) per unit cable inductance, (d) per unit cable                                                                                                           | 147<br>148 |

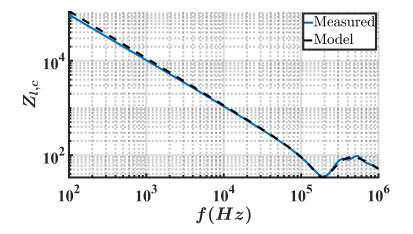

| 7.12 Motor frequency responses: magnitude of the phase-to-ground impedar                                                                                                                                                                                                                                                 |            |

| 7.13 Schematic representation of an elementary component of transmis-                                                                                                                                                                                                                                                    |            |

| sion line: the proposed one.                                                                                                                                                                                                                                                                                             | 150        |

| 7.14 Three decoupled transmission lines with the proposed transmission line model.                                                                                                                                                                                                                                       | 151        |

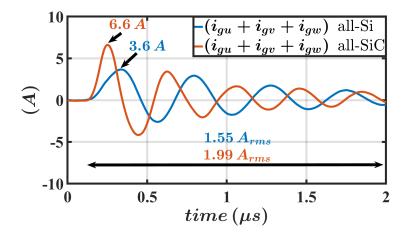

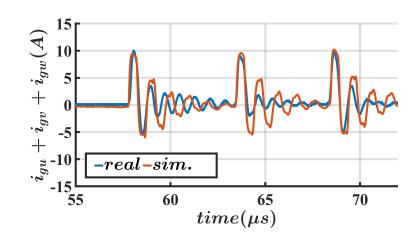

| 7.15 Comparison between the proposed simulation and the experimental                                                                                                                                                                                                                                                     | 101        |

| results: common mode current $(i_{gu} + i_{gv} + i_{gw})$                                                                                                                                                                                                                                                                | 152        |

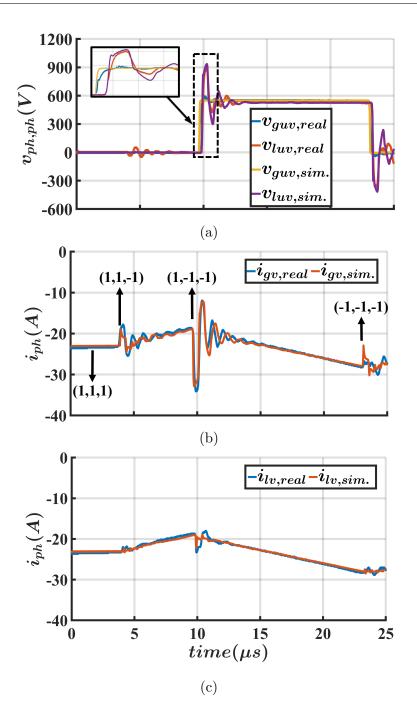

| 7.16 Comparison between the proposed simulation and the experimen-                                                                                                                                                                                                                                                       |            |

| tal results. (a) Input and output line voltages. (b) Inverter phase currents. (c) Motor phase currents.                                                                                                                                                                                                                  | 153        |

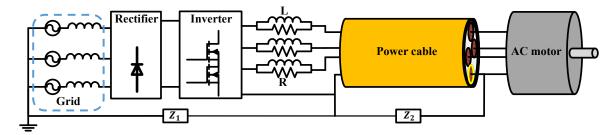

| 8.1 Schematic representation of an electric drive and standard location                                                                                                                                                                                                                                                  | 100        |

| of the overvoltage filters.                                                                                                                                                                                                                                                                                              | 156        |

| 8.2 Schematic representation of an electric drive with mounted the RL                                                                                                                                                                                                                                                    |            |

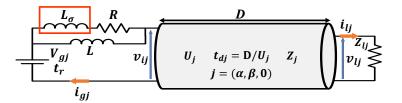

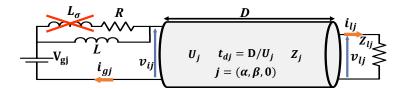

| filter                                                                                                                                                                                                                                                                                                                   | 161        |

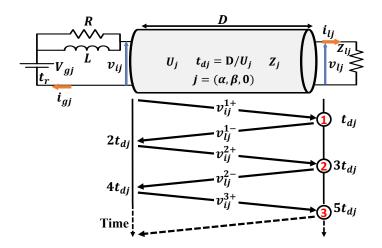

| 8.3 $\alpha$ , $\beta$ and 0 drive model plus RL filter equivalent model and the corresponding Bewley lattice diagram. In red circles, the order of                                                                                                                                                                      |            |

| the propagation is indicated                                                                                                                                                                                                                                                                                             | 162        |

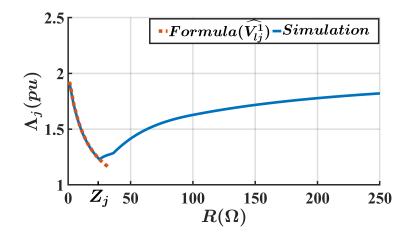

| 8.4 Comparison of the resistance sweep using the same filter inductance                                                                                                                                                                                                                                                  |            |

| $(L = 21 \ \mu \text{H})$ between equation and simulation data $(Z_j = 25 \ \Omega,$                                                                                                                                                                                                                                     |            |

| $t_r = 0$ , $\Gamma_{lj} = 1$ and $t_{dj} = 200$ ns). The results are normalized by the generator voltage $(V_{gj})$ .                                                                                                                                                                                                   | 162        |

| 8.5 The experimental setup: electric drive plus RL filter                                                                                                                                                                                                                                                                |            |

| 8.6 Equivalent circuit scheme of the used experimental setup with a de-                                                                                                                                                                                                                                                  | 101        |

| tailed representation of the electrical variables of the system. In this                                                                                                                                                                                                                                                 |            |

| scheme, the common mode voltage term, introduced by the power                                                                                                                                                                                                                                                            | 100        |

| grid, is neglected $(V_{th,CM})$                                                                                                                                                                                                                                                                                         | 166        |

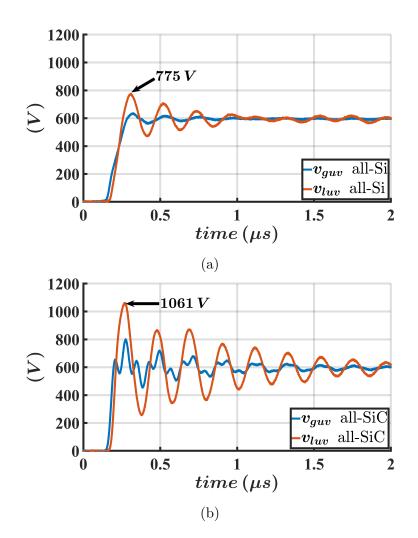

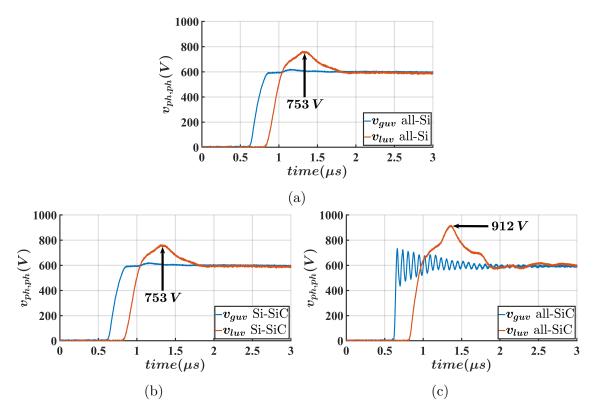

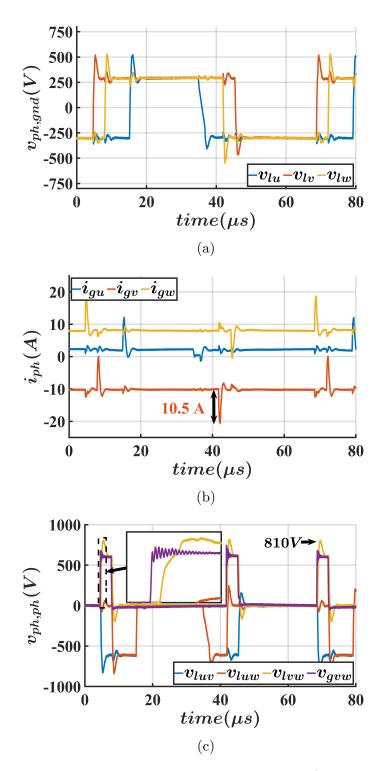

| tor terminals when RL filter is adopted. (a) all-Si. (b) Si-SiC. (c)                                                                                                                                                                                                                                                     |            |

| all-SiC                                                                                                                                                                                                                                                                                                                  | 167        |

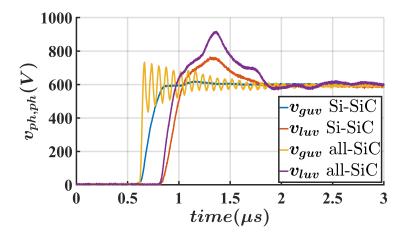

| 8.8 Inverter and motor line-to-line voltages comparisons using the same                                                                                                                                                                                                                                                  |            |

| filter $(R = 23 \Omega, L = 21 \mu \text{H})$ and two inverters: Si-SiC $(tr = 200 \text{ ns})$                                                                                                                                                                                                                          | 100        |

| and all-SiC $(tr = 30 \text{ ns})$ .                                                                                                                                                                                                                                                                                     | 168        |

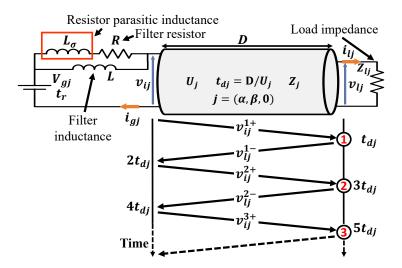

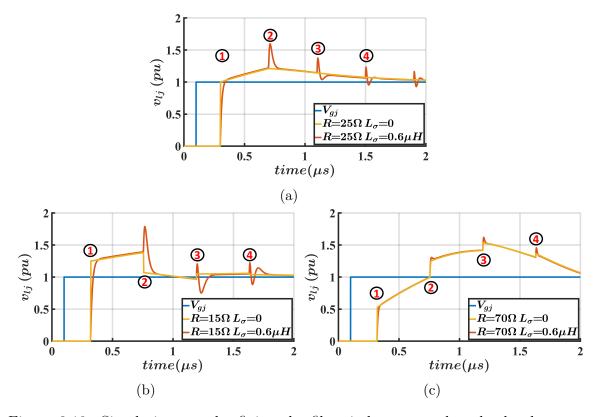

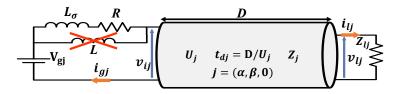

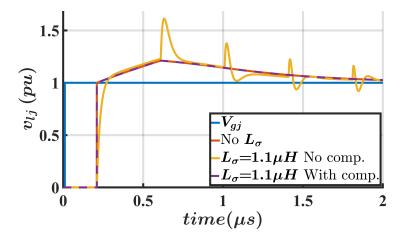

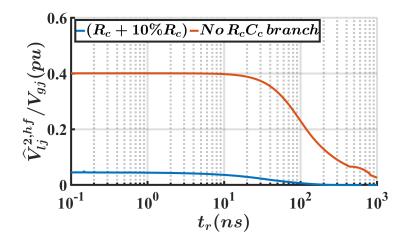

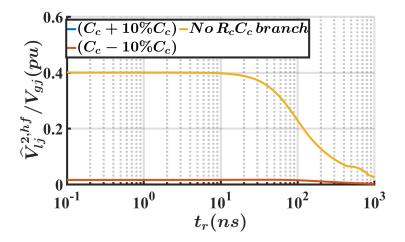

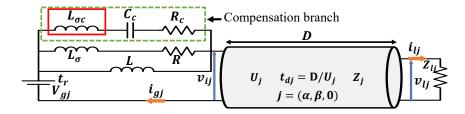

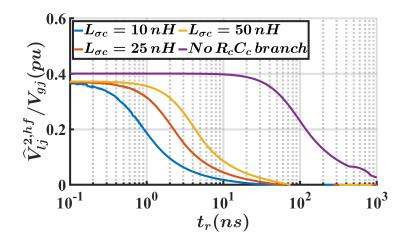

| 8.9<br>8.10 | $\alpha$ , $\beta$ and 0 drive model plus RL filter equivalent model and the corresponding Bewley lattice diagram. In red circles, the order of the propagation is indicated                                                                                                                                                                                                      | 170       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

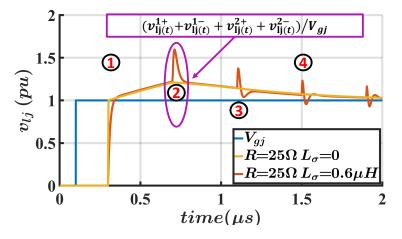

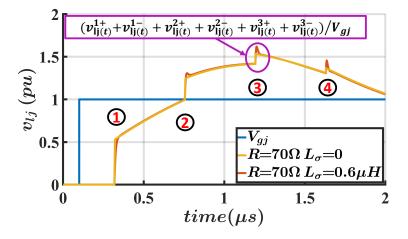

|             | response to a unit step with and without the resistor parasitic in-<br>ductance $(Z_j = 25 \ \Omega, L = 21 \ \mu\text{H}, \Gamma_{lj} = 1, t_{dj} = 200 \text{ ns and } L_{\sigma} = 0.6 \ \mu\text{H})$ . (a) filter resistor is equal to the characteristic impedance $(Z_j)$ , (b) filter resistor is smaller than the characteristic impedance $(Z_j) = 0.6 \ \mu\text{H}$ . |           |

|             | $(Z_j)$ and, (c) the filter resistor is bigger than the characteristic impedance $(Z_j)$ .                                                                                                                                                                                                                                                                                        | ce<br>171 |

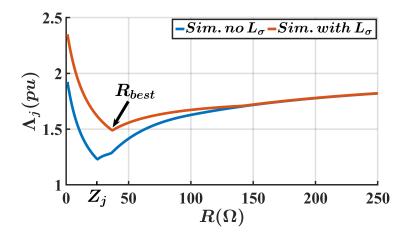

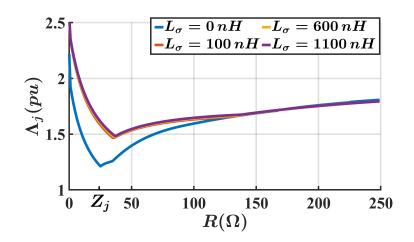

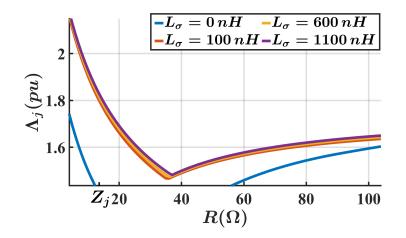

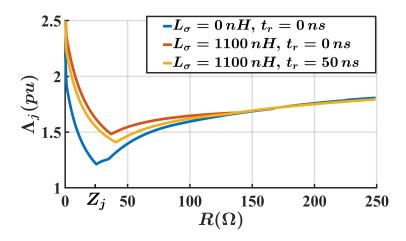

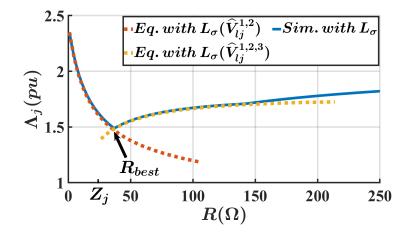

| 8.11        | Simulation results: overvoltage factors $(V_{lj}/V_{gj})$ in function of the filter resistance. A comparison between the condition with and without the resistor parasitic inductance $(Z_j = 25 \Omega, L = 21 \mu H, \Gamma_{lj} = 1 \text{ and}$                                                                                                                               | 172       |

| 8.12        | $t_{dj} = 200 ns$ )                                                                                                                                                                                                                                                                                                                                                               | 172       |

|             | parasitic inductance ( $Z_j = 25 \Omega$ , $L = 21 \mu H$ , $\Gamma_{lj} = 1$ and $t_{dj} = 200 ns$ )                                                                                                                                                                                                                                                                             | 173       |

| 8.13        | The zoomed portion of Fig. 8.12.                                                                                                                                                                                                                                                                                                                                                  | 173       |

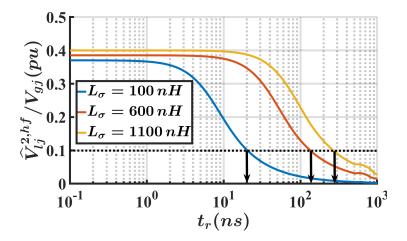

| 8.14        | Simulation results: additional load voltage caused by $L_{\sigma}$ , as a func-                                                                                                                                                                                                                                                                                                   |           |

|             | tion of the $V_{gj}$ rise time $(R = Z_j = 25 \Omega, L = 21 \mu H, t_{dj} = 200 ns$ and                                                                                                                                                                                                                                                                                          | 174       |

| 8.15        | $\Gamma_{lj} = 1$ ). The results are in per unit                                                                                                                                                                                                                                                                                                                                  | 174       |

|             | $(Z_j = 25 \ \Omega, L = 21 \ \mu \text{H}, \Gamma_{lj} = 1 \text{ and } t_{dj} = 200 \text{ ns}).$                                                                                                                                                                                                                                                                               | 175       |

| 8.16        | Transmission line model using the RL filter.                                                                                                                                                                                                                                                                                                                                      | 177       |

|             | The RL filter equivalent low-frequency circuit. The parasitic induc-                                                                                                                                                                                                                                                                                                              |           |

|             | tance is considered as a short circuit.                                                                                                                                                                                                                                                                                                                                           | 178       |

| 8.18        | The RL filter equivalent high-frequency circuit. The inductance is considered as an open circuit.                                                                                                                                                                                                                                                                                 | 178       |

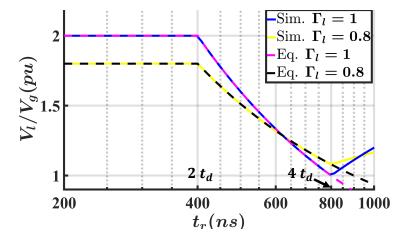

| 8.19        | Simulations results fixing the filter inductance value: load voltages                                                                                                                                                                                                                                                                                                             | 110       |

|             | response to a unit step with and without the resistor parasitic in-<br>ductance $(Z_j = 25 \ \Omega, L = 21 \ \mu\text{H}, \Gamma_{lj} = 1 \text{ and } t_{dj} = 200 \text{ ns})$ . The<br>resistor is equal to the line characteristic impedance $(Z_j)$ . In detail,                                                                                                            |           |

| 8.20        | the analyzed component is highlighted in purple                                                                                                                                                                                                                                                                                                                                   | 179       |

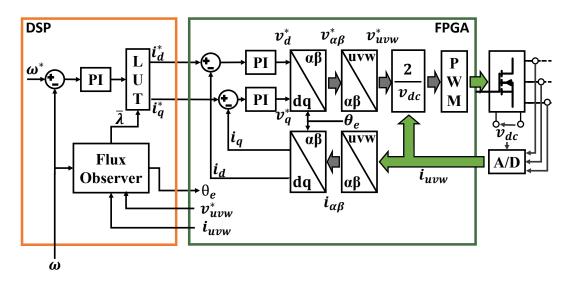

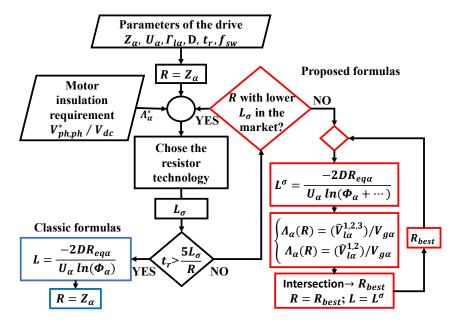

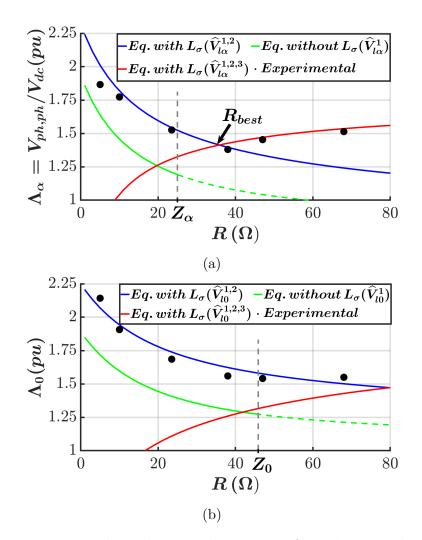

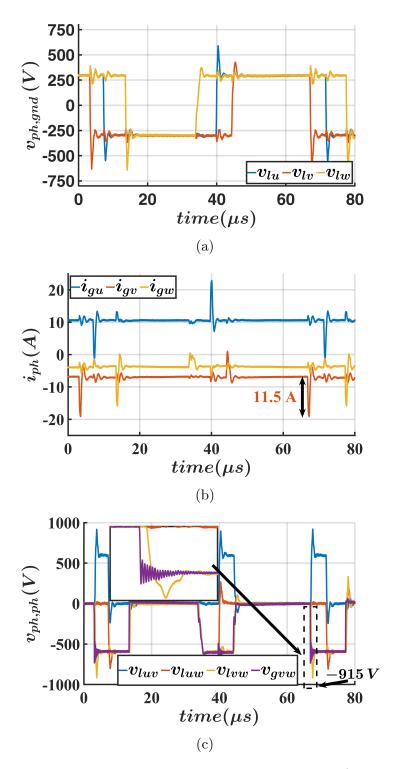

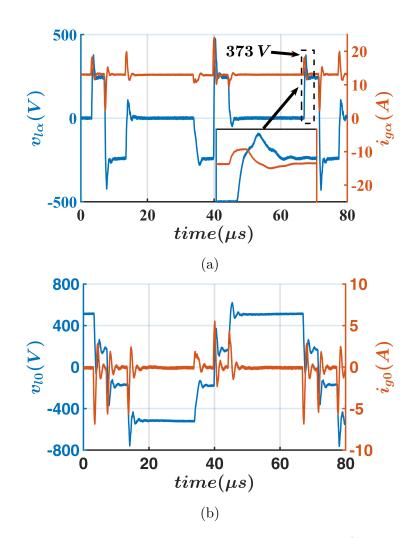

|             | tance $(Z_j = 25 \ \Omega, L = 21 \ \mu\text{H}, \Gamma_{lj} = 1 \text{ and } t_{dj} = 200 \text{ ns})$ . Resistor major than the line characteristic impedance $(Z_j)$                                                                                                                                                                                                           | 182       |