# POLITECNICO DI TORINO Repository ISTITUZIONALE

Power loss analysis and measurement of a high efficiency DC-DC converter for EV traction AC drives

Original

Power loss analysis and measurement of a high efficiency DC-DC converter for EV traction AC drives / Fratta, Antonino; Guglielmi, Paolo; Pellegrino, GIAN - MARIO LUIGI; Villata, Franco. - STAMPA. - 1:(2000), pp. 347-352. (Intervento presentato al convegno IEEE International Conference on Industrial Technology ICIT 2000 tenutosi a Goa (IND) nel 19-22 January 2000) [10.1109/ICIT.2000.854179].

*Availability:* This version is available at: 11583/1412239 since:

Publisher: IEEE

Published DOI:10.1109/ICIT.2000.854179

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

## Power loss analysis and measurement of a high efficiency DC-DC converter for EV traction AC drives.

A. Fratta\* (member), P. Guglielmi, G.M. Pellegrino, F. Villata (member)

Dipartimento di Ingegneria Elettrica Industriale, Politecnico di Torino, c.so duca degli Abruzzi 24, 10129 Torino, Italy; \*corr. auth. email: frattato@athena.polito.it

Abstract - Previous works have shown the power design effectiveness of novel H-bridge-based dc-dc boost conversion structure, as well as the feasibility of real-time dc-link voltage adaptation to inverter load, in battery-supplied ac motor drives. In this paper a novel test bench has been developed, suitable for power loss measurements in high-efficiency bi-directional dc-dc converters. In order to allow for quasi-direct measurement of the lost power, the concept is to operate the converter by input current having constant module, handling alternating energy flow between two large capacitor banks at given input/output DC voltages. Accordingly, the input current reference is a low frequency (65 Hz) rectangular-wave, whose duty-cycle is regulated by suitable voltage loop due to constant module operation. Except for added large capacitor banks' losses and other secondary effects related to 65Hz operation, the input DC power supply is shown equivalent to conversion losses at given DC working point.

The results point-out the high efficiency of the conversion structure well matched with simple analytical models.

## I. INTRODUCTION

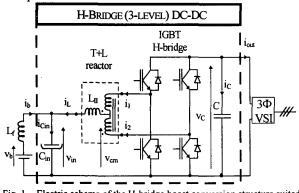

As far as dc-voltage battery-supplied ac motor drives are investigated [3], the cost-effectiveness of a proper H-Bridgebased boost dc-dc conversion structure has been demonstrated [1], interposed between battery and inverter to adapt the dc-link voltage to load requirements.

This result has been achieved thanks to the large current rating reduction in the inverter's power module design, mainly related to the wide voltage range of practical battery packs [1,3]. The possible drawbacks, in weight and cost of the input coupling reactor, have been shown balanced by considerable decrease on rms current requirements of filter capacitors, thanks also to the peculiar integration of interphase transformer and input coupling inductance functions in a single power reactor, namely "T+L" reactor [1].

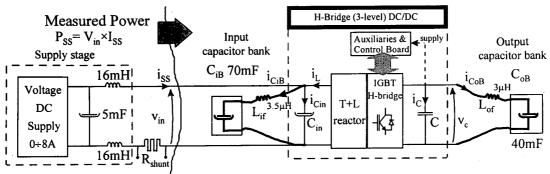

New high rms-current-rated non-electrolytic small film power capacitors have been also adopted to filter the dc-link PWM current ripple [2]. Further improvements in size, cost and transient dc-link voltage response have been reliably achieved by adopting proper non-linear control and modulation strategies [2], purposely analyzed and developed in order to overcome the peculiar low energy-storage operation of the bi-directional boost conversion. The experimental verification in [2] has been carried-out on a 30 kW prototype convertor system adopting commercial 3-phase IGBT Intelligent Power Modules (IPM). This convertor system (whose scheme is reported in Fig.1) is under test in the work, concerning specifically the measurement of efficiency and the related verification of power loss models in the various operating conditions of practical interest in EV or HEV traction AC drives. The very high efficiency of the adopted boost conversion structure has requested a novel measurement concept, purposely defined and experimentally developed.

#### II. DESCRIPTION OF THE POWER CONVERSION SYSTEM.

A summarized description of the conversion system is reported. Fig.1 reports the electrical scheme of the power converter as a part of battery supplied AC drive.

## A. Variables definition.

With reference to Fig.1 scheme, a list of system variables and parameters is introduced as used in the following; mean values are expressed by capital letters of the corresponding instantaneous variables.

$P_{in} \cong V_{in} I_L$ : converted input power;

i<sub>L</sub>: total converted input current;

- v<sub>in</sub>: converter's input voltage;

- v<sub>c</sub>: converter's output voltage;

C<sub>in</sub>: input capacitor inside the converter;

C: inner output capacitor (non-electrolytic);

L<sub>II</sub>: T+L reactor's input inductance;

R<sub>ph</sub>: T+L phase resistance (each winding);

$f_{SW}=1/T_{SW}$ :switching modulation frequency (each phase);

I<sub>label</sub>: H-bridge IPM rated current;

$a_{SW} = \Delta I_{L,pk}/I_L$ : switching ratio (peak ripple/mean value);

m<sub>1</sub>,m<sub>2</sub>: modulation indexes;

D: H-bridge average duty-cycle ( $\equiv M_1, M_2$ ).

| TABLE I - | RATINGS | OF CONVERTOR | SYSTEM. |

|-----------|---------|--------------|---------|

|           |         |              |         |

| RATED VALUES            |                        |                          |                          |                                                |                             |                         |                                              |

|-------------------------|------------------------|--------------------------|--------------------------|------------------------------------------------|-----------------------------|-------------------------|----------------------------------------------|

| P <sub>in</sub><br>[kW] | v <sub>in</sub><br>[V] | v <sub>c</sub><br>[V]    | f <sub>sw</sub><br>[kHz] | C <sub>in</sub><br>[mF]<br>350[V]<br>electrol. | C<br>[µF]<br>600[V]<br>film | L <sub>II</sub><br>[µH] | I <sub>label</sub><br>[A]<br>PM200<br>CVA060 |

| 15<br>30 max            | 150÷<br>300            | v <sub>in</sub> ÷<br>400 | 10                       | 3.3                                            | 330                         | 38                      | 200                                          |

B. Current dynamics.

The T+L reactor behavior is modeled in terms of state variables through a transformation from "phase" to "mode" variables (common- and differential-mode of phase variables). Referring to a generic couple of phase variables  $x_1, x_2$ , the correspondent "mode" variables vector is:

$$\mathbf{x}_{cm,dm} = \frac{1}{2} \mathbf{U} \mathbf{x}_{1,2}$$

;  $\mathbf{U} = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$  (1)

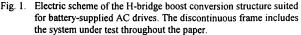

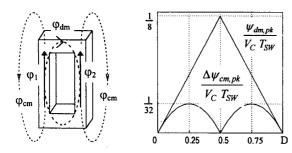

This transformation defines common and differential mode modulation indexes, voltages, currents and fluxes ( $v_{cm,dm}$ ,  $m_{cm,dm}$ ,  $i_{cm,dm}$ ,  $\psi_{cm,dm}$ , respectively). Typical modulation index waveforms are shown in Fig.2, in two operating conditions differing for D value. D is equal to common mode index mean value, and then very close (excepting for inner voltage drops) to the i/o voltage ratio:

Notice that, being the "phase" ripple frequency  $f_{SW}$ , and due to half modulation period displacement of phase modulation indexes, the common-mode fundamental frequency is "2· $f_{SW}$ " (second harmonic), while differentialmode frequency is  $f_{SW}$  (first harmonic).

"Mode" inductances (3) are derived as in (3):

$$\begin{cases} L_{cm} = \frac{\psi_{cm}}{i_{cm}} = \frac{(\psi_1 - \psi_2)}{\frac{1}{2}i_L} = 2L_{II} \\ L_{dm} = \frac{\psi_{dm}}{i_{dm}} = \frac{\frac{1}{2}(\psi_1 - \psi_2)}{i_{dm}} = \frac{1}{2}L_{\mu 12} \end{cases}$$

(3)

where  $L_{II}$  and  $L_{\mu 12}$  are the inductance values which can be measured: between common input and short-circuited phase terminals; between the phase terminals by common input left open (respectively 38µH and 3.3mH in the design).

The current dynamics can be then expressed in terms of common- and differential-mode variables, disregarding on (4) resistive and power switches drops:

$$\frac{\mathrm{d}}{\mathrm{d}t} \left\{ \begin{bmatrix} \mathbf{L}_{\mathrm{cm}} & \mathbf{0} \\ \mathbf{0} & \mathbf{L}_{\mathrm{dm}} \end{bmatrix} \cdot \begin{vmatrix} \mathbf{i}_{\mathrm{cm}} \\ \mathbf{i}_{\mathrm{dm}} \end{vmatrix} \right\} = \begin{vmatrix} \mathbf{1} \\ \mathbf{0} \end{vmatrix} \mathbf{v}_{\mathrm{in}} - \begin{vmatrix} \mathbf{m}_{\mathrm{cm}} \\ \mathbf{m}_{\mathrm{dm}} \end{vmatrix} \mathbf{v}_{\mathrm{C}}$$

(4)

#### C. Flux and current waveform and properties.

Multilevel conversion structures own peculiar properties concerning modulation ripple both on i/o currents and on T+L reactor fluxes, leading to a general reduction of ripple terms, falling down to cancellation in singular working points (D=1/2, in particular) [1]. Since the differential-mode flux is generated by modulation ripple without DC component, the differential-mode current can be freely designed to be very small with respect to common-mode one (3A peak max in the design). This is why "i<sub>dm</sub>" will be ignored in the calculation of rms current values.

Referring to continuos current mode of operation, the input current ripple is a "second harmonic" triangle. The total input rms current can be then referred to mean value by (5):

$$I_{L,rms} = I_L \sqrt{1 + \frac{a_{SW}^2}{3}}$$

(continuos mode) (5)

Note a<sub>sw</sub> is a function of D by two-range expressions (6):

$$I_{sw} = \frac{\Delta I_{in,pk}}{I_{batt}} = \begin{cases} \frac{1}{4} \frac{V_c}{I_L} \frac{T_{sw}}{L_{II}} (1-2D) \cdot D; & @ D < \frac{1}{2} \\ \frac{1}{4} \frac{V_c}{I_L} \frac{T_{sw}}{L_{II}} (2D-1) \cdot (1-D); & @ D > \frac{1}{2} \end{cases}$$

(6)

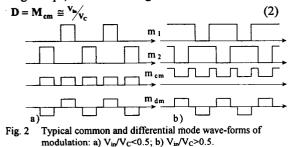

Correspondingly, input and output capacitors' rms current values are derived (7,8) [1], as depicted in Fig.3.

$$I_{\text{Cin,rms}} = I_{\text{L}} \frac{a_{\text{SW}}}{\sqrt{3}}$$

(7)

Fig.3 I/O capacitors rms current values vs.  $V_{in}$  @ V<sub>c</sub>=400V, P=30kW

Common-mode flux peak value is reported (9), both in terms of common-mode and of converter's input quantities:

$$\Psi_{\rm cm,pk} = \mathbf{L}_{\rm cm} \mathbf{I}_{\rm cm} + \Delta \Psi_{\rm cm,pk} = \mathbf{L}_{\rm II} \mathbf{I}_{\rm L} + \Delta \Psi_{\rm cm,pk}$$

(9)

Ψ

where  $\Delta$  indicates alternative components, the only component in differential-mode flux (steady state):

$$\psi_{\rm dm,pk} \equiv \Delta \psi_{\rm dm,pk} \tag{10}$$

Common-mode waveform is a "second harmonic" triangle while differential-mode is a "first harmonic" trapezoid, according to integration of the respective waveforms in Fig.2.

Analogously to capacitor currents, the peak flux values (11,12) are differing in D operating ranges, as depicted by Fig.4, showing also the T+L reactor flux path.

Fig. 4 T+L common- and differential-mode fluxes; their ripple peak values as a function of common mode index  $(M_{cm}=D)$ .

$$\Delta \Psi_{\rm cm,pk} = \begin{cases} \frac{T_{\rm SW} V_{\rm c}}{4} D(1-2D) & @ D < \frac{1}{2} \\ \frac{T_{\rm SW} V_{\rm c}}{4} (1-D)(2D-1) & @ D > \frac{1}{2} \end{cases}$$

(11)

$$\Delta \Psi_{\rm dm,pk} = \begin{cases} \frac{T_{\rm SW} V_{\rm c}}{4} D & @ D < \frac{1}{2} \\ \frac{T_{\rm SW} V_{\rm c}}{4} (1-D) & @ D > \frac{1}{2} \end{cases}$$

(12)

## III. CONVERTOR LOSS ANALYSIS AND MODEL.

The detailed expression of convertor's power losses is:

$$\mathbf{P}_{\text{tot,conv}} = \mathbf{P}_{\text{Cin}} + \mathbf{P}_{\text{C}} + \mathbf{P}_{\text{T+L}} + \mathbf{P}_{\text{HB}} + \mathbf{P}_{\text{aux}}$$

(13)

1)  $P_{Cin}$  and  $P_C$  (input and output capacitors losses) are depending on their ESR, respectively  $R_{Cin}$  and  $R_C$ :

$$\mathbf{P}_{\text{Cin}} = \mathbf{R}_{\text{Cin}} \cdot \left(\mathbf{I}_{\text{Cin,rms}}\right)^2 \qquad [\text{refer to (7)}] \qquad (14)$$

$$\mathbf{P}_{\mathrm{C}} = \mathbf{R}_{\mathrm{C}} \cdot \left(\mathbf{I}_{\mathrm{C,rms}}\right)^{2} \qquad [\text{refer to (8)}] \qquad (15)$$

2)  $P_{T+L}$  (integrated transformer + inductor losses) must be modeled by copper and ferrite losses:

$$\mathbf{P}_{\mathrm{T+L}} = \mathbf{P}_{\mathrm{Cu}} + \mathbf{P}_{\mathrm{Ferr}} \tag{16}$$

The first term in (16) is expressed to depend on commonmode resistance  $R_{cm}$  (equal to "phase" resistance  $R_{ph}$ ), by splitting the DC ad PWM contributions due to consistent impact of skin effects:

$$P_{Cu} = \frac{R_{cm}|_{DC}}{2} \cdot I_{L}^{2} + \frac{R_{cm}|_{PWM}}{2} (I_{Cin,rms})^{2}$$

(17)

Ferrite core losses are very low, however an accurate model (18) has been tested for the purpose, where  $k_{ferr}$  factor encloses ferrite properties, core mass and section.

$$P_{ferr} \cong k_{ferr} \cdot \frac{\left(\psi_{cm} + \psi_{dm}\right)_{pk}^{2.19}}{T_{SW}^{1.39}}$$

(18)

3)  $P_{HB}$  (total H-bridge IGBT and free-wheeling diode losses) is composed by conduction and switching losses. Conduction losses are generally depending on duty-cycle, however this is cancelled by identical ON voltage drops on IGBTs and diodes thanks to peculiar alternative operation [1]. The best match with test-bench measurements is achieved by "averaging" the two drop functions, as in (19), providing a very accurate conduction loss model (20):

$$\frac{\mathbf{v}_{CE,sat}(\mathbf{I}) + \mathbf{v}_{diode,forward}(\mathbf{I})}{2} \cong \mathbf{V}_{J} + \Delta \mathbf{V}_{R} \frac{\mathbf{I}}{\mathbf{I}_{tabel}}$$

(19)

$$\mathbf{P}_{\text{cond},\text{HB}} = 2 \cdot \left[ \mathbf{V}_{\text{J}} + \frac{\Delta \mathbf{V}_{\text{R}}}{\mathbf{I}_{\text{label},\text{HB}}} \left| \frac{\mathbf{I}_{\text{L}}}{2} \right| \cdot \left( 1 + \frac{\mathbf{a}_{\text{SW}}^2}{3} \right) \right] \cdot \left| \frac{\mathbf{I}_{\text{L}}}{2} \right|$$

(20)

Switching losses are quite complex. According to factory specifications, (21) is a simple while effective model, being  $\Delta t_{\text{comm}}$  a switching time "constant" (temperature depending).

$$\mathbf{P}_{\mathrm{sw,HB}} \cong 2 \cdot \left\{ \frac{\mathbf{V}_{\mathrm{c}}}{\mathbf{T}_{\mathrm{SW}}} \cdot \frac{|\mathbf{I}_{\mathrm{L}}|}{2} \cdot \Delta \mathbf{t}_{\mathrm{comm}} \right\}$$

(21)

4)  $P_{aux}$  includes control board and auxiliaries power loss, and it's fairly constant (~27W). All the inherent devices are supplied from V<sub>c</sub> by a small DC/DC converter.

## IV. TEST BENCH CONCEPT AND DESIGN.

## A. Power loss dependence on input current.

According to previous equations (11 to 19), if  $V_c$  and D are constant values, converter's power losses do not depend on input current sign, but only on its module. This is the theoretical basis for the adopted test method.

## B. Basic concept of operation.

The alternative operation at constant input voltage and current module and set output voltage is provided by a proportional-integrative voltage regulator. Its output is PW modulated to generate a variable duty rectangular wave, whose (constant) module is representing the current reference for power loss evaluation. The rectangular reference period is short to limit the i/o capacitor banks voltage ripples, while it has to be very large with respect to current loop time response (~200 $\mu$ s), in order to fairly disregard the effect of current inversion transients (and related "error" of input current with respect to the reference constant value). The suitable rectangular reference frequency is set to 65Hz, low enough also to minimize skin effects (extra losses) of such a rectangular-wave operating cycle.

## C. Basic test-bench composition.

The proposed test bench is depicted in Fig.5, basically comprising the converter under test and a pair of outer large capacitor banks (input and output sides of the converter). Designed capacitance values are large enough to keep D as constant as practical ( $\Delta D < 8\%$ ) during the alternating 65Hz operation, holding validity of the power loss analytical models described in section III.

The two high-frequency filter inductances ( $L_{if}$  and  $L_{of}$  in series with i/o capacitor banks in fig.5), are disposed not to affect the inner capacitor ripples at switching frequency (PWM current ripples either on  $i_{Cin}$  or  $i_C$ ). By this way, during the tests,  $i_{Cin}$  and  $i_C$  ESR losses are equivalent to ordinary steady-state DC/DC operating conditions.

The input voltage (Supply stage in Fig.5) is obtained by a small power voltage generator, followed by suitable CL filter (32mH-5mF) to counteract with input voltage ripple effects.

## D. I/O capacitor banks and filters.

Each bank is constituted by smaller groups, adopting short, large section wires  $(16 \div 75 \text{ mm}^2)$  to minimize any additional resistance. In addition, due to large data-sheet tolerances both on capacitance and ESR values, these ones have been measured by an AC 50Hz volt-amperometric test with 50V DC bias (useful to 65Hz validation). Calculated capacitance and ESR values are 66.6[mF],  $3.6[m\Omega]$  for input bank, and 40.4[mF], 6.3[m $\Omega$ ] for output bank. The respective measured values are: 71.5[mF], 3.9[m $\Omega$ ] at input; 44.0[mF], 5.5[m $\Omega$ ] at output.

According to basic principle, inner capacitor currents (i<sub>Cin</sub> and  $i_{\rm C}$  in fig.5) should contain only high frequency components (PWM modulation ripples), leaving to outer capacitor banks (i<sub>CiB</sub> and i<sub>CoB</sub> in fig.5) the low frequency ones (65Hz). This is made practically possible for loss estimation by the two filter inductors ( $L_{if}$  and  $L_{of}$  in fig.5), reducing the 20kHz currents flow towards outer capacitor banks, without rising the banks impedance up at 65Hz harmonics. Some oscillations are anyway arising in response to power inversions as shown in the followings.

## E. Power losses estimation.

Total test bench power loss, at set working point, comes from DC power supply stage measurement:

$$\mathbf{P}_{\mathbf{SS}} = \mathbf{V}_{\mathrm{in}} \times \mathbf{I}_{\mathbf{SS}} \tag{22}$$

where both factors are directly measured by real mean value voltmeters (Iss is measured through R<sub>shunt</sub> shown in fig.5). Obviously, effects and losses of the extra i/o large capacitor banks should be carefully evaluated.

Measured power (22) is composed as in (25):

$$\mathbf{P}_{SS} = \mathbf{P}_{conv} + \mathbf{P}_{CiB} + \mathbf{P}_{CoB}$$

(25)

where:

$$\mathbf{P}_{\mathbf{CiB}} = \mathbf{R}_{\mathbf{CiB}} \cdot \mathbf{I}_{\mathbf{CiB,rms}}^2 \tag{26}$$

$$\mathbf{P}_{\text{CoB}} = \mathbf{R}_{\text{CiB}} \cdot \mathbf{I}_{\text{CoB,rms}}^2 \tag{27}$$

As assumed, I<sub>CiB</sub> is a 65Hz rectangular shaped current with constant module:

$$\mathbf{I}_{\mathbf{CiB},\mathbf{rms}} \cong \left| \mathbf{I}_{\mathbf{L}} \right| \tag{29}$$

Considering a constant i/o voltage ratio, during the test at a set working point, output capacitor bank rms current is very close to (30):

$$\mathbf{I}_{\mathbf{CoB},\mathbf{rms}} \cong |\mathbf{I}_{\mathbf{L}}| \cdot \frac{\mathbf{V}_{\mathrm{in}}}{\mathbf{V}_{\mathrm{c}}}$$

(30)

Finally, quasi-direct measurement of convertor's losses is: . 2

$$\mathbf{P}_{conv} = \mathbf{P}_{SS} - \mathbf{I}_{L}^{2} \cdot \left[ \mathbf{R}_{CiB} + \left( \frac{\mathbf{V}_{in}}{\mathbf{V}_{c}} \right)^{2} \cdot \mathbf{R}_{CoB} \right]$$

(31)

.

where the "error" term is as low as practical by design.

## **V. EXPERIMENTAL RESULTS**

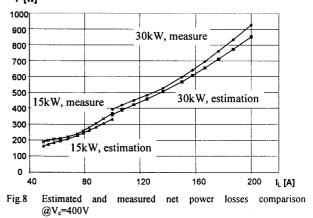

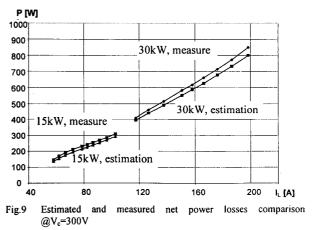

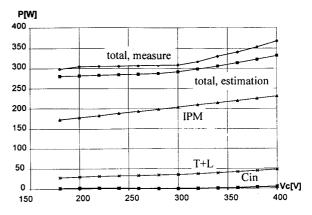

A series of efficiency tests has been carried out, covering the whole V<sub>in</sub>/V<sub>c</sub> ratio operative range according to TBL.II. By constant V<sub>c</sub> values (300V and 400V), two different constant-power tests (15-30kW) are provided. A further test, at rated power, refers to low constant input voltage  $(V_{in}=150V, |I_L|=100A)$  and variable output voltage.

TABLE II - DEFINITION OF EFFICIENCY TEST CONDITIONS.

| Test<br>group |                          | P<br>[kW] | V <sub>IN</sub><br>[V] | V.<br>[V] | I <sub>L</sub>  <br>[A] |

|---------------|--------------------------|-----------|------------------------|-----------|-------------------------|

| 1             | CONSTANT V <sub>C</sub>  | 15<br>30  | 150÷300                | 400       | 50÷100<br>100÷200       |

| 2             | constant V <sub>c</sub>  | 15<br>30  | 150÷260                | 300       | 50÷100<br>100÷200       |

| 3             | CONSTANT V <sub>in</sub> | 15        | 150                    | 170÷400   | 100                     |

## A. Converted current waveform.

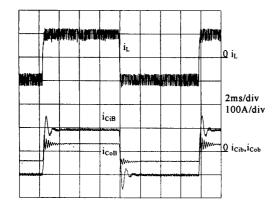

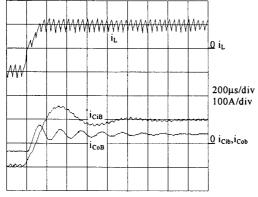

According to basical assessment, the converted input current is as close as possible to a rectangular wave. In Figs.6,7 the measured currents behavior is shown. Input and output capacitor banks currents are ripple-free while oscillating at every step. This is due to designed inductors filtering effects (Lif and Lof in Fig.5) oscillating with inner capacitors (Cin and C in Fig.5). In Fig.7 the quick response (~200µs) to one of the 65Hz alternated steps is evidenced.

Fig. 5 Test bench electrical-topological scheme.

Fig. 6 Input converted current and i/o capacitor banks currents alternated behavior @ 65Hz operation;  $V_{in}$ =150V,  $V_c$ =400,  $|I_L|$ =100A.

Fig. 7 Input converted current and i/o capacitor banks currents: responses to an inversion transient;  $V_{in}$ =150V,  $V_c$ =400,  $|I_L|$ =100A.

## B. Measured losses. Mathematical model validation.

## TABLE III - SUMMARY OF LOSSES MODEL PARAMETERS

|                    | f <sub>sw_</sub>                               |                      | [kHz]                                       | 10.124 |

|--------------------|------------------------------------------------|----------------------|---------------------------------------------|--------|

| IPM                | Vj                                             |                      | [V]                                         | 0.9    |

| $(I_{label}=200A)$ | $\Delta V_R$                                   | Ձ <sub>j</sub> ≅75°C | [V]                                         | 1.4    |

|                    | $\Delta t_{comm}$                              |                      | [ns]                                        | 260    |

|                    | L <sub>II</sub>                                |                      | [µH]                                        | 38     |

| T+L                | $R_{cm} _{DC}$<br>$R_{cm} _{PWM}/R_{cm} _{DC}$ |                      | [mΩ]                                        |        |

| reactor            |                                                |                      |                                             | 13.5   |

|                    | k <sub>ferr</sub>                              |                      | [W·s <sup>1.39</sup> mWb <sup>-2.29</sup> ] | 40.8   |

| Inner              | R <sub>Cin</sub>                               |                      | [mΩ]                                        | 25.0   |

| capacitors         | R <sub>C</sub>                                 | •                    | [mΩ]                                        | 2.2    |

| Outer              | R <sub>CiB</sub>                               |                      | [mΩ]                                        | 3.9    |

| capacitors         | R <sub>CoB</sub>                               |                      | [mΩ]                                        | 5.5    |

| Auxiliaries        | P <sub>aux</sub>                               |                      | [W]                                         | 27     |

Referring to parameter values reported in TBL.III, the comparison between total measured and estimated losses is here reported. Figs.8,9 report the constant output voltage

tests (V<sub>c</sub>=300V and 400V), while Fig.10 reports the constant input voltage test (V<sub>in</sub>=150V). All the reported plots refer to net measured losses, by 10 seconds operation at each working point, trying to operate IGBTs and diodes @75°C, by varying the initial heatsink temperature inversely with power. The reported power values come from the difference between P<sub>SS</sub> (22) and measured auxiliaries term P<sub>aux</sub> (=27W). **P**[W]

Fig.10 Measured and estimated power loss comparison and main inner estimated terms ( $P_C$  fairly null) @V<sub>in</sub>=150V, |I\_L|=100A.

The graphical comparison between Figs.8,9.10. shows a general underestimation trend of the losses model. The maximum absolute difference between model and measure is ~75W (on >900W measured losses  $@V_c=400V$ ,  $V_{in}=150V$ ,  $I_1 = 150A$ , Fig.8), while the relative estimation error is always under 10%. A first point of difference is evidenced by Figs.8,9, in which the difference between curve pairs generally grows up with converted input current module quite quadratically. This is a "resistive-equivalent" effect, due to an underestimation of rms current terms of loss (partially related to 65Hz skin effects). As a second point, a duty-cycle dependent discontinuous term of error is evidenced by Figs.8,10, with a minimum corresponding to D=1/2. The error shape is someway linked to common-mode flux ripple amplitude (11), reported as a function of D in Fig.4 (corresponding to underestimation of PWM skin effects). The comparison between Figs.8 and 9, clearly shows a general growth of the underestimation with  $V_c$  (300V in Fig.9, 400V in Fig.8) at set D value. This, accordingly to (11), would be a confirmation of the estimation error related to flux-ripple.

### D. Model refinement.

Looking back to loss terms neglected in par.III analysis, other two terms depending on current-module can be found. The first term is due to the damping of the oscillating behavior evidenced by Figs.6,7 (estimated losses ~25W @) $|I_L|=200A$ ). A second analogous term refers to a further contribution to switching losses, due to stray commutation inductance on the dc-link connection between "C" and the IPM. Suitable small 100nF capacitor is locally mounted on IPM, resulting on 1.4MHz oscillations and estimated 130nH stray inductances. From measured transient overshoot value (~80% of switched current), the related loss term is ~20W @) $|I_L|=200A$ . In both cases, these power losses are function of  $|I_L|^2$ , proportional to stored inductive energies.

Differing from previous terms, the effective commonmode ripple resistance, as defined by (17), should be upgraded with respect to TBL.III calculation @20kHz.

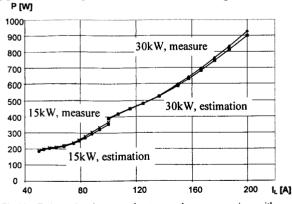

Fig.11 Estimated and measured net power losses comparison with estimation corrective terms  $@V_c=400V$

Furthermore, common-mode flux path in air and related eddy currents on all conductors, heatsink and convertor's box should be also estimated. These losses can be equivalently estimated by increasing the skin effect on the windings.

By adding these three terms, Fig.11 shows the comparison analogously to Fig.8. The model accuracy, still slightly defecting, has become practically perfect. The added terms refer to:

- two terms in the form  $K I_L^2$ , due to inductive oscillating losses, where K factors suitably summarize inductance values, current steps and overshoots, respective frequency;

- 3 times the common-mode PWM resistance reported in TBL.III.

The maximum estimation error is then reduced to  $\sim 25W$  (on 900W measured losses).

## E. Convertor's losses summary.

In all the effected tests, measured power losses are fairly under 1kW level. By subtracting from measured losses outer capacitor banks contributions, both ESR losses [ $P_{CiB}$  and  $P_{CoB}$ defined by (26),(27)] and KI<sub>L</sub><sup>2</sup> term due to filter inductances, an exact estimation of power convertor's losses is given. TBL.IV reports net convertor's efficiency, referring to rated and overload converted power (15,30kW @V<sub>c</sub>=400V).

TABLE IV - NET CONVERTOR'S EFFICIENCY  $@V_c=400V$

| Converted Power<br>[kW] | I <sub>L</sub>  <br>[A] | Net Power Losses<br>[W] | η          |

|-------------------------|-------------------------|-------------------------|------------|

| 15                      | 50÷100                  | 170÷315                 | 0979÷0.989 |

| 30                      | 100+200                 | 266÷654                 | 0978÷0.991 |

## VI. CONCLUSIONS.

The efficiency of a novel DC-DC three-level boost power converter has been investigated, already designed to adapt the battery voltage to PWM VSI in EV AC motor drives.

Due to very high efficiency, a new measurement method has been proposed, based on suitable alternating power flow between outer large capacitor banks.

An accurate analysis of power loss terms and model has been presented, in order to validate either the proposed measurement or the novel DC/DC convertor loss model.

The obtained results are completely satisfactory, demonstrating at the same time the very high efficiency of the novel DC-DC three-level boost converter, the accuracy of the power loss model and the effectiveness of the proposed measurement method.

## REFERENCES

[1] A. Fratta, P. Guglielmi, F. Villata, A. Vagati, "Efficiency and costeffectiveness of AC drives for electric vehicles improved by a novel boost DC-DC conversion structure", 1998 IEEE Workshop on Power Electronics in Transportation (WPET 98), pp. 11-19.

[2] A. Fratta, P. Guglielmi, G.M. Pellegrino, F. Villata, "Efficient Modulation Tecnique and NL Control of H-bridge Boost Converters for Battery-Supplied AC Motor Drives", 1999 IEEE International Symposium on Industrial Electronics (ISIE 99), pp. 806-812.

on Industrial Electronics (ISIE 99), pp. 806-812. [3] A.Vagati, A.Fratta, P.Guglielmi, G.Franchi, F.Villata, "Comparison of AC Motor Based Drives for Electric Vehicle Application", 1999 Power Conversion & Intelligent motion (PCIM '99), pp. 173-182.