### **Doctoral Dissertation**

Doctoral Program in Electronics and Communications Engineering  $(28^{th}\text{cycle})$

# High-Level Synthesis Based VLSI Architectures for Video Coding

By

# Waqar Ahmad

\*\*\*\*\*

### **Supervisor(s):**

Prof. Guido Masera, Supervisor Prof. Maurizio Martina, Co-Supervisor

## **Doctoral Examination Committee:**

Prof. Matteo Cesana, Politecnico di Milano Prof. Sergio Saponara, Università di Pisa Prof. Enrico Magli, Politecnico di Torino

Politecnico di Torino 2017

## **Declaration**

Waqar Ahmad 2017

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

| I would like to dedicate this | thesis to my loving part<br>lovely son–Mujtaba | ents, my wife–Sania and m |

|-------------------------------|------------------------------------------------|---------------------------|

|                               |                                                |                           |

|                               |                                                |                           |

|                               |                                                |                           |

|                               |                                                |                           |

|                               |                                                |                           |

|                               |                                                |                           |

|                               |                                                |                           |

## Acknowledgements

I wish to express my sincere thanks to Prof. Guido Masera for his support and advice. I would like to express my very great appreciation for his support and advice, his visionary project ideas, and for providing such a great research environment. I would like to express my deep gratitude to Prof. Maurizio Martina, who served as PhD co-supervisor. His constant support, his enthusiastic encouragement and exciting research ideas and his constructive criticism have been an invaluable help for the success of this thesis. Also, I am particularly grateful for the technical and non-technical help given by my supervisor Prof. Guido Masera and Prof. Maurizio Martina. Furthermore, I want to thank all my colleagues from VLSI Lab. Polito for an excellent work environment and a great time. I would further like to thank the support and administrative team at VLSI Lab, who are doing a perfect job such that PhD students can focus on their research work. Finally, I wish to thank my wife Sania for her non-technical contributions to this work and for letting me follow my passion, my lovely son Mujtaba, my parents for their constant support in what I do, and my family and friends for reminding me of life outside my office.

## **Abstract**

High Efficiency Video Coding (HEVC) is state-of-the-art video coding standard. Emerging applications like free-viewpoint video, 360degree video, augmented reality, 3D movies etc. require standardized extensions of HEVC. The standardized extensions of HEVC include HEVC Scalable Video Coding (SHVC), HEVC Multiview Video Coding (MV-HEVC), MV-HEVC+ Depth (3D-HEVC) and HEVC Screen Content Coding. 3D-HEVC is used for applications like view synthesis generation, free-viewpoint video. Coding and transmission of depth maps in 3D-HEVC is used for the virtual view synthesis by the algorithms like Depth Image Based Rendering (DIBR). As first step, we performed the profiling of the 3D-HEVC standard. Computational intensive parts of the standard are identified for the efficient hardware implementation. One of the computational intensive part of the 3D-HEVC, HEVC and H.264/AVC is the Interpolation Filtering used for Fractional Motion Estimation (FME). The hardware implementation of the interpolation filtering is carried out using High-Level Synthesis (HLS) tools. Xilinx Vivado Design Suite is used for the HLS implementation of the interpolation filters of HEVC and H.264/AVC. The complexity of the digital systems is greatly increased. High-Level Synthesis is the methodology which offers great benefits such as late architectural or functional changes without time consuming in rewriting of RTL-code, algorithms can be tested and evaluated early in the design cycle and development of accurate models against which the final hardware can be verified.

# **Contents**

| Li | st of l | Figures                                         | X    |

|----|---------|-------------------------------------------------|------|

| Li | st of ' | Tables                                          | xii  |

| No | omen    | clature                                         | xiii |

| 1  | Intr    | roduction                                       | 1    |

|    | 1.1     | Introduction to Video Coding                    | 1    |

|    | 1.2     | High Level Synthesis Based Video Coding         | 3    |

|    | 1.3     | Problem Statement                               | 6    |

|    | 1.4     | Contribution                                    | 7    |

|    | 1.5     | Organization of the Thesis                      | 7    |

| 2  | Stat    | e-of-the-art Video Coding Standards             | 9    |

|    | 2.1     | History of The Standardization Process          | 10   |

|    | 2.2     | H.264/AVC Video Coding                          | 11   |

|    | 2.3     | High Efficiency Video Coding (HEVC)             | 14   |

|    |         | 2.3.1 HEVC Feature Highlights and Coding Design | 14   |

|    | 2.4     | Standardized Extensions of HEVC                 | 17   |

|    |         | 2.4.1 Range Extensions                          | 17   |

|    |         | 2.4.2 Scalability Extensions                    | 18   |

| vii |

|-----|

|     |

|   |      | 2.4.3   | 3D Video Extensions                                  | 18 |

|---|------|---------|------------------------------------------------------|----|

|   | 2.5  | 3D Hi   | gh Efficiency Video Coding (3D-HEVC)                 | 20 |

|   |      | 2.5.1   | Neighbouring Block-Based Disparity Vector Derivation | 20 |

|   |      | 2.5.2   | Inter-View Motion Prediction                         | 20 |

|   |      | 2.5.3   | Inter-View Residual Prediction                       | 22 |

|   |      | 2.5.4   | Illumination Compensation                            | 23 |

|   |      | 2.5.5   | Multiview HEVC With Depth                            | 24 |

| 3 | Cod  | ing Cor | mplexity Analysis of 3D-HEVC                         | 27 |

|   | 3.1  | 3D-HE   | EVC Tools                                            | 28 |

|   |      | 3.1.1   | Dependent View Coding                                | 28 |

|   |      | 3.1.2   | Depth Maps Coding                                    | 30 |

|   |      | 3.1.3   | Encoder Control                                      | 31 |

|   | 3.2  | Compl   | lexity Analysis                                      | 31 |

|   |      | 3.2.1   | Profiling of 3D-HTM Encoder                          | 32 |

|   |      | 3.2.2   | Profiling of 3D-HTM Decoder                          | 34 |

|   | 3.3  | Identif | ned Computational Complex Tools                      | 35 |

| 4 | Higl | h-Level | Synthesis                                            | 37 |

|   | 4.1  | What i  | s High-Level Synthesis?                              | 37 |

|   | 4.2  | Overvi  | iew of High-Level Synthesis Tools                    | 39 |

|   |      | 4.2.1   | Academic HLS Tools                                   | 39 |

|   |      | 4.2.2   | Other HLS Tools                                      | 40 |

|   | 4.3  | HLS C   | Optimizations                                        | 43 |

|   |      | 4.3.1   | Operation Chaining                                   | 43 |

|   |      | 4.3.2   | Bitwidth Optimization                                | 43 |

|   |      | 4.3.3   | Memory Space Allocation                              | 43 |

viii Contents

|   |     | 4.3.4    | Loop Optimizations                                    | 44 |

|---|-----|----------|-------------------------------------------------------|----|

|   |     | 4.3.5    | Hardware Resource Library                             | 44 |

|   |     | 4.3.6    | Speculation and Code Motion                           | 44 |

|   |     | 4.3.7    | Exploiting Spatial Parallelism                        | 45 |

|   |     | 4.3.8    | If-Conversion                                         | 45 |

|   | 4.4 | Xilinx   | Vivado Design Suite                                   | 45 |

|   |     | 4.4.1    | Benefits of High-Level Synthesis                      | 46 |

|   |     | 4.4.2    | Basics of High-Level Synthesis                        | 46 |

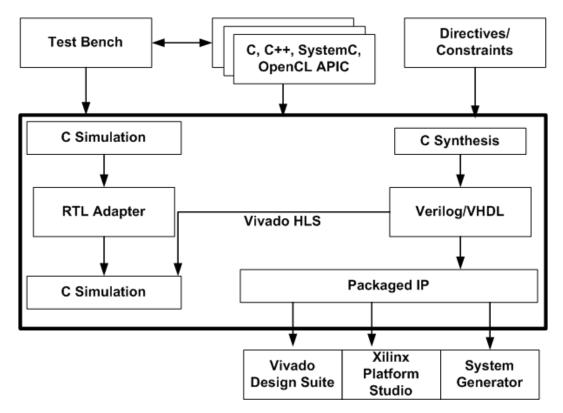

|   |     | 4.4.3    | Understanding the design flow of Vivado HLS           | 48 |

| 5 | HLS | S Based  | FPGA Implementation of Interpolation Filters          | 53 |

|   | 5.1 | Fractio  | onal Motion Estimation                                | 53 |

|   | 5.2 | H.264/   | 'AVC Sub-pixel Interpolation                          | 55 |

|   |     | 5.2.1    | HLS based FPGA Implementation                         | 57 |

|   | 5.3 | HEVC     | Sub-pixel Interpolation                               | 62 |

|   |     | 5.3.1    | HEVC Luma Sub-pixel Interpolation                     | 63 |

|   |     | 5.3.2    | HLS based FPGA Implementation of Luma Interpolation   | 64 |

|   |     | 5.3.3    | HEVC Chroma Sub-pixel Interpolation                   | 67 |

|   |     | 5.3.4    | HLS based FPGA Implementation of Chroma Interpolation | 70 |

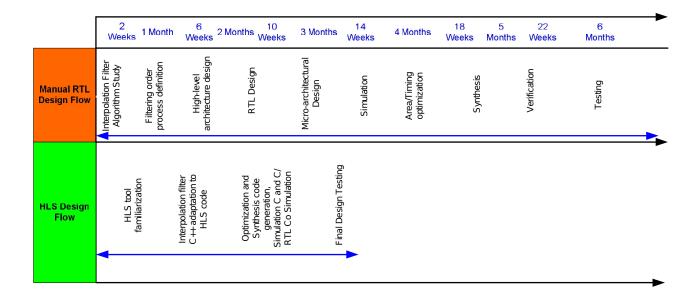

|   |     | 5.3.5    | Summary: HLS vs manual RTL Implementations            | 73 |

|   |     | 5.3.6    | Design Time Reduction                                 | 74 |

| 6 | Con | clusions | s and Future Work                                     | 76 |

|   | 6.1 | Conclu   | asions                                                | 76 |

|   |     | 6.1.1    | Hardware Implementation: HLS vs Manual RTL            | 76 |

|   | 6.2 | Future   | Work                                                  | 77 |

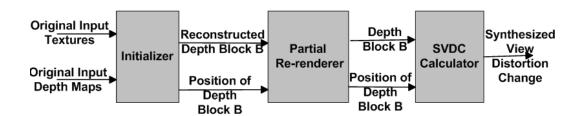

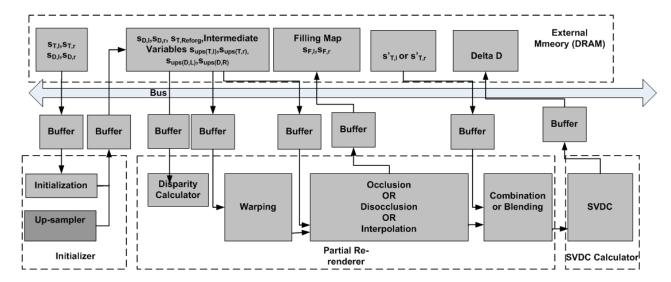

|   |     | 6.2.1    | 3D-HEVC Renderer Model                                | 77 |

| Contents   |                                                | ix |

|------------|------------------------------------------------|----|

| 6.2.2      | Hardware complexity analysis of Renderer Model | 80 |

| References |                                                | 85 |

# **List of Figures**

| 1.1  | Postcard from 1910                                             | 2  |

|------|----------------------------------------------------------------|----|

| 2.1  | Video coding standardization scope                             | 10 |

| 2.2  | H.264/AVC macroblock basic coding structure                    | 11 |

| 2.3  | HEVC video encoder                                             | 15 |

| 2.4  | 3-view case: Prediction structure of Multiview HEVC            | 19 |

| 2.5  | HEVC Inter-view motion prediction                              | 19 |

| 2.6  | Spatial Neighbouring blocks for NBDV                           | 21 |

| 2.7  | 3D-HEVC temporal motion prediction                             | 22 |

| 2.8  | 3D-HEVC Temporal motion vector prediction                      | 23 |

| 2.9  | Illumination Compensation                                      | 24 |

| 2.10 | Partitioning of depth PU                                       | 25 |

| 2.11 | Contour partition of a block                                   | 26 |

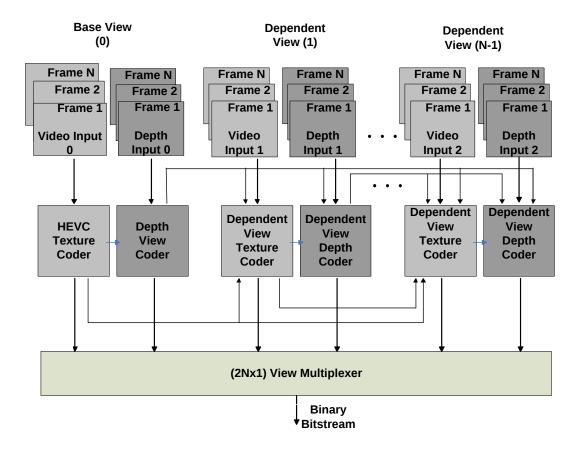

| 3.1  | Block Diagram of basic structure of 3D-HEVC                    | 29 |

| 3.2  | Block Level Representation of 3D Tools of HEVC                 | 30 |

| 3.3  | Computationally Complex parts of 3D-HEVC                       | 36 |

| 4.1  | HLS Tools Classification                                       | 40 |

| 4.2  | Vivado HLS Design Flow                                         | 49 |

| 5.1  | Pixel positions for Integer, Luma half and Luma quarter pixels | 57 |

List of Figures xi

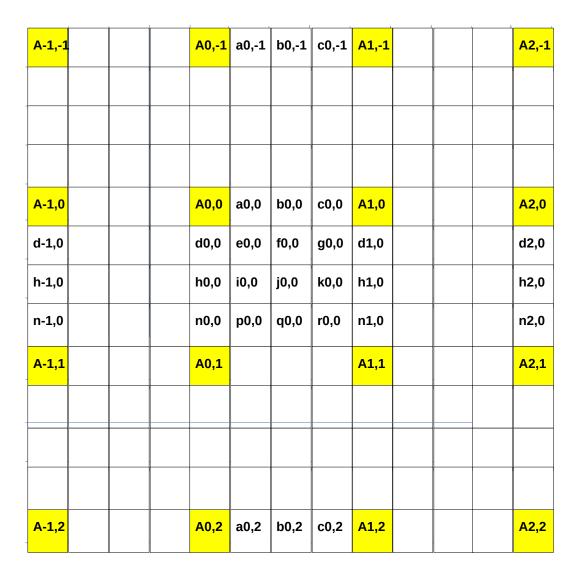

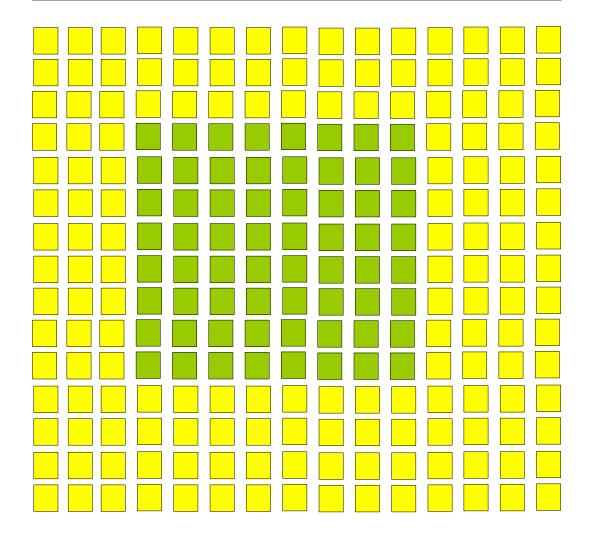

| 5.2 | 13x13 Pixel Grid for H.264/AVC Luma Interpolation of 8x8 block (where green colour represents the integer pixels block to be interpolated and yellow colour represents the required integer pixels padded to the block to support interpolation) | 58 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

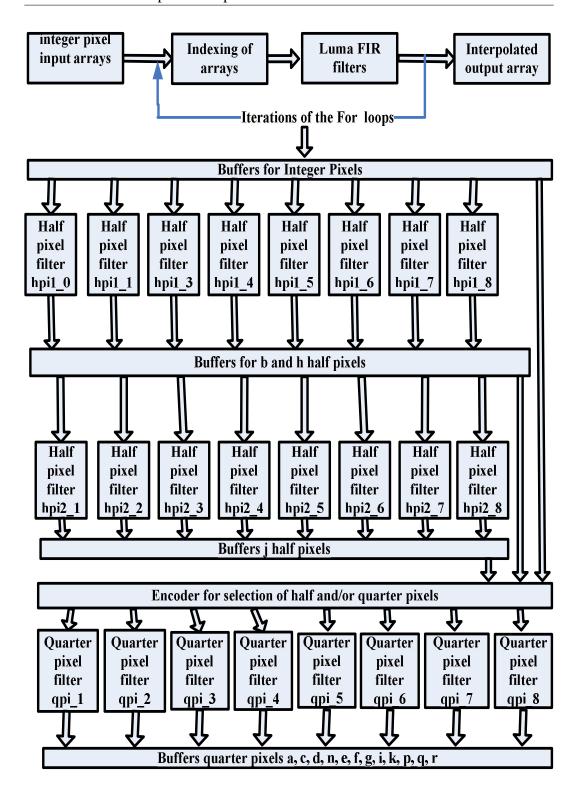

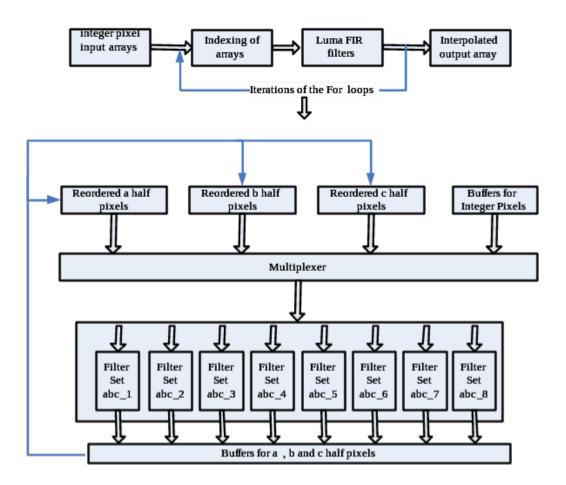

| 5.3 | HLS implementation of H.264/AVC Luma Sub-pixel                                                                                                                                                                                                   | 59 |

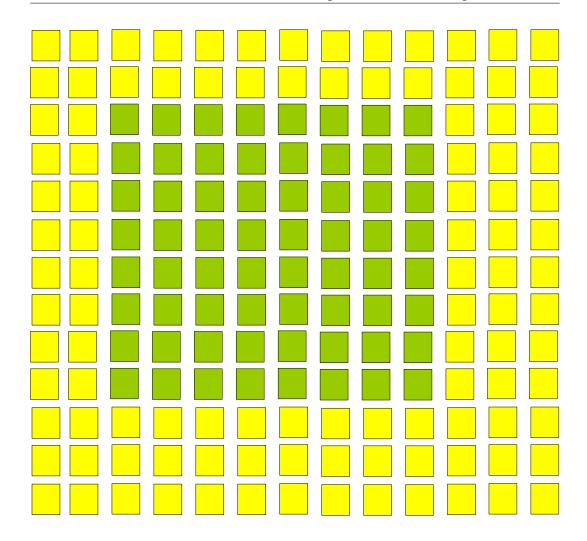

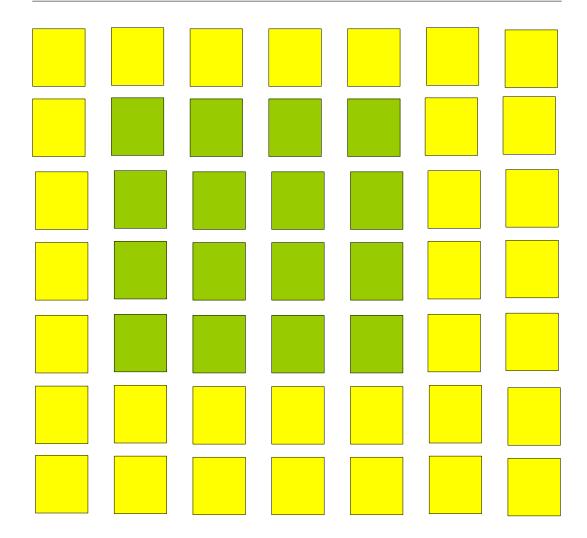

| 5.4 | 15x15 Pixel Grid for HEVC Luma Interpolation of 8x8 block (where green colour represents the integer pixels block to be interpolated and yellow colour represents the required integer pixels padded to the block to support interpolation)      | 65 |

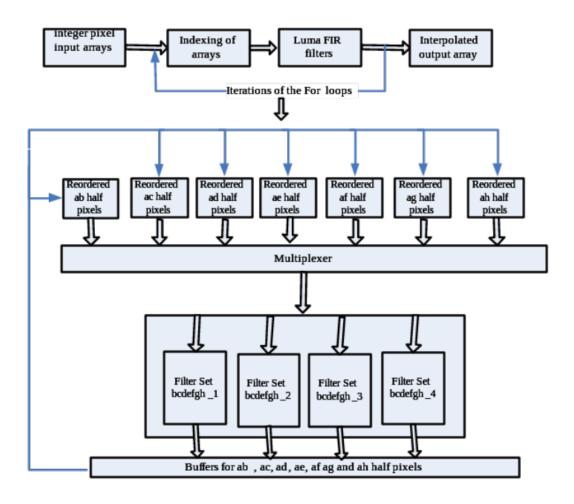

| 5.5 | HLS implementation of HEVC Luma Sub-pixel                                                                                                                                                                                                        | 66 |

| 5.6 | Chroma sample grid for eight sample interpolation                                                                                                                                                                                                | 69 |

| 5.7 | 7x7 Pixel Grid for HEVC chroma Interpolation of 4x4 block (where green colour represents the integer pixels block to be interpolated and yellow colour represents the required integer pixels padded to the block to support interpolation)      | 71 |

| 5.8 | HLS implementation of HEVC Chroma Sub-pixel                                                                                                                                                                                                      | 72 |

| 5.9 | Design time comparison HLS vs Manual RTL Design                                                                                                                                                                                                  | 75 |

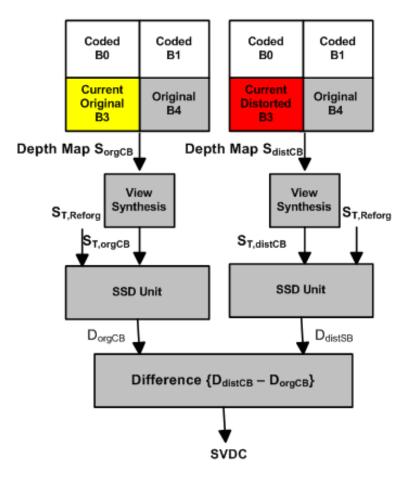

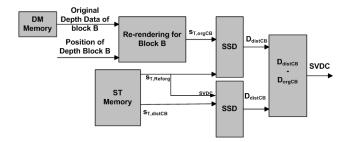

| 6.1 | Block Diagram of SVDC                                                                                                                                                                                                                            | 79 |

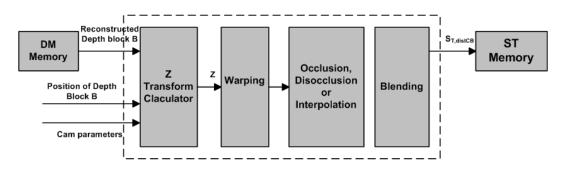

| 6.2 | Block Diagram of Renderer Model                                                                                                                                                                                                                  | 79 |

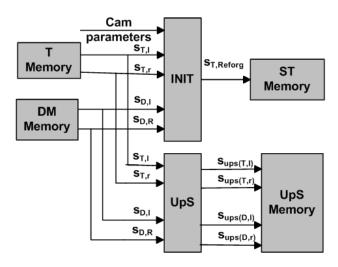

| 6.3 | High Level Hardware Architecture of Renderer Model                                                                                                                                                                                               | 80 |

| 6.4 | Initializer Hardware Diagram.                                                                                                                                                                                                                    | 81 |

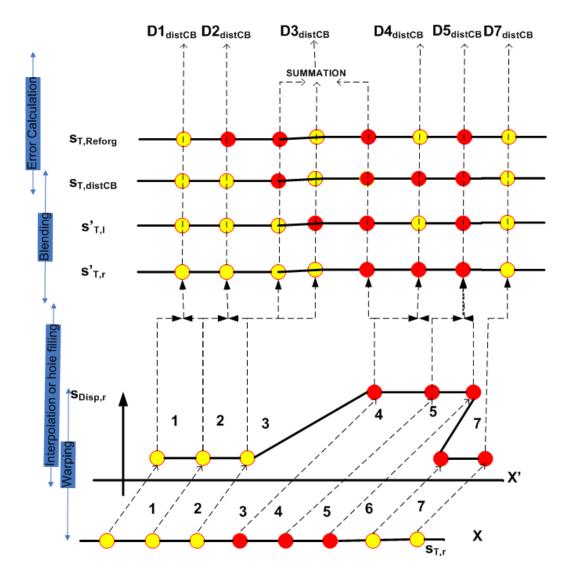

| 6.5 | Partial re-rendering algorithm flow diagram                                                                                                                                                                                                      | 82 |

| 6.6 | Re-renderer Hardware Diagram                                                                                                                                                                                                                     | 83 |

| 67  | SVDC Calculator Hardware Diagram                                                                                                                                                                                                                 | 84 |

# **List of Tables**

| 3.1  | Class-wise time distribution 3D-HEVC vs HEVC Encoder                                                                                  | 33 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Class-wise time distribution 3D-HEVC vs HEVC Decoder                                                                                  | 35 |

| 5.1  | Resources required for HLS implementation of H.264/AVC Luma Sub-pixel Interpolation using multipliers for multiplication              | 61 |

| 5.2  | Resources required for HLS implementation of H.264/AVC Luma Sub-pixel Interpolation using add and shift operations for multiplication | 61 |

| 5.3  | H.264/AVC Luma Sub-pixel HLS vs Manual RTL Implementations.                                                                           | 62 |

| 5.4  | H.264/AVC vs HEVC Luma Sub-pixel HLS implementation                                                                                   | 62 |

| 5.5  | Resources required for HLS based HEVC luma implementation using multipliers for multiplication                                        | 67 |

| 5.6  | Resources required for HLS based HEVC luma implementation using add and shift operations for multiplication                           | 67 |

| 5.7  | HEVC luma sub-pixel HLS vs manual RTL Implementations                                                                                 | 67 |

| 5.8  | Resources required for HLS based HEVC chroma implementation using multipliers for multiplication                                      | 72 |

| 5.9  | Resources required for HLS based HEVC chroma implementation using add and shift operations for multiplication                         | 72 |

| 5.10 | HEVC Chroma sub-pixel HLS vs manual RTL Implementations                                                                               | 73 |

# **Nomenclature**

## **Acronyms / Abbreviations**

|  | 3D-1 | HEVC | 3D | High | Efficiency | Video | Coding |

|--|------|------|----|------|------------|-------|--------|

|--|------|------|----|------|------------|-------|--------|

AVC Advanced Video Coding

CPU Central Processing Unit

DSL Digital Subscriber Line

DVD Digital Versatile Disk

FF Flip-Flop

FPGA Field-Programmable Gate Array

FPS Frames Per Second

*HD* High Definition

HDL Hardware Description Language

HEVC High Efficiency Video Coding

HLL High-Level Language

HLS High-Level Synthesis

IEC International Electrotechnical Commission

ISDN Integrated Services Digital Network

ISO International Organization for Standardization

**xiv** Nomenclature

ITU-T International Telecommunication Union-Telecommunication

JTC Joint Technical Committee

JVT Joint Video Team

LAN Local Area Network

LUT Lookup Table

MB Macro Block

MMS Multimedia Messaging Services

MPEG Moving Picture Experts Group

PSTN Public Switched Telephone Network

RTL Register Transfer Level

SD Standard Definition

SoC System on Chip

TV Television

UMTS Universal Mobile Telecommunications System

VCEG Video Coding Experts Group

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

VoD Video-on-Demand

# Chapter 1

# Introduction

This chapter starts with an introduction to the fundamentals of video coding through an historical perspective. Following this, the chapter surveys High-Level Synthesis (HLS) based video coding. Subsequently, we propose an alternative methodology for VLSI implementation of video coding algorithms and introduce its main components, i.e., the HLS based simulation, verification, optimization and synthesis. We conclude with an overview of the individual chapters, indicating the relevant contributions.

## 1.1 Introduction to Video Coding

The process of compressing and decompressing video is called video coding or video compression. Moving digital images are digitally compressed by video compression algorithms. There is a long list of the video coding applications, some applications of the video compression include TV, phones, laptops, cameras etc. Where there is a digital video content, there should be video compression behind that content. For the digital video large amount of the storage capacity is required if the video is in its original form i.e. uncompressed. As an example, uncompressed 1080p high definition (HD) video at 24 frames/second requires 806 GB of storage for a video of 1.5 hours duration with bit-rate requirement of 1.2 Gbits/second. That is why, for storage and transmission purposes of the digital video, video compression is a must, otherwise it will be impossible to store and process the uncompressed video contents for applications of today's era. Decompression of compressed video is required for displaying the video contents to the consumers.

2 Introduction

Sending visual images to a remote location has captured the human imagination for more than a century Figure 1.1. The invention of television in 1926 by the Scotsman John Logie Baird [1] led to the realisation of this concept over analogue communication channels. Even analogue TV systems made use of compression or information reduction to fit higher resolution visual images into limited transmission bandwidths [2].

Fig. 1.1 "in the year 2000", postcard from 1910

The emergence of mass market digital video in the 1990s was made possible by compression techniques that had been developed during the preceding decades. Even though the earliest videophones [3] and consumer digital video formats were limited to very low resolution images (352x288 pixels or smaller), the amount of information required to store and transmit moving video was too great for the available transmission channels and storage media. Video coding or compression was an integral part of these early digital applications and it has remained central to each further development in video technology since 1990 [4].

By the early 1990s, many of the key concepts required for efficient video compression had been developed. During the 1970s, industry experts recognised that video compression had the potential to revolutionise the television industry. Efficient compression would make it possible to transmit many more digital channels in the bandwidth occupied by the older analogue TV channels.

Present-day video coding standards [5]–[6] and products share the following features:

- 1. Motion compensated prediction [7].

- 2. Subtraction of a motion compensated prediction for residual unit creation (e.g. a residual MB).

- 3. Block transform and quantization to form blocks of quantized coefficients.

## 1.2 High Level Synthesis Based Video Coding

Video compression technology can be seen in a variety of applications ranging from mobile phones to autonomous vehicles. Many video compression applications such as drones and autonomous vehicles requires real-time processing capability in order to communicate with the control unit for sending commands in real time. Besides real-time processing capability, it is crucial to keep the power consumption low in order to extend the battery life of not only mobile devices, but also drones and autonomous vehicles. Field Programmable Gate Arrays (FPGAs) are desired platforms that can provide high-performance and low-power solutions for real-time video processing. Increasing demands of multimedia applications and services has make up the need for embedded systems aiding ever-accelerating functionality and flexibility [8]. Evolution of video coding supporting new advanced coding tools and increased demand of multimedia contents make the embedded media processing systems difficult to design and implement, under shorter time-to-market restriction. Sate-of-the-art video coding standards i.e. HEVC [9] and H.264/AVC are good examples of complex multimedia system with low-power and typical performance embedded implementation requirements. Several works [10]–[11] has been proposed for the performance enhancement and complexity reduction of HEVC and H.264/AVC multimedia systems. As hardware designs typically are more time consuming than equivalent software designs. Due to difficult and time hungry process of manual RTL design, an alternative methodology for hardware implementations of complex system is High-Level Synthesis (HLS) based hardware implementation. Increased complexity of the digital systems [12], energy-efficient heterogeneous systems [13] for high-performance and shortening time-to-market, are the key factors for the popularity of the High-Level Synthesis (HLS) [14]. In HLS, hardware functionality is specified by using the software i.e. at a higher-level of abstraction. Moreover, field-programmable gate array (FPGA) design by HLS

4 Introduction

becomes interesting and has two fold advantage i.e. the hardware implementations in the target device can be easily replaced and refined at higher abstraction level.

Nowadays, heterogeneous-systems are being adopted as the energy-efficient, high-performance and high-throughput systems. The reason behind this is the impossibility of further clock frequency scaling. These systems consist mainly of two parts i.e., the application-specific integrated circuits (ASICs) [15] and the software processor [16]. Each part of the system is dedicated for a specific task. The design of these types of systems become very complex due to increase in the complexity of the systems. ASICs are the dedicated hardware components for the accelerated implementation of the computational complex parts for the system. As stated above, due to increase in the complexity of the systems, the design of these dedicated hardware also become complex and time-consuming. Hardware description languages (HDLs) [17] are used for the register transfer level (RTL) [18] implementation of these components. Cycle-by-cycle activity for RTL implementation of these components is specified, which is a low abstraction level. For such a low level of implementation, advanced expertise in hardware design are required, alongside being unmanageable to develop. The impact of these low-level implementation of complex systems increase the time-to-market by taking more design and development time.

High-level synthesis (HLS) and FPGAs in combination, is an intriguing solution to these problems of longer time-to-market and to realize these heterogeneous systems [19]. FPGAs are used for the configurable implementation of digital integrated circuits. Manufacturing cost is an important factor in the implementation of digital ICs. The use of FPGAs as reconfigurable hardware, help us the fast implementation and optimization by providing ability to reconfigure the integrated circuits, hence, removing the extra manufacturing cost. It allows the designer to re-implement modifications made to the design, by changing the HDL code description, re-synthesize and implement the design using same FPGA fabric by the help of implementation tools. Thus HLS based FPGA implementation of digital systems can be helpful in functional verification, possible hardware implementation and large design-space exploration of the systems. FPGA based implementation of user applications can be used an intermediate implementation before the ASICs and SoC implementation.

C, SystemC and C++ etc. are the High-level languages (HLLs) being used for the software programming and development. HLS tools take HLL as input and HDL

description (circuit specification) is generated automatically. This automatically generated circuit specification performs the same functionality as software specification. Since, the benefits of HLS i.e. to have a new fast hardware implementation just by changing the code in software, help software engineers with very little requirement of the hardware expertise. The benefits of the HLS to hardware engineers are the fast, rapid and high-level abstraction implementation of complex systems design, thus increasing the possibility in design space exploration. For the fast and optimized implementation of the complex systems and designs having FPGAs as the implementation technology, HLS based implementation provides significant suitability in terms of alternative design-space explorations by facilitating implementations of the modifications made to the design [20].

The prominent developments in the applications of FPGA industry include the use of FPGAs in the acceleration of the Bing search by the Microsoft and the Altera acquisition by Intel [21]. These developments enhance the possibility of usability of FPGAs in computing platforms with the help of high-level design methodologies. Further recent applications of HLS include in the areas of machine learning, medical imaging, neural networks etc. The primary reason behind the application of HLS in above specified areas is energy and performance benefits [22].

As hardware designs typically are more time consuming than equivalent software designs, this thesis proposes a rapid prototyping flow for FPGA-based video processing system design. High-level synthesis tools translate a software design into hardware descriptive language, which can be used for configuring hardware devices such as FPGAs. The video processing algorithm design of this thesis takes advantage of a high-level synthesis tool from one of the major FPGA vendors, Xilinx. However, high-level synthesis tools are far from being perfect. Users still need embedded hardware knowledge and experience in order to accomplish a successful design. This thesis focuses on interpolation filter architecture design and implementation for high-performance video processing system designs using a high-level synthesis. The consequent design results in a frame processing speed of 41 QFHD, i.e. 3840x2160@41fps for H.264/AVC sub-pixel Luma interpolation, 46 QFHD for HEVC luma sub-pixel and 48 QFHD for HEVC chroma interpolation. This thesis shows the possibility of realizing a high-performance hardware specific application using software. By comparing our approach with the approaches in other works, the optimized interpolation filter architecture proves to offer better performance and

6 Introduction

lower resource usage over what other works could offer. Its reconfigurability also provides better adaptability of many video coding interpolation algorithms.

## 1.3 Problem Statement

In recent years, FPGA development has been moved towards higher abstraction levels. The move not only helps improve productivity, but also lowers the barrier for more algorithm designers to get access to the tempting FPGA platform. There is a wide selection of tools available in the market that can be used for high-level synthesis. Conventionally algorithm designers prefer using high-level languages such as C/C++ for algorithm developments, and Vivado HLS is one of the tools that is capable for synthesis C/C++ code into RTL for hardware implementation. Nevertheless, most high-level synthesis tools could not translate a high level implementation to a RTL implementation directly, and users must restructure the high level implementations in order to make them synthesizable and suitable for the specific hardware architecture. Therefore, it becomes important to adapt to the high-level synthesis tool and to discover approaches for achieving an efficient design with high performance and low resource usage. The high-level synthesis tool used in this work is Vivado HLS from Xilinx.

This thesis addresses the following issues:

- 1. How can engineers with limited FPGA experience quickly prototype an FPGA-based SoC design for high performance video processing system?

- 2. How productive is Vivado HLS? What changes need to be made in order for a software implementation to be synthesized to a hardware implementation?

- 3. How are the performance and area of video processing algorithms modelled by Vivado HLS compared to that of RTL modelling from related works?

- 4. How are the performance and power consumption of a FPGA-based video processing system compared to that of an Intel CPU based video processing system?

1.4 Contribution 7

## 1.4 Contribution

This thesis work presents an FPGA-based video processing system rapid prototyping flow that aims to lower the boundary between software and hardware development. The rapid prototyping flow consists of two major parts: 1) the video processing system architecture design, and 2) the video processing algorithms design. By understanding the underlying architecture of Xilinx's Zynq platform, I can quickly assemble a video processing system on the block level with minimum RTL modifications. The development period can be reduced from months to weeks. In addition, since Vivado HLS does not provide a common structure for domain-specific algorithm designs, this thesis proposed HLS based hardware architecture for interpolation filters of video coding algorithm designs in Vivado HLS. Several optimizations are also done to the proposed interpolation filter architecture so that it not only improves the video processing rate, but also reduces the flip-flop utilization and saves the LUT utilization when comparing with similar works done in the literature. This work demonstrates the possibility of rapid prototyping of a computation-intensive video processing system with more than enough of the real-time processing performance.

# 1.5 Organization of the Thesis

This thesis is organized as the following: Chapter 2 discusses and compares the sate-of-the-art video coding standards i.e. High Efficiency Video Coding (HEVC), H.264/AVC and standardized extensions of HEVC. Also included in Chapter 2 are several related works that were done by others as well as some background information related to the coding tools that have been added in 3D-HEVC. Moreover, Chapter 3 describes the coding complexity analysis of 3D-HEVC. It identifies the computational intensive tools of 3D-HEVC encoder and decoder. Chapter 3 also discusses the class-wise coding and decoding time distribution of different classes (tools). In addition, Chapter 4 presents the High-level synthesis, available High-level synthesis tools and Xilinx Vivado Design Suite. Chapter 5 describes the HLS based implementation of interpolation filters of HEVC and H.264/AVC, which is one of the computational intensive part of the video coding algorithms. It includes the performance and resource utilization comparison between my work and other works.

8 Introduction

Last but not least, Chapter 6 will conclude this thesis with discussion about the contributions, challenges and future work.

# **Chapter 2**

# State-of-the-art Video Coding Standards

For effective communication, standard define a common language to be used between different parties. The same holds equally valid for the video coding standards. The common language that the video encoding and decoding components use for communication and syntax of the bitstream, is defined by the video compression standards. For the video compression standards, it is very important to support efficient compression algorithms and allow efficient implementation of the encoder and decoder.

Coding efficiency optimization is the most important and primary goal of majority of the video coding standards. For specific video quality, coding efficiency can be defined as, minimization of the bit-rate required for representing the specified video quality. Other way around, for a specific bit-rate, the increase in the video quality can be termed as coding efficiency.

The goal of this chapter is to describe the state-of-the-art video coding standards being used i.e. High Efficiency Video Coding (HEVC) standard [5][23] and H.264/AVC [24][6] comparative to their major forerunner including H.262/MPEG-2 Video [25][26], H.263 [27] and MPEG-4 Visual [28].

## 2.1 History of The Standardization Process

An enabling technology for digital television systems worldwide was, the MPEG-2 video coding standard [25], which was an extension of MPEG-1. MPEG-2 was widely used for transmission of TV signals of High definition (HD) and Standard Definition (SD) over a variety of transmission media such as terrestrial emission, cable, satellite and for storage onto DVDs.

The popular growth of HDTV and its services increase the need for higher coding efficiency. Coding efficiency enhancement allows the transmission of high quality and higher number of video channels over already available digital media transmission infrastructures e.g. UMTS, xDSL, Cable Modem etc. These mediums allow less data rates as compared to the broadcast channels.

The evolution of video coding in applications of telecommunication include the development of H.261 [29], H.262 [25][26], H.263 [27], H.264/AVC [24][6] and H.265 (HEVC) [5] video coding standards. The prominent telecommunication applications are wireless mobile networks, ISDN, LAN and T1/E1. To maximize the coding efficiency, significant efforts dealing with the loss/error optimization, network types and formatting of the characteristic have been made. This evolution of the video coding standards expanded the capabilities like video shaping and broadened the application areas of the digital video.

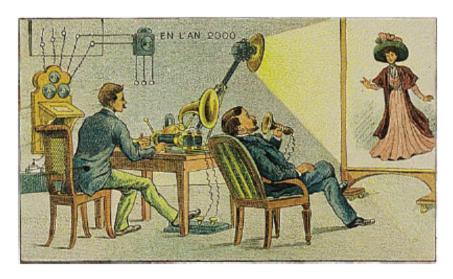

Fig. 2.1 Video coding standardization scope [6].

The scope of the video coding standard is shown in Fig.2.1. The transportation and storage media for video signal is not present in the scope of the video coding standard. The standardization of the decoder is central to video coding standard in all ISO/IEC and ITU-T standards. The standardization is about the syntax, bitstream structure and procedure for decoding the syntax elements. This makes for all the

decoders to produce the same type of output when an encoded input bitstream conforming to the constraints of a specific standard is given. This limitation in standard's scope, allows the flexibility and freedom for optimized implementations e.g. time-to-market, quality of compression, cost of implementation etc. But there is no guarantee of reproduction quality as any crude coding technology can be conforming to the standard.

## 2.2 H.264/AVC Video Coding

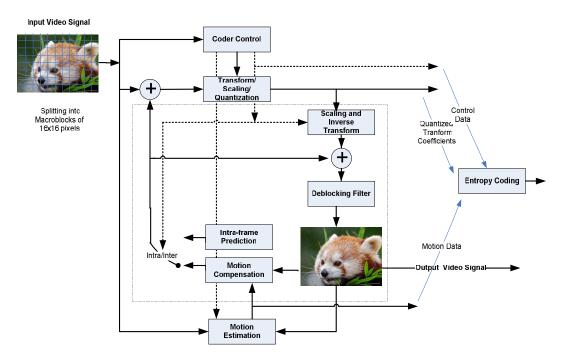

H.264/AVC macroblock basic coding structure is shown in Fig. 2.2. By splitting the input video frame results in macroblocks, each macroblock is associated with a specific slice, slice consists of several macroblocks. As shown, processing on each macroblock of every slice is performed. Usually, one picture consists of various slices, in that case parallel processing is possible by processing more than one macroblocks in parallel.

Fig. 2.2 H.264/AVC macroblock basic coding structure.

The prominent applications areas of H.264/AVC for which the technical solutions are designed include the following

- DSL, cable, terrestrial, satellite etc.

- Storage on DVD, optical and magnetic disks etc.

- Services over mobile networks, LAN, modems, Ethernet etc.

- Multimedia services like Video-on-demand, MMS over ISDN, DSL, wireless networks etc.

Some prominent features of the H.264/AVC are as follows [6].

- Supports motion compensation of small block sizes as 4 x 4 luma, hence, more flexible.

- More accurate motion vector by supporting quarter-sample motion compensation.

- Supports picture boundary extrapolation technique.

- For efficient coding supports enhanced reference picture selection.

- More flexible selection of pictures ordering for display and referencing purposes.

- Flexible picture referencing and representation methods.

- Supports weighted motion prediction.

- Supports "Skipped" motion inference in improved form and in addition to that supports "direct" motion inference method.

- Intra coding based on directional spatial prediction.

- Supports In-the-loop deblocking filtering.

For improvement in the coding efficiency, the following parts of the standard were also enhanced:

- Supports block size of 4x4 transform.

- Supports block transform in hierarchical manner.

- Supports 16-bit transform i.e. short, as comparative to 32-bit processing of the previous standards.

- Inverse transform is more efficient in terms of video content equality after decoding from all decoders.

- Includes CABAC (context-adaptive binary arithmetic coding) and CAVLC (context-adaptive variable-length coding), more powerful and advanced entropy coding methods.

For the more robust and flexible operations, the new design features included in H.264/AVC standard are as follows:

- For the efficient and robust header information conveyance the Parameter set structure is provided.

- The logical data packet is used for every syntax structure, this is called NAL

unit. This structure provides more flexibility in terms of customization for

transmission of the video content over specific networks.

- Supports more flexible slice sizes.

- Supports Flexible macroblock ordering (FMO).

- Supports Arbitrary slice ordering (ASO), in real-time applications which can improve delay e.g., internet protocol networks.

- Supports Redundant pictures, which improves robustness to data losses.

- Supports Data Partitioning, allows the partitioning of the slice syntax up-to three different parts, for purpose of transmission, it depends on syntax elements categorization.

- Supports SP/SI synchronization/switching pictures, picture types specification

enables synchronization of the decoder in decoding process of an ongoing

video content stream produced by other decoders, hence improving the efficiency. This allows decoder switching between video content representations

for different data rates, losses or errors recovery, enabling trick modes such as

fast-reverse and fast-forward etc.

# 2.3 High Efficiency Video Coding (HEVC)

Growth in the popularity of HD video, increase in diversification of services, appearance of UHD and QFHD formats of video e.g. 4K or 8K resolution, demands the higher coding efficiency as compared to H.264/AVC's abilities. In addition to that, the demand for higher coding efficiency becomes more strong while considering the multiview or stereo applications of higher resolution. Furthermore, tablet PCs and mobile devices become the source of higher video contents consumption, application like video-on-demand needs efficient network infrastructure. Accumulatively, all these factors are imposing big challenges on the current networks. Mobile applications require higher resolutions and quality.

To address all existing H.264/AVC applications, need for a more efficient video standard becomes obvious. The most recent video project of the ITU-T Video Coding Experts Group (VCEG) and the ISO/IEC Moving Picture Experts Group (MPEG) standardization organizations is the High Efficiency Video Coding (HEVC). These organizations are collaborating as Joint Collaborative Team on Video Coding (JCT-VC) [23]. In 2013, HEVC's first edition was finalized in the form of an aligned draft published by both ISO/IEC and ITU-T. For extending the applications areas of HEVC standard more work was planned to support scalable, extended-range, 3D, multiview and stereo video coding. HEVC has been designed for this purpose and specifically to focus on two hot issues: increased applications of parallel architectures and higher resolution for video processing. Like all previous video compression standards of ITU-T and ISO/IEC, only the bitstream structure and syntax is standardized, and also the procedure for decoding.

## 2.3.1 HEVC Feature Highlights and Coding Design

HEVC has been designed to accomplish many goals, including integration of transport system, coding efficiency, resilience to data losses and architectures implementation using parallel processing.

Main features of the HEVC design are described briefly in the following paragraphs.

## **Video Coding Layer**

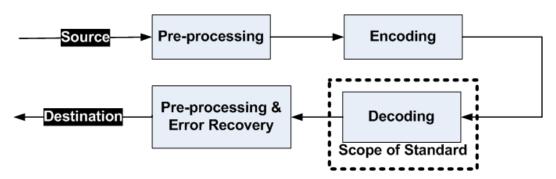

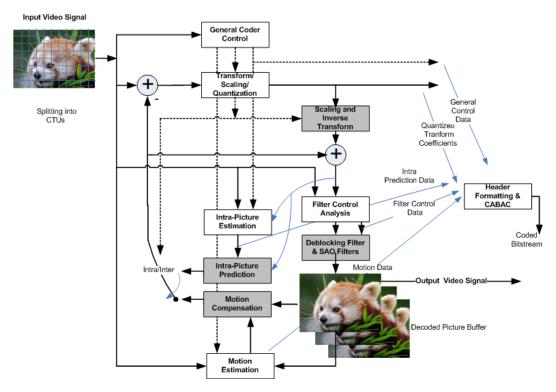

Video coding layer utilize the hybrid approach for intraprediction, interprediction and 2-D transform coding, the same approach was used in all previous video coding algorithms since H.261. Hybrid video encoder's block diagram is shown in Fig. 2.3, which could make a HEVC conformed bitstream.

Fig. 2.3 HEVC video encoder (Light gray elements show decoder).

Highlighted features of HEVC are given in the following text. A more detailed version of these properties can be found in [9].

- Coding tree block (CTB) and Coding tree units (CTUs): One luma CTB, related chroma CTBs comprise the CTU. The size of the luma CTB can be LxL, where L= 16, 32, or 64 pixels. The larger the size the better the compression. CTBs are partitioned into smaller blocks of quadtree-like structure and signalling [30].

- *Coding blocks (CBs) and Coding units (CUs)*: One luma CB and two corresponding chroma CBs and the related syntax comprise a coding unit (CU). CUs are partitioned into prediction units (PUs) and transform units (TUs) tree.

- *Prediction blocks (PBs) and Prediction units*: Luma and chroma CBs can be further partition in size and predicted from luma and chroma PBs depending on the decision of the prediction-type. 64×64 down to 4×4 samples variable PB sizes are supported in HEVC.

- *Transform blocks (TBs) and Transform units (TUs):* Transforms blocks are used for the coding of prediction residual. Supported TB size are 32x32, 16x16 and 4x4.

- Motion vector signalling: In Advanced motion vector prediction (AMVP),

most probable candidates are derived from reference picture and the adjacent

PBs. For MV coding, a merge mode can be used. In merge mode, MVs

are inherited from the spatially or temporally neighbouring PBs. Direct and

improved skipped motion can also be used.

- *Motion compensation:* For the motion vectors (MVs), quarter-pixel precision is used. 7-tap and 8-tap filters are designed for the sub-pixel interpolation as compared to the H.264/AVC six-tap filters.

- *Intrapicture prediction:* 33 directional, DC (flat) and planar (surface fitting) prediction modes are supported in HEVC. The encoding of the selected prediction mode is performed based on neighbouring blocks previously decoded.

- *Quantization control:* HEVC supports uniform reconstruction quantization (URQ). For different transform block sizes the scaling matrices for quantization are used.

- *Entropy coding:* Context adaptive binary arithmetic coding (CABAC) method is used. The improvements made to the entropy coding method includes better coding performance, higher speed of throughput and reduction in the requirements of the context memory.

- *In-loop deblocking filtering:* More simplified deblocking filter in terms of filtering and decision-making, friendly in terms of parallel processing.

- Sample adaptive offset (SAO): Post deblocking in the interpicture prediction loop, a new type of non-linear amplitude mapping is used, for the better original signal reconstruction.

### **Modified Slice Structuring and Parallel Decoding Syntax**

For slice data structure modification and parallel processing enhancement for the purpose of packetization, new features are added in the HEVC. In the context of a particular application, these features have specific benefits.

- *Tiles:* Partitioning a picture into rectangular area (Tiles) is supported in HEVC. Parallel processing capability can be increased by application of the concept of tiles. Tiles can be decoded independently with some common header information. Tiles support parallelism in terms of subpicture/picture i.e. coarse level of granularity.

- Wavefront parallel processing: WPP supports parallelism in terms of slice

i.e. at a fine level of granularity. It gives better performance of compression as

compared to tiles and removes the visual artefacts which may be present in

case of tiles.

- *Dependent slice segments:* Dependent slice segment structure enables the fragmented packetization (separate NAL unit) of the data of a specific tile or wavefront entry. It improves the performance by reducing the latency. Low-level encoding may takes advantage of the dependent slice segments.

## 2.4 Standardized Extensions of HEVC

HEVC extensions can be divided into three types:

- 1. Range extensions

- 2. Scalability extensions

- 3. 3D video extensions

All of these extensions are briefly described in the following paragraphs:

## 2.4.1 Range Extensions

The structures of enhanced chroma sampling 4:2:2 and 4:4:4 and pixel bit depths more than 10 bits are supported in the range extensions of the HEVC. Range ex-

tensions are applicable to the areas of screen content coding, direct source content coding of the RGB, auxiliary pictures coding and lossless and high bit-rate coding. The draft range extensions can be found in [31].

## 2.4.2 Scalability Extensions

The coarse grain SNR and spatial scalability are possible through scalability extensions of the HEVC also termed as "SHVC". [32] provides the draft text of scalability extensions. SNR and spatial scalability in SHVC can combined with already available temporal scalability [33]–[34]. Resampling of the decoded reference layer picture is performed when spatial scalability is used. This resampling is performed by the use of upsampling filter defined specifically for the spatial scalability scenario.

#### 2.4.3 3D Video Extensions

Depth for a visual scene can perceived by the multiview and 3D video formats in combination with the proper 3D display system. There are two type of the 3D displays available in the market:

- 1. **Stereoscopic displays:** Special glasses are required to perceive the depth of the view.

- 2. Auto-stereoscopic displays: No requirement of the glasses to perceive the depth of the scene, instead, view-dependent pixels are emitted. Auto-stereoscopic displays perform depth-image based rendering (DIBR). For DIBR systems, depth is part of the input coded bitstream. 3D formats in form of video plus depth is an important category of 3D formats.

#### **Multiview HEVC**

Mutiview HEVC is the most simple and straightforward architectural extension of HEVC, also termed as MV-HEVC, based on H.264/AVC MVC design principles [35], [36]. The draft text can be found in [37].

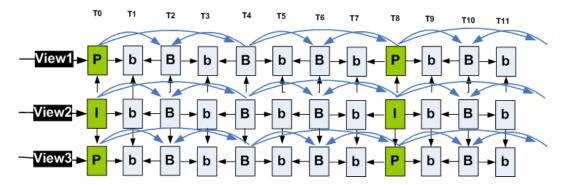

Fig. 2.4 3-view case: Prediction structure of Multiview HEVC.

The 3-view case prediction structure of the multiview is shown in Fig. 2.4. HEVC is capable of flexible management of the reference pictures. This capability of the HEVC enables the inter-view sample prediction.

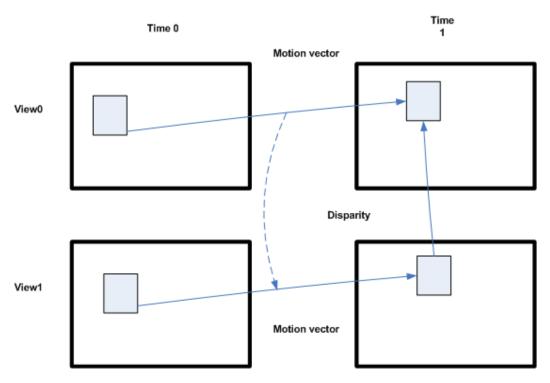

Fig. 2.5 HEVC Inter-view motion prediction.

#### **Multiview HEVC With Modification in Block-Level Tools**

The correlation between views exploited through residual and motion data. Block-level changes make possible the exploitation of this correlation as shown in 2.5

# 2.5 3D High Efficiency Video Coding (3D-HEVC)

3D-HEVC is the HEVC extension for which the working draft and the reference test model are specified in [38], [39]. The advanced coding tools for multiple views are included in this extension. [40] becomes the basis for the 3D-HEVC. Prominent 3D-HEVC tools are presented in the following paragraphs.

## 2.5.1 Neighbouring Block-Based Disparity Vector Derivation

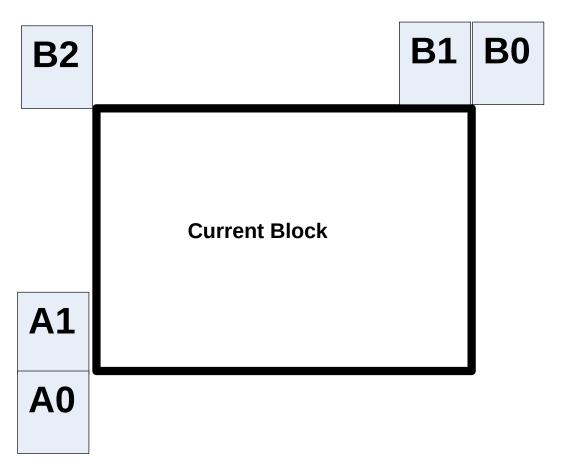

Neighbouring block based disparity vector (NBDV) is the 3D-HEVC tool used for the identification of similar blocks in multiple different views. This tool's design is very similar to the merge mode and AMVP in HEVC. For inter-view pixel prediction of spatial and temporal neighbouring blocks, NBDV is used which make use of already available disparity vectors [41].

Fig. 2.6 shows the spatial neighbouring blocks used for the NBDV process, these are same blocks as in merge modes/AMVP of HEVC. The order of the block's access is also same as in merge mode:  $A_1$ ,  $B_1$ ,  $B_0$ ,  $A_0$ , and  $B_1$ .

#### 2.5.2 Inter-View Motion Prediction

The merge mode modification by the addition of more candidates make the realization of the inter-view motion prediction. No modification to the AMVP is made. The new merge list has six candidates. The construction of the list is still same as in HEVC. Additional two candidates can be put into the list as described in the following text.

NBDV provides the index of the reference picture and motion vector of block found, as shown in Fig. 2.5. This is the first candidate inserted into the merge list. NBDV also provides the disparity vector and index of the reference inter-view

picture. This is the second candidate inserted in merge list. Disparity vector insertion into the candidate list does not depend on existence of the inter-view candidate [42].

Fig. 2.6 Spatial Neighbouring blocks for NBDV.

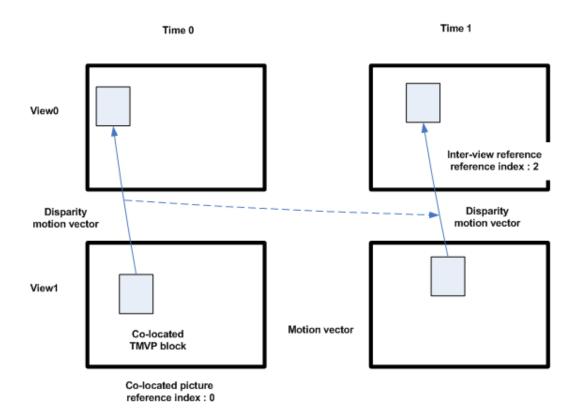

Fig. 2.7 shows that the TMVP co-located block of view 1 at time 1 for current block, have a reference index 0 and disparity vector according to the current picture's temporal reference. That is why the TMVP candidate is usually regarded as unavailable. The candidate is regarded as available by changing the reference target index to 2 i.e. according to the inter-view reference picture.

Fig. 2.7 3D-HEVC temporal motion prediction.

## 2.5.3 Inter-View Residual Prediction

In case of two-views residual signal motion-compensation, the advantage of the correlation is taken by the application of advanced residual prediction (ARP) [43].

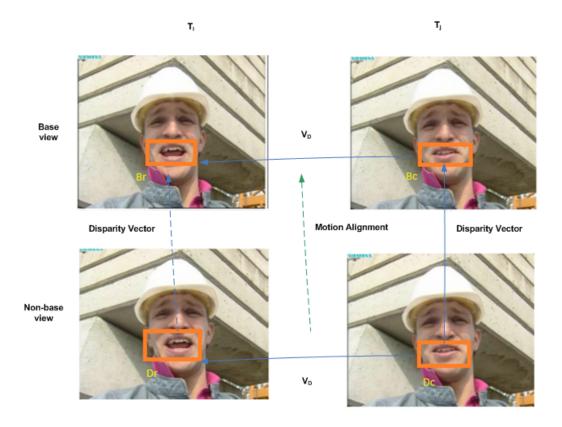

Fig. 2.8 3D-HEVC Temporal motion vector prediction.

In current non-base view i.e. for the block  $D_C$ , motion compensation is carried out using the  $V_D$  motion vector as shown in as shown in Fig. 2.8. The NBDV vector identifies the  $B_C$  inter-view block. Then, by the use of  $V_D$ , the motion compensation is performed by the base view reconstructed  $B_r$  and  $B_C$ . Addition of this predicted signal to the signal predicted by motion compensation of  $D_r$  is performed. The precision of the current block's residual signal is best as same  $V_D$  vector is used. This residual prediction can be can weighted by 1 or 0.5, with ARP enabled.

# 2.5.4 Illumination Compensation

The calibration of the cameras in lighting effects and colour transfer is very important. Otherwise, the prediction of the cameras recording the same scene may fail. For improvement in the coding efficiency of the blocks predicted through inter-view pictures, new coding tool named as illumination compensation is developed [44].

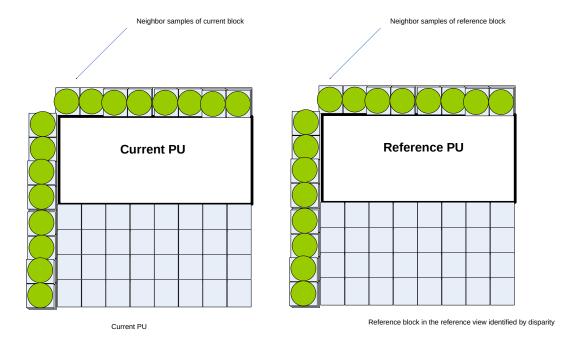

The disparity vector of the current PU is used for the identification of reference view neighbour sample as shown in Fig. 2.9.

Fig. 2.9 Illumination Compensation.

# 2.5.5 Multiview HEVC With Depth

In 3D-HEVC, Depth maps are used in the investigation of compression formats such as video-plus-depth. The 3D data consists of multiple video and depth data components. For their efficient implementation, many new coding tools are added in 3D-HEVC for exploiting the correlation among video and depth data components. For coding of these types of formats, first video component is assumed as to be coded by 2D HEVC. This makes the codec compatible with the 2D video service. For the dependent video and depth maps, specific 3D tools are added in 3D-HEVC. Each block can be optimally coded by the application of appropriate tools from a set of 3D and 2D tools.

### **Partition-Based Depth Intra Coding**

Coding tools specific to the depth for efficient depth information representation, are added in the 3D-HEVC design. These tools allow the non-rectangular partitioning of the depth blocks. Depth coding modes such as depth modelling modes (DMM) [45], simplified depth coding (SDC) [46] and region boundary chain coding (RBC) [47] are used for partition-based depth intra coding. Fig. 2.10 shows the division of depth PU as one or two parts. DC value is used for representing each part of the depth PU.

| P0 | P0 | P0 | P0 |

|----|----|----|----|

| P0 | P0 | P0 | P1 |

| P0 | P0 | P1 | P1 |

| P0 | P1 | P1 | P1 |

| P0        | P0 | P0 | P0 |

|-----------|----|----|----|

| <b>P1</b> | P0 | P0 | P0 |

| P1        | P1 | P0 | P1 |

| P1        | P1 | P1 | P1 |

(a) Wedge-shaped pattern

(b) Boundary chain coding pattern

Fig. 2.10 Partitioning of depth PU.

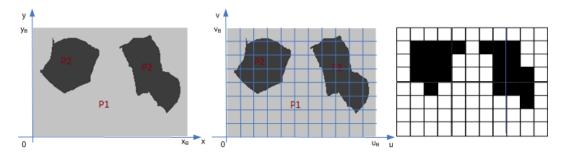

Two types of depth partitioning are available in case of DMM. These are contour and wedge-shaped pattern. As shown in Fig 2.10(a), In case of the wedge-shaped pattern the depth PU is segmented by a straight line. Connected chain in a series fashion are used for segmenting the depth PU in case of RBC as shown in Fig. 2.10(b). Fig. 2.11 shows the partitioning of the depth PU based on contour pattern. As shown, these are irregular partitions with separate sub-regions.

Fig. 2.11 Contour partition of a block.

### **Motion Parameter Inheritance**

The motion parameters of the texture block can be used for the depth block. Merge list of current depth block is modified by the addition of one more candidate, making the inheritance of motion parameters of texture block for the corresponding depth. The co-located block of texture helps in the generation of the extra candidate [48].

## **View Synthesis Prediction (VSP)**

For the reduction of the inter-view redundancy, the VSP approach is used. In this approach for texture view warping depth data information is used. By this method a current view predictor can be generated [49].

# **Chapter 3**

# Coding Complexity Analysis of 3D-HEVC

Recent advancements in video technology increased the interest in 3D Video. Video sequences are found in mobile, 3D cinema, internet and 3D television broadcast channels [50]. The quality of the video sequences is rapidly increasing due to the improvements in the video compression techniques and tools. Also, the improvements in the 3D video display technologies have led to an increased demand for 3D videos. Autostereoscopic displays are the future of displaying technologies in 3D Cinemas, 3D-TV and home entertainment. Video contents in resolutions are getting high definition and ultra-high definition for mobile and home applications respectively. 3D video features are already being integrated in most of the video processing devices including capturing, processing and display devices. The demand for compression of videos is also increased. The most recent and advanced standard for video compression is High Efficiency Video Coding (HEVC) [9]. After HEVC, focus is on extensions of the standard to support broad range of applications. 3D-HEVC is one of the extensions of High Efficiency Video Coding. Advanced coding algorithms are developed for 3D video coding. To analyse and assess the complexity, profiling of the reference software of 3D-HEVC is carried out using gprof and gcc compiler of the standard video sequences mentioned in the Common Test Conditions (CTC). Results based on profiling show that alongside motion estimation and interpolation filters, majority of the encoding time (18-26%) of total encoding time is consumed by the Renderer model. Thus, 3D-HEVC Renderer model is identified as one of the computational intensive part of the standard alongside motion estimation and interpolation filters. While some papers in the literature are available on the complexity evaluation of some tools of 3D-HEVC encoder/decoder, no results are currently available to specifically explore the complexity and hardware implementation analysis of renderer model of 3D-HEVC used for the View Synthesis Optimization (VSO). [51] presents time profiling of 3D-HTM 10.2 reference software, in which the complexity of texture and Depth Modelling Modes (DMMs) used for depth maps encoding, is given. Inter-prediction encoding time percentage for 3D-HTM 8.0 reference software is given in [52], no information is presented regarding the complexity analysis of rendering distortion estimation model for 3D-HEVC.

Renderer model is used for RDO of depth maps coding by estimation of synthesized view distortion. Depth maps are used for virtual view synthesis. Depth maps lie at the core of 3D video technologies. Distortion in depth maps coding effect the quality of intermediate virtual views generated during the process of DIBR. Because of these important observations and based on the profiling result, in Chapter 6, we have focused on the Renderer model. Identification of computational hotspots help both in decreasing the complexity and increasing the performance by developing the efficient tools and by implementing the accelerated software and hardware solutions for real time visualization of the 3D video coding standard.

# 3.1 3D-HEVC Tools

3D-HEVC basic structure is shown in Fig. 3.1. 3D-HEVC is an enhanced version of HEVC codec, for coding dependent views, the base view is coded using the HEVC codec.

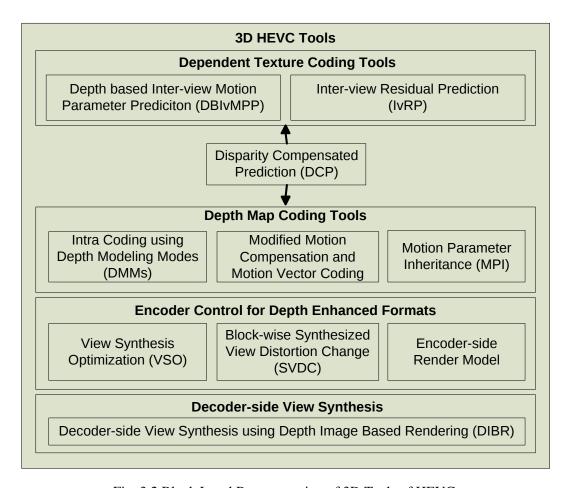

Supplementary coding tools and techniques, as shown in Fig. 3.2, take into account the already coded data of other views, hence reducing the data redundancy.

# 3.1.1 Dependent View Coding

Dependent view coding in 3D-HEVC is performed by applying some supplementary coding methods in addition to the basic tools of independent view coding. Additional coding methods are used to decrease the data redundancy in the dependent view as described in the following paragraphs.

3.1 3D-HEVC Tools 29

Fig. 3.1 Block Diagram of basic structure of 3D-HEVC.

#### **Disparity-Compensated Prediction**

Disparity Compensated Prediction (DCP) is used for the inter-view prediction of dependent views. The incorporation of DCP affects only the reference list construction procedure i.e. already coded pictures of other views and same access unit are added in the reference picture lists.

#### **Inter-view Motion Prediction**

Inter-view motion prediction is used for eliminating the data redundancy of the multiple views. The detailed description of Inter-view motion prediction is given in [53]. The motion information of current block of dependent view is obtained from corresponding block in the reference view.

Fig. 3.2 Block Level Representation of 3D Tools of HEVC.

#### **Advanced Residual Prediction**

In [54] the Advanced Residual Prediction (ARP) is described in detail. The correlation between the residual of already coded view and residual of current view also exist. To compensate this correlation advanced interview prediction is used.

# 3.1.2 Depth Maps Coding

Depth maps represent the distance of the objects in scene from the camera. Depth maps are used for view synthesis of intermediate views in multi-view generation systems. Depth maps consist of constant value regions with sharp edges. For depth maps intra-prediction, additional coding tools are used.

## **Depth Modelling Modes**

In [55] depth modelling modes are introduced for coding of the depth maps intraprediction. These tools divide the depth maps in two different non-rectangular regions of constant values for intra coding.

#### **Motion Parameter Inheritance**

Partitioning of a block to sub-blocks and motion information of the current block of depth map can be inherited from the corresponding block of texture as in [56].

#### 3.1.3 Encoder Control

In 3D-HEVC, encoder mode is decided based on Lagrangian cost measure. Depth maps added for virtual view synthesis, the distortion measure for the depth maps can be observed only in synthesized views as described in [57]. Synthesized View Distortion Change (SVDC) is used for efficient estimation of distortion in rendered synthesized views due to distortion in depth maps coding.

# 3.2 Complexity Analysis

3D-HEVC is based on video plus depth format. Depth maps facilitate the synthesis of intermediate views on the decoder side for applications like 3D-TV, Free viewpoint TV etc. The compression errors of depth maps result in synthesis artefacts for the intermediate views rendered through Depth Image Based Rendering (DIBR) methods. To remove these coding artefacts in the virtual view synthesis process, the Synthesized View Distortion Computation (SVDC) models are included in 3D-HEVC. Encoding and decoding time Complexity analysis of 3D-HEVC standard is presented in this section. Profiling of the reference software of 3D-HEVC is carried out using *gprof* and *gcc* compiler of the standard video sequences mentioned in the Common Test Conditions (CTC). Results based on profiling show that (18-26%) of total encoding time is consumed by the Renderer model. Alongside other compute-intensive parts i.e. Motion Estimation (ME) and Interpolation Filtering,

3D-HEVC Renderer model is identified as one of the computational intensive part of the standard.

The 3D-HTM software provides the reference implementations of 3D-HEVC video encoder and decoder. Our aim is to identify computational hotspots of the standard. Implementation and complexity analysis of the standard may be assessed based on these computational hotspots. The detailed analysis of 3D-HEVC coding tools based on profiling results is given as in the following paragraphs.

# 3.2.1 Profiling of 3D-HTM Encoder

We have performed the profiling of latest available 3D-HTM Software Encoder Version 15.0 based on HM Version 16.6. GNU *gprof* is used for profiling. Computationally intensive parts are identified based on the profiling. CTC of 3DV Core Experiments are used for encoding the video sequences, used for profiling of the encoder [58]. Eight test video sequences (1024 x 768 pixels and 1920 x 1088 pixels) of 3DV Core Experiments are used for encoding at five different QP values (25, 30, 35, 40, 45). Two types of Encoder configuration i.e. Random Access (RA) and All Intra (AI), are used for the experiments. We have used the three-view case (C3) test scenario of the multiview/stereo video coding with depth data. Majority of the encoding time is spent in classes and functions shown in Table 3.1. Encoding times are obtained on an Intel Xeon-based (16 Core) Processor (E312xx clocked at 1.99 GHz) and using gcc 4.4.7.

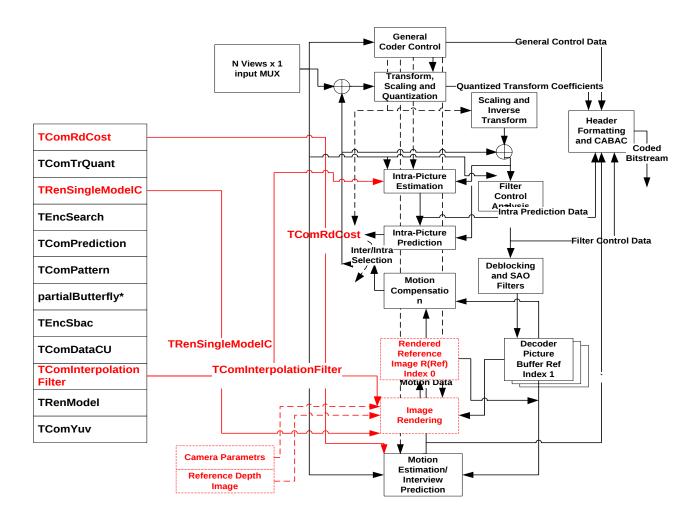

#### Profiling Results comparison of 3D-HEVC and HEVC Encoder

Although in [51] and [52] partial profiling results of 3D-HEVC texture and depth maps are presented. We cannot directly compare our profiling results with results presented in [51] and [52] because our results are more detailed up-to class/function level. Table 3.1 shows the comparison between the profiling results of encoder of 3D-HEVC and HEVC [59] standards for Random Access (RA) and All Intra (AI) configurations, respectively. As shown in the Table 3.1, TComRdCost class consumes majority of the time spent in encoding i.e. about 31.3-35.4% and 9.8-38.8% in both configuration of 3D-HEVC and HEVC, respectively. Motion Estimation (ME), Inter view residual, Inter view motion prediction and other distortion operations takes place in TcomRdCost class. Operations like Sum of Absolute Difference (SAD),

Hadmard transform (HAD) and Sum of Squared Error (SSE) for Rate Distortion Computation are performed. Depth maps estimation used in inter view motion prediction for the calculation of disparity vector derivation in dependent views is also calculated in this class. TRenSingleModelC class consumes about (26.8% and 18.3%) of time. Process like VSO and SVDC estimation takes place in this class. Process of rendering is used for Virtual View Synthesis generation. In Random Access (RA) configuration, the time taken by TComInterpolationFilter class is about (19.3%) and (19.8%), respectively, where the motion compensation Vertical and Horizontal Filtering (VHF) occurs. Interpolation filtering is used, whenever the inter-view residual prediction, de-blocking and View Synthesis prediction is applied.

Table 3.1 Class-wise time distribution 3D-HEVC vs HEVC Encoder.

| Function / Class         | 3D-HEVC |       | HEVC [59] |       |

|--------------------------|---------|-------|-----------|-------|

| Tunetion / Class         | AI%     | RA%   | AI%       | RA%   |

| TComRdCost               | 35.4    | 31.3  | 9.8       | 38.8  |

| TRenSingleModelC         | 26.8    | 18.3  | Nil       | Nil   |

| TComInterpolationFilter  | 0.0     | 19.3  | 0.0       | 19.8  |

| TComTrQuant              | 9.0     | 10.0  | 24.4      | 10.7  |

| TEncSearch               | 8.7     | 3.6   | 11.8      | 7.4   |

| TComPrediction           | 5.0     | 0.88  | 10.0      | 1.1   |

| partialButterfly*        | 2.3     | 4.1   | 8.7       | 4.0   |

| TEncSbac                 | 2.9     | 1.8   | 8.4       | 3.5   |

| TRenModel                | 0.4     | 2.3   | Nil       | Nil   |

| TComDataCU               | 2.2     | 1.0   | 5.8       | 2.7   |

| TComPattern              | 2.2     | 0.2   | 6.6       | 0.4   |

| TComYuv                  | 0.2     | 1.8   | 0.1       | 1.7   |

| TEncEntropy              | Nil     | Nil   | 1.2       | 0.6   |

| TEncBinCABAC*            | Nil     | Nil   | 2.2       | 0.9   |

| memcpy/memset            | Nil     | Nil   | 11.0      | 7.1   |

| Total percentage of time | 95.1%   | 95.3% | 100%      | 98.7% |

In 3D-HEVC and HEVC, TComTrQuant class accounts for about (9% and 10%) and (24.4% and 10.7%) of total encoding time, respectively. In TComTrQuant the process of Rate-Distortion Optimized Quantization (RDOQ) occurs. As the name of

class shows, in TComTrQuant, the process of rate and distortion optimized transform and quantization takes place. TEncSearch accounts for about (8.7 % and 3.6 %) and (11.8 % and 7.4 %) of the time in both configurations of HEVC encoders, respectively. In TEncSearch , the encoder searches for the cost and rate-distortion computation of modes for inter, intra, depth intra for DMM, for motion estimation processes and Advanced Motion Vector Prediction (AMVP) of HEVC based standards. Similarly for intra prediction classes like TComPrediction and TComPattern contribute about (2% to 7%) to the total encoding time in both configuration of 3D-HEVC. Actual optimized Transform takes place in partialButterfly\* and contribute about (2.3 % and 4.1 %) and (2.3 % and 4.1 %) in both configurations of the standards. Other classes like TEncSbac,TComDataCU and TComYuv contribute about (1%-3%) to total encoding time in both configurations.

# 3.2.2 Profiling of 3D-HTM Decoder

Profiling of 3D-HTM Software Decoder Version 15.0 based on HM Version 16.6 is carried out using GNU *gprof*. Computationally intensive critical parts of decoder are identified based on the profiling information.

#### Profiling Results comparison of 3D-HEVC and HEVC Decoder

Table 3.2 shows the decoding time distribution of 3D-HEVC and HEVC Decoder. Classes contributing significantly in terms of time consumption, in the decoding process, are shown. In all intra configuration more than quarter of total time is spent in TComInterpolationFilter. In the process of motion compensation, interpolation filtering is used. TComCUMvField, TComLoopFilter, TComDataCU classes also account for most of the decoding time. In these classes the processes internal to CU, advance motion vector prediction and filtering takes place. TComYuv is a general YUV buffer class, it manages the memory related functionalities of decoder. In random access configuration, partialButterflyInverse, TComPattern, TDecCu and TComLoopFilter classes are computationally intensive classes in the decoding process. In these classes processes related to inverse transform, functions related to coding unit, intra prediction and loop filtering takes place. In HEVC and 3D-HEVC, the computational complexity of classes varies from one standard to the other, as observed from the profiling results.

Table 3.2 Class-wise time distribution 3D-HEVC vs HEVC Decoder.

| Function / Class             | 3D-HEVC |        | HEVC [59] |       |

|------------------------------|---------|--------|-----------|-------|

| Tunction / Cluss             | AI%     | RA%    | AI%       | RA%   |

| TComInterpolationFilter      | 0.0     | 26.96  | 0.0       | 24.8  |

| TComCUMvField                | 7.39    | 16.03  | Nil       | Nil   |

| TDecCu                       | 15.97   | 3.69   | 7.2       | 2.6   |

| partialButterflyInverse      | 15.83   | 1.80   | 15.9      | 7.6   |

| TComYuv                      | 0.83    | 14.42  | 0.5       | 8.2   |

| TComDataCU                   | 7.54    | 13.89  | 7.5       | 7.1   |

| TComLoopFilter               | 13.73   | 8.94   | 12.9      | 12.4  |

| TComPattern                  | 10.19   | 0.0    | 9.4       | 2.6   |

| TComTrQuant                  | 8.07    | 2.74   | 8.7       | 4.2   |

| TComPrediction               | 5.22    | 2.06   | 5.1       | 2.3   |

| TDecSbac                     | 3.84    | 0.0    | 6.2       | 2.8   |

| TDecBinCABAC                 | 2.93    | .42    | 5.3       | 2.3   |

| TCom Sample Adaptive Off set | 2.64    | 1.04   | 3.8       | 2.4   |

| TComPicYuv                   | 0.0     | 2.3    | Nil       | Nil   |

| writeplane                   | 1.06    | 1.68   | Nil       | Nil   |

| TDecEntropy                  | 1.23    | .71    | 1.4       | 1.0   |

| memcpy/memset                | Nil     | Nil    | 6.2       | 10.1  |

| Total percentage of time     | 96.47%  | 96.68% | 90.1%     | 90.4% |

# 3.3 Identified Computational Complex Tools

Fig. 3.3 shows the identification and mapping of computationally intensive parts of the 3D-HTM standard. The identification of these parts is carried out by mapping the profiling results of C++ HTM encoder and decoder classes to 3D-HEVC High level encoder coding tools. From the profiling results, it is identified that the major part of the encoding time of 3D-HEVC is consumed in motion estimation including interview motion prediction, encoder control regions consisting of the VSO, SVDC by the use of rendering method and interpolation filters, as shown in Fig. 3.3. Identified computational intensive parts of 3D-HEVC standard are listed as follows:

- 1. Motion Estimation (ME)

- 2. Synthesized View Distortion Change (SVDC)

- 3. Interpolation Filters

Fig. 3.3 Identification and mapping of Computationally Complex parts of 3D-HEVC.

# **Chapter 4**

# **High-Level Synthesis**

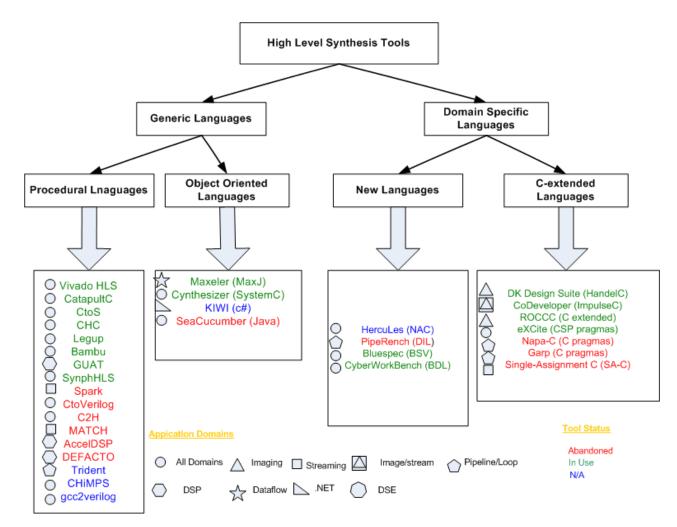

In this chapter, an analysis of HLS techniques, HLS tools, current HLS research topics are presented. For the automatic design of customized application-specific hardware accelerators, academia and industry are working together. Three academic tools considered are Delft workbench automated reconfigurable VHDL generator (DWARV) [60], BAMBU [61], and LEGUP [62] alongside many other commercial available tools. Many research challenges are still open in HLS domain.

# 4.1 What is High-Level Synthesis?

Nowadays, heterogeneous-systems are being adopted as the energy-efficient, high-performance and high-throughput systems. The reason behind this is the impossibility of the further scaling of the clock frequency. These systems consist mainly of two parts i.e., the application-specific integrated circuits (ASICs) and the software processor [16]. Each part of the system is dedicated for a specific task. The design of these types of systems become very complex due to increase in the complexity of systems. ASICs are the dedicated hardware components for the accelerated implementation of the computational complex parts for the system. As stated above, due to increase in the complexity of systems, the design of these dedicated hardware also become complex and time-consuming. Hardware Description Languages (HDLs) are used for the register transfer level (RTL) implementation of these components. Cycle-by-cycle activity for RTL implementation of these components is specified, which is a low abstraction level. For the such a low level of implementation, advanced

expertise in the hardware design are required, alongside being unmanageable to develop. The impact of these low-level implementation of complex systems increase the time-to-market by taking more design and development time.

High-level synthesis (HLS) and FPGAs in combination, is an intriguing solution to these problems of longer time-to-market and to realize these heterogeneous systems [19]. FPGAs are used for the configurable implementation of digital integrated circuits. Manufacturing cost is an important factor in the implementation of digital ICs. The use of FPGAs as reconfigurable hardware, help us the fast implementation and optimization by providing the ability to reconfigure the integrated circuits, hence, removing the extra manufacturing cost. It allows the designer to re-implement modifications made to the design, by changing the HDL code description, re-synthesize and implement the design using the same FPGA fabric by the help of implementation tools.

C, SystemC and C++ etc. are High-level languages (HLLs) being used for the software programming and development. HLS tools take HLL as input and then HDL description (circuit specification) is generated automatically. This automatically generated circuit specification perform the same functionality as the software specification. Since, the benefits of HLS i.e. to have a new fast hardware implementation just by changing the code in software, help software engineers with very little requirement of the hardware expertise needed. The benefits of the HLS to hardware engineers include are the fast, rapid and high-level abstraction implementation of complex systems design, thus increasing the possibility in design space exploration. For the fast and optimized implementation of the complex systems and designs having FPGAs as the implementation technology, HLS based implementation provides significant suitability in terms of alternative design-space explorations by facilitating implementations of the modifications made to the design [20].