### POLITECNICO DI TORINO

SCUOLA DI DOTTORATO Dottorato in Ingegneria Elettronica e delle Comunicazioni – XXVIII ciclo

Tesi di Dottorato

# Architectural Solutions for NanoMagnet Logic

Giovanni Causapruno

**Tutore** prof. Maurizio Zamboni Coordinatore del corso di dottorato prof. Ivo Montrosset

Maggio 2016

## Summary

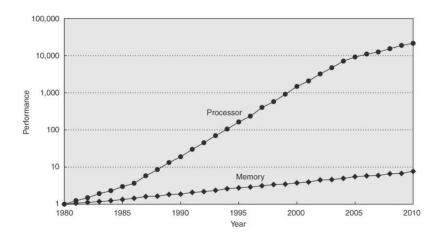

The successful era of CMOS technology is coming to an end. The limit on minimum fabrication dimensions of transistors and the increasing leakage power hinder the technological scaling that has characterized the last decades. In several different ways, this problem has been addressed changing the architectures implemented in CMOS, adopting parallel processors and thus increasing the throughput at the same operating frequency. However, architectural alternatives cannot be the definitive answer to a continuous increase in performance dictated by Moore's law. This problem must be addressed from a technological point of view.

Several alternative technologies that could substitute CMOS in next years are currently under study. Among them, magnetic technologies such as NanoMagnet Logic (NML) are interesting because they do not dissipate any leakage power. Moreover, magnets have memory capability, so it is possible to merge logic and memory in the same device.

However, magnetic circuits, and NML in this specific research, have also some important drawbacks that need to be addressed: first, the circuit clock frequency is limited to 100 MHz, to avoid errors in data propagation; second, there is a connection between circuit layout and timing, and in particular, longer wires will have longer latency. These drawbacks are intrinsic to the technology and for this reason they cannot be avoided. The only chance is to limit their impact from an architectural point of view.

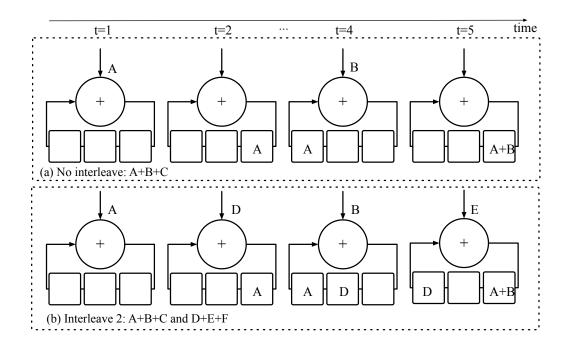

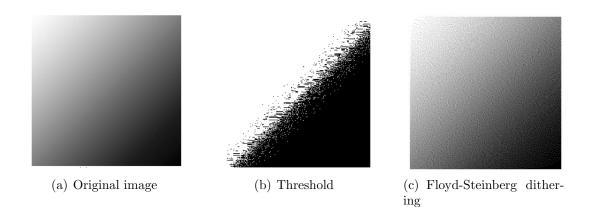

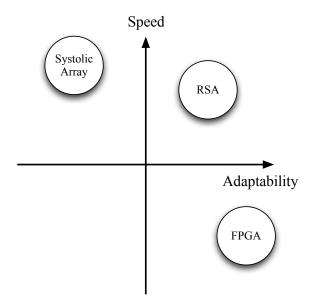

The first step followed in the research path of this thesis is indeed the choice and optimization of architectures able to deal with the problems of NML. Systolic Arrays are identified as an ideal solution for this technology, because they are regular structures with local interconnections that limit the long latency of wires; moreover they are composed of several Processing Elements that work in parallel, thus exploit parallelization to increase throughput (limiting the impact of the low clock frequency). Through the analysis of Systolic Arrays for NML, several possible improvements have been identified and addressed: 1) it has been defined a rigorous way to increase throughput with interleaving, providing equations that allow to estimate the number of operations to be interleaved and the rules to provide inputs; 2) a latency insensitive circuit has been designed, that exploits a data communication protocol between processing elements to avoid data synchronization problems. This feature has been exploited to design a latency insensitive Systolic Array that is able to execute the Floyd-Steinberg dithering algorithm. All the improvements presented in this framework apply to Systolic Arrays implemented in any technology. So, they can also be exploited to increase performance of today's CMOS parallel circuits. This research path is presented in Chapter 3.

While Systolic Arrays are an interesting solution for NML, their usage could be quite limited because they are normally application-specific. The second research path addresses this problem. A Reconfigurable Systolic Array is presented, that can be programmed to execute several algorithms. This architecture has been tested implementing many algorithms, including FIR and IIR filters, Discrete Cosine Transform and Matrix Multiplication. This research path is presented in Chapter 4.

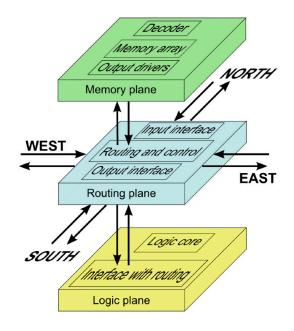

In common Von Neumann architectures, the logic part of the circuit and the memory one are separated. Today bus communication between logic and memory represents the bottleneck of the system. This problem is addressed presenting Logic-In-Memory (LIM), an architecture where memory elements are merged in logic ones. This research path aims at defining a real LIM architectures. This has been done in two steps. The first step is represented by an architecture composed of three layers: memory, routing and logic. In the second step instead the routing plane is no more present, and its features are inherited by the memory plane. In this solution, a pyramidal memory model is used, where memories near logic elements contain the most probably used data, and other memory layers contain the remaining data and instruction set. This circuit has been tested with odd-even sort algorithms and it has been benchmarked against GPUs and ASIC. This research path is presented in Chapter 5.

MagnetoElastic NML (ME-NML) is a technological improvement of the NML principle, proposed by researchers of Politecnico di Torino, where the clock system is based on the induced stretch of a piezoelectric substrate when a voltage is applied to its boundaries. The main advantage of this solution is that it consumes much less power than the classic clock implementation. This technology has not yet been investigated from an architectural point of view and considering complex circuits. In this research field, a standard methodology for the design of ME-NML circuits has been proposed. It is based on a Standard Cell Library and an enhanced VHDL model. The effectiveness of this methodology has been proved designing a Galois Field Multiplier. Moreover the serial-parallel trade-off in ME-NML has been investigated, designing three different solutions for the Multiply and Accumulate structure. This research path is presented in Chapter 6.

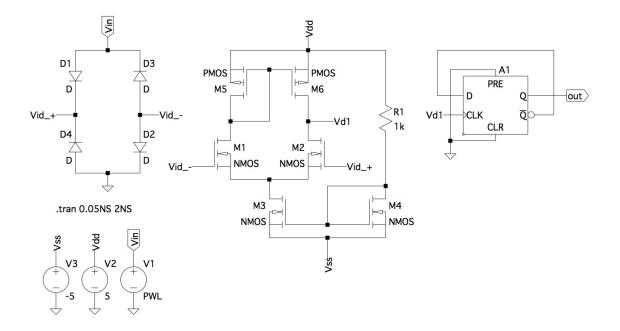

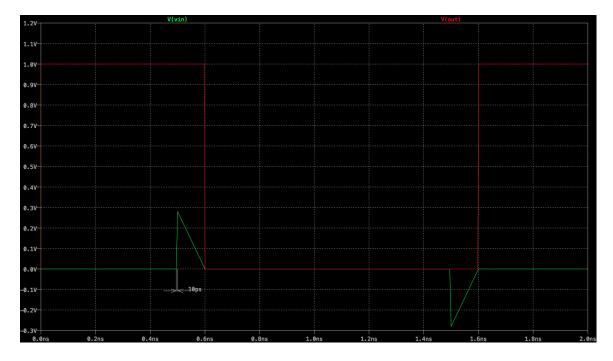

While ME-NML is an extremely interesting technology, it needs to be combined with other faster technologies to have a real competitive system. Signal interfaces between NML and other technologies (mainly CMOS) have been rarely presented in literature. A mixed-technology multiplexer is designed and presented as the basis for a CMOS to NML interface. The reverse interface (from ME-NML to CMOS) is instead based on a sensing circuit for the Faraday effect: a change in the polarization of a magnet induces an electric field that can be used to generate an input signal for a CMOS circuit. This research path is presented in Chapter 7.

The research work presented in this thesis represents a fundamental milestone in the path towards nanotechnologies. The most important achievement is the design and simulation of complex circuits with NML, benchmarking this technology with real application examples. The characterization of a technology considering complex functions is a major step to be performed and that has not yet been addressed in literature for NML. Indeed, only in this way it is possible to intercept in advance any weakness of NanoMagnet Logic that cannot be discovered considering only small circuits. Moreover, the architectural improvements introduced in this thesis, although technology-driven, can be actually applied to any technology. We have demonstrated the advantages that can derive applying them to CMOS circuits. This thesis represents therefore a major step in two directions: the first is the enhancement of NML technology; the second is a general improvement of parallel architectures and the development of the new Logic-In-Memory paradigm.

# Contents

| Su       | mma | ary     |                                                                                                       | II |

|----------|-----|---------|-------------------------------------------------------------------------------------------------------|----|

| 1        | Mot | ivatior | n                                                                                                     | 1  |

| <b>2</b> |     | 0       | ical Background                                                                                       | 6  |

|          | 2.1 |         | $S$ scaling $\ldots$ | 6  |

|          | 2.2 |         | um-Dot Cellular Automata (QCA)                                                                        | 7  |

|          |     | 2.2.1   | Signal propagation and Clock                                                                          | 9  |

|          | 2.3 | NanoN   | Iagnet Logic                                                                                          | 9  |

|          |     | 2.3.1   | Logic Gates                                                                                           | 11 |

|          |     | 2.3.2   | Magnetic Clock NML                                                                                    | 12 |

|          |     |         | 2.3.2.1 Snake Clock Layout                                                                            | 13 |

|          |     |         | 2.3.2.2 Working frequency                                                                             | 15 |

|          |     | 2.3.3   | Magnetoelastic Clock NML (ME-NML)                                                                     | 16 |

|          |     |         | 2.3.3.1 Circuit Layout                                                                                | 18 |

|          |     | 2.3.4   | Intrinsic Pipeline                                                                                    | 19 |

|          |     | 2.3.5   | Summary on NanoMagnet Logic                                                                           | 20 |

| Ι        |     |         | Architectures for NanoMagnet Logic                                                                    | 23 |

| 3        | •   |         | rrays Optimization                                                                                    | 25 |

|          | 3.1 |         | uction to Systolic Arrays                                                                             |    |

|          |     | 3.1.1   | Systolic Arrays for NanoMagnet Logic                                                                  | 27 |

|          | 3.2 |         | nterleaving in Systolic Arrays                                                                        | 28 |

|          |     | 3.2.1   | Interleaving Technique                                                                                | 28 |

|          |     | 3.2.2   | Proposed SA Taxonomy                                                                                  | 30 |

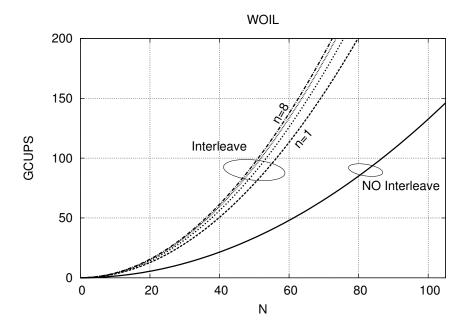

|          |     |         | 3.2.2.1 WOIL Systolic Arrays                                                                          |    |

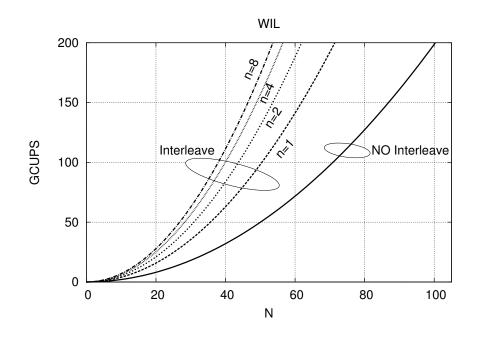

|          |     |         | 3.2.2.2 WIL Systolic Arrays                                                                           |    |

|          |     | 3.2.3   | WOIL SA Optimization                                                                                  |    |

|          |     | 3.2.4   | WIL SA Optimization                                                                                   | 33 |

|          |     | 3.2.5            | Results                                    | 34         |

|----------|-----|------------------|--------------------------------------------|------------|

|          |     |                  | 3.2.5.1 WOIL Systolic Arrays results       | 35         |

|          |     |                  | 3.2.5.2 WIL Systolic Arrays results        | 36         |

|          |     | 3.2.6            | Data Interleaving in CMOS and NML          | 38         |

|          | 3.3 | Laten            | cy Insensitive Systolic Arrays             | 39         |

|          |     | 3.3.1            | Motivation                                 | 39         |

|          |     | 3.3.2            | Proposed Communication Protocol            | 40         |

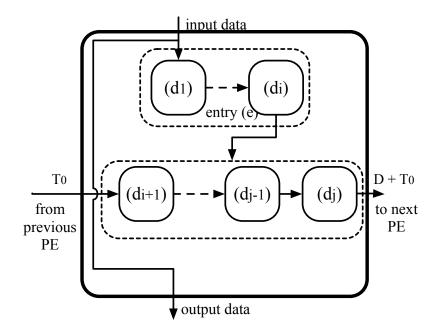

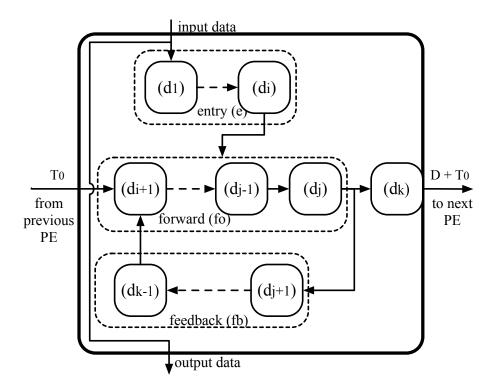

|          |     | 3.3.3            | Latency Insensitive PE                     | 42         |

|          |     |                  | 3.3.3.1 Algorithm Block                    | 43         |

|          |     |                  | 3.3.3.2 I/O Blocks                         | 44         |

|          |     |                  | 3.3.3.3 Communication Block                | 44         |

|          |     | 3.3.4            | Application Example: Matrix Multiplication | 46         |

|          |     |                  | 3.3.4.1 Serial Booth Multiplier            | 47         |

|          | 3.4 | Systol           | ic Array for the Floyd-Steinberg algorithm | 48         |

|          |     | 3.4.1            | Floyd-Steinberg Algorithm                  | 48         |

|          |     | 3.4.2            | Latency Insensitive Implementation         | 50         |

|          |     | 3.4.3            | Simulation                                 | 51         |

|          | 3.5 | Final            | Remarks                                    | 52         |

| 4        | Boc | onfigu           | rable Systolic Array                       | <b>54</b>  |

| т        | 4.1 | -                | ation                                      | <b>5</b> 4 |

|          | 1.1 | 4.1.1            | Limits of Systolic Arrays                  | 55         |

|          |     | 4.1.2            | The Reconfigurable approach                | 55         |

|          |     | 4.1.3            | Existing Reconfigurable architectures      | 57         |

|          | 4.2 | Propo            | sed Reconfigurable Systolic Array          | 58         |

|          |     | 4.2.1            | Architecture                               | 58         |

|          |     | 4.2.2            | Preloading Phase                           | 61         |

|          |     | 4.2.3            | Results in CMOS and NML                    | 61         |

|          | 4.3 | Algori           | thms                                       | 64         |

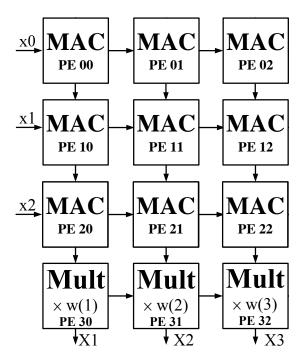

|          |     | 4.3.1            | Matrix Multiplication                      | 65         |

|          |     | 4.3.2            | Discrete Cosine Transform (DCT)            | 66         |

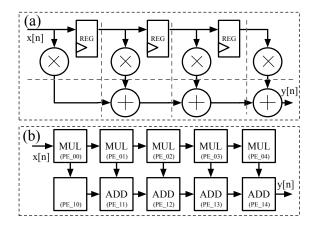

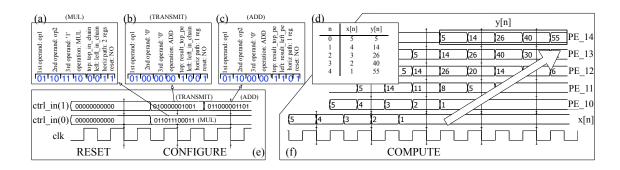

|          |     | 4.3.3            | FIR Filters                                | 66         |

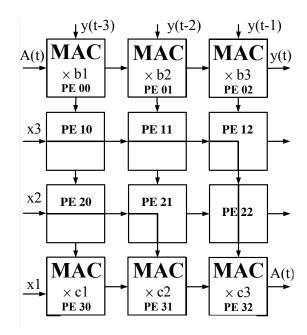

|          |     | 4.3.4            | IIR Filters                                | 69         |

|          |     | 4.3.5            | RSA Configurator                           | 71         |

|          | 4.4 | Final            | Remarks                                    | 72         |

| <b>5</b> | Log | ic-In-N          | Летоту                                     | <b>74</b>  |

| -        | 5.1 |                  | $\mathbf{pt}$                              | 75         |

|          |     | 5.1.1            | Limit of Von-Neumann Architecture          | 75         |

|          |     | -                |                                            |            |

|          |     | 5.1.2            | Other Parallel Architectures               | 76         |

|          |     | $5.1.2 \\ 5.1.3$ | Other Parallel Architectures               | 76<br>79   |

|         | 5.2                  | LIM 1.                                                                                               | 0 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 80                                                                                                                                                                        |

|---------|----------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                      | 5.2.1                                                                                                | Routing Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 82                                                                                                                                                                        |

|         |                      |                                                                                                      | 5.2.1.1 The input interface $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 82                                                                                                                                                                        |

|         |                      |                                                                                                      | 5.2.1.2 The selection unit $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 83                                                                                                                                                                        |

|         |                      |                                                                                                      | 5.2.1.3 The output interface $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 83                                                                                                                                                                        |

|         |                      | 5.2.2                                                                                                | Logic Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 85                                                                                                                                                                        |

|         |                      |                                                                                                      | 5.2.2.1 Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 85                                                                                                                                                                        |

|         |                      |                                                                                                      | 5.2.2.2 Cell Logic Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 85                                                                                                                                                                        |

|         |                      | 5.2.3                                                                                                | Memory Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 85                                                                                                                                                                        |

|         |                      | 5.2.4                                                                                                | Operation Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 86                                                                                                                                                                        |

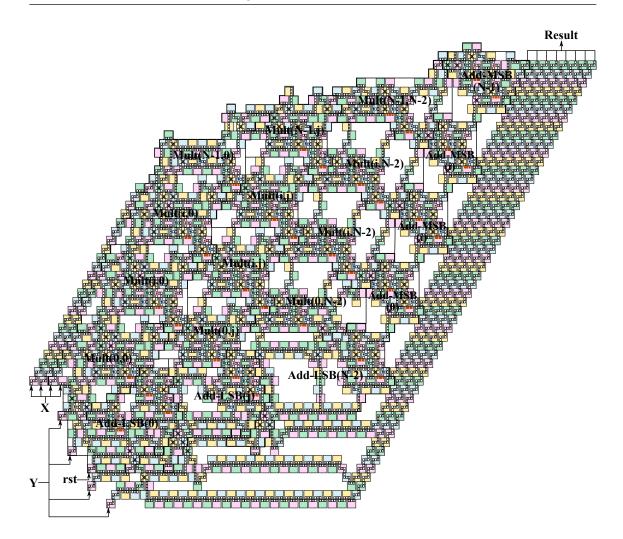

|         | 5.3                  | LIM 2.                                                                                               | 0 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 87                                                                                                                                                                        |

|         |                      | 5.3.1                                                                                                | Improvement Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 87                                                                                                                                                                        |

|         |                      | 5.3.2                                                                                                | Pyramidal Memory Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 88                                                                                                                                                                        |

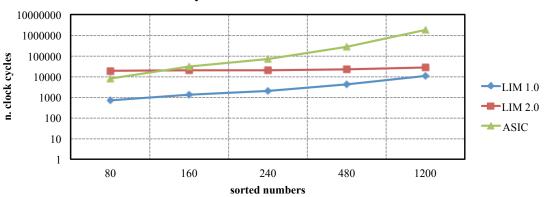

|         | 5.4                  | Results                                                                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 90                                                                                                                                                                        |

|         |                      | 5.4.1                                                                                                | Test Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 91                                                                                                                                                                        |

|         |                      | 5.4.2                                                                                                | Results Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 91                                                                                                                                                                        |

|         | 5.5                  | Final F                                                                                              | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 94                                                                                                                                                                        |

| тт      | - <b>N</b> /         | Ingrad                                                                                               | oFlagtic NML Circuit Degign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 07                                                                                                                                                                          |

| 11      |                      | Iagnet                                                                                               | oElastic NML Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97                                                                                                                                                                          |

| 11<br>6 |                      | ign Rul                                                                                              | les for ME-NML Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 99                                                                                                                                                                          |

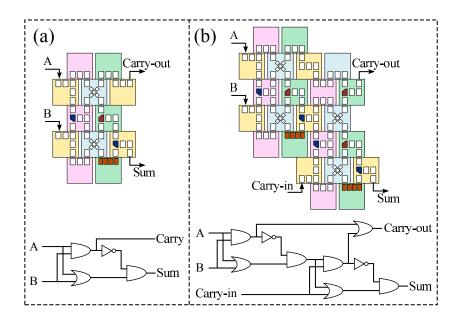

|         |                      | <b>ign Ru</b> l<br>Standa                                                                            | les for ME-NML Circuits<br>rd Cell Approach for ME-NML Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>99</b><br>. 100                                                                                                                                                          |

|         | $\operatorname{Des}$ | <b>ign Ru</b> l<br>Standa<br>6.1.1                                                                   | les for ME-NML Circuits<br>rd Cell Approach for ME-NML Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>99</b><br>. 100<br>. 100                                                                                                                                                 |

|         | $\operatorname{Des}$ | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2                                                          | les for ME-NML Circuits<br>rd Cell Approach for ME-NML Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>99</b><br>. 100<br>. 100<br>. 103                                                                                                                                        |

|         | $\operatorname{Des}$ | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2                                                          | les for ME-NML Circuits<br>rd Cell Approach for ME-NML Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>99</b><br>. 100<br>. 100<br>. 103<br>. 103                                                                                                                               |

|         | $\operatorname{Des}$ | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2                                                          | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1         Generic parameters         6.1.2.2         Logic Behavior of the Cell                                                                                                                                                                                                                                                                                                                                      | <b>99</b><br>. 100<br>. 100<br>. 103<br>. 103<br>. 104                                                                                                                      |

|         | $\operatorname{Des}$ | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2                                                          | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1         Generic parameters         6.1.2.2         Logic Behavior of the Cell         6.1.2.3         Area and Energy                                                                                                                                                                                                                                                                                              | <b>99</b><br>. 100<br>. 100<br>. 103<br>. 103<br>. 104<br>. 104                                                                                                             |

|         | $\operatorname{Des}$ | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2                                                          | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1         Generic parameters         6.1.2.2         Logic Behavior of the Cell         6.1.2.3         Area and Energy         6.1.2.4                                                                                                                                                                                                                                                                              | <b>99</b><br>. 100<br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 107                                                                                                    |

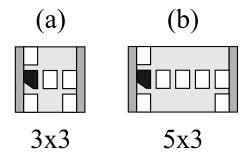

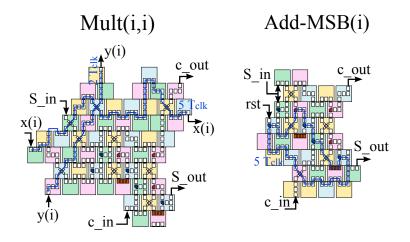

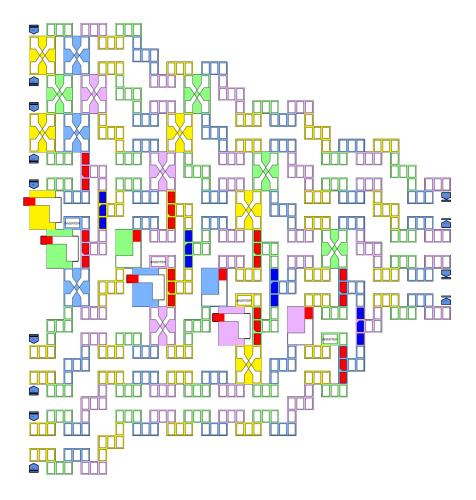

|         | <b>Des</b><br>6.1    | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3                                                 | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1         Generic parameters         6.1.2.2         Logic Behavior of the Cell         6.1.2.3         Area and Energy         6.1.2.4         Hierarchical model         Circuit layout                                                                                                                                                                                                                            | <ul> <li>99</li> <li>100</li> <li>103</li> <li>103</li> <li>104</li> <li>104</li> <li>107</li> <li>109</li> </ul>                                                           |

|         | $\operatorname{Des}$ | <b>ign Rul</b><br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit                                       | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1         Generic parameters         6.1.2.2         Logic Behavior of the Cell         6.1.2.3         Area and Energy         6.1.2.4         Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier                                                                                                                                                                            | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110                                                                                  |

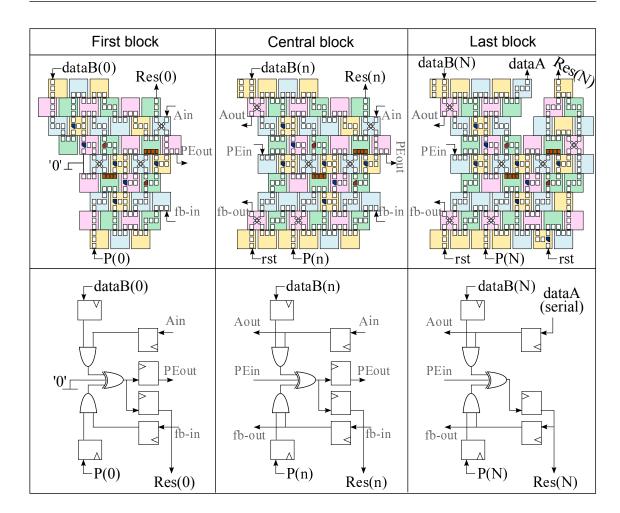

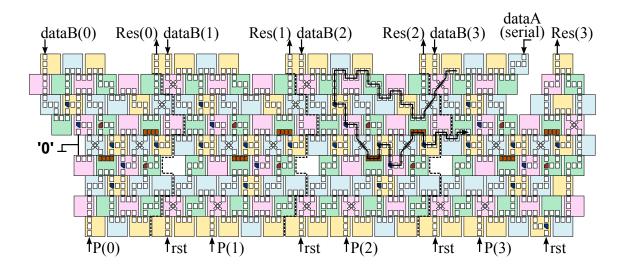

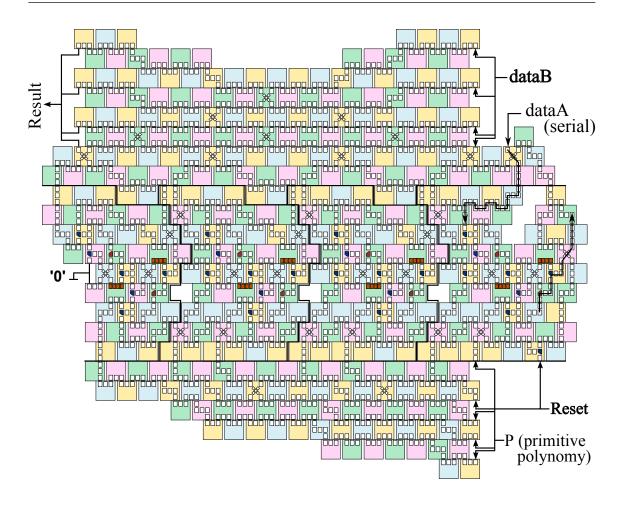

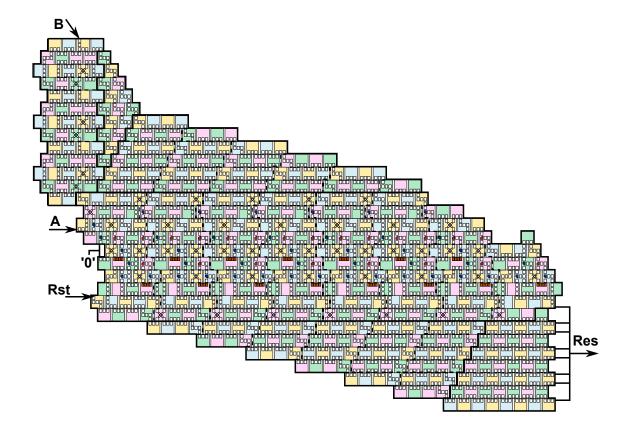

|         | <b>Des</b><br>6.1    | <b>ign Rul</b><br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit                                       | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit                                                                                                                                                                    | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111                                                                         |

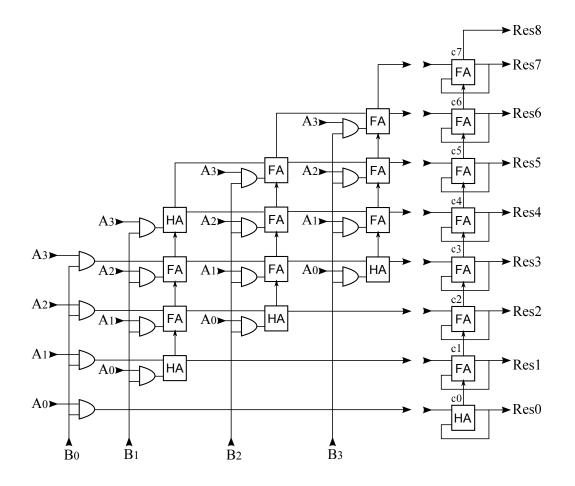

|         | <b>Des</b><br>6.1    | <b>ign Rul</b><br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1                              | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         6.2.1.1 Galois Field Multiplier scheme                                                                                                                                                             | <pre>99 . 100 . 100 . 103 . 103 . 104 . 104 . 107 . 109 . 110 . 111 . 112</pre>                                                                                             |

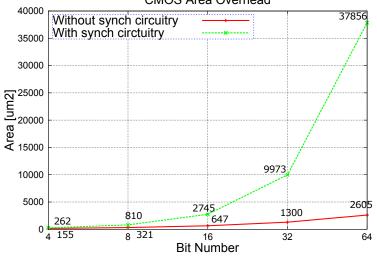

|         | <b>Des</b><br>6.1    | <b>ign Rul</b><br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2                     | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         6.2.1.1 Galois Field Multiplier scheme         CMOS Implementation                                                                                                                                 | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113                                                       |

|         | <b>Des</b><br>6.1    | <b>ign Ru</b> l<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2<br>6.2.3           | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit         CMOS Implementation                                                                                                                                        | <pre>99 . 100 . 100 . 103 . 103 . 104 . 104 . 107 . 109 . 110 . 111 . 112 . 113 . 115</pre>                                                                                 |

|         | <b>Des</b><br>6.1    | ign Rul<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4          | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit         6.2.1.1 Galois Field Multiplier scheme         MDL Multiplier circuit         MUL Implementation         ME-NML Implementation                             | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 115<br>. 116                                     |

|         | <b>Des</b><br>6.1    | ign Rul<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5 | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit         6.2.1.1 Galois Field Multiplier scheme         CMOS Implementation         NML Implementation         ME-NML Implementation                                | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 115<br>. 116<br>. 120                            |

|         | <b>Des</b><br>6.1    | ign Rul<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5 | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit         6.2.1.1 Galois Field Multiplier scheme         MML Implementation         ME-NML Implementation         ME-NML Implementation         6.2.5.1 CMOS Results | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 115<br>. 116<br>. 120<br>. 121                   |

|         | <b>Des</b><br>6.1    | ign Rul<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5 | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit         CMOS Implementation         NML Implementation         ME-NML Implementation         Results         6.2.5.1 CMOS Results                                  | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 103<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 115<br>. 116<br>. 120<br>. 121<br>. 122          |

|         | <b>Des</b><br>6.1    | ign Rul<br>Standa<br>6.1.1<br>6.1.2<br>6.1.3<br>Circuit<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5 | les for ME-NML Circuits         rd Cell Approach for ME-NML Circuits         Standard Cells Library         VHDL Model for ME-NML Circuits Design         6.1.2.1 Generic parameters         6.1.2.2 Logic Behavior of the Cell         6.1.2.3 Area and Energy         6.1.2.4 Hierarchical model         Circuit layout         Design Example: Galois Field Multiplier         Galois Field Multiplier circuit         6.2.1.1 Galois Field Multiplier scheme         MML Implementation         ME-NML Implementation         ME-NML Implementation         6.2.5.1 CMOS Results | <b>99</b><br>. 100<br>. 103<br>. 103<br>. 103<br>. 104<br>. 104<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 115<br>. 116<br>. 120<br>. 121<br>. 122<br>. 125 |

| 8<br>A | Cor  | 7.2.1<br>7.2.2<br>Final | 7.1.2.1       RSA with Mixed Technology Multiplexer         nological Interfaces          From CMOS to ME-NML          From ME-NML to CMOS          7.2.2.1       Signal Transduction         7.2.2.2       CMOS bridge         Remarks          ms         ablications | 15<br>15<br>15<br>15<br>15<br>15<br>16                              |

|--------|------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 8      | 7.3  | 7.2.1<br>7.2.2<br>Final | nological Interfaces                                                                                                                                                                                                                                                    | 15 $     15 $ $     15 $ $     15 $ $     15 $ $     16 $ $     16$ |

|        |      | 7.2.1<br>7.2.2          | Nological InterfacesFrom CMOS to ME-NMLFrom ME-NML to CMOS7.2.2.1Signal Transduction7.2.2.2CMOS bridge                                                                                                                                                                  | 15<br>15<br>15<br>15<br>15<br>15<br>16                              |

|        |      | 7.2.1<br>7.2.2          | Nological InterfacesFrom CMOS to ME-NMLFrom ME-NML to CMOS7.2.2.1Signal Transduction7.2.2.2CMOS bridge                                                                                                                                                                  | 15<br>15<br>15<br>15<br>15<br>15<br>16                              |

|        | 7.2  | 7.2.1                   | rological Interfaces          From CMOS to ME-NML          From ME-NML to CMOS          7.2.2.1       Signal Transduction                                                                                                                                               | 15<br>15<br>15<br>15<br>15                                          |

|        | 7.2  | 7.2.1                   | nological Interfaces                                                                                                                                                                                                                                                    | 15<br>15<br>15<br>15                                                |

|        | 7.2  |                         | ological Interfaces                                                                                                                                                                                                                                                     | 15<br>15                                                            |

|        | 7.2  | Techn                   | 00 I                                                                                                                                                                                                                                                                    | 15                                                                  |

|        |      |                         | 7.1.2.1 RSA with Mixed Technology Multiplexer                                                                                                                                                                                                                           |                                                                     |

|        |      |                         |                                                                                                                                                                                                                                                                         | 10                                                                  |

|        |      | 7.1.2                   | Circuit Layout                                                                                                                                                                                                                                                          |                                                                     |

|        | 1.1  | 7.1.1                   | -                                                                                                                                                                                                                                                                       |                                                                     |

| 7      | 7.1  |                         | E-NML/CMOS Circuits                                                                                                                                                                                                                                                     | $15 \\ 15$                                                          |

| 7      | זע:- | rad N/D                 | E NML (CMOS Circuita                                                                                                                                                                                                                                                    | 1 P                                                                 |

|        | 6.4  | Final                   | Remarks                                                                                                                                                                                                                                                                 |                                                                     |

|        |      |                         | 6.3.4.4 Results Comparison                                                                                                                                                                                                                                              |                                                                     |

|        |      |                         | 6.3.4.3 Serial MAC Results                                                                                                                                                                                                                                              |                                                                     |

|        |      |                         | 6.3.4.2 Serial-Parallel MAC Results                                                                                                                                                                                                                                     |                                                                     |

|        |      | 0.3.4                   | 6.3.4.1 Parallel MAC Results                                                                                                                                                                                                                                            |                                                                     |

|        |      | 6.3.4                   | 6.3.3.4 Timing analisys                                                                                                                                                                                                                                                 |                                                                     |

|        |      |                         | 6.3.3.3 ME-NML implementation                                                                                                                                                                                                                                           |                                                                     |

|        |      |                         | 6.3.3.2 Serial MAC with shared Accumulator                                                                                                                                                                                                                              |                                                                     |

|        |      |                         | 6.3.3.1 Serial MAC scheme                                                                                                                                                                                                                                               |                                                                     |

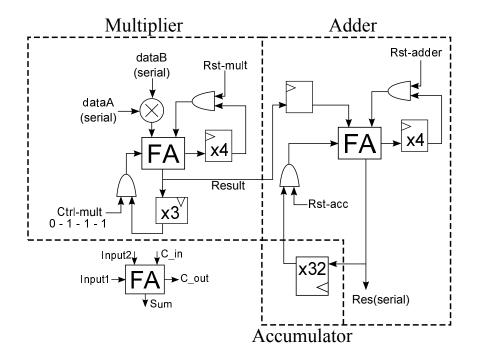

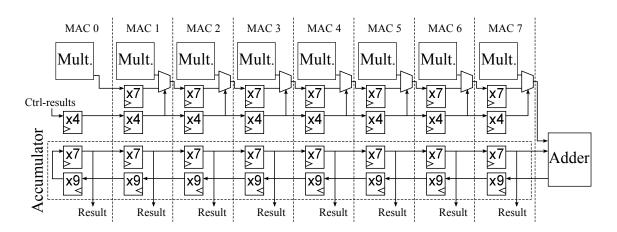

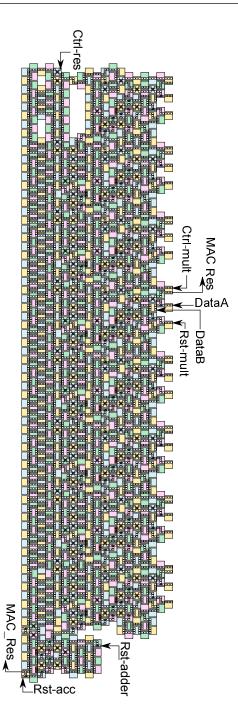

|        |      | 6.3.3                   | Serial MAC Unit                                                                                                                                                                                                                                                         | 14                                                                  |

|        |      |                         | 6.3.2.3 Timing analysis                                                                                                                                                                                                                                                 |                                                                     |

|        |      |                         | 6.3.2.2 ME-NML implementation                                                                                                                                                                                                                                           |                                                                     |

|        |      | 0.0.2                   | 6.3.2.1 Circuit scheme                                                                                                                                                                                                                                                  |                                                                     |

|        |      | 6.3.2                   | Serial-Parallel MAC Unit                                                                                                                                                                                                                                                |                                                                     |

|        |      |                         | 6.3.1.3 Timing Analysis                                                                                                                                                                                                                                                 |                                                                     |

|        |      |                         | 6.3.1.1Circuit Scheme                                                                                                                                                                                                                                                   |                                                                     |

|        |      | 6.3.1                   | Parallel MAC Unit                                                                                                                                                                                                                                                       | 10                                                                  |

|        |      | 601                     | Denallal MAC Unit                                                                                                                                                                                                                                                       | I                                                                   |

# Chapter 1

## Motivation

This Chapter explains the motivations that guided me through research path described in this Thesis.

Over the past three decades, the constant evolution of electronics has been founded on the ever-smaller device dimensions of silicon-based CMOS technology. CMOS has exponentially improved in both performance and density of integration, producing the transistor trend described by Moore's law. Today, however, the conventional physical scaling is slowing down. As forecasted in the International Technology Roadmap for Semiconductors [1], CMOS scaling is expected to reach its boundaries soon, probably marking the end of CMOS era. Scaling in CMOS cannot continue forever for two main reasons: 1) the minimum achievable dimensions is in any case limited; 2) the off-state leakage power is increasing with device shrinking. We will describe in next Chapter with more details the physical limitations that CMOS is encountering. With these limitations, it seems to be clear that CMOS will not be the leading technology in the next 20 years, because it cannot keep-up with improvements expected by Moore's law.

The negative effects of CMOS scaling have been already addressed from an architectural point of view: parallel architectures have been introduced in CMOS to avoid an excessive increase of clock speed leading to too high power consumption. Therefore, in this framework, where architectural solutions have already been explored, the only chance to keep-up with Moore's law is to address these limitations from a technological point of view. This happened in past decades when technology shifted from BJT to CMOS transistors, and more recently with the introduction of 3D transistors. Today, one of the most important challenges of VLSI and technology researchers is to find a valid alternative that could substitute CMOS in next years.

Several technologies are currently under study. The International Technology Roadmap for Semiconductors (ITRS) [1] summarizes some of them, among which Quantum-dot Cellular Automata (QCA) and its magnetic implementation Nano Magnetic Logic (NML). NML is particularly interesting for its physical features: a magnetic circuit does not have leakage power consumption, and magnets have an intrinsic memory capability. Therefore, NanoMagnet Logic could be an important solution to reduce power consumption (and area occupation), that are the main drivers of today logic circuit design. The most important drawback of magnetic circuits is the low clock frequency achievable (hundreds of MegaHertz). Another limitation of this kind of circuits is that the layout influences the timing characteristics of the circuit. Indirectly, long wires have long latency. A complete description of NML technology is given in Section 2.3.

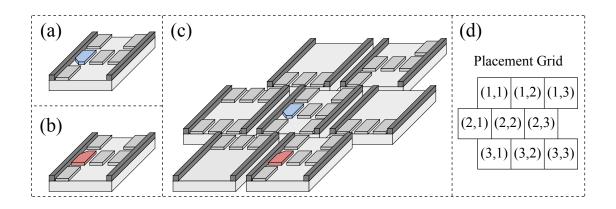

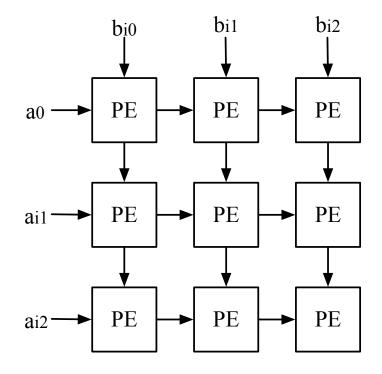

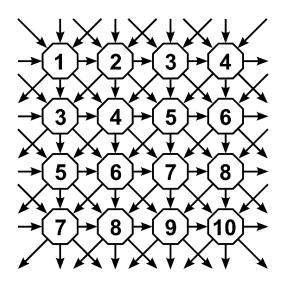

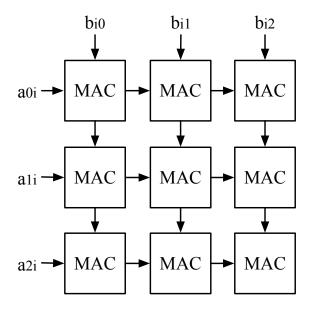

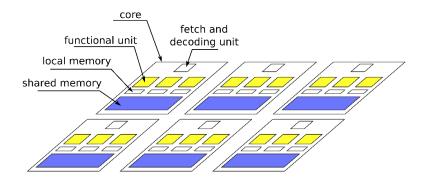

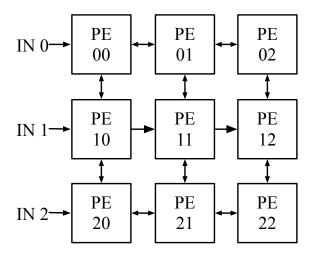

The approach here followed is to design logic circuits in NML, addressing the limitations that this technology has nowadays from an architectural point of view. We will explain in detail in Chapter 3 that Systolic Arrays can be an ideal architecture for NML technology. Systolic Arrays are parallel architectures made of identical and locally interconnected Processing Elements. In this way they can address the low clock frequency of NML, because the throughput is guaranteed with parallelization of tasks in several Processing Elements. At the same time the short local interconnections allow to reduce the long latency of wires problem.

We start introducing Systolic Arrays for NML and analyzing several alternatives to improve them. Then we consider another kind of architecture called Logic-In-Memory. In this way we push forward the research for NanoMagnet Logic architectures as it has never been done before. Indeed, literature presents only small architectures with few gates designed for NanoMagnet Logic. However, we believe that a correct and complete study of a technology shall be done taking into account real circuits that implement complex functions. This is the only possible way to intercept any limitation of the technology that can appear only when big circuits are considered. In fact, it is not at the device level that the features of a technology can be asserted. It is therefore necessary to analyze how NML behaves in real operating conditions (many cells with complex interconnections and complex algorithms).

NanoMagnet Logic and in general all post-CMOS proposed technologies are still under development. So, the technological solution is not definitive, yet it is already interesting for its preliminary results. For this reason it is worth working on NML in its actual state. It is probable that the technology will evolve with new features and different behaviors: for example considering Domain Wall interconnections, it could be possible to eliminate the long latency of wire problem. Therefore, it is important that the enhancements introduced with this research can be used also with other technologies. Without this assumption the work here presented may be useless in few years if the technology is modified.

In general, an architectural approach allows to refrain from the technology itself. In this way the improvement introduced thinking to the circuit in NML can also be applied to a CMOS circuit (or a circuit implemented in any other nanotechnology). All the improvements that we propose at architectural level are indeed applicable to CMOS and in several cases the effect on the current technology has also been asserted to show the achievable improvement.

The whole research activity is divided into two parts: the first deals with Parallel Architectures for NanoMagnet Logic; the second is focused on MagnetoElastic NML Circuit Design.

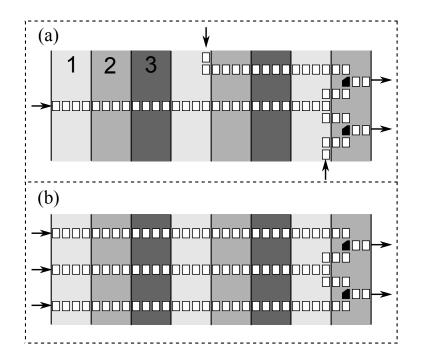

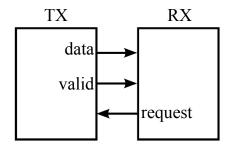

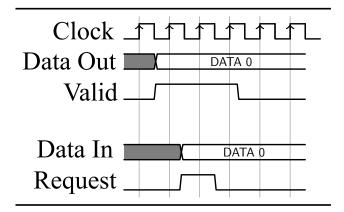

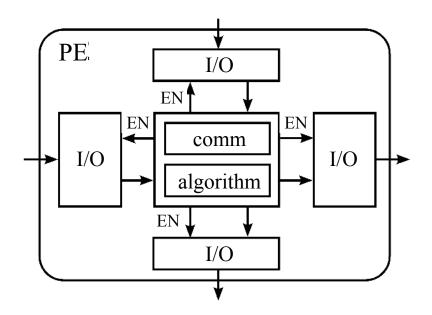

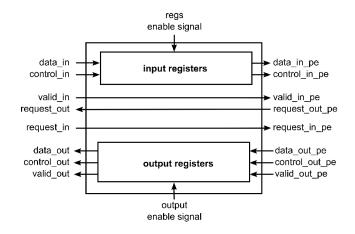

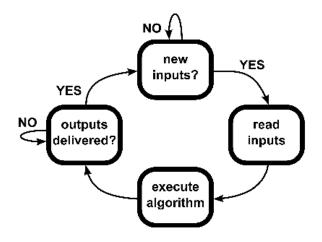

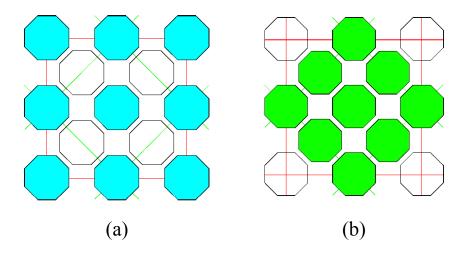

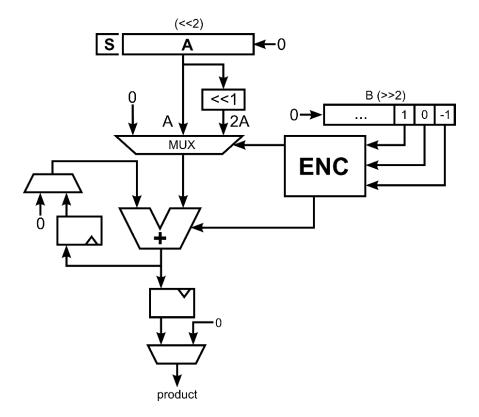

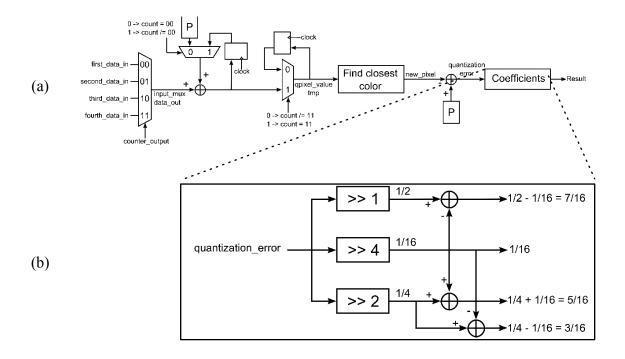

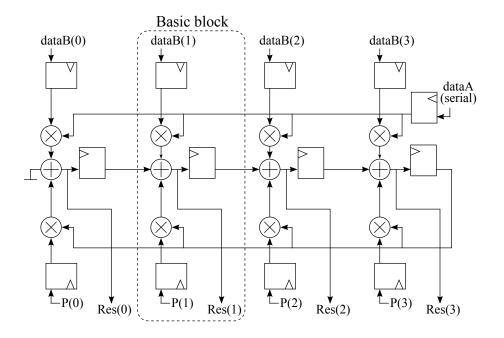

The first step in this architectural approach towards NML logic circuits has been the adaption of current existing solutions to overcome main limitations of this technology. Indeed, starting from technological constraints (long delay of wires and low clock frequency) architectures like Systolic Arrays have been identified as an ideal solution. The Systolic Array concept has been enriched with a "Pipeline Interleaving" concept based on input data feeding, that has been analyzed in detail and described with mathematical equations. This approach has been adapted also to CMOS circuits that can benefit from input interleaving. Moreover Systolic Arrays have been made latency-insensitive through a communication protocol among Processing Elements. In this way even if Processing Elements have different delays, the asynchronous communication protocol guarantees the correct circuit behavior. Finally to test this approach a real-case scenario has been identified, based on the Floyd-Steinberg dithering algorithm for image processing. This research path is described in Chapter 3.

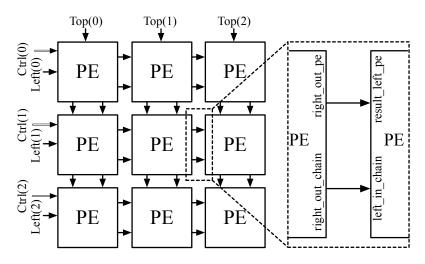

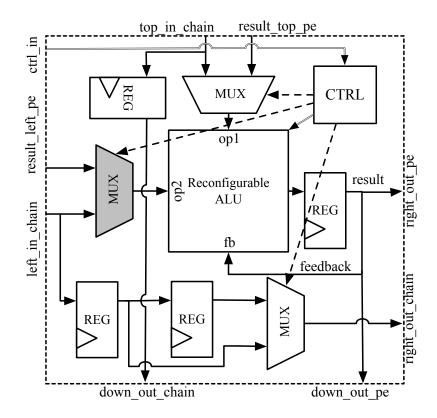

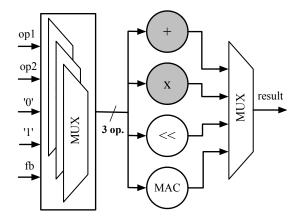

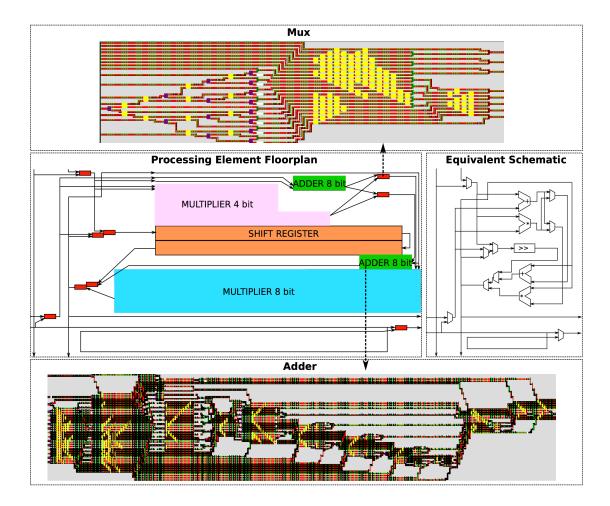

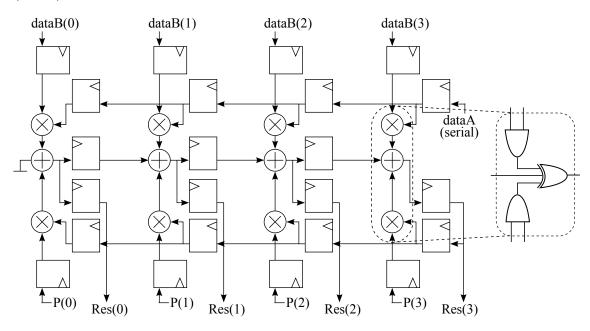

The second step has been the definition of a new Systolic Array that overcomes the main limitation of the original one, i.e. the algorithm-dependency. The Array has been made reconfigurable through new interfaces and functions inside each Processing Element. The reconfigurable Systolic Array has been mapped both in CMOS and NML technologies. Moreover, it has been tested with several algorithms to properly show the reconfigurability potentiality. Algorithms belong to real processing applications such as FIR and IIR filters. This research path is described in Chapter 4.

Finally other parallel architectures that exploit the Logic-In-Memory concept have been designed. In these kind of circuits, logic and memory can be mixed in the same device, overcoming the common bottleneck of today's systems in communication between ALU and memory. The Logic-In-Memory array was designed first as a 3-layered circuit (logic - routing - memory) and then as 2-layered circuit with a pipelined memory. Also in this case, a real application has been used to test these circuits: the Odd-Even Sort algorithm. Results show that this circuit can outperform both GPUs and ASIC when big datasets are considered. This research path is described in Chapter 5.

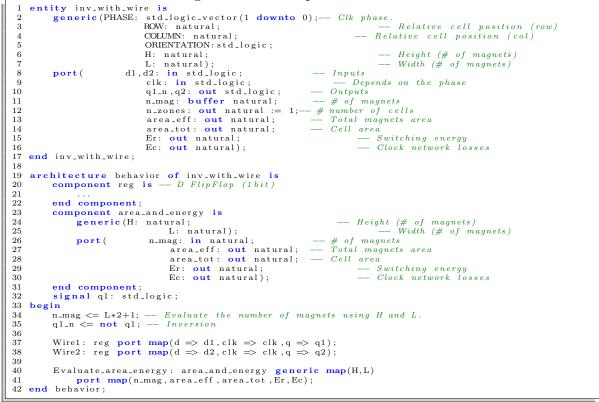

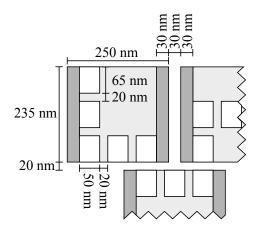

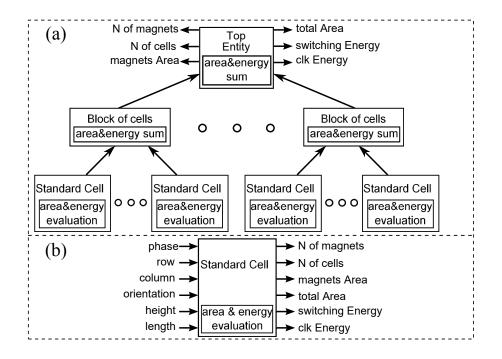

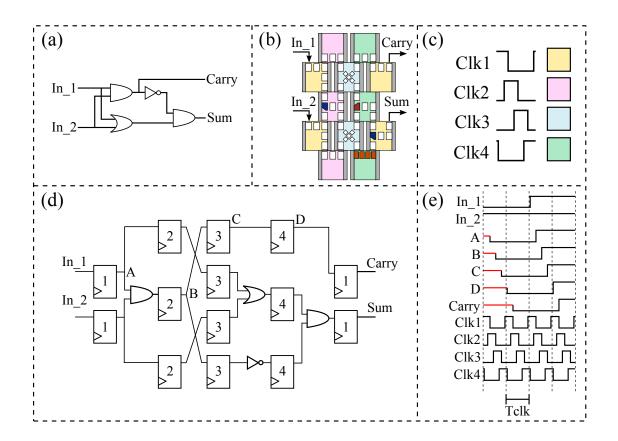

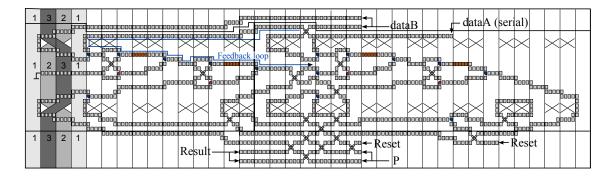

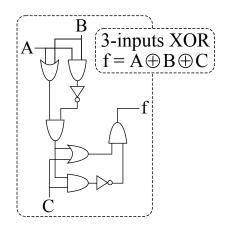

An important phase of the research has been tailored to the new technological solution proposed for NML clock, called MagnetoElastic NML (ME-NML) from our

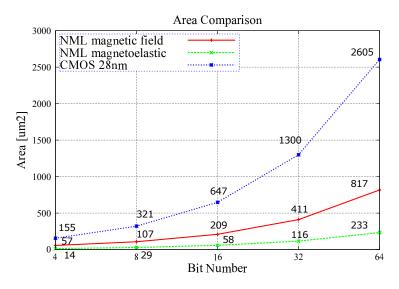

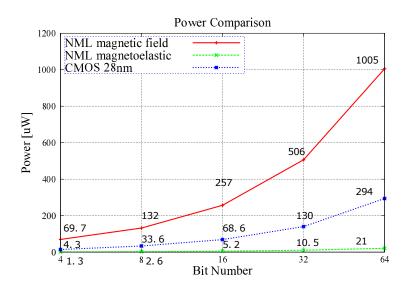

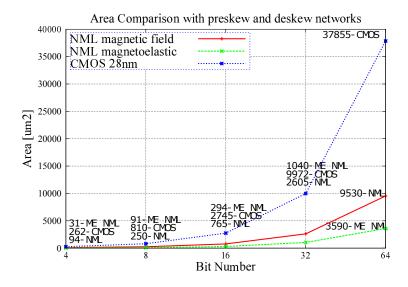

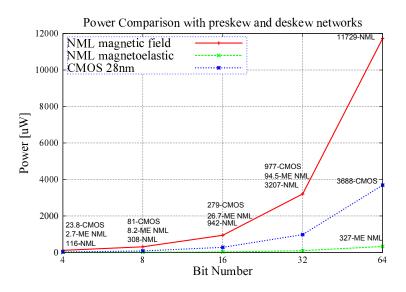

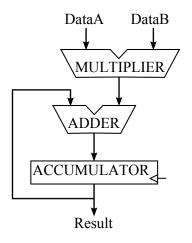

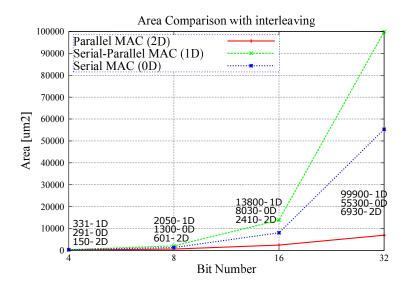

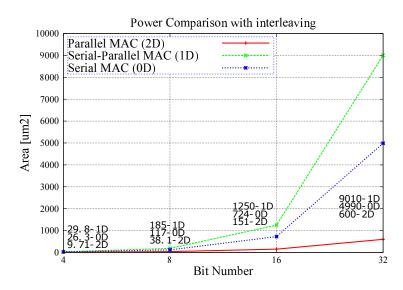

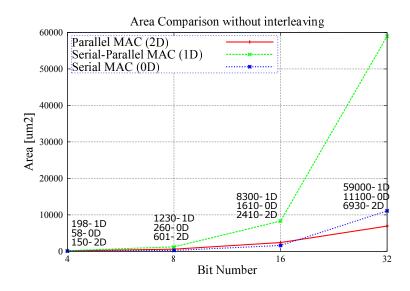

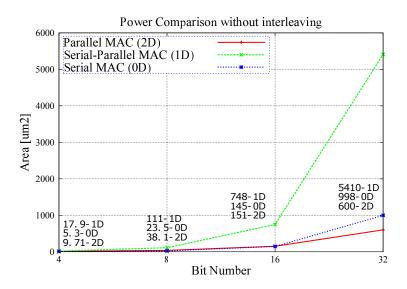

group. ME-NML has a quite different approach at circuital level with respect to classic NML. For this reason in this thesis we have defined: 1) a set of standard cells for these circuits and 2) a VHDL model that can be used to design and simulate ME-NML circuits. In addition, this VHDL model can compute area occupation and power dissipation of the circuit. To evaluate how well ME-NML performs when complex circuits are considered, we have designed a Galois Field Multiplier. Synthesis results are encouraging since ME-NML outperforms CMOS and classic NML in area and power dissipation. Finally we have analyzed the trade-off between Parallel and Serial circuits in ME-NML. While in CMOS the parallel solution is always the best one, in ME-NML this is not always true. For example the Galois Field Multiplier performs extremely well in ME-NML thanks to its partially parallel and partially serial input protocol. For this reason we have investigated in general parallel and serial solutions in ME-NML. We have used Multiply and Accumulate (MAC) as test circuit, thus exploiting this opportunity to introduce new ME-NML circuits never designed before. This research path is described in Chapter 6.

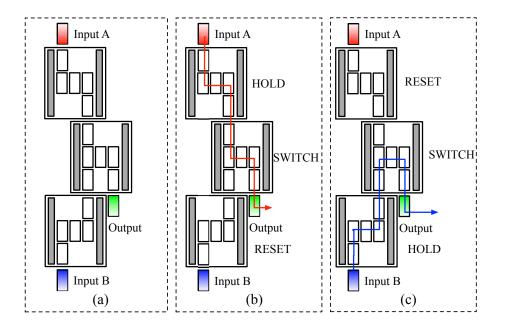

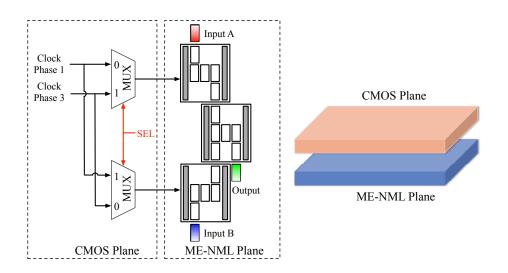

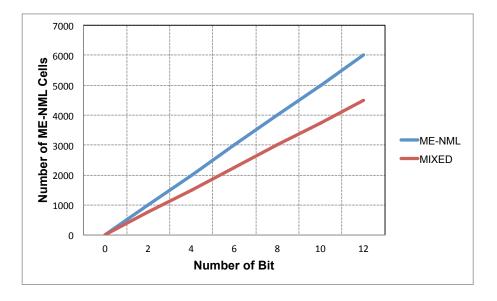

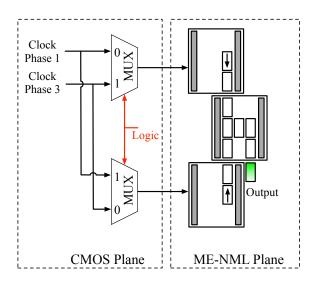

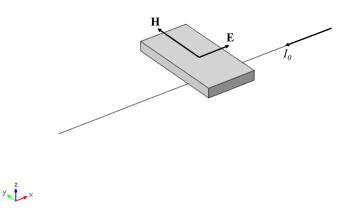

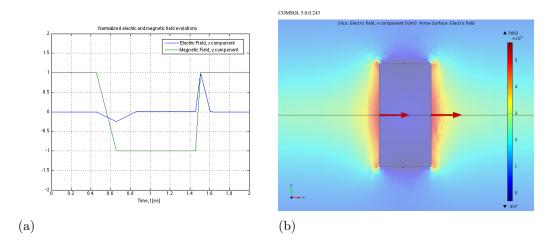

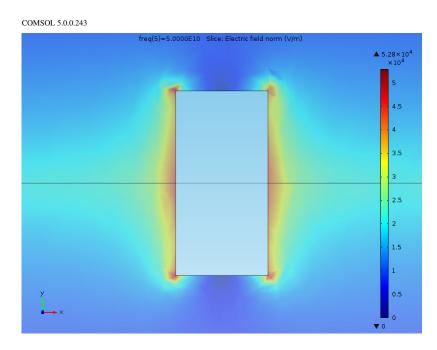

The Reconfigurable Systolic Array mentioned before has great features but also one important drawback: the high number of multiplexers used to reconfigure the array have a big impact on circuit area in NML. It was hence proposed a mixed architecture NML/CMOS for multiplexers, where a simple logic gate made by 3 NML cells is used to work as multiplexer with correct CMOS clock signals. Actually the multiplexer is moved to the CMOS plane instead of being in the NML one. While this approach has been successfully verified for MUX structures, it could be also extended to other gates to have a fully hybrid CMOS/NML circuit. The basis for this kind of circuits were laid identifying the readout circuit for NML and the command circuit for CMOS. This last research path is described in Chapter 7.

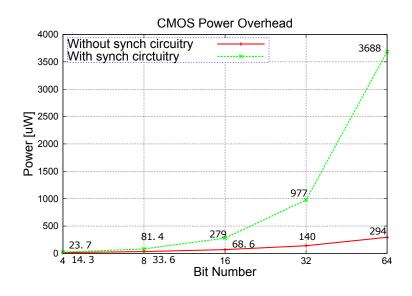

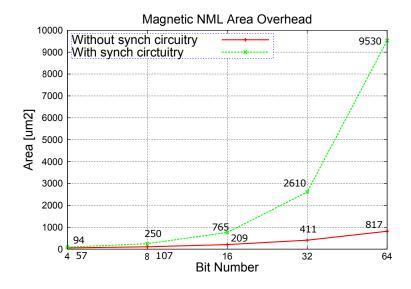

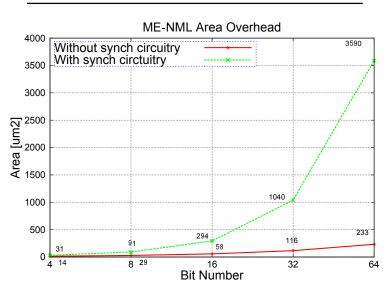

Before starting the description of the five research paths and their results, it is worth giving an advice. Throughout the thesis and in general during the research activities, several technological comparisons are presented (among CMOS and NML implementations). Usually this comparison is given in terms of area occupation and power dissipation. While in CMOS it is possible to obtain true and reliable estimations using Synopsys and Encounter, this is not true for NML. The only tools that we have to make a simple estimation of area and power are ToPoliNano for classic NML and a VHDL model developed ad-hoc for ME-NML. These two ways are neither official, nor tested against thousands of circuits as it is done for CMOS. It is then possible that the real numbers vary from those obtained for NML and ME-NML in our synthesis. It is also reasonable that changes in the technology itself may lead to circuits requiring less or more area, less or more power. At this moment it is not possible to state that one technology that outperforms CMOS in our tests will truly behave better in a real environment. Nevertheless, the comparison is still meaningful and important if seen in a different way: With our architectural approach, we want to intercept as soon as possible potential weaknesses of NML technology that cannot be discovered looking only at small circuits made of few cells. With this in mind, it is clear that if a technology has already worse performance than CMOS, it will probably not be the technology of the future. We will see that this is exactly the case of classic NML with magnetic clock. Differently, it is possible to identify if a technology is encouraging on one aspect and instead is performing worse on another aspect: in this way technologists can focus on the weak aspect and try to identify technological solutions in a precise scenario. The final consideration of this advice is that even if numbers are not reliable at 100%, it is still very important to analyze and compare them, to have a clearer idea of the characteristics of the technology when complex circuits are considered. An analysis of this kind is done in NML in this thesis, and similarly it is done on other technologies by other researchers.

## Chapter 2

## **Technological Background**

### 2.1 CMOS scaling

Over the past three decades, the constant evolution of electronics has been founded on the ever-smaller device dimensions of silicon-based CMOS technology. CMOS has exponentially improved in both performance and density of integration, producing the transistor trend explicited in Moore's law. Today, however, the conventional physical scaling is slowing down. As forecasted in the International Technology Roadmap for Semiconductors [1], it is expected to reach its boundaries soon, probably marking the end of CMOS era.

CMOS decay is due to several factors [2], mainly due to physical and material limits. Basically, both electrostatics and tunneling mechanisms cause leakage current increase in ultra-small MOSFETs, till it has become comparable to the drain current. The increased leakage current negates the threshold and supply voltages reduction, denying a speed increase. These are some of the well known effects of down scaling: Drain Induced Barrier Lowering (DIBL), Short Channel Effect (SCE), Punch-Through and subthreshold inversion, mobility degradation, band-toband tunneling [3][4]. Another challenge involves power consumption and thermal dissipation: Power density has been growing, as the supply voltage did not scale as much as the channel length.

Due to all these factors, keeping up with the Moore's Law will most probably be a challenge that will not be answered by Silicon CMOS nanoelectronics. For this reason many alternative technologies are under study to preserve the same rate of performance improvements. The efforts have been focused toward two main directions [1]:

• Innovation of CMOS materials and structures. Some examples are: SOI (Silicon On Insulator) transistors, with an insulator layer between substrate silicon body, and FinFET, where a multigate structure heavily reduces short channel effects.

• Creation of completely new nanoelectronic devices, called "Beyond CMOS Devices", able to replace CMOS technology. One of the most promising principle is Quantum-dot Cellular Automata (QCA). Nanotechnologies like QCA offer very high integration density, but they are still in a premature stage: A reliable and functional realization still requires extended study from the device up to the architectural level.

Current transistors exploit electronic charge to store information, therefore switching between logic levels involves charge movement, thus requiring a current flow and a consequent Joule dissipation. Energy losses are then an intrinsic characteristic of charge based electronics and, as explained before, highly scaled transistors will not be able to preserve the charge due to significant leakage. It is clear that charge based devices do not seem to be able to maintain the cost per function improvements of the last decades. The spreading concept is to replace the charge with a new kind of information token such as for instance: Polarization of nanomagnets, change in molecular configuration, electron spin or position of a micro-mechanical object.

### 2.2 Quantum-Dot Cellular Automata (QCA)

Since the introduction of the Cellular Automata idea in 1993 [5], Quantum-Dot Cellular Automata (QCA) has been attracting an increasing interest. QCA is a valuable candidate for the post-CMOS era, because it effectively addresses the problems of device density and power dissipation.

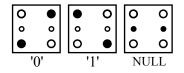

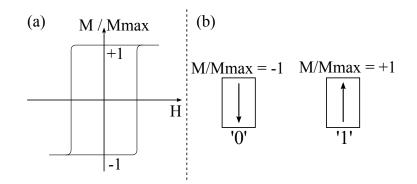

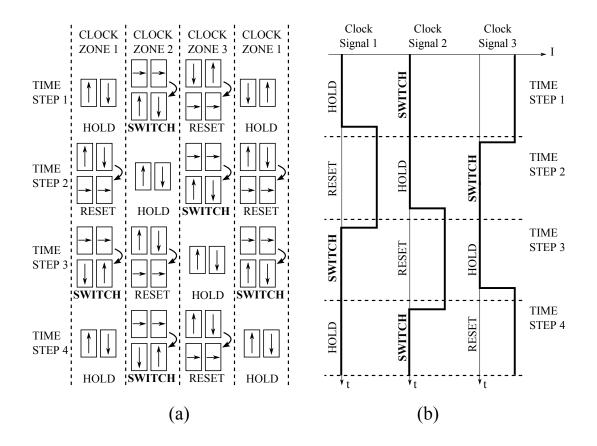

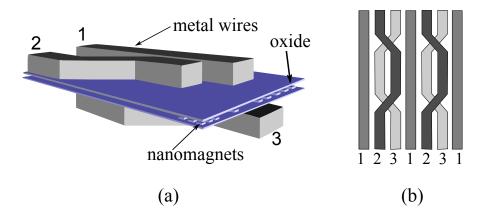

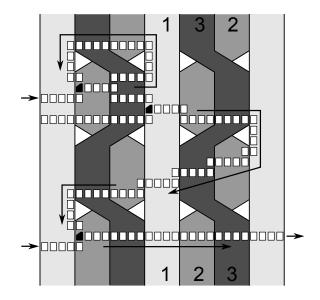

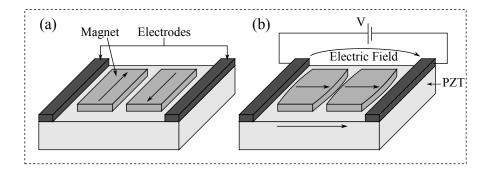

Figure 2.1. Possible states of a QCA cell: Stable states '0' and '1' and unstable NULL state.

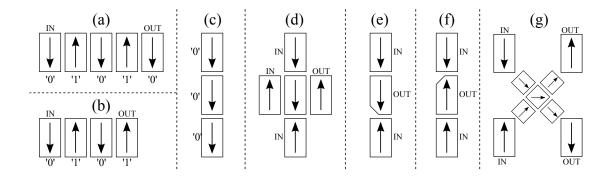

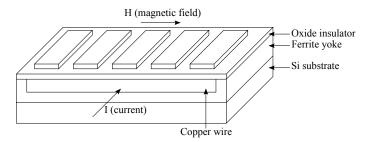

QCA technology is based on a bistable cell; properly organized arrays of these cells can realize logic functions. The first proposed implementation used a square cell with 4 quantum dots in the corners and 2 electronis. Due to electric repulsion, electrons will place at opposites corner in steady state. The two possible configurations represent hence logic values '0' and '1' [6]. In reality, to allow a correct signal propagation a third unstable state (NULL state) is necessary, therefore two more dots need to be added (Figure 2.1). The explanation of the NULL state is given

in paragraphs 2.3.2 and 2.3.3. In Figure 2.1 it is shown the generic base cell, but the theoretical principle of QCA can be realized in different ways, depending on the technology used.

Several technological implementations have been proposed in the literature. Here we present three physical solutions that seem to be more promising.