# POLITECNICO DI TORINO

SCUOLA DI DOTTORATO Dottorato in Meccatronica – XX ciclo

Tesi di Dottorato

# FPGA Operating System for Hard Real Time Applications

System Architecture and Application

Gianluca Botto

**Tutore** Ing. Marcello Chiaberge Coordinatore del corso di dottorato Prof. Giancarlo Genta

Maggio 2008

# Contents

| Ι        | FF                   | FPGA Operating System                          |    |  |  |  |  |  |

|----------|----------------------|------------------------------------------------|----|--|--|--|--|--|

| 1        | Cor                  | Context                                        |    |  |  |  |  |  |

|          | 1.1                  | State of the art                               | 2  |  |  |  |  |  |

|          | 1.2                  |                                                | 4  |  |  |  |  |  |

|          | 1.3                  |                                                | 6  |  |  |  |  |  |

| <b>2</b> | $\operatorname{Dig}$ | Digital Programmable Platform for Mechatronics |    |  |  |  |  |  |

|          | 2.1                  | EKU Kernel                                     | 9  |  |  |  |  |  |

|          | 2.2                  | EKU Interfaces                                 | 2  |  |  |  |  |  |

|          |                      | 2.2.1 Floating Point Expansion                 | 3  |  |  |  |  |  |

|          |                      | 2.2.2 Communications                           | 4  |  |  |  |  |  |

|          |                      | 2.2.3 From/To Field                            | 6  |  |  |  |  |  |

| 3        | Sys                  | System Bus                                     |    |  |  |  |  |  |

|          | 3.1                  | Memory Mapping                                 | 7  |  |  |  |  |  |

|          | 3.2                  | Address Decoder                                | 20 |  |  |  |  |  |

|          | 3.3                  | Interrupt Management                           | 24 |  |  |  |  |  |

|          | 3.4                  | DSP-FPGA Synchronous Memory                    | 26 |  |  |  |  |  |

| <b>4</b> | System Interfaces 28 |                                                |    |  |  |  |  |  |

|          | 4.1                  | Floating Point Expansion                       | 29 |  |  |  |  |  |

|          |                      | 4.1.1 HRT Tandem                               | 29 |  |  |  |  |  |

|          |                      | 4.1.2 Host Tandem                              | 82 |  |  |  |  |  |

|          | 4.2                  | Communication Interface                        | 84 |  |  |  |  |  |

|          |                      | 4.2.1 Standard Networks                        | 84 |  |  |  |  |  |

|          |                      | 4.2.2 HRT Grid                                 | 86 |  |  |  |  |  |

|          | 4.3                  | From/To Field                                  | 15 |  |  |  |  |  |

|          |                      | 4.3.1 Digital Field Bus                        | 15 |  |  |  |  |  |

|          |                      | 4.3.2 DAC Management                           | 17 |  |  |  |  |  |

| <b>5</b> | Per | Performances Evaluation      |    |  |  |  |  |  |

|----------|-----|------------------------------|----|--|--|--|--|--|

|          | 5.1 | EKU Kernel Performances      | 49 |  |  |  |  |  |

|          | 5.2 | Tandem and Grid Performances | 55 |  |  |  |  |  |

### II Real Application: Driving piezoelectric stack actuators 57

| 6 | Context           |        |                                                               |    |  |  |  |  |  |

|---|-------------------|--------|---------------------------------------------------------------|----|--|--|--|--|--|

|   | 6.1               | Piezoe | electric principle                                            | 59 |  |  |  |  |  |

|   |                   | 6.1.1  | Symbols and Units                                             | 60 |  |  |  |  |  |

|   |                   | 6.1.2  | Hysteresis of the material                                    | 60 |  |  |  |  |  |

|   | 6.2               | State  | of the art                                                    | 60 |  |  |  |  |  |

| 7 | Model             |        |                                                               |    |  |  |  |  |  |

|   | 7.1               | FEM I  | Model                                                         | 64 |  |  |  |  |  |

|   |                   | 7.1.1  | FEM analysis: main steps                                      | 64 |  |  |  |  |  |

|   |                   | 7.1.2  | Modal Residues Model                                          | 69 |  |  |  |  |  |

|   | 7.2               | FEM 1  | model validation                                              | 75 |  |  |  |  |  |

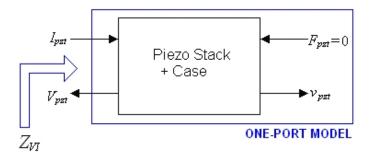

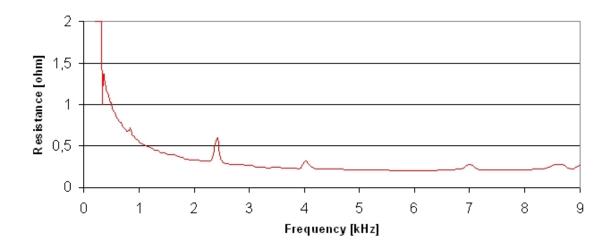

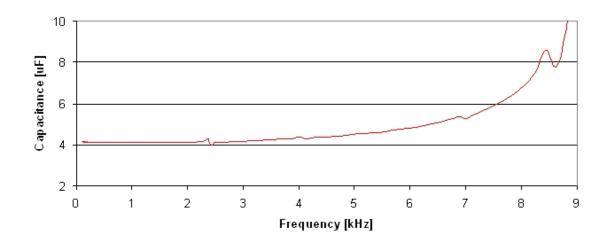

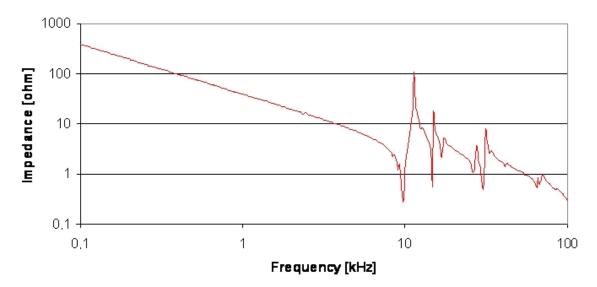

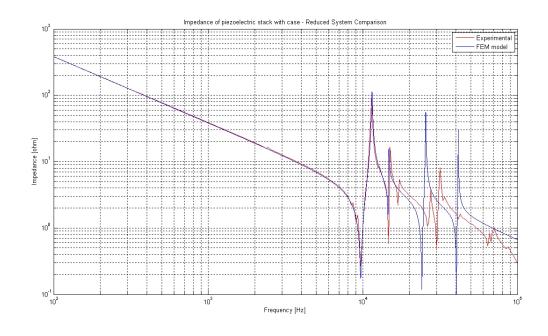

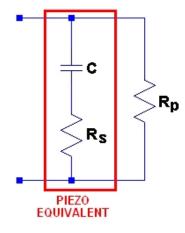

|   |                   | 7.2.1  | Experimental Measurement of the Piezoelectric Stack Impedance | 75 |  |  |  |  |  |

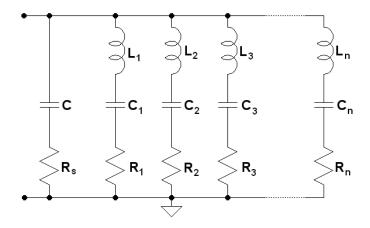

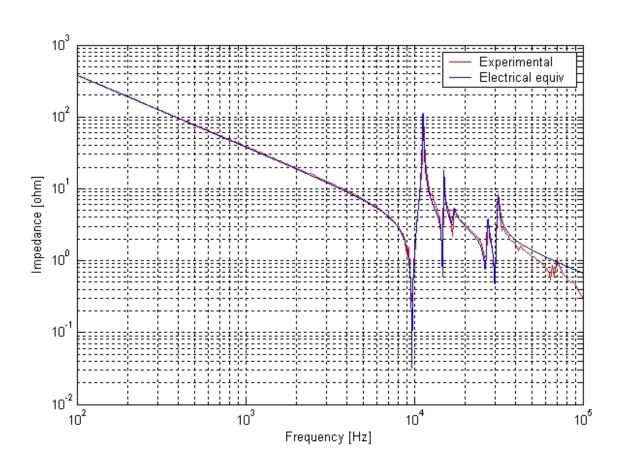

|   |                   | 7.2.2  | Electrical Equivalent Circuit                                 | 76 |  |  |  |  |  |

| 8 | Design 80         |        |                                                               |    |  |  |  |  |  |

|   | 8.1               | 0      | e Estimation                                                  | 80 |  |  |  |  |  |

|   |                   | 8.1.1  | Analog integration of measured current                        | 81 |  |  |  |  |  |

|   |                   | 8.1.2  | Digital integration of measured current                       | 81 |  |  |  |  |  |

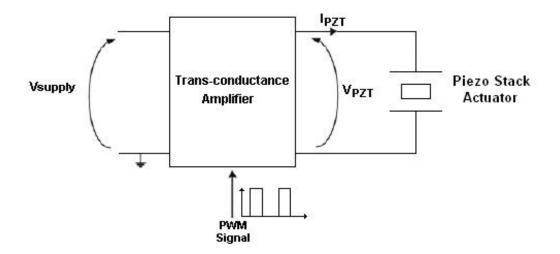

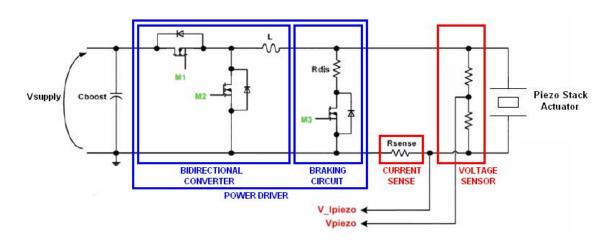

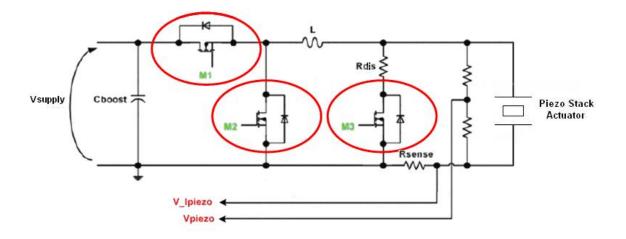

|   | 8.2               | Power  | Driver                                                        | 82 |  |  |  |  |  |

|   |                   | 8.2.1  | Concept                                                       | 82 |  |  |  |  |  |

|   |                   | 8.2.2  | Electrical Specifications                                     | 84 |  |  |  |  |  |

|   |                   | 8.2.3  | Topology                                                      | 84 |  |  |  |  |  |

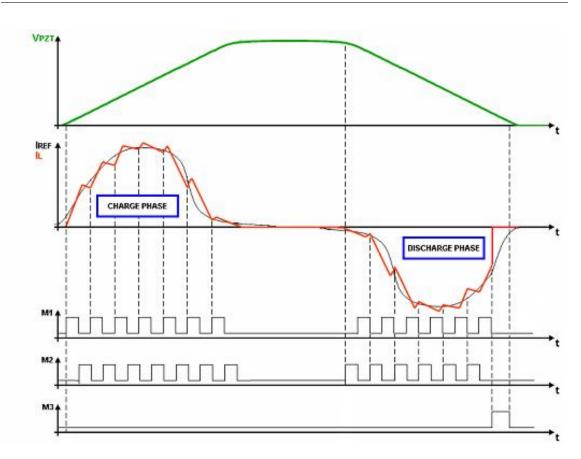

|   |                   | 8.2.4  | Switches Driving Strategy                                     | 84 |  |  |  |  |  |

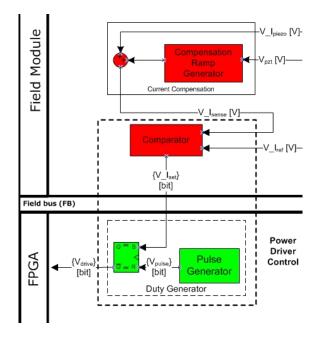

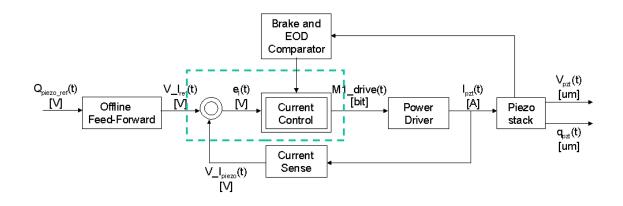

|   | 8.3               | Curren | nt Control                                                    | 86 |  |  |  |  |  |

|   |                   | 8.3.1  | Peak current with analog compensation ramp                    | 87 |  |  |  |  |  |

|   |                   | 8.3.2  | Section Omitted                                               | 88 |  |  |  |  |  |

|   |                   | 8.3.3  | Peak-Valley current mode                                      | 88 |  |  |  |  |  |

|   |                   | 8.3.4  | One Cycle Control                                             | 88 |  |  |  |  |  |

|   |                   | 8.3.5  | Average current mode                                          | 88 |  |  |  |  |  |

| 9 | Implementation 89 |        |                                                               |    |  |  |  |  |  |

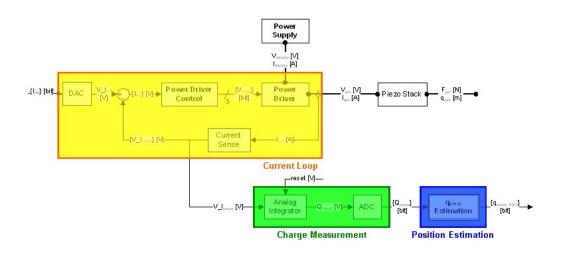

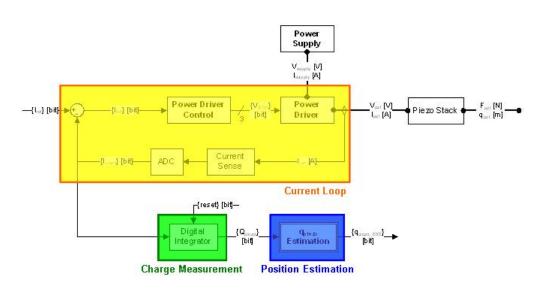

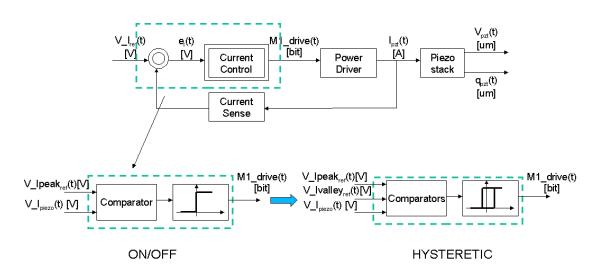

|   | 9.1               |        | loop                                                          | 89 |  |  |  |  |  |

|   |                   | 9.1.1  | -                                                             | 91 |  |  |  |  |  |

|   |                   |        | -                                                             |    |  |  |  |  |  |

|                                              | 9.1.2  | Section Omitted                                | . 95  |  |  |  |  |  |  |  |

|----------------------------------------------|--------|------------------------------------------------|-------|--|--|--|--|--|--|--|

|                                              | 9.1.3  | Current Loop adaptation on $V_{pzt}$           | . 96  |  |  |  |  |  |  |  |

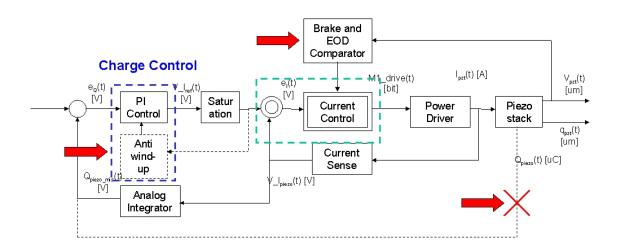

| 9.2                                          | Outer  | loop                                           | . 96  |  |  |  |  |  |  |  |

|                                              | 9.2.1  | Charge Loop                                    | . 96  |  |  |  |  |  |  |  |

|                                              | 9.2.2  | Section Omitted                                | . 100 |  |  |  |  |  |  |  |

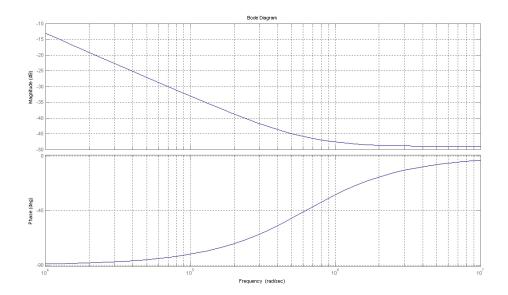

|                                              | 9.2.3  | Tuning of the compensator parameters           | . 101 |  |  |  |  |  |  |  |

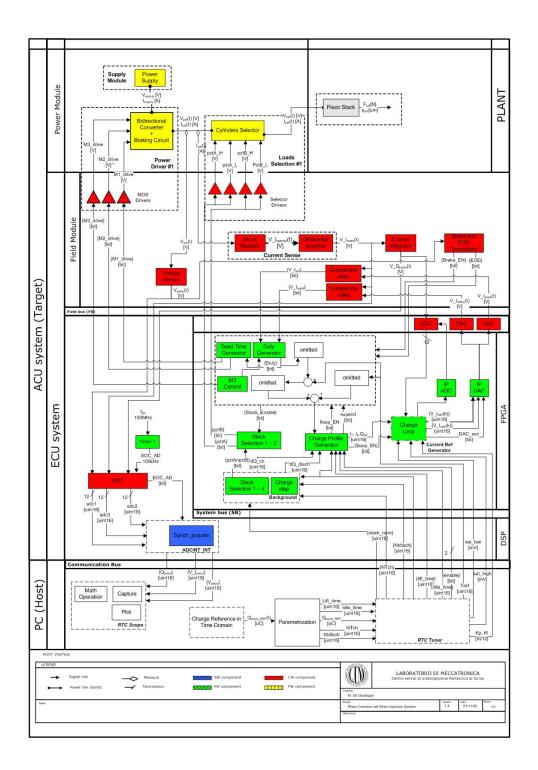

| 9.3                                          | Algori | thms on Hardware                               | . 103 |  |  |  |  |  |  |  |

| 10 Experimental Results and Model Validation |        |                                                |       |  |  |  |  |  |  |  |

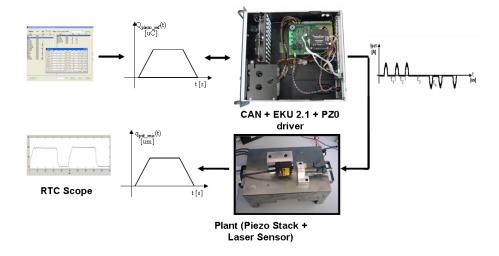

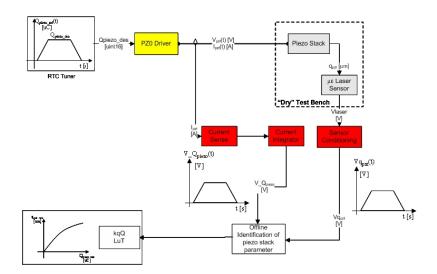

| 10.1                                         | Experi | imental Setup                                  | . 106 |  |  |  |  |  |  |  |

| 10.2                                         | Model  | Validation                                     | . 110 |  |  |  |  |  |  |  |

|                                              | 10.2.1 | Piezoelectric Stack Dynamic Equations          | . 110 |  |  |  |  |  |  |  |

|                                              | 10.2.2 | Tip Displacement Equations                     | . 111 |  |  |  |  |  |  |  |

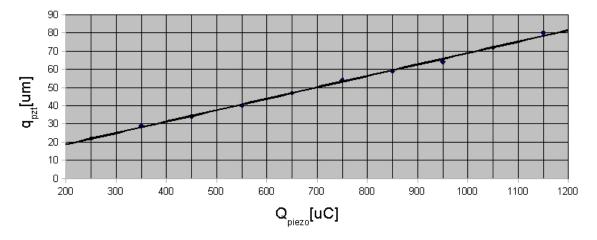

|                                              | 10.2.3 | Static Characterization of piezoelectric stack | . 111 |  |  |  |  |  |  |  |

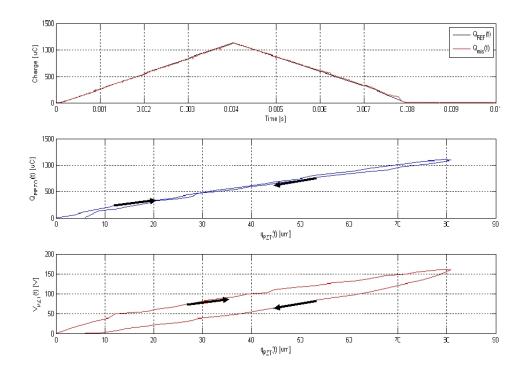

|                                              | 10.2.4 | Experiments on Hysteresis                      | . 113 |  |  |  |  |  |  |  |

| Bibliography                                 |        |                                                |       |  |  |  |  |  |  |  |

# Part I FPGA Operating System

# Chapter 1

# Context

### 1.1 State of the art

In mechatronics, as in many others fields, one of the main aspect is the prototyping. Since the mechatronics covers a lot of complex applications, the availability of a common digital platform to use in all of them is a valid help in the prototyping phase of the project.

On the market two companies are producing advanced prototyping systems:

- dSPACE with the MicroAutoBox [3] for automotive applications and the RapidPro [4] for general purpose applications and for MicroAutoBox expansion

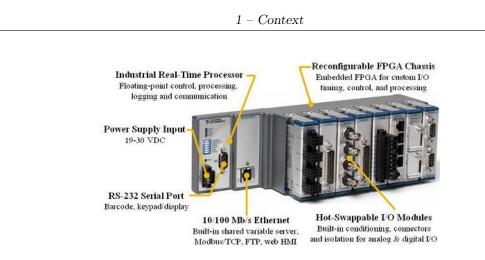

- National Instruments with the CompactRIO [11]

Figure 1.1. dSPace MicroAutoBox picture taken from dSPACE web site

The dSPACE MicroAutoBox (fig.1.1) is a rapid prototyping module intended to perform fast function related to automotive applications, such as chassis control, powertrains, body control and X-by-wire applications. MicroAutoBox is based on the IBM PPC 750FX processor which runs at a frequency of 800MHz.

Algorithms can be programmed directly in Matlab/Simulink environment and downloaded by means of a custom host PC link. A dedicated block-set for typical automotive applications is provided but the user cannot modify this functions.

The dSPACE RapidPro (fig.1.2) are modules that can be used as expansion of the MicroAutoBox system. Three modules are available: the RapidPro Signal Conditioning unit, the RapidPro power stage unit and the RapidPro control unit.

The dSPACE RapidPro control unit can be used to add advanced I/O functional-

Figure 1.2. dSPACE RapidPro system picture taken from dSPACE web site

ities to the MicroAutoBox system.

The dSPACE RapidPro control unit is based on the Freescale MPC565 processor which runs at a frequency of 40MHz (optionally 56MHz).

The strength of these systems is the user programmability interface: it is very easy and based on the well known Simulink environment; the disadvantage using these systems is that the system architecture is closed: this means limited versatility.

The National Instruments CompactRIO (fig.1.3) is a general purpose prototyping system oriented, but not limited to, the industrial automation.

CompactRIO is based on a real time processor running at 400MHz and a reconfigurable FPGA (Field Programmable Gate Array) used for I/O interface and controls. The programmability is facilitated by the use of the graphical, proprietary, LabView environment. Again the architecture is closed and the user is strongly limited by the use of high level programming tools.

CompactRIO is, maybe, the prototyping system, that uses a FPGA, known by most people. The FPGA devices offers the maximum hardware flexibility at the moment; from now on the hardware configuration performed by means of the FPGAs is called FirmWare.

FPGAs offer the possibility to implement glue logic depending on the application

Figure 1.3. National Instruments CompactRIO picture taken from the National Instruments web site

but, also, to implement complex DSP-like algorithms and even embedded processors. A good introduction to these aspects can be seen in [16].

FPGAs are often used as software acceleration in reconfigurable computers (RC), in which the operating system is a standard off-the-shelf real time operating system such as Linux and VxWorks; at university of California at Berkeley has been recently developed a custom FPGA operating system for reconfigurable computers called BORPH [9].

As mentioned before the FPGA devices can host soft core processors on which can run standard or custom operating systems. Some examples can be seen in [2] [21] [17] [7] and [23].

The object of this work is to develop a hardware operating system for mechatronic applications, which means that the FPGA device does not host a soft core processor, able to execute one only operation at a time, but it executes many concurrent hard real time functions allowing the user to develop his own application code taking advantage of the main features of the device: concurrency, flexibility and determinism.

### **1.2 FPGA Architecture**

The FPGA (Field-Programmable Gate Array) are semiconductor devices containing programmable components called Logic Elements (LE) or Logic Blocks (LB) and programmable interconnections between the blocks.

This means that the designer does not have to go through the costly and time consuming process of manufacturing an ASIC (Application Specific Integrated Circuit). The major benefit with the FPGA is the possibility to reconfigure the device if the design changes. Even the pin assignment can be changed to some extent if it turns out to be a Printed Circuit Board (PCB) design error. Main disadvantages with respect to ASIC solution are:

- FPGAs are slower

- FPGAs handle simpler designs

- FPGAs are more power consuming

Nevertheless FPGAs are often used as first phase of an ASIC design.

A classic FPGA logic element consists in a 6(or 8)-input lookup table (LUT) and a flip-flop.

There is only one output, which can either be the registered or the unregistered LUT output. The logic block has six or eight inputs for the LUT and a clock input. Since clock signals, and often other high-fanout signals, are normally routed via dedicated routing (global network), they and other signals are separately managed.

To define the behavior of the FPGA the user provides a hardware description language (HDL) or a schematic design. Common HDLs are VHDL and Verilog. Then a technology-mapped netlist must be generated. The netlist can then be fitted to the actual FPGA architecture using a process called place-and-route. The user will validate the map, place and route results via timing analysis, simulation, and other verification methodologies. Once the design and validation process is complete, the binary file generated is used to program the FPGA.

Commonly the code designed and downloaded on an FPGA is called firmware and its parts are called IP-cores or IP-blocks (Intellectual Properties cores/blocks).

All these passages are usually performed by means of a software tool provided by the device manufacturer.

In addition to logic elements, FPGAs provides I/O pins, memory and clock management.

To interconnect the device to the external world, the I/O pins are configurable between different standards (LVTTL, LVPECL, LVDS and so on) with the possibility to set pull-up/down resistors, terminations, slew rate and current strength.

Memory is usually divided into distributed memory and block memory. Distributed memory consists in the LUTs of the logic elements; using this memory more area is spent but the application runs faster.

Block memory is located in a defined location of the chip and is divided into blocks of some kilo bits. The total amount of RAM depends on the FPGA family, size and producer but, up to now it is always less than a few Mbits .

### **1.3 Real Time Systems**

Usually an operating system is intended as a platform on which programs, or better, processes, can be executed. An operating system is also a resources allocator.

With the FPGA we can not speak about programs and resources as we are used to do while we can use the word **process** to indicate a portion of the code, or algorithm, implemented on the chip.

First of all the language used to write an FPGA code is not a programming language but a hardware description language and the output is a low level logic algorithm and many of the notions used for the computer world operating systems are not applicable.

For sure it is possible to give some definitions of real time systems and real time applications that become constraints and specification for a real time operating system.

There is not only one approved definition of real time application but the basic idea is that a real time system is called so when the overall correctness depends on both the functional correctness and timing correctness.

In other words, it means that a real time operating system has to allow executing tasks with strictly time constraints called deadlines.

A distinction has been made between soft real time systems and hard real time systems and the main difference is:

• In a soft real time system the deadlines must be generally met

while

• In a hard real time system the deadlines must be deterministically met

In this way consider a system, soft or hard real time, depends from the application and from how huge are the damages in case of deadline missing.

The main advantage of the FPGAs with respect to processors is the possibility to execute different concurrent processes but the FPGA operating system concept is often applied to an operating system, custom or standard, running on a soft core which implements a processor.

A soft core processor on an FPGA allows to execute code written in common programming language like C or C++ with the advantage of custom hardware acceleration performed building custom complex instructions directly on the FPGA logic. However, only one instruction is executed at a time and the FPGA become a sequential processor.

If the area on the FPGA is large enough, it is possible to instantiate more than one soft core processor in a single chip allowing the execution in parallel of different tasks. In my opinion, this is a great limitation for the FPGA potential because the parallelism degree is always limited and a great FPGA has a cost higher than the sum of the costs of standard discrete processors.

Furthermore the scheduler implemented on the soft core processor, which allows multi task operations, has always a system overhead due to the context switching that is the change of context due to an interrupt request.

The context switching overhead is the main reason for deadline missing when the frequency of the service routine increases because the time lost while saving and restoring the context variables become non negligible with respect to the time between two consecutive interrupts.

For this reason my work was concentrated on creating a firmware framework for FPGA which allows the application designer to create and instantiate its own IP-cores disregarding the hardware device on which they will be executed, that is the main purpose of a generic operating system. In section 2 this concept will be explained more extensively.

# Chapter 2

# Digital Programmable Platform for Mechatronics

The environment in which the project has been developed is the mecatronics where mechanic engineering, electronic engineering and software engineering are gathered in order to create a complete system, control it and interface it with the external world.

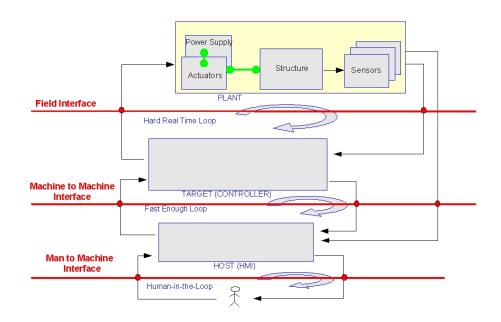

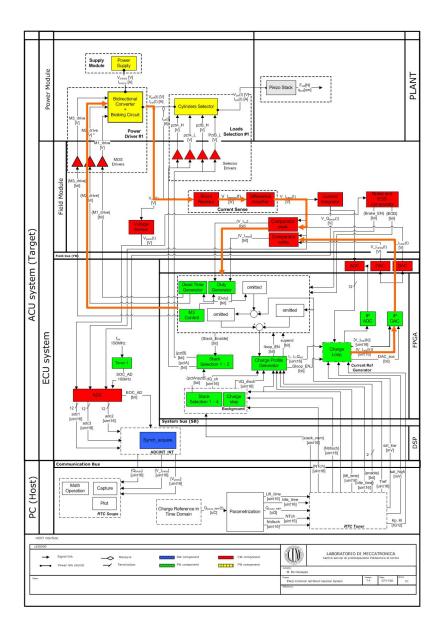

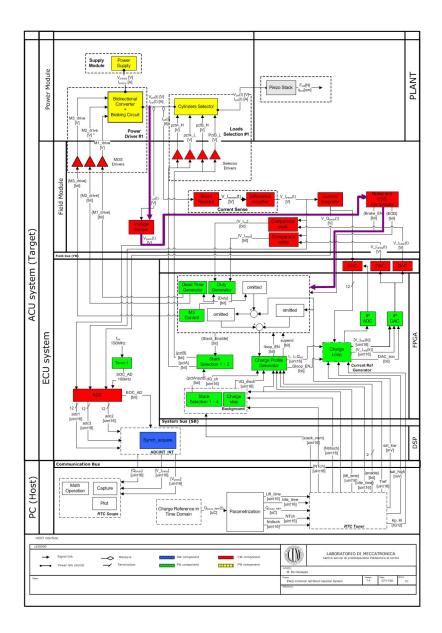

This system can be simply represented with the scheme 2.1 that we called mechatronic framework which follows the PKH (Plant Control Host) paradigm.

Figure 2.1. Mechatronic Framework

Starting from the top it is possible to see the Plant which is composed of:

- Power Supply which exchanges energy with the system through the actuators

- Actuators which transform, normally, electrical energy into mechanical energy

- Mechanical structure that is the object to move and to control

- Sensors which allows the controller or the host to have a feedback from the field

The second layer is the controller also called **target** from the point of view of the host. Plant and controller communicate by means of the Field Interface divided into commands and sensors signals.

From the control point of view, plant and controller are inserted in a Hard Real Time loop.

The third layer is the Host, usually a PC which acts as the system supervisor and allows the user to set control parameters and acquire real time variables.

Controller and Host are inserted in a Fast Enough loop. This loop can not be defined as real time because, usually, an non real time operating system runs on the host PC, and the communication layer (Machine to Machine Interface) can not have real time characteristics.

The last layer on the bottom represents the user who is often present especially in a prototyping phase when he becomes a part of the loop modifying the parameters of the control.

The object of this work is the controller and especially the firmware part of it.

The main idea was to develop a cross platform operating system that can be used on different digital platforms which have a similar architecture.

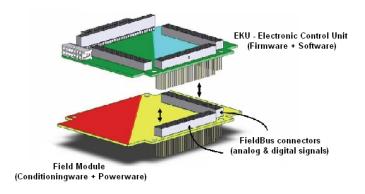

For this reason, we started working with an electronic control unit developed in our laboratory. Later, others versions of this ECU has been developed and finally born a spin-off company (ACTUA S.R.l.) that produces these boards with the name of EKU (Electronic Kontrol Unit).

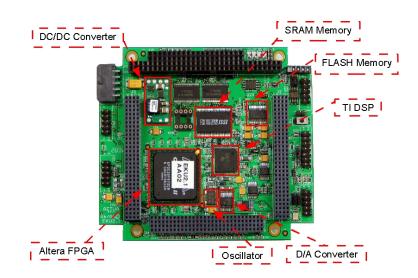

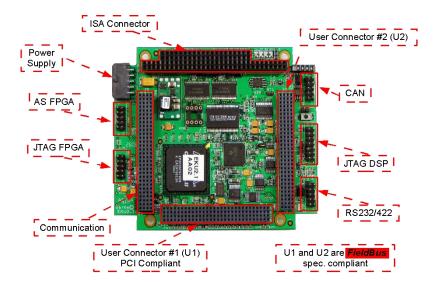

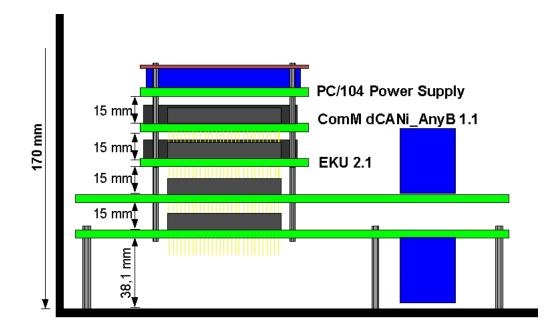

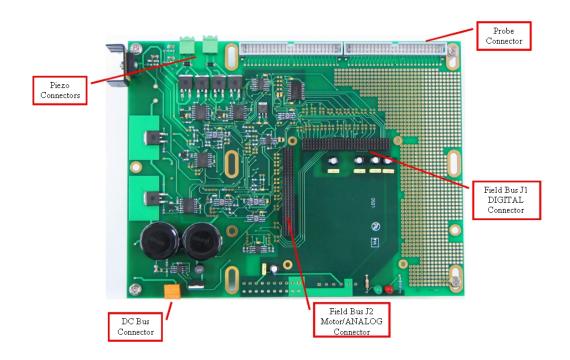

The architecture of these boards was always the same and, even if the components change between a version to the other, the kernel of the operating system was kept. The last version of the EKU is shown in the pictures 2.2 and 2.3 where key components and connectors are evidenced.

### 2.1 EKU Kernel

This board kernel is based on two main programmable devices:

Figure 2.2. EKU 2.1: key components

Figure 2.3. EKU 2.1: connectors

- DSP (Digital Signal Processor) (TMS320F2812) from Texas Instruments; is a fixed point 32 bits DSP with an external memory interface of 16 bits data width and peripherals targeted for automation control (I/O captures, PWM signals, Encoder interface, 16 channels ADC and more)

- FPGA (Field Programmable Gate Array) (CycloneII EP2C35F672C8) from ALTERA; it has about 35000 logic elements, 480 kbits of RAM, different I/O

standards and four PLLs (Phase Locked Loop) for clock managements

Figure 2.4. EKU 2.1: Kernel and Interfaces

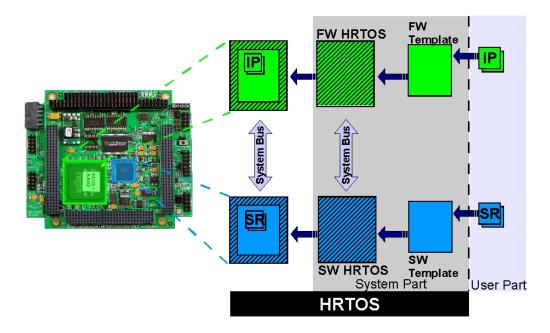

The main idea of the Hard Real Time Operating System for our digital platforms is illustrated in figure 2.5 in which the concept mentioned in 1.3 for both the firmware (FPGA device) and the software (DSP device) is shown.

HRTOS is intended as an abstraction layer that allows the user to program his

Figure 2.5. HRTOS main idea

code independently from the hardware devices and the connections with them.

The operating system gives the rules to the user in order to respect the physical constraints related to the available resources and is customized and compiled by the system analyst for the specific digital platform.

The user code are called SR (Service Routines) when related to the software and IP (Intellectual Properties) when related to the firmware.

SRs and IPs are linked to the HRTOS by means of a software template and a firmware template which are user friendly framework containing the links to all the resources available on the device. In these templates the user instantiates his own code divided in more SRs and IPs and links its interfaces to those of the template in a logical way, neglecting the physical aspects.

SRs and IPs communicate by means of the HRTOS and precisely through the System Bus that is a deterministic protocol based on the memory mapping concept.

The system bus uses the external memory interface of the DSP in order to create a single master (DSP) single salve (FPGA) communication channel able to exchange up to 16 bits in a single transaction.

The determinism is guaranteed by the use of a signal, managed by the slave, able to hold the master until the write or read operation has been completely performed. In this way the duration of the transaction is defined a **priori** by the time this signal is held active.

The system bus includes the possibility to interrupt the execution of the code running on the DSP by means of 16 interrupt lines multiplexed on two DSP hardware interrupts. More details on the system bus can be seen in chapter 3.

### 2.2 EKU Interfaces

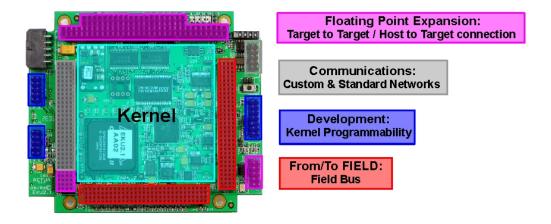

The EKU 2.1 interfaces are divided into four parts (see figure 2.4):

- Floating Point Expansion which allows to interconnect the EKU to a real time micro processor in order to create a target to target communication for co-processing designs, or to a host PC for data logging, monitoring and tuning

- Communications which allow to create a custom hard real time grid between two or more EKUs for distributed systems that require high computational power, or to interconnect the EKU with the external world by means of standard automotive or industrial protocols

- Development that is the kernel programmability interface (JTAG connections for DSP and FPGA)

• From/To Field that implements the field bus used to interconnect the EKU with digital and analog sensors and peripherals, used to interconnect the EKU with one or more field modules, and used to interconnect the EKU with analog and digital signal power supplies

#### 2.2.1 Floating Point Expansion

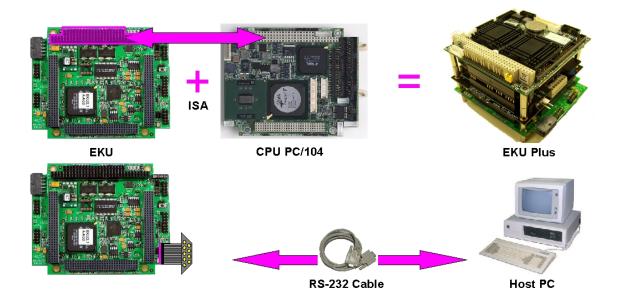

The Floating Point expansion consists in a communication channel between the EKU and a micro processor, usually a PC.

As mentioned before this communication channel has two main purposes: real time target to target communication for co-processing designs, and non real time host to target communication for data acquisitions, monitoring and tuning.

The EKU has two possibilities to perform this channel:

- with a serial RS232/RS422 channel only for host to target communications

- through ISA (Industry Standard Architecture) protocol for both target to target and host to target communications

Figure 2.6. Floating Point Expansion: EKU and PC through ISA Potocol (top); EKU and PC through RS232/422 protocol (bottom)

These configurations are shown in figure 2.6 where the top part illustrates the stack composed of an EKU and a PC, both compliant to the standard pc/104; this configuration is called EKUplus and the link between the EKU and the PC is also

called HRT Tandem because it is possible to perform a Hard Real Time communication between the fixed point DSP, the FPGA and the floating point micro processor using the ISA protocol.

While the RS232/RS422 protocol is managed by the DSP, the ISA protocol is entirely managed by the FPGA with an operating system dedicated IP. This IP is explained better in section 4.1.

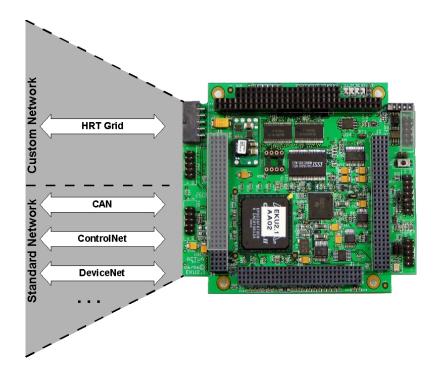

#### 2.2.2 Communications

The Communication Interface is intended to manage both standard communication protocols (usually to create standard networks) and a custom communication protocol developed in order to create a hard real time grid (HRT Grid) between different EKUs in the same application.

Figure 2.7. Communication Interface

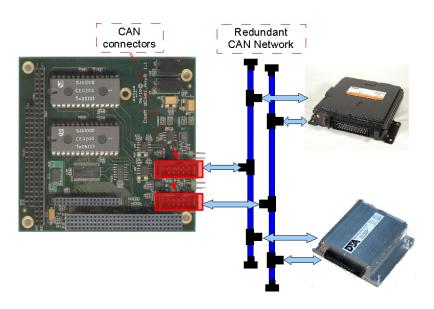

Standard network protocol can be, for instance, the CAN bus protocol that can be managed directly by the DSP which has a native CAN controller, or external CAN bus channels implemented on a separated board (dCANi\_AnyB 1.1) developed in order to have two more CAN channels electrically isolated (see figure 2.8).

With the same board other protocols can be used because there is a connector

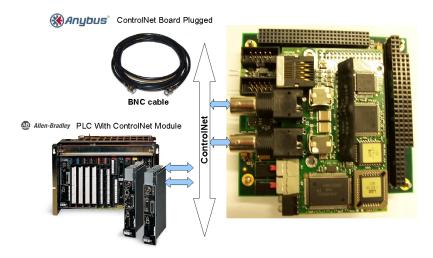

Figure 2.8. dCANi\_anyB1.1 : Dual isolated CAN bus board used for redundancy

on the board that is compliant with the anybus slave modules, which performs a lot of standard industrial and automotive protocols such as ControlNet, DeviceNet, CANopen, Modbus, Profinet-IO, Profibus and so on (see figure 2.9).

Figure 2.9. dCANi\_anyB board used as bridge for anybus modules in standard networks

While the higher level of these protocols is managed by external devices, the communication between the external devices and the DSP is performed by the FPGA that creates a link between the DSP external memory interface and the registers of the chips. In this way the DSP user can easily access this devices as physically mapped in the DSP accessible memory.

The HRT Grid is a custom protocol, entirely managed by the FPGA, which allows a high performance communication bus between EKUs. This bus is used for remote task synchronization and few data exchange in scheduled periods opposite to standard networks which are used to transfer a large amount of data as fast as possible. More details on the communication interface can be seen in section 4.2.

#### 2.2.3 From/To Field

The From/To Field Interface is divided between DSP and FPGA; DSP can manage both analog and digital signal since it has integrated a 16 channel analog to digital converter, while the FPGA can directly manage only digital signals.

Neither DSP nor FPGA has an integrated DAC device and to overcome this limitation an external DAC device has been provided on the EKU. This device is controlled by a dedicated IP-core of the firmware operating system. More details on the field interface are in section 4.3.

# Chapter 3

# System Bus

### 3.1 Memory Mapping

As mentioned in the previous chapter, the System Bus is based on the DSP external memory interface.

The DSP used in the digital platform has a 16 bits wide data bus compliant with the AMI (Asynchronous Memory Interface) standard.

In addition to the data bus, the AMI protocol implemented in the DSP has an address bus of 20 bits able to address up to one mega locations of 16 bits each and few control signals such as:

- three chip select signals able to address different regions with different parameters

- RnW signal that is high when the transaction is a write and low when it is a read

- WEn signal (active low) indicates a write operation

- RDn signal (active low) indicates a read operation

- Hold signal (active low) is used by the external device to hold the DSP until the transaction has been fully performed

The AMI protocol is a single master single slave protocol that performs only single word transactions (no burst transfer is allowed) and the DSP is always the master of the channel while the FPGA is the slave.

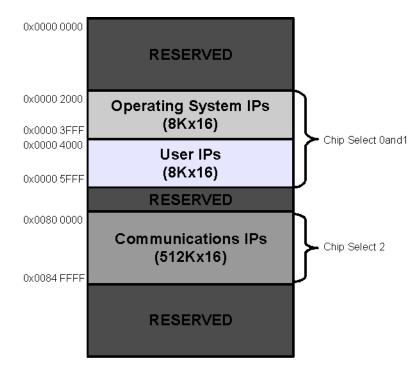

In order to address more than one IP internally in the FPGA, the bus is split into many interfaces each of them activated when the DSP address is in a precise range. The memory regions addressed by the DSP, by means of the three chip select signals, are shown in figure 3.1; the regions six and seven has been reserved for DSP code and data, while the regions zero, one and two are used by the firmware operating system to map its IPs.

In this way the code running on the DSP can easily access the registers and

Figure 3.1. DSP-FPGA Memory Mapping

functions implemented on the FPGA by means of a memory pointer, in the same way as it accesses the resources embedded on the DSP.

This technique is widely used in the computer field and it is known as memory mapping.

The first chip select (chip select 0 and 1) addresses two memory zones:

- In zone 0 are mapped the IPs of the operating system such as the DAC management IP and the Interrupts manager IPs

- In zone 1 are mapped the IPs written by the FPGA user (application designer)

The system IPs are statically memory mapped because this operation needs to be executed once, while the user IPs are dynamically mapped starting from the address 0x0000 4000.

The second chip select (chip select 2) addresses the zone 2 in which are mapped the IPs related to the communications such as the CAN interface (that is a bridge between the DSP and the SJA1000 device used on the dCANi\_anyB 1.1, the Anybus interface between the DSP and the anybus modules, the ISA protocol to communicate with the PC and the HRT Grid protocol used to create a grid of EKUs. The AMI protocol is very simple but it is not very common in FPGA environment. For this reason inside the operating system the IPs use a different protocol that is called wishbone protocol.

The wishbone protocol is again an asynchronous protocol which uses:

- two data buses (data\_in and data\_out)

- address bus

- strobe signal (active high) that indicates when a transaction is being performed

- WE signal (active high) that indicates when the transaction is a write operation

- ACK signal (active high) that is asserted by the slave to indicate that the operation is completed

The wishbone protocol allows many types of transaction included the burst mode but since the AMI protocol allows only single transactions, only this mode has been implemented.

The translation from the AMI protocol into the Wishbone one is performed simply with combinational logic:

- wishbone data input bus is fed by the DSP data bus

- DSP data output bus is fed by the wishbone data output only when the operation is a read

- strobe signal is a combination of the address bus and the chip selects

- DSP hold signal is fed by the ACK signal of the wishbone protocol

To ensure that the DSP is released when the transaction is really completed, the hold signal is de-asserted after the ACK signal is gone high and returns low (after the strobe signal goes low).

The logic of the hold and ACK signals is synchronous and takes on some clock periods to be performed. The entire transaction of a word between the DSP and the FPGA takes on about 160nS both for read and write operations.

### **3.2** Address Decoder

In each zone addressed by the DSP through the system bus are allocated more than one IP-core. It means that an address decoder is needed in order to choose which of these IP-cores must respond.

The first layer of the address decoder is performed directly by the IP translating the AMI protocol into the wishbone one using the chip select signals and the bit number 14 of the address bus. In this way, the three zones (0, 1 and 2) are correctly recognized: the zone 2 directly by the relative chip select, while zone 0 if the 14th address bit is equal to zero and zone 1 vice versa with the chip select 0 and 1.

Every IP-core mapped in a single region can have different number of registers and so it can take up more or less memory locations than another one.

For this reason a new layer for the address decoder is needed. In zones 0 are mapped the IP-cores listed below:

- System Config IP (start address 0x0000 2000) takes up 16 registers

- User Interrupt Manager IP (start address 0x0000 2010) takes up 8 registers

- System Interrupt Manager IP (start address 0x0000 2018) takes up 8 registers

- DAC Manager IP (start address 0x0000 2020) takes up 16 registers

The System Config IP is a configuration module used to set some parameters of the operating system and to read the status of some registers.

It acts also as a time keeper counting, with a precision of a milliseconds the time since the EKU has been powered up.

For the time keeper function three registers are used for a total of 42 bits (10 bits for milliseconds, 6 bits for seconds, 6 bits for minutes and 20 bits for hours) able to count for longer than 19 years.

The User Interrupt Manager is used to interrupt the execution of the DSP code when a particular event is recognized by one of the user IP-cores. For example, a reason to interrupt the DSP can be a particular angle reached by an electrical motor in order to execute angular sampling and control; or else the output of an hardware comparator can be connected to an FPGA pin and then linked, after a digital filtering, to an interrupt request line to interrupt the DSP control algorithm when an analog signal reaches a predefined threshold.

The System Interrupt Manager is used by some of the operating system IPs to interrupt the execution of the DSP code and to trigger particular tasks related to the IPs themselves.

More details about these IP-cores are given in the next section.

The DAC Manager IP is used to configure and use an external multi channel DAC device. The IP performs the configuration during the initialization of the system

and then feeds the inputs of the DAC during run time. More details about this IP are given in section 4.3.

In zone 1, the user IPs instantiates are dynamically mapped by the firmware developer in the operating system template.

In order to correctly map these IPs, the user must set a constant named NUM\_IP\_CONST with the number of the IPs he wants to instantiate in the system.

Each user IP has 16 register locations available; in this way it is simple for the operating system to assign memory ranges to the IPs starting from the address 0x0000 4000.

For every IP instantiated by the user, a number  $(num\_ip)$  that is used by the operating system is declared to order the IPs in the memory zone. The system can host up to 64 IPs; for example if three user IPs are used, one performs the read of an incremental encoder and the hall effect sensors with num\\_ip = 0, the second is used to control the current in a DC brush-less motor with num\\_ip = 2, and the last one performs a PWM signals modulation with num\\_ip = 1. Finally, the memory mapping will be:

- Encoder IP (start address 0x0000 4000)

- PWM modulator IP (start address 0x0000 4010)

- Current control IP (start address 0x0000 4020)

To write on the registers unused of the zone 1 has no effects, while the reads return the value 0x0000. The ACK signal of the wishbone protocol is fed with the strobe signal in order to release the DSP as soon as possible.

In zone 2, the system IPs related with the communication with the external world are mapped and a particular IP of the system bus is used to implement memory sharing between DSP and FPGA.

The order implemented in this portion of the address decoder is listed below:

- Anybus modules IP (start address 0x0008 0000) takes up 4096 registers

- CAN bus channel 1 IP (start address 0x0008 1000) takes up 128 registers

- CAN bus channel 2 IP (start address 0x0008 1080) takes up 128 registers

- RSMP channel 1 (RS multi protocol) IP (start address 0x0008 1100) takes up 16 registers

- RSMP channel 2 (RS multi protocol) IP (start address 0x0008 1110) takes up 16 registers

- RSMP channel 3 (RS multi protocol) IP (start address 0x0008 1120) takes up 16 registers

- RSMP channel 4 (RS multi protocol) IP (start address 0x0008 1130) takes up 16 registers

- Scheduler 1 IP (start address 0x0008 1200) takes up 32 registers

- Scheduler 2 IP (start address 0x0008 1220) takes up 32 registers

- Scheduler 3 IP (start address 0x0008 1240) takes up 32 registers

- Scheduler 4 IP (start address 0x0008 1260) takes up 32 registers

- HRT Grid config IP (start address 0x0008 1280) takes up 32 registers

- HRT Grid registers IP (start address 0x0008 12A0) takes up 32 registers

- ISA core IP (start address 0x0008 2000) takes up 8192 registers

- DSP2FPGA synchronous memory IP (start address 0x0008 4000) takes up 4096 registers

Anybus modules IP and CAN bus IPs are simply bridges between the system bus and the interface of the external devices.

The DSP can easily access these devices as for all the others IPs instantiated in the FPGA through a memory pointer.

RSMP channels IPs are system IPs that implement the standard RS protocol such as RS232, RS422 and RS485. The host interface of these IPs is the standard UART and are used with the board developed by ACTUA S.r.l called qRSMPi, which stands for quad RS multi protocol isolated. This board implements four isolated RS standard communication channels.

Scheduler IPs have been developed in order to trigger the DSP service routines starting from events generated into or acquired by the FPGA.

These schedulers are directly connected to the HRT Grid IP and allow to trigger three different service routines for each DSP in the grid; it is possible to trigger the same service routines on all the EKUs composing the grid or to trigger, for example, the service routine number two on a DSP and the service routine number one on another DSP.

These scheduler IPs perform the so called **Distributed Scheduler** discussed deeper in section 4.2.

HRT Grid config IP is used to set parameters of the grid configuration such as the number of boards in the grid, the identification number of the board inside the grid, which are the boards enabled to write on the bus and others.

The HRT Grid registers IP contains the registers shared in the grid, since the main feature of the HRT Grid is the shared memory between the boards.

These 32 registers are divided into two parts: registers written by the DSPs and registers written by the FPGAs. DSPs usually shares control variables of the running code while FPGAs normally share services such as an encoder sensor measurement, but there are not limitations due to the implementation.

HRT Grid config and HRT Grid registers IPs are explained better in section 4.2.

ISA core IP allows to communicate with a floating point PC using the Industry Standard Architecture protocol. This protocol is still largely used in industry environment because of its low price and it has enough throughput for many control applications.

The communication between the EKU and the PC is based on the concept of the shared memory; in this way DSP and PC can perform a co-processing application in the easiest way: using the same variables and parameters and addressing them by means of a simple memory pointer.

PC and DSP can trigger a service routine to each other simply writing on a dedicated register.

More details on this IP are given in section 4.1.

DSP2FPGA synchronous memory IP allows to exchange consistent patterns of data between DSP and FPGA. This can be very useful when more than one control variable has to be passed from the DSP to the FPGA and vice versa, for example to update the coefficients of a filter; in this case a data inconsistency between the coefficients produces errors in the output.

This IP uses some control registers to perform the update of the patterns. The patterns are eight of 256 words each.

More details are given later in this chapter.

These three address decoder perform the second layer of the complete address decoding; the third, and last, layer is performed in each IP, both system IP and user IP.

In order to be able to communicate through the wishbone protocol, every IP must contain a state machine implementing the wishbone slave interface and one of the task of this process is to discern between the register to update (DSP write operation) or to output (DSP read operation) basing on the address in its own IP address range. Summing up the address decoding function is hierarchical distributed on three layers:

- Layer 1 AMI to Wishbone protocols translation IP

- Layer 2 three address decoder IPs, one for each memory zones

- Layer 3 Each IP in the system has an internal address decoder working on the number of registers it takes up

### **3.3** Interrupt Management

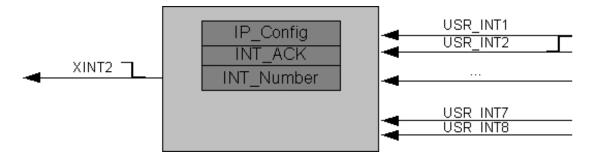

The task of User Interrupt Manager IP is to assert the DSP interrupt request line XINT2 when one or more interrupt request lines (USR\_INTn) are asserted by one or more user IP.

In the template of the firmware operating system it is possible to wire the signals of the user IP-cores to the 8 inputs of the interrupt manager IP. In this way a portion of the user code can interrupt the execution of the DSP code in order to start the execution of a specified task associated with that interrupt.

Considering the system as a co-processing between a DSP and an FPGA, the interruption of the DSP code by the FPGA can be seen as a distributed scheduler: in addition to the service routines scheduled by the software operating system, others that are scheduled by the FPGA can be executed at any time. In fact, they usually depend on external events.

The 8 interrupts available in the FPGA template are then multiplexed in a single interrupt request line to the DSP side (see figure 3.2).

One of the registers involved in the interrupt management is the configuration reg-

Figure 3.2. User Interrupt Manager: 8 FPGA lines are multiplexed to one DSP hardware interrupt

ister by means of which it is possible to set the event, associated to each interrupt

line, that will trigger the interruption. For each interrupt line are used two bits for a total of 16 bits.

The possibilities are:

- (00) the line is disabled

- (01) the line is active on rising edge

- (10) the line is active on falling edge

- (11) the line is active on both rising and falling edges

A second register reports the number of the (first) line that triggered the interrupt request. In this way, when the DSP scheduler receives the interrupt request, it performs a read operation of this register and decides which is the task to call. This operation is the demultiplexing of the single interrupt line to the original eight. This operation takes some DSP clock cycles but allows to multiply the possibility to interrupt the DSP code.

When the correct task has been performed the DSP scheduler writes it on another register of the interrupt manager which deactivates the request line (XINT2) and starts again listening to the eight inputs.

The System Interrupt Manager is identical to the user one but the eight inputs lines are fed by operating system IPs. The hardware DSP interrupt line is XINT1 instead of XINT2 but the FPGA registers and DSP scheduler have the same behavior.

The associations between the inputs of the interrupt manager and the system IPs are:

- line 0 is associated with the HRT Grid ISR 1 (Interrupt Service Routine 1)

- line 1 is associated with the HRT Grid ISR 2

- line 2 is associated with the HRT Grid ISR 3

- line 3 is associated with the HRT Grid Fault ISR

- line 4 is associated with the Interrupt from the PC (through ISA bus)

- line 5 is associated with the Anybus module ISR

- line 6 is associated with the ISR of the first CAN channel

- line 7 is associated with the ISR of the second CAN channel

### 3.4 DSP-FPGA Synchronous Memory

As mentioned before, this IP is intended to perform a block data exchange between DSP and FPGA in a consistent way. It means that writes and reads on the same block can not be interposed.

Being the DSP and the FPGA two autonomous devices, the probability of data inconsistency is high; however, in a hard real time system even a low probability can not be accepted.

For this reason a particular IP-core has been developed to help the application designer to avoid this problem.

The principle at the bottom of this IP is the concept of the dual port memory.

In a dual port memory, read operation during a write operation is allowed: two distinct data and address buses are provided and they can be used by two different devices. However the limitation of the data consistency is not solved with a simple dual port memory. To overcome this problem two dual port memory blocks must be used.

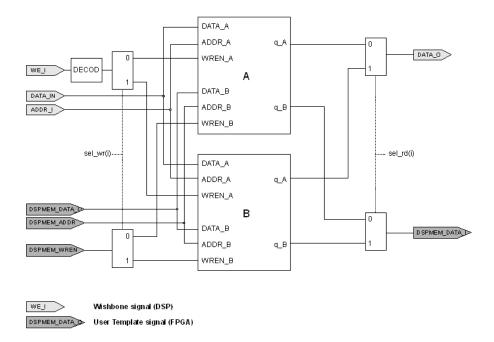

A simplified block scheme of this idea is shown in figure 3.3 where signals indicated

Figure 3.3. Structure of the double dual port memory at the base of the IP

as Wishbone signal (DSP) are the signals of the system bus (driven by the DSP) and then translated to the wishbone protocol, while the signals indicated as User Template signal (FPGA) are driven by the user IPs instantiated in the firmware

user template.

While the first block is updated by a device that writes values on it, the second device can read from the second block and vice versa. At the end of the writing phase, while the second device is not performing read operations, the pointers to the memory blocks are exchanged. Then the first device writes on the second block while the second device reads from the first one.

To understand better this mechanism an example is proposed: the DSP code has to transfer to the FPGA code a list of parameters for the position profile of an AC brush-less motor. The FPGA code needs the complete set of these parameters in order to perform a linear interpolation to obtain the position profile as a function of time.

The designer chooses the fourth portion of memory among the eight available; at the beginning, the memory is empty and the signal called **ready** (active high) is low. The DSP code starts filling the block A of the fourth memory portion and when it has finished, it sets a configuration register of the IP accordingly. The register field is called **swap\_en**.

At this point, the IP changes the writing pointer from the block A to the block B while the read pointer remains set to block A and the **ready** signal becomes high (active).

The FPGA code can start reading parameters from the block A. Then a signal called **busy** is emitted from the FPGA to indicate that the memory block can not be updated or the data consistency can not be assured.

While the FPGA code is reading from the block A, the DSP code has a new set of parameters to write, which is done on block B. When the DSP code has finished to fill the memory, it sets again the swap\_en field which remains active until the FPGA code has not finished to read the parameters from the block A. At this point the busy signal is de-asserted and the IP changes the writing pointer from block B to block A and the reading pointer from block A to block B.

Now the DSP code can start again writing on block A while the FPGA code reads the new parameters from block B.

Obviously these operations can be performed also in the other direction: the FPGA code writes data and the DSP code reads but the procedure is substantially the same.

A consideration must be done: as two dual port memory blocks (A and B) for each portion of memory are used, the RAM bits used is doubled with respect to the useful memory bits. However, this choice has been motivated by the will to maximize the flexibility.

# Chapter 4

# System Interfaces

This chapter presents the FPGA operating system implementation of the EKU interfaces.

As seen in chapter 2 the main interfaces of our digital programmable platform are:

- Floating point expansion (EKU-PC via ISA)

- Communications (standard networks and custom HRT Grid)

- From/To Field (Field bus)

Floating point expansion is implemented in a single IP-core called ISA core performing two communication channels:

- Target to target communication (EKU-PC co-processing)

- Host to target communication (data logging, monitoring and tuning)

Concerning Field interface, the FPGA field interface and how the FPGA operating system manages this interface will be discussed. The DSP field interface is the object of this thesis.

In the Communication interface a distinction will be done between standard communication protocols (networks) and a custom communication protocol (HRT Grid). Standard networks are managed by external devices; the FPGA task is to allow the interaction with these devices.

HRT Grid is entirely managed by the FPGA and main features and characteristics are presented.

### 4.1 Floating Point Expansion

With floating point expansion we intend the integration in the system of a floating point micro processor. This floating point micro processor can be seen either as a co-processor for hard real time applications, or as a host PC able to acquire from the target and present to the user a large amount of data (real time variables). In this case the PC can also be a bridge between the target and a standard network (for example a LAN) in order to act on the EKU remotely.

The link between EKU and PC is the ISA protocol (Industry Standard Architecture) since it is still a protocol commonly used in industrial systems and because it guarantees direct access to PC peripherals such as DMA controller (for PC memory direct access), interrupt controller (direct access to the 15 hardware CPU interrupts) and all the other peripherals mapped in low memory region.

ISA is an asynchronous memory interface protocol with separated address and data buses; the data bus is 16bits wide with the possibility to perform 8bits write and read operations.

ISA is a low level PC protocol which allows to access two distinct memory regions (or range): low memory (from 0x0000 to 0xFFFF), called PORT I/O, used to access the PC low level peripherals and the high memory (from 0x00010000), called MEMORY I/O, used as a standard memory.

In our implementation PORT I/O range is used for IP configuration registers while MEMORY I/O range is used as co-processing shared memory.

#### 4.1.1 HRT Tandem

As seen in section 2 the digital platform used to develop the system is based on an FPGA and fixed point DSP.

The EKU is an electronic control unit intended for rapid prototyping purpose; for this reason sometimes very complex algorithms have to be implemented and evaluated.

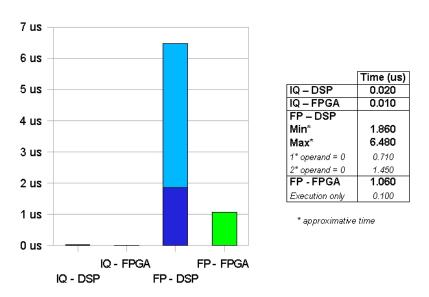

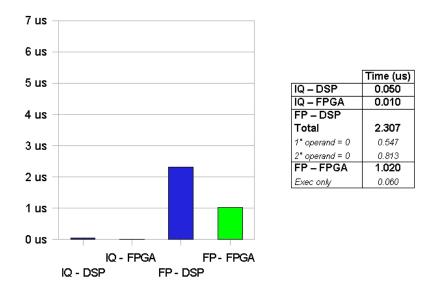

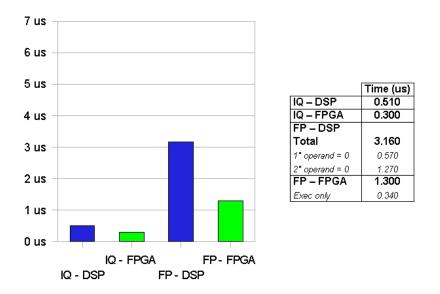

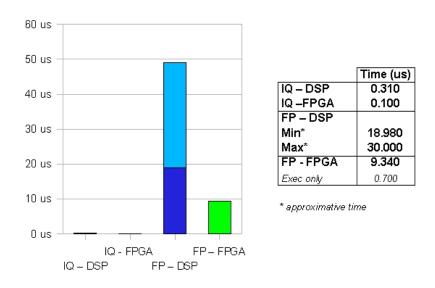

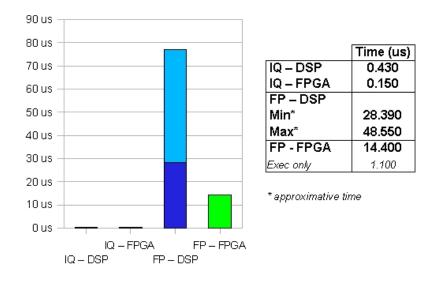

The fixed point mathematics is often precise enough to implement the most control algorithms but writing complex code in fixed point is difficult.

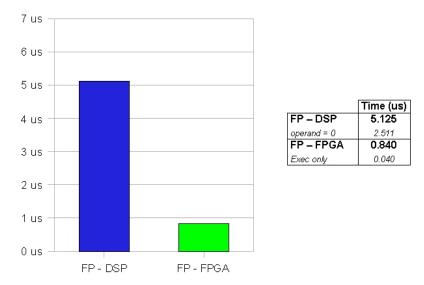

The FPGA can implement operations in single precision floating point and can be used as a DSP mathematical co-processor for simple control codes where the dynamics and precisions require floating point computation. Floating point operations implemented on the FPGA take up a lot of logic elements each and so are limited in number.

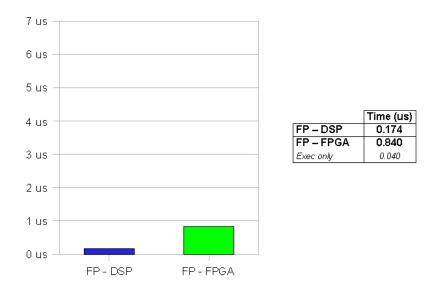

The DSP can execute floating point operations but they are emulated since the DSP has not a hardware floating point unit. Time spent by every floating point multiplication is about  $2.3\mu S$  while a division takes about  $3.2\mu S$ , which is ten times slower

than the computation performed in fixed point.

When the DSP and the FPGA are not sufficient to implement the algorithms, the use of a micro processor becomes necessary.

EKU and PC used for real time co-processing by means of a target to target communication have been called HRT Tandem to indicate two entities working together (in hard real time) for a common purpose.

HRT Tandem is based on the concept of memory share: DSP, FPGA and PC execute tasks sharing the same variables and parameters. In this way data inconsistency is avoided and the code variables are linked using memory pointers. To implement this architecture a multi port memory is necessary and for this reason the FPGA has been used.

The memory shared between the EKU and the PC is physically located on the FPGA (FPGA RAM blocks) which acts as a switch in order to allow both DSP and microprocessor to access the same memory.

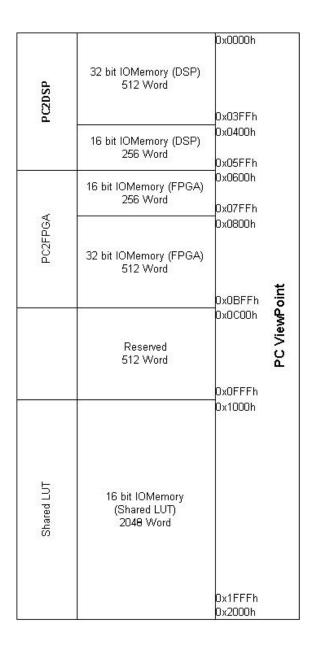

The total shared memory is 8Kbytes (4Kwords) and is divided into different sections:

- $\bullet~256$  32bits locations shared between PC and DSP

- 256 16bits locations shared between PC and DSP

- 256 32bits locations shared between PC and FPGA

- 256 16bits locations shared between PC and FPGA

- Look Up Table (LUT) of 2048 words (16bits) shared between PC and FPGA

Both system bus (DSP-FPGA) and ISA (PC-FPGA) have a data bus of 16 bits wide; considering to exchange floating point data or even long integer variables, there is the possibility that a 32 bits variable is read while only the least significant word has been written. In this case data inconsistency occurs.

The FPGA, using temporary variables, performs atomically writes into and reads from the 32 bits memory sections; that means these operations are not interrupted by any other ones.

The LUT is filled with discretized trigonometric functions in order to avoid the functions computing, or, moreover, in order to easily generate trigonometric curve profiles simply accessing sequentially the LUT locations and outputting the read values.

The memory mapping, from the PC point of view, is shown in figure 4.1.

The addresses on the right refer to the offset address; it means that these are relative addresses. The absolute address is the sum of the relative one and the base address.

ISA MEMORY I/O range is dynamically allocated: the EKU-ISA driver searches

Figure 4.1. HRT Tandem Shared memory

for an available address block and allocates this memory; the start address reached is then written on a FPGA register mapped in the PORT I/O range which is fixed and known; from now PC and EKU can communicate using the MEMORY I/O range.

In order to realize a hard real time co-processing between DSP tasks and PC tasks a synchronization between them is required. The easily way to perform a task synchronization is to use the interrupts lines.

As mentioned is chapter 3 one of the system bus interrupts is dedicated to the PC-DSP communication. In order to trigger a DSP service routine the PC code writes a value into a dedicated HRT Tandem register (PORT I/O); the FPGA is sensible to the register writing (the value written does not matter) and asserts the relative SYS\_INT line.

The synchronization in the other direction is similar: the DSP asserts a predefined bit of a system bus register; the FPGA recognizes the bit value and asserts the CPU hardware interrupt; the FPGA resets the bit written by the DSP in order to be ready for another interrupt request.

The CPU hardware interrupt line is a parameter of the EKU-ISA driver; this selection is written by the driver to a PORT I/O register at the start up in order to instruct the FPGA on the interrupt line to assert when needed.

#### 4.1.2 Host Tandem

As seen in chapter 2 the link between the EKU and a host PC can be performed in two ways:

- Serial RS232/RS422 communication protocol

- ISA protocol

This connection allows to acquire real time variables, in order to plot data while the system is running, to tune the control parameters in real time and to monitor the time occupation of the tasks running on the DSP.

The serial connection is managed, by the EKU point of view, directly by the DSP and this solution is very cheap. The main limitations are the low throughput and the short distance between the target and the host PC.

The PC solution allows to transfer data between target and host in two different ways:

- FIFO (First In First Out) mode

- DMA (Direct Access Memory) mode

FIFO mode consists in two FIFOs, managed by the ISA-core IP, allowing data exchange in both PC to DSP direction (PC2DSP FIFO) and DSP to PC direction (DSP2PC FIFO).

PC2DSP FIFO is used by the PC to set DSP and FPGA control parameters and to send commands for variables acquisitions while DSP2PC FIFO is used by the DSP to send to the PC the acquired variables.

PC2DSP FIFO is written by the PC simply accessing a dedicated PORT I/O register; once that register is read, the PC has information about the number of words stored on the FIFO, useful to avoid writing on a full FIFO.

The other end-point of this FIFO is accessed by the DSP through a system bus register: with each read operation a new value is output from the FIFO and the number of elements present on it is decremented.

DSP2PC FIFO is filled by the DSP writing on a dedicated system bus register; DSP can know the number of words stored on the FIFO reading the same register.

The output of this FIFO is accessed by the PC when it reads another dedicated PORT I/O register.

FIFO mode is completely asynchronous and it does not use any interrupts.

DMA mode is only used in the DSP to PC direction for real time variables acquisition.

It consists in a direct access to the PC RAM: DSP fills a dedicated FIFO instead of the DSP2PC one, FPGA automatically requires the access to PC DMA controller and starts transferring data from the FIFO to the PC RAM. Data flow is divided into pages of 4096 words each; at the end of each page the FPGA triggers the PC using a dedicated interrupt line. Once the page is received, PC acquires data and acknowledge the data reception writing a dedicated PORT I/O register; FPGA can now start sending another page until all the variables are sent.

The interrupt line and the DMA channel number are EKU-ISA driver parameters which writes this values to a PORT I/O register at the start up in order to instruct the FPGA.

DMA mode can reach a throughput of about 2MByte/S and allows to acquire up to tens megabytes every time.

## 4.2 Communication Interface

The communication interface discussed here is related to networks and grids between electronic control units. It is divided into the standard protocols and a custom protocol; the first ones are used to interconnect the EKU with a standard network formed by different and various digital platforms. The second is intended to create an Hard Real Time Grid between EKUs for applications that need high computational power or for redundancy reasons.

All these communications pass through the FPGA because they all use the digital connector that is directly connected to the FPGA.

#### 4.2.1 Standard Networks

As mentioned in the previous chapters, the standard networks, which the EKU is able to interconnect to, are, at the moment:

- CAN bus

- RS232, RS422, RS485

- All the protocol implemented in the Anybus products developed by HMS company

The FlexRay expansion is, at the moment, under investigation and development. All these protocols are implemented in external devices mounted on communication boards and all these boards are connected to the same communication connector of the EKU. For this reason these boards are mutually exclusive.

The drivers for all these devices are implemented in the firmware operating system, but only one of these can be used at a time.

To do this a constant named ComM is provided; this constant can assume the values CAN, ANYBUS and UART) and the user has to set this constant accordingly with the board mounted on the stack.

type ComM\_select is (CAN,ANYBUS,UART); ... -- CAN enabled / ANYBUS disabled / UART disabled constant ComM : ComM\_select := CAN; -- ANYBUS enabled / CAN disabled / UART disabled --constant ComM : ComM\_select := ANYBUS;

```

-- UART enabled / ANYBUS disabled / CAN disabled

--constant ComM : ComM_select := UART;

...

```

The firmware operating system, based on the value set, instantiates the correct IPcore and links the communication connector pins to the IP-core input and output signals.

A change of this constant value requires the firmware to be recompiled because the EKU needs to power up with the correct firmware in order to avoid collision on the communication bus at the start up.

The total pins available for the external standard communication in the EKU board is 30; these pins are called COMMxx, where xx goes from 00 to 29, and are set as bidirectional pins in the top level entity.

```

entity top_level is

port{

...

COMMOO : INOUT STD_LOGIC;

COMMO1 : INOUT STD_LOGIC;

COMMO2 : INOUT STD_LOGIC;

...

COMM29 : INOUT STD_LOGIC;

...

}

end top_level;

```

Two buses (COMM\_I and COMM\_O) are used to propagate the communication bus through the FPGA code. A pins direction bus is provided (COMM\_DIR(xx) in order to instruct the FPGA output drivers as for the field bus pins.

```

begin

. . .

<= COMM_0(0)

when COMM_DIR(0)

COMMOO

= '1' else 'Z';

<= COMM_0(1)

when COMM_DIR(1)

= '1' else 'Z';

COMM01

COMM02

<= COMM_0(2)

when COMM_DIR(2)

= '1' else 'Z';

. . .

COMM29

<= COMM_0(29) when COMM_DIR(29) = '1' else 'Z';

. . .

. . .

```

```

COMM_I(0) <= COMMOO;

COMM_I(1) <= COMMO1;

COMM_I(2) <= COMMO2;

...

COMM_I(29) <= COMM29;

...

end;

```

The pins assignment related to the value assumed by the constant ComM is performed using the construct with select; this construct implements a combinational logic multiplexer and the assignment is performed in a time as short as possible. An example of this assignment for some of the communication pins is presented below:

| with ComM select<br>COMM_O( 0)   | <= | can1_CSn<br>'1'<br>uart_HDPLX( 0)     | ANYBUS,                  |

|----------------------------------|----|---------------------------------------|--------------------------|

| with ComM select<br>COMM_DIR( 0) | <= | OUTPUT<br>INPUT<br>OUTPUT             | CAN,<br>ANYBUS,<br>UART; |

| with ComM select<br>COMM_O( 1)   | <= | can1_WRn<br>Dsp_WEn<br>uart_SHDNn( 0) | ANYBUS,                  |

| with ComM select<br>COMM_DIR( 1) | <= | OUTPUT<br>OUTPUT<br>OUTPUT            | CAN,<br>ANYBUS,<br>UART; |

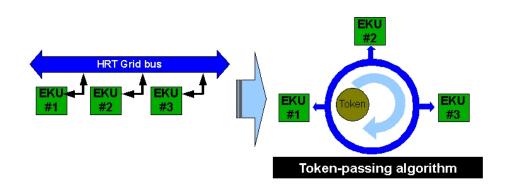

#### 4.2.2 HRT Grid

HRT Grid is, first of all, a concept: more than one EKU hardly connected in order to realize a computational grid with hard real time characteristics.

A grid is intended for few data exchange between components in scheduled period, in contrast with a network where large amount of data is exchanged as soon as possible.

The EKU composing the grid usually work on the same application and often on the same plant when the grid is used to implement a redundant system.

A smart way to work, when the application is common, is:

- EKUs share the same resources

- EKUs are synchronized

To satisfy these constraints a custom communication protocol has been developed. The grid topology chosen is shared parallel bus with dedicated data and address bus; few control signals are used to manage the arbitration.

In the actual implementation the maximum number of EKUs in the grid is limited to 8; data bus width is 16 bits (in order to be compliant with the system bus); the address bus is 5 bits wide; the maximum distance between EKUs depend on the flat cable used since the main issue is signal integrity.

The implementation has been performed completely in FGPA using the device pin drivers to access the bus while the DSP application code accesses the grid resources by means of the system bus. The ISO/OSI model is illustrated in figure 4.2: in the left side the environments (Soft Ware, Firm Ware and Conditioning Ware) where the layers are implemented are shown while in the right side the EKU target devices are linked.

The physical layer is a simple flat cable directly driven by the FPGA pins for the

Figure 4.2. HRT Grid ISO/OSI model and target devices

address and data buses, while open drain configuration (with a pull-up resistor) for control signals is used.

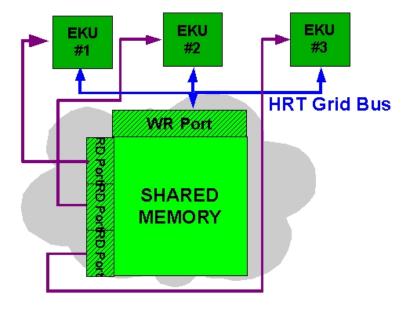

#### Shared memory

To perform the resources sharing the HRT grid has been developed basing on the shared memory concept. Since it is difficult to manage a de-localized memory, the solution that has been implemented is a distributed multi-port memory:

- Every EKU accesses to the shared variables from its own local memory (without accessing the bus)

- Variables update is performed accessing the HRT Grid bus

- Local memory is updated from the bus (even the memory located on the EKU that is performing the update operation)

From the system level point of view the shared memory has as many concurrent read ports as the number of EKUs in the grid and only one write port multiplexed between all the masters accessing the bus (see figure 4.3). With masters we mean the EKUs in the grid enabled to write on the bus.

The main issue regarding the use of a shared bus is the bus contention and then

Figure 4.3. HRT Grid shared memory: Writes use the bus; Reads are executed locally

the protocol arbitration. To overcome this problem, a solution based on the token passing algorithm has been chosen (see figure 4.4). One of the master EKUs in the grid has the task of generating the token to pass between the other masters; this EKU will be called token generator.

Figure 4.4. Data link implementation: Token Passing Algorithm

The token is constituted by a three bits number indicating the identification number (ID) of the master enabled to access the bus in that slot.

The complete operating flow concerning the token passing implementation is listed here:

- While the bus is in idle state, the token generator drives the three least significant address bits with the token number

- Until a master EKU access the bus, the token generator increments the token ID every 40nS; the token IDs generated include only the master EKUs IDs

- When a master EKU has a word to write on shared memory, recognizes proper token ID and assert a control signal (busy, active low) to indicate a new bus transaction

- The token generator releases the bus and puts the previously driven address bits to high impedance

- when the transaction has finished the EKU master responsible of that deasserts the busy signal and the token generator starts again to generate the ID sequence

The token generating process is implemented in all the EKUs of the grid but it is enabled only on one of these; this process is concurrent with the others therefore the token generator acts on the bus as all the others EKUs (writes on the bus when the token ID is correct).

The write transaction is very simple:

• The master EKU which is accessing the bus drives the busy signal (as seen before), the address bus, the data bus and then a control signal (strobe) to indicate that the data on the bus are valid

- all the EKUs in the grid (included those that are not master and that is writing on the bus) acquire the data and write it on the correspondent location of the local memory

- when the data has been saved each EKU asserts a control signal (ACK, active high, wired-and) to indicate the end of the update operation

- when the master EKU recognize the ACL signal at high level release the bus de-asserting the strobe, data and address signals

- when the strobe signal is de-asserted, each EKU release the ACK signal and the token generator accesses the bus

- if, after a time-out time, the ACK signal is still inactive, a fault interrupt is triggered on the DSP to indicate an error in the grid

All the write process takes about 100nS.

The total amount of shared memory is 32 words due to the 5 bits for the address bus; a location is reserved for the start up configuration of the grid; a second location is dedicated for the grid synchronization as we will see later in this section, while the other 30 words are divided into two parts:

- DSP shared memory (16 words)

- FPGA shared registers (14 words)

The DSP shared memory is dedicated to the real time variables of the codes running on the DSPs. Sometimes these variables are floating point or often in IQ format. IQ format is a Texas Instruments variation of the Q format to represent the numbers in fixed point mathematics; in the IQ format the data width is always 32 bits and only the number of bits after the point is indicated (i.e. IQ14 means 32 - 14 = 18bits for the signed integer field and 14 bits after the decimal point).

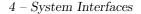

To write a 32 bits variable on the shared memory, two accesses must be performed and it means that a data inconsistency may occur (see figure 4.5).

Figure 4.5. Example of 32 bits variable writing (EKU 1) and erroneous data reading (EKU 5)

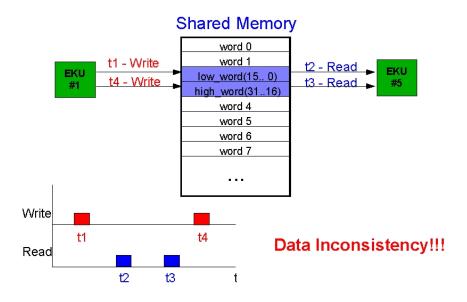

To overcome this issue a particular protocol feature has been implemented: the DSP has the possibility to write up to four words in the same transaction (burst transfer) in order to avoid data inconsistency for two 32 bits variables or up to four 16 bits variables that must be updated simultaneously (for example the filter coefficients). To perform the burst transaction the DSP writes the number of words that must be transferred on a dedicated register of the HRT Grid config IP; when the token ID is equal to those of the EKU ID, the HRT Grid IP starts the transaction similarly to the single transaction but, at the end of the first word writing, the busy signal is not released and new address and data values are set. When the burst transaction is finished (the last word has been written), the busy signal is released and the bus come back in idle state.

Data inconsistency is avoided because the local memories update is performed when the busy signal come back high (busy signal is active low); An example with the temporal actions is illustrated in figure 4.6.

Figure 4.6. Temporal flow of a 32 bits variable updating in burst mode

To avoid any other data inconsistency problems, the EKU that is reading from the shared memory has the possibility to hold the bus until all the variables, of a consistent set, has been read from the local memory; in this way the latch operation, seen in figure 4.6, does not occur between two read operations.

The FPGA shared memory is dedicated to the registers managed by the firmware user IPs; these registers can be, for example, the output of a motor encoder interface that the developer wants to share between the EKUs in the grid in order to minimize the resource redundancy, or any other product of a firmware IP the user has implemented.

In the user template 14 data registers and a control register have been provided in order to manage the registers share on the grid. The control register acts as a trigger: each bit of this register (first 14 bits) is related to a particular register to share; when one of these bits is asserted, the relative register is sent to the HRT Grid manager IP which waits the token and then writes the value on the bus.

The writing procedure is equal to that of the DSP shared memory but only single transactions are allowed.

The registers triggering can also be performed by the DSP of the same EKU: a register managed by the HRT Grid config IP has the same functionality of that of the user template; in this way an FPGA register is shared when a user IP asserts the correspondent bit in the user template OR the DSP asserts the correspondent bit by means of the system bus.

With this two possibilities the system scheduler can be located either on the FPGA or on the DSP where, usually, the main program is running.

#### **Distributed Scheduler**

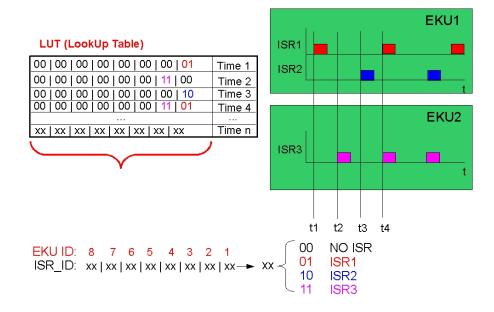

In order to satisfy the constraint about the EKU synchronization one of the 32 shared register is dedicated to the DSP interrupt service routines trigger.

As mentioned in chapter 3, three of the eight system interrupt manager lines are dedicated to the HRT Grid ISRs (ISR1, ISR2 and ISR3); a fourth interrupt service routine is reserved for faults notification.

As seen the maximum number of EKU in the grid is 8. The trigger register has been virtually divided into eight fields of two bits each (one field for each EKU); these two bits can assume four numerical values (00b, 01b, 10b, 11b). At each of these values is associated a triggering function:

- 00b does not produce effects (this is the idle situation)

- 01b produces the assertion of the ISR1

- 10b produces the assertion of the ISR2

- 11b produces the assertion of the ISR3

For example, writing 0x0020 on the trigger register will assert the ISR2 on the EKU number 3 in the grid, while writing 0xC821 on the same register will assert the ISR1 on the EKU number 1, the ISR2 on the EKUs number 3 and number six, and the ISR3 on the EKU number 8.

The trigger register is accessible by the DSP through a system bus register managed by the HRT Grid registers IP.

To make the triggering operation completely autonomous a particular IP called Scheduler has been implemented.

The task of the Scheduler IP is to trigger the ISRs on all the EKUs in the grid when particular events occur. An example can be the time driven scheduler where a counter is used as time base and when the IP recognize a particular time event, it triggers the relative distributed ISRs.

The association between the events and the triggering patterns is stored in a two columns look up table of 16 lines each. A graphical example is given in figure 4.7. Instead of the time domain, another domain often used is the angular one, especially

Figure 4.7. Time scheduling of three ISRs on two different EKUs in the grid

in the system where the HRT Grid is used to substitute the mechanical camshafts in industrial machines. In this case instead of the time, the Scheduler IP input is the angle (read for example by means of an encoder) and the LUT is filled with angular values and triggering patterns. A graphical example of the angular LUT filling is shown in figure 4.8.

| LUT (LookUp Table)                                                           |         |  |  |  |

|------------------------------------------------------------------------------|---------|--|--|--|

| 01   01   11   00   01   00   10   01                                        | 0°      |  |  |  |

| 11   11   00   10   00   00   11   00                                        | 90°     |  |  |  |

| 00   10   <mark>01</mark>   00   00   <mark>01</mark>   00   10              | 150°    |  |  |  |

| 00   <mark>01</mark>   00   10   <mark>01</mark>   00   11   <mark>01</mark> | 235°    |  |  |  |

| · · · · · · · · ·                                                            |         |  |  |  |

| xx   xx   xx   xx   xx   xx   xx   xx                                        | Angle n |  |  |  |

Figure 4.8. Scheduler IP LUT filled with angular values associated to triggering patterns

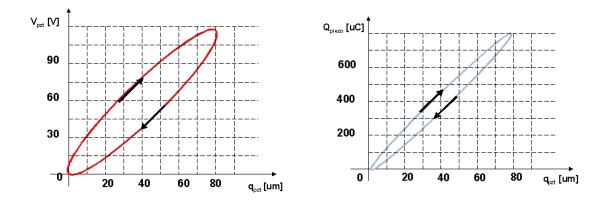

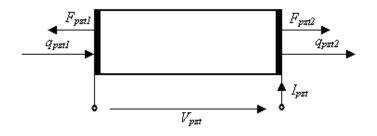

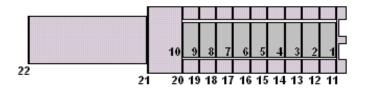

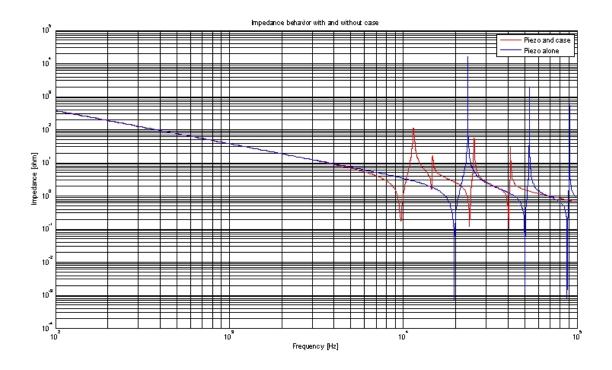

## 4.3 From/To Field