## POLITECNICO DI TORINO Repository ISTITUZIONALE

Hardware implementation of memristor-based artificial neural networks

| Original Hardware implementation of memristor-based artificial neural networks / Aguirre, Fernando; Sebastian, Abu; Le Gallo, Manuel; Song, Wenhao; Wang, Tong; Yang, J. Joshua; Lu, Wei; Chang, Meng-Fan; Ielmini, Daniele; Yang, Yuchao; Mehonic, Adnan; Kenyon, Anthony; Villena, Marco A.; Roldán, Juan B.; Wu, Yuting; Hsu, Hung-Hsi; Raghavan, Nagarajan; Suñé, Jordi; Miranda, Enrique; Eltawil, Ahmed; Setti, Gianluca; Smagulova, Kamilya; Salama, Khaled N.; Krestinskaya, Olga; Yan, Xiaobing; Ang, Kah-Wee; Jain, Samarth; Li, Sifan; Alharbi, Osamah; Pazos, Sebastian; Lanza, Mario, -In: NATURE COMMUNICATIONS ISSN 2041-1723 15:1(2024). [10.1038/s41467-024-45670-9] This version is available at: 11583/2996345 since: 2025-01-07T15:40:41Z |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This version is available at. 11363/2996343 Since. 2025-01-07113.40.412                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Publisher:<br>NATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Published DOI:10.1038/s41467-024-45670-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Terms of use:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Publisher copyright                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (Article begins on next page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## nature communications

Review article

https://doi.org/10.1038/s41467-024-45670-9

# Hardware implementation of memristorbased artificial neural networks

Received: 8 June 2023

Accepted: 1 February 2024

Published online: 04 March 2024

Fernando Aguirre<sup>1,2</sup>, Abu Sebastian <sup>3</sup>, Manuel Le Gallo <sup>3</sup>, Wenhao Song<sup>4</sup>, Tong Wang<sup>4</sup>, J. Joshua Yang <sup>4</sup>, Wei Lu<sup>5</sup>, Meng-Fan Chang <sup>6</sup>, Daniele Ielmini <sup>7</sup>, Yuchao Yang <sup>8</sup>, Adnan Mehonic <sup>9</sup>, Anthony Kenyon <sup>9</sup>, Marco A. Villena <sup>1</sup>, Juan B. Roldán <sup>10</sup>, Yuting Wu<sup>5</sup>, Hung-Hsi Hsu<sup>6</sup>, Nagarajan Raghavan<sup>11</sup>, Jordi Suñé <sup>2</sup>, Enrique Miranda<sup>2</sup>, Ahmed Eltawil <sup>12</sup>, Gianluca Setti<sup>12</sup>, Kamilya Smagulova<sup>12</sup>, Khaled N. Salama <sup>12</sup>, Olga Krestinskaya <sup>12</sup>, Xiaobing Yan <sup>13</sup>, Kah-Wee Ang<sup>14</sup>, Samarth Jain<sup>14</sup>, Sifan Li<sup>14</sup>, Osamah Alharbi <sup>1</sup>, Sebastian Pazos <sup>1</sup>& Mario Lanza <sup>1</sup>

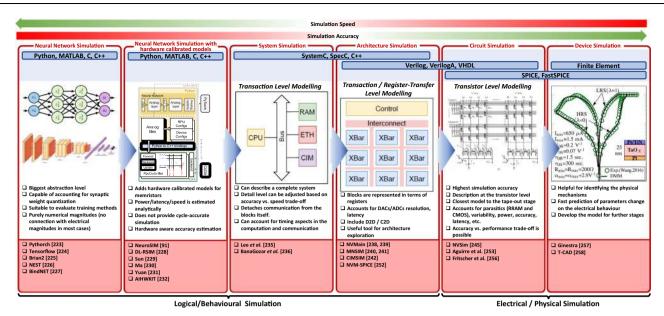

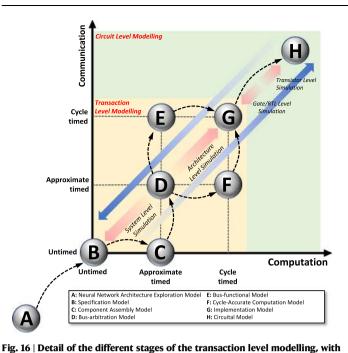

Artificial Intelligence (AI) is currently experiencing a bloom driven by deep learning (DL) techniques, which rely on networks of connected simple computing units operating in parallel. The low communication bandwidth between memory and processing units in conventional von Neumann machines does not support the requirements of emerging applications that rely extensively on large sets of data. More recent computing paradigms, such as high parallelization and near-memory computing, help alleviate the data communication bottleneck to some extent, but paradigm-shifting concepts are required. Memristors, a novel beyond-complementary metal-oxide-semiconductor (CMOS) technology, are a promising choice for memory devices due to their unique intrinsic device-level properties, enabling both storing and computing with a small, massively-parallel footprint at low power. Theoretically, this directly translates to a major boost in energy efficiency and computational throughput, but various practical challenges remain. In this work we review the latest efforts for achieving hardware-based memristive artificial neural networks (ANNs), describing with detail the working principia of each block and the different design alternatives with their own advantages and disadvantages, as well as the tools required for accurate estimation of performance metrics. Ultimately, we aim to provide a comprehensive protocol of the materials and methods involved in memristive neural networks to those aiming to start working in this field and the experts looking for a holistic approach.

The development of sophisticated artificial neural networks (ANNs) has become one of the highest priorities of technological companies and governments of wealthy countries, as they can boost the fabrication of artificial intelligence (AI) systems that generate economic and social benefits in multiple fields (e.g., logistics, commerce, health care,

national security, etc.)¹. ANNs are able to compute and store the huge amount of electronic data produced (either by humans or machines), and to execute complex operations with them. Examples of electronic products that contain ANNs with which we interact in our daily lives are those that identify biometric patterns (e.g., face, fingerprint) for access

A full list of affiliations appears at the end of the paper. 🖂 e-mail: mario.lanza@kaust.edu.sa

control in smartphones<sup>2</sup> or online banking apps<sup>3</sup>, and those that identify objects in images from social networks<sup>4</sup> and security/traffic cameras<sup>5</sup>. Beyond image recognition, other examples are the engines that convert speech to text in computers and smartphones<sup>6</sup>, natural language processing as for example the novel automated chat system chat-GPT<sup>7</sup>, and those that provide accurate recommendations for online shopping based on previous behaviours from ourselves and/or people in our network<sup>8</sup>.

ANNs can be understood as the implementation of a sequence of mathematical operations. The structure of ANNs consists of multiple nodes (called neurons) interconnected to each other (by synapses), and the learning is implemented by adjusting the strength (weight) of such connections. Modern ANNs are implemented via software in general-purpose computing systems based on a central processing unit (CPU) and a memory —the so-called Von Neumann architecture. However, in this architecture a large amount of the energy consumption and computing time is related to continuous data exchange between both units, which is not efficient. The computing time can be accelerated by

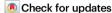

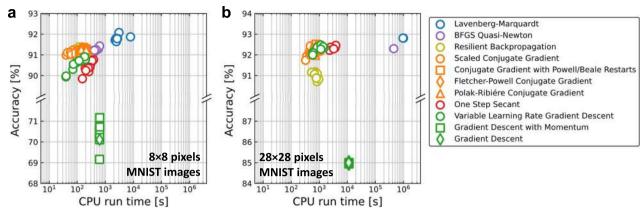

using graphics processing units (GPUs) to implement the ANNs (see Fig. 1a), as these can perform multiple operations in parallel<sup>10-12</sup>. However, this approach consumes even more energy, which requires large computing systems and thereby cannot be integrated in mobile devices. Another option is to use field programable gate arrays (FPGAs), which consume much less energy than GPUs while providing an intermediate computing efficiency between CPUs and GPUs<sup>13-17</sup>. A survey carried out by Guo et al.<sup>18</sup> on the existing hardware solutions for ANN implementation and their performance is condensed in Fig. 1b.

In the past few years, some companies and universities have presented application specific integrated circuits (ASICs) based on the complementary metal oxide semiconductor (CMOS) technology that are capable to compute and store information in the same unit. This allow such ASICs to perform multiple operations in parallel very fast, making them capable of mimicking, directly in the hardware, the behaviour of the neurons and synapses in the ANN. A comprehensive list of these ASICs comprising those such as the Google TPU<sup>19</sup>, Amazon inferentia<sup>20</sup>, Tesla NPU<sup>21</sup>, etc., are summarized in ref. 22. Such integrated

Fig. 1 | Computing power demand increase and platform transition from Von-Neumann towards highly parallelized architectures. a The increase in computing power demands over the past four decades expressed in petaFLOPS per days. Until 2012, computing power demand doubled every 24 months; recently this has shortened to approximately every 2 months. The colour legend indicates different

application domains<sup>10</sup>. Mehonic, A., Kenyon, A.J. Brain-inspired computing needs a master plan. Nature 604, 255–260 (2022), reproduced with permission from SNCSC. **b** A comparison of neural network accelerators for FPGA, ASIC, and GPU devices in terms of speed and power consumption. *GOP/s* giga operations per second, *TOP/s* tera operations per second.

circuits can be grouped in two categories. On one hand, dataflow processors are custom-designed processors for neural network inference and training. Since neural network training and inference computations can be entirely deterministically laid out, they are amenable to dataflow processing in which computations, memory accesses, and inter-ALU communications actions are explicitly/statically programmed or placed-and-routed onto the computational hardware. On the other hand, processor in memory (PIM) accelerators integrate processing elements with memory technology. Among such PIM accelerators are those based on an analogue computing technology that augments flash memory circuits with in-place analogue multiply-add capabilities. Please refer to the references for the Mythic<sup>23</sup> and Gyrfalcon<sup>24</sup> accelerators for more details on this innovative technology.

Previously mentioned ANNs and those reported in detail in the survey presented in ref. 22 belongs to the subgroup of so-called deep neural networks (DNNs). In a DNN the information is represented with values that are continuous in time and can achieve high data recognition accuracy by using at least two layers of nonlinear neurons interconnected by adjustable synaptic weights<sup>25</sup>. Conversely, there is an alternative information codification which gave birth to another type of ANNs, the Spiking Neural Networks (SNN). In SNNs the information is coded with time-dependent spikes, which remarkably reduces the power consumption compared to DNNs<sup>26</sup>. Moreover, the functioning of SNNs is more similar to the actual functioning of biological neural networks, and it can help to understand complex mammal's neural systems. Intel probably has the most extensive research program for evaluating the commercial viability of SNN accelerators with their Loihi technology<sup>27,28</sup>, and Intel Neuromorphic Development Community<sup>29</sup>. Among the applications that have been explored with Loihi are target classification in synthetic aperture radar and optical imagery<sup>30</sup>, automotive scene analysis<sup>31</sup>, and spectrogram encoder<sup>27</sup>. Further, one company, Innatera, has announced a commercial SNN processor<sup>32</sup>. Also, the platforms developed by IBM (TrueNorth<sup>33</sup>), and Tsingshua<sup>34</sup> are well known examples of the research effort of both the industry and the academia in this field.

However, fully-CMOS implementations of ANNs require tens of devices to simulate each synapse, which threatens energy and area efficiency, and thereby renders large-scale systems impractical. As a result, the performance of CMOS-based ANNs is still very far from that of biological neural networks. To emulate the complexity and ultra-low power consumption of biological neural networks, hardware platforms for ANNs must achieve an ultra-high integration density (>1 Terabyte per cm²) and low energy consumption (<10 fJ per operation)<sup>35</sup>.

Recent studies have proposed that the use of memristive devices to emulate the synapses may accelerate ANN computational tasks while reducing the overall power consumption and footprint<sup>36-42</sup>. Memristive devices are materials systems whose electrical resistance can be adjusted to two or more stable (i.e., non-volatile) states by applying electrical stresses<sup>43</sup>. Memristive devices that exhibit two nonvolatile states are already being commercialized as standalone memory<sup>44,45</sup>, although their global market is still small (~621 million USD by 2020, i.e., ~0.5% of the 127-billion-worth standalone memory market<sup>46</sup>). However, memristive devices can also exhibit three disruptive attributes particularly suitable for the hardware implementation of ANNs: i) the possibility to program multiple non-volatile states (up to -100<sup>47,48</sup>, and even -1000<sup>49</sup>), ii) a low-energy consumption for switching (~10fJ per state transition with zero-static consumption when idle<sup>50</sup>), and iii) a scalable structure appropriate for matrix integration (often referred to as crossbar<sup>51</sup>) and even 3D stacking<sup>52</sup>. Moreover, the switching time can be as short as 85 ps<sup>42</sup>.

So far, several groups and companies have claimed the realization of hybrid CMOS/memristor implementations of ANNs<sup>53-61</sup>, –from now on, memristive ANNs– with performance that is superior to that of fully-CMOS counterparts. However, most of those studies in fact only measured the figures-of-merit of one/few devices and simulated the

accuracy of an ANN via software<sup>62-67</sup> in such type of studies the connection between the memristors fabricated and the ANN is relatively weak. Few studies went beyond that and built/characterized crossbar arrays of memristive devices<sup>48,68-70</sup>, but that are still very far from real full-hardware implementations of all the mathematical operations required by the ANN. The most advanced studies in this field have reported fully integrated memristor-based compute-in-memory systems<sup>48,53-55,58,59,61,71-73</sup>, but a systematic description of essential details on the device structure or circuit architecture are generally lacking in these reports.

In this article we provide a comprehensive step-by-step description of the hardware implementation of memristive ANNs for image classification —the most studied application often used to benchmark performance, describing all the necessary building blocks and the information processing flow. For clarity, we consider relatively simple networks, being the multilayer perceptron the most complex case. We take into account the challenges arising at both the device and circuit levels and discuss a SPICE-based approach for their study in the design stage, as well as the required circuital topologies for the fabrication of a memristive ANN.

### **Structure of memristor-based ANNs**

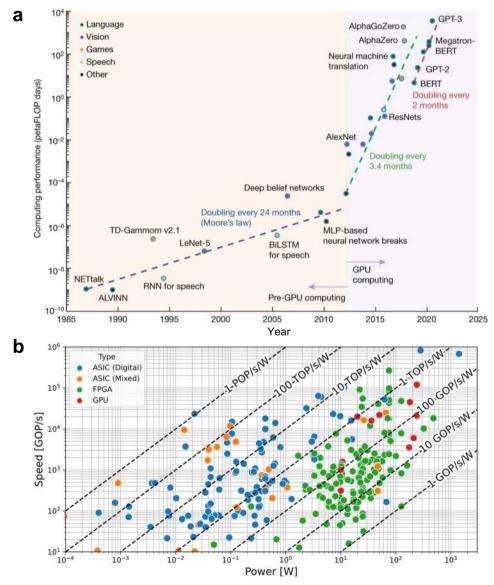

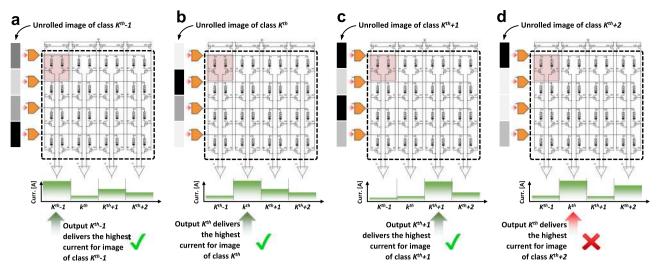

Figure 2 shows a flowgraph depicting the generalized structure of an ANN; it has multiple inputs (for single channel images like indexed color, grayscale and bitmap images, there are as many inputs as pixels the image to classify has) and several outputs (as many as types/classes of images the ANN will recognize). As it can be seen, the ANN consists of multiple mathematical operations (green boxes), such as vector matrix multiplication (VMM), activation function, and softargmax function. Among all the critical operations in the ANN, the VMM is the most complex and demanding, and it is carried out multiple times both during the training process and inference. Hence, the development of new hardware for ANN implementation is strongly oriented to realize VMM operations in a more efficient way. Interestingly, the VMM operation -often understood as multiply and accumulate (MAC) routine-can be implemented using a crossbar array of memory elements. Those memory devices could be either charge-based memories as well as resistance-based memories<sup>25,74</sup>.

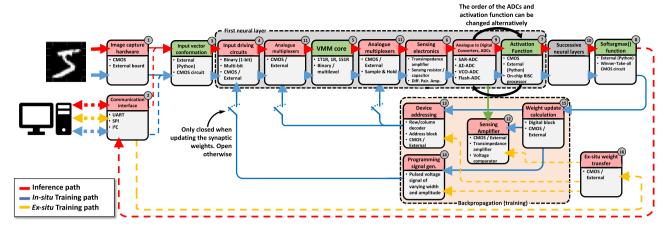

Before explaining memristive hardware for ANN, in this paragraph we describe the state of the art of CMOS hardware for ANNs, to provide the author with a comprehensive picture of the different technologies available for hardware based ANNs. Among charge-based memories, SRAM cells (a bi-stable transistor structure typically made of two CMOS inverters connected back-to-back which retains a charge concentration, see Fig. 3a for an example of the structure of a crossbar array of 6T SRAM) have been widely used for VMM<sup>75–77</sup>. If the elements of the input vector and the weight matrix are limited to signed binary values, the multiply operation is simplified to a combination of XNOR and ADD functions carried out directly through SRAM cells. An example of this is the work by Khwa et al., which reports a compute in memory system based on a crossbar array of 6T SRAM memory cells as binary synaptic connections that uses binary inputs/outputs<sup>78</sup>. The proposed circuit comprises 4 kb synapses fabricated in a 65 nm CMOS process and reported an energy efficiency of 55.8 TOPS per W. In cases where x is non-binary, one approach is to employ capacitors in addition to the SRAM cells<sup>76,77,79</sup>, involving a three-step process. However, a major drawback of SRAM memories is their volatile nature. Due to the low field-effect transistor barrier height (0.5 eV), the charge constantly needs to be replenished from an external source and hence SRAM always needs to be connected to a power supply. An alternative memory element for VMM operation is the flash memory cell<sup>80,81</sup>, in which the charge storage node is coupled to the gate of a FET with charge stored either on a conductive electrode surrounded by insulators (floating gate) or in discrete traps within a defective insulator layer (charge trapping layer). Unlike in SRAM, the barrier height of the

**Fig. 2** | **Generalized block diagram indicating the required circuital blocks to implement a memristive ANN for pattern classification.** Green blocks (3, 5, 7 and 8) indicate the required mathematical operations (such as the VMM or activation functions). Red blocks (1, 2, 4, 6, 9, 11, 12, 13, 14, 15, 16) identify the required circuits for signal adaptation and/or conversion. The data path followed during the inference (or forward pass) is indicated by the red arrows/lines. The data path followed for in-situ training is indicated by the blue arrows/lines. The data path followed

under ex-situ training is shown by the yellow arrows/lines. For each box, the upper (colored) part indicates the name of the function to realize by the circuital block, and the bottom part indicates the type of hardware required. The box titled successive neural layers would encompass multiple sub-blocks with a structure similar to the group titled First neural layer. 1S1R stands for 1Selector 1 Resistor while 1R stands for 1 Resistor. UART, SPI and I<sup>2</sup>C are well known communication standards. RISC stands for Reduced Instruction Set Computer.

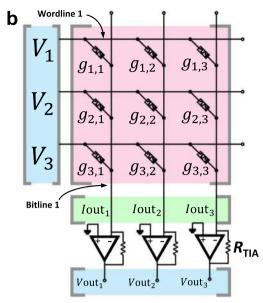

storage node is sufficiently high for long-term data retention. Also, flash-based VMM operates in a slightly different manner than SRAMbased VMM. In Flash-based VMM, each memory element contribute a different amount to the current in each column of the crossbar depending on the voltage applied to the input or crossbar row and matrix element are stored as charge on the floating gate<sup>81</sup> (i.e., multiplication) and all the currents in a column are instantaneously summed (i.e., accumulation) by Kirchhoff's currents law. Because the devices can be accessed in parallel along a BL, NOR Flash has generally been preferred over NAND Flash for in-memory computing. This is the case of the work by Fick et al from the company Mythic<sup>23</sup>, which relies on a 1024×1024 NOR Flash array to develop an analogue matrix processor for human pose detection in real time video processing. However, there is recent work describing the use of 3D NAND, consisting of vertically stacked layers of serially connected FLASH devices, whereby each layer of the array encodes a unique matrix<sup>82</sup>. This approach could help to overcome the scalability issue of NOR Flash, which is difficult to scale beyond the 28 nm technology node. The proposed 3D-aCortex accelerator83 is a fully CMOS implementation that relies on a commercial 3D-NAND flash crossbar array as synaptic element. Partial outputs from multiple crossbars are temporally aggregated and digitized using digital counters, shared by all the crossbars along a row of the grid, avoiding the communication overhead of performing these reductions across multiple levels of hierarchy. The entire 3D array shares a global memory and a column of peripheral circuits, increasing its storage efficiency. This is however still theoretical and is yet to be fabricated. Nonetheless, the write operation on flash memories requires high voltages (typically >10 V) and entails significant latency (>10 µs) due to the need to overcome the storage node barriers. These problems can be potentially solved using resistance-based memories, or memristors as memory element at the intersections of the crossbar, as they can realize the multiplication operation by Ohm's Law ( $I=V\cdot G$ , where *I* is current, *V* is the input voltage and *G* is the conductance of each memristor), while reducing the energy consumption and area footprint as well as providing CMOS compatible operation voltages. The structure of memristive crossbar arrays for VMM is depicted in Fig. 3b, c: a common integration option is to place a CMOS transistor in series with the memristor to control the current through it (Fig. 3b) in a so called 1 transistor 1 resistor (1T1R) structure, while the highest integration density would be achieved by a crossbar comprising no transistors, i.e., considering cells usually referred to as 1 resistor/

memristor (1R or 1M) structures or passive crossbar (Fig. 3c). When using crossbar arrays of memristors to perform VMM operations, additional circuitry might be needed at the input and output to sense and/or convert electrical signals (see red boxes in Fig. 2). Examples of such circuits are digital-to-analogue (DAC), analogue-to-digital (ADC) converters and transimpedance amplifiers (TIA). Note that other studies employed implementations slightly different from this scheme, i.e., combining or avoiding certain blocks to save area and/or reduce power consumption (see Table 1).

In the following subsections we describe in detail all the circuital blocks required for a truly full-hardware implementation of a memristive ANN. To provide both a clear global picture and detailed explanations, the titles of the sub-sections correspond to the names of the blocks in Fig. 2.

## Image capture hardware (block 1) and input vector conformation (block 3)

An image (or pattern) is a collection of pixels with different colours arranged in a matrix form (referred as  $p \times p$  in this article). In this work, we will consider grayscale images, in which the colour of those pixels can be codified by one single value. However, in coloured images, each pixel is represented by 3 (in RGB encoding) or 4 (in CMYK encoding) values, this arranged in a tensor fashion, i.e.,  $p \times p \times 3$  or  $p \times p \times 4$ . Both the training and testing of an ANN for image classification are conducted by presenting large datasets of images to its inputs. In a real ANN each image could come directly from an embedded camera (block 1), or it could be provided as a file by the user (block 2). Depending on the format of the image (e.g., black/white, 8-bit \*.bmp, 24-bit \*.bmp, \*.jpg, \*.png, among many others) the range of possible colours (encoded as numerical values) for each pixel will be different. Each of the above mentioned approaches to feed images to the neural network implies different hardware overhead. For the case of on-the-fly image classification, a CMOS imager is necessary to capture the input images<sup>82,83</sup>. For instance, ref. 84 uses a 480×330 pixel image sensor, with each pixel consisting of a photo diode and four transistors that generates an analogue signal whose amplitude is proportional to the light intensity. Then a 5×6 pixel binary image is generated by mapping 96×55 neighbourhood pixels into one pixel in the binary image. A similar approach is considered in ref. 85 where a 640×480 pixels image is captured by an image sensor and then resized to a 16×16 image. The resizing procedure and the need of such a procedure will be covered later in this Sub-

Multi-level storage is possible by more complex SRAM cells (larger cell area)

Fig. 3 | Non-Von Neumann vector-matrix-multiplication (VMM) cores reported in the literature. a Full-CMOS SRAM (Static Random Access Memory) crossbar array, **b** Hybrid memristor/CMOS 1T1R crossbar array and **c** Full-memristive passive crossbar array. All cases assume a crossbar array integration structure which performs the Multiply-and-Accumulate (MAC) by exploiting the Kirchhoff's law of currents. The use of memristors allows a smaller footprint per synapse as a lower number of smaller devices is employed. Passive crossbar arrays of memristors allow the highest possible integration density, yet they are still an immature technology

with plenty of room for optimization. a<sup>290</sup> Yamaoka, M. Low-Power SRAM. In: Kawahara, T., Mizuno, H. (eds) Green Computing with Emerging Memory. Springer, New York, NY (2013), reproduced with permission from SNCSC. **b** is adapted with permission under CC BY 4.0 license from ref. 54. c is adapted with permission under CC BY 4.0 license from ref. 93. F is the feature size of the litography and the energy estimation is on the cell-level. FEOL and BEOL stands for Front End Of Line and Back End Of Line, respectively.

section. Both cases consider an FPGA in order interface the image acquisition system (i.e. CMOS image sensor and the resizing algorithm) with the memristor crossbar and its peripheral circuitry. On the other hand, some studies exclusively focused on the memristor crossbar use an on-chip communication interface to acquire the image from a computer (e.g. ref. 54 uses a serial communication port) already shaped in the required input format.

Regarding the input images, there are multiple datasets of images online available for ANN training and testing. Some of the most commonly used ones are: 1) MNIST (Modified National Institute of Standards and Technology), which is basically a dataset containing 70,000 greyscale images showing handwritten numbers from 0 to 9 (i.e., around 7,000 for each number); 60,000 of them used for training and 10,000 for testing86; 2) CIFAR (Canadian Institute for Advanced Research), which contains 60, 000 color images divided into 10 classes for CIFAR-10 and 100 classes for CIFAR-100<sup>87</sup>; 3) ImageNet, one of the largest image datasets, which consists of over 1.2 million labelled from 1000 classes for the ImageNet competition<sup>88</sup>. MNIST is a good starting point, since this simple dataset can be classified with even small neural networks. For benchmarking a device or a chip, it is essential to evaluate the accuracy of standard deep neural network models like VGG<sup>89</sup> and ResNet90 on CIFAR and ImageNet dataset by utilizing architecturelevel simulation and realistic hardware statistics 91,92. For clarity, here we illustrate with MNIST dataset. The number of types/classes of images (referred to as *m* in this article) in the MNIST dataset is 10. The images are compressed in a \*.idx3-ubyte file that can be opened with MATLAB; each of them comes in grayscale and with a resolution of 28×28 pixels. In Python, the MNIST images can be found embedded in a library named Keras. The training images are used to let the ANN understand the characteristic features of each pattern (i.e., the numbers), and the testing images are presented to the ANN (after training) to be classified. A few examples of these images can be seen in Fig. 4a, where the X and Y axis stand for the pixel index. Pixel's brightness is codified in 256 grey levels between 0 (fully OFF, black) and 255 (fully ON, white). In the MNIST dataset, each of the 60,000  $p \times p$  training images is represented as a  $p^2 \times 1$  column vector, and all these vectors are horizontally

<sup>\*\*</sup> Analogue synaptic weight is desired but usually only a finite number of stable levels is available

| apre    | rable 1   Fist of reported prototypes in the uterature and the |                                              |               |         |                            |                   |                          |                        |                                                             |                       |                           |                         |                              |

|---------|----------------------------------------------------------------|----------------------------------------------|---------------|---------|----------------------------|-------------------|--------------------------|------------------------|-------------------------------------------------------------|-----------------------|---------------------------|-------------------------|------------------------------|

| Work(s) | Device                                                         | NN Type/<br>Dataset                          | Crossbar size | CMOS    | ADC                        | Cell<br>Structure | Input cir-<br>cuit (DAC) | Sensing<br>Electronics | Activation function                                         | Row/Col.<br>Selectors | Softmax Activation Func.  | Inference/<br>training  | Weight<br>Prog.<br>circuitry |

| 57      | Au/Pd/WO <sub>x</sub> /Au                                      | SLP, Sparse<br>coding, MLP/<br>Greek letters | 54 × 108      | 180 nm  | On-chip<br>(13-bit)        | 1R                | On-chip (6-bit)          | Charge<br>integration  | On-chip digital<br>(Sigmoid)                                | On-chip               | Off-chip<br>(Software)    | Inference &<br>training | On-chip                      |

| 55      | TiN/TaOx/<br>HfOx /TiN                                         | CNN/MNIST                                    | 128 × 16      | 130 nm  | Off-chip<br>(8-bit)        | 1T1R              | On-chip (1-bit)          | Charge<br>integration  | Off-chip (software:<br>ReLU and max.<br>Pooling)            | On-chip               | Off-chip<br>(Software)    | Inference & training    | Off-chip                     |

| 102     | Pt/Ta/Ta2O5/<br>Pt/Ti                                          | MLP/MNIST                                    | 128 × 64      | 2 µm    | N/A                        | 1T1R              | N/A                      | N/A                    | Off-chip hard-<br>ware: ReLU)                               | Off-chip              | Off-chip<br>(Software)    | Learning & training     | Off-chip                     |

| 61      | No data (propietary dev.)                                      | BNN, MNIST,<br>CIFAR-10                      | 128 × 64      | 90 nm   | On-chip<br>(3-bit)         | 1T1R              | Not<br>implemented       | On-chip (VSA)          | On-chip (Binary)                                            | On-chip               | Off-chip (soft-<br>ware)* | Inference<br>only       | Off-chip                     |

| 113     | Ta/TaOx/Pt                                                     | CNN/MNIST                                    | 64 × 64       | 180 nm  | On-chip                    | 1T1R              | On-chip                  | On-chip (TIA)          | Off-chip (software)*                                        | On-chip               | Off-chip (soft-<br>ware)* | Inference<br>only       | Off-chip                     |

| 114,115 | TaOx                                                           | CNN/MNIST                                    | 64 × 64       | 180 nm  | On-chip<br>(10-bit)        | 1T1R              | On-chip                  | On-chip (TIA)          | Off-chip (software)*                                        | On-chip               | Off-chip (soft-<br>ware)* | Inference<br>only       | Off-chip                     |

| 219,    | W/TiN/TiON                                                     | BNN/MNIST                                    | 100 × 100     | 65 nm   | On-chip<br>(3-bit)         | 1T1R              | N/A                      | On-chip (CSA)          | Off-chip (FPGA: max.<br>Pooling)                            | On-chip               | Off-chip (FPGA)           | Inference<br>only       | Off-chip                     |

| 116     | Pt/SiOxAg/Pt/Ti,<br>Ta/Pd/HfO2/Pt/Ti                           | CNN/ 'U', 'M, 'A', 'A', 'S'                  | & × & &       | No data | Off-chip                   | 1T1R              | On-chip                  | Off-chip (TIA)         | On-chip (ReLU), Off-<br>chip (software: max.<br>Pooling)    | Off-chip              | Off-chip (MCU)            | Inference &<br>training | Off-chip                     |

| 272     | TiN/HfO2/Ti/TiN                                                | BNN/MNIST,<br>CIFAR-10                       | 1 Kb          | 130 nm  | On-chip                    | 2T2R              | Not<br>implemented       | On-<br>chip (PCSA)     | On-chip (Binary)                                            | On-chip               | On-chip<br>(Binary)       | Inference<br>only       | Off-chip                     |

| 66      | W/Ta <sub>2</sub> O <sub>5</sub> /TaO <sub>x</sub> /W          | MLP/MNIST                                    | 2 Mb          | 180 nm  | On-chip<br>(1-bit)         | 1T1R              | On-chip (1-bit)          | On-chip                | No data                                                     | On-chip               | No data                   | Inference<br>only       | Off-chip                     |

| 100     | AlCu/TiN/Ti/<br>HfO <sub>2</sub> /TiN                          | MLP/                                         | 32 × 32       | 150 nm  | On-chip<br>(1 or<br>3-bit) | 1T1R              | On-chip (1-bit)          | On-chip                | Off-chip (software)*                                        | On-chip               | Off-chip (soft-<br>ware)* | Inference<br>only       | On-<br>chip (SRAM)           |

| 122     | PCM (no<br>more data)                                          | MLP/MNIST                                    | 512 × 1024    | 180 nm  | No data                    | 3T1C<br>+ 2PCM    | No data                  | Off-chip<br>(software) | Off-chip (Soft-<br>ware: ReLU)                              | Off-chip              | Off-chip<br>(Software)    | Inference<br>only       | Off-chip                     |

| 71,73   | PCM (no<br>more data)                                          | MLP/MNIST,<br>ResNET-9/<br>CIFAR-10          | 256 × 256     | 14 nm   | On-chip                    | 4T4R              | On-chip (8-bit)          | On-chip<br>(CCO-based) | On-chip (ReLU)                                              | On-chip               | Off-chip<br>(Software)    | Inference<br>only       | On-chip                      |

| 72,     | PCM (no<br>more data)                                          | MLP/MNIST                                    | 512 × 512     | 14 nm   | Off-chip                   | 4T4R              | On-chip (8-bit)          | On-chip                | Off-chip (Sigmoid)                                          | On-chip               | Off-chip (FPGA)           | Inference<br>only       | On-chip                      |

| 273     | No data                                                        | CNN/<br>CIFAR-10                             | 256 × 512     | 55 nm   | On-chip                    | 1T1R              | No data                  | On-chip                | Off-chip (FPGA)                                             | On-chip               | Off-chip (FPGA)           | Inference<br>only       | Off-chip                     |

| 274     | TiN/HfO2/Ti/TiN                                                | CNN/MNIST                                    | 18 KB         | 130 nm  | Off-<br>chip*              | 1T1R              | Off-chip*                | Off-chip*              | Off-chip (FPGA)                                             | Off-chip*             | Off-chip (FPGA)           | Inference<br>only       | On-chip                      |

| 123     | TiN/HfO2/Ti/TiN                                                | BNN/MNIST                                    | 1 Kb          | 130 nm  | N/A                        | 2T2R              | N/A                      | On-chip                | Off-chip (software)*                                        | On-chip               | Off-chip (soft-<br>ware)* | Inference<br>only       | Off-chip                     |

| 275     | -/HfO <sub>2</sub> /TaO <sub>x</sub> /-                        | MLP/MNIST                                    | 158.8 Kb      | 130 nm  | On-chip<br>(8-bit)         | 2T2R              | On-chip (8-bit)          | Charge<br>integration  | Off-chip                                                    | On-chip               | Off-chip                  | Inference<br>only       | Off-<br>chip (FPGA)          |

| 09      | TiN/HfO <sub>2</sub> /<br>TaO <sub>X</sub> /TiN                | CNN/MNIST,<br>CIFAR-10                       | 256×256       | 130 nm  | On-chip<br>(8-bit)         | 1T1R              | On-chip                  | Charge<br>integration  | On-chip (analog:<br>ReLU), Off-chip<br>(FPGA: max. Pooling) | On-chip               | Off-chip (FPGA)           | Off-chip<br>(Software)  | On-chip                      |

\*Assumed as no information is provided.

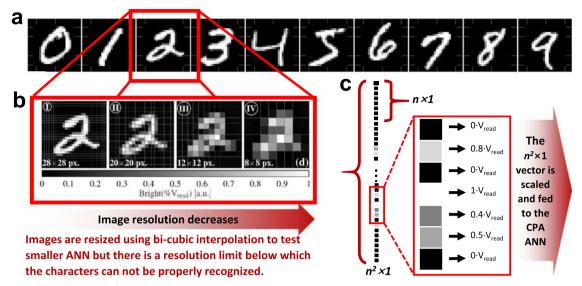

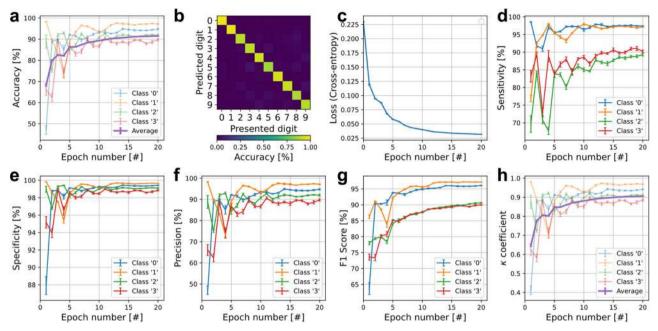

Fig. 4 | Example of a widely popular image database used for ANNs training and test, and how they are feed to the network. a Samples of the MNIST dataset of handwritten numeric digits considered in this article. In all cases images are represented in  $28 \times 28$  px. Pixel brightness (or intensity) is codified in 256 levels ranging from 0 (fully OFF, black) to 1 (fully ON, white). **b** Readability loss as the

resolution decreases from  $28 \times 28$  pixels (case I) to  $8 \times 8$  (case IV). **c** Schematic representation of the unrolling of the image pixels. Note that each of the *n* image columns of pixels are vertically concatenated to reach a  $n^2 \times 1$  column vector. It is then scaled by  $V_{READ}$  to produce a vector of analogue voltages that is fed to the ANN.

concatenated to render a  $p^2 \times 60,000$  matrix. Similarly, the test dataset consists of a  $p^2 \times 10,000$  matrix. In both cases, each of the  $p^2$  pixels must be fed to the crossbar array for further processing.

As previously mentioned, the simplest ANN architectures (multilayer perceptrons) should have as many inputs as pixels there are in the images to be classified. In software based ANNs, this is not a challenge. However, the available inputs in hardware ANNs are limited by the maximal size of the memristor crossbar. In the literature, such a challenge has been tackled considering different approaches: For instance, given the MNIST dataset in which images have a resolution of 28 × 28 pixels one option is to implement the synaptic layer using multiple crossbars to fit the 784 inputs (e.g.,  $13.64 \times 64$  or  $4.256 \times 256$ crossbars would be needed93). However, for research efforts focused on the device level, this is usually out of reach as requires a nonstraightforward CMOS - memristor integration. Another option is to consider more complex neural networks, such as the convolutional neural networks (CNN) $^{55}$ . LeNet-5 (a kind of CNN) first layer is 25 × 6, which can be implemented with a 64×64 crossbar. In fact, image classification tasks in modern deep learning usually rely on a convolutional layer. As for the previous case, this is not easy to implement for research projects centred on the device level as it also requires complex hybrid CMOS - memristor integration. Nonetheless, in some cases, the first convolutional layers are implemented on software and off-chip to reduce the image dimensionality and then the resulting feature vector is feed to the memristive part of the ANN. Note that in this case, device non-idealities are not equally represented throughout the network, and their influence is only assessed for the fullyconnected part<sup>55</sup>. Finally, other option is to rescale each of the images of the original MNIST dataset (in this work, represented by block 3). For example, if our crossbar has 64 inputs, then the image would have to be rescaled from  $28 \times 28$  to  $8 \times 8$  (i.e., 64 pixels); the size of the rescaled image will be referred as  $n \times n$ . The rescaling can be easily done via software, using for example MATLAB and its Deep Learning Toolbox as language/platform to carry out this type of computational operations, or Python altogether with the TensorFlow, Keras or Pytorch libraries. However, and as shown in Fig. 4b, the aggressively rescaled images becomes barely readable and therefore the entire dataset is changed and so it is the benchmark, i.e. inference results obtained for the 8×8 MNIST rescaled images should only be compared

with 8×8 MNIST results and not with the original MNIST benchmark results. This is similar to using a custom-made dataset. With this in mind, and provided the frequent use of this methodology in the literature, we will consider its usage yet stressing the aforementioned considerations, and we encourage authors not to rescale the image dataset if aiming to compare their results against the original datasets.

As an example, Supplementary Algorithm 1 shows the MATLAB code used for image dataset rescaling from  $28 \times 28$  to  $8 \times 8$  pixels. Before downscaling the images, each of them needs to be reshaped from a  $p^2 \times 1$  column vector to a  $p \times p$  matrix, using the MATLAB function reshape(). Then, the image is resized to the desired  $n \times n$  size in pixels by the MATLAB function imresize()<sup>94</sup>. This function receives as argument the desired down-sampling method, which in this example was selected to be the bi-cubic interpolation (as in other articles in the field of memristive ANNs<sup>54</sup>). The results of the rescaling for a single image are shown in Fig. 4b. Note that using this method, values outside the [0, 1] range are expected. Thereby, the downscaled image is processed and any output value exceeding such range is truncated to 0 or 1. The rescaled images are then reshaped back to the  $n^2 \times 1$  column vector representation format and stored in a new matrix. Now this image can be used as input in the crossbar array of memristors.

#### Input driving circuits (Block 4)

The colour of each pixel in the image (represented as  $n^2 \times 1$  column) is codified as a voltage that is applied to a row in the crossbar (i.e., wordline), as depicted in Fig. 4c, resulting in a vector V of analogue voltages  $V_{\rm i}$ . If the image is black-white (i.e., 2 possible values), the values of the voltage  $V_i$  of each pixel will be 0 and  $V_{READ}$  ( $V_{READ}$  being a reference voltage defined by the application); however, the colour of each pixel can also range within a greyscale, which leads to a range of analogue voltages. For instance, the colour of each pixel in the 8-bits  $p \times p$  images of the MNIST dataset (and hence, the colour of each pixel in the resized  $n \times n$  image to be input to the crossbar) varies within a greyscale of  $2^8 =$ 256 possible values (codified in binary representation from 00000000 to 11111111), meaning that the voltages to be applied to each input of the crossbar may take values such as OV,  $V_{READ}/256$ ,  $2 \cdot V_{READ}/256$ , etcetera until  $V_{READ}$ . Hence, an 8-bit digital-to-analogue converter (DACs) is necessary for each input to convert the 8-bits-code into a single voltage. When the ANN is employed to recognize other types of

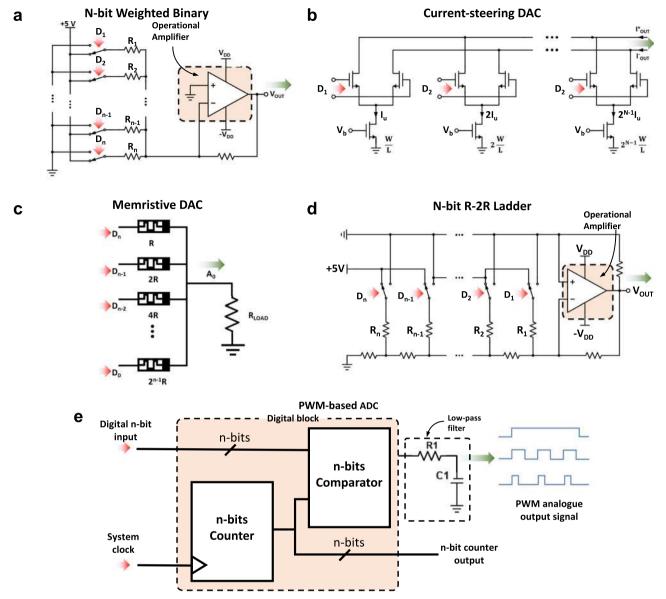

Fig. 5 | Schematic diagrams of DAC circuits conventionally used in the literature to bias the rows of the memristive crossbar. a N-bit weighted Binary, b Current-steering DAC, c Memristive-DAC d N-bit R-2R DAC and e Pulse Width Modulation (PWM)-based DAC.

images codified with a different format (e.g., 24-bit), DACs of different resolution are needed. The format in which the images are presented depends on the ultimate application of the network, i.e., ANNs for plate number identification may work well with black/white (i.e., 1-bit) images, and ANNs for object identification may need to consider 24 bits (16.7 million) colours. Examples of DACs often employed in memristive ANNs are displayed in Fig. 5: N-bit weighted Binary (Fig. 5a), Current-steering DAC Fig. 5b, Memristive-DAC (Fig. 5c), N-bit R-2R DAC (Fig. 5d) and Pulse Width Modulation (PWM)-based DAC (Fig. 5e).

Deciding the resolution of the DACs at the input of each row of the crossbar is a critical factor affecting power consumption, area, and output impedance of the ANN –lowering impedance is important to realize large crossbars. Conventional high-resolution DACs with a low output impedance comprise a DAC core with an operational amplifier (in a buffer configuration) as output stage in order to lower the output resistance. As such, the power dissipation of the DAC can be divided into the switching/leakage power of the digital DAC core and the static/dynamic power of the operational amplifier. On one hand, the power dissipation of the digital DAC core can be estimated as  $P_D = f_D C_D V^2 + P_{leakage}$ , where  $f_D$  is the output frequency,  $C_D$  is the parasitic

capacitance, V is the supply voltage, and  $P_{\rm leakage}$  is the leakage power that depends on the technology node, and for a 65 nm technology with a 1 V power supply is of several pico-Watts in an inverter. On the other hand, the power dissipation of the analogue block can be estimated by assuming a class-AB follower stage, with an efficiency of 50%. In this scenario the static power of this block equals its dynamic power and the addition of them can be computed as  $P_{\rm A}$ = $nV/R^2$ , where n is the number of memristors to drive and R is their minimum resistance. Below frequencies of roughly 100 MHz,  $P_{\rm A}$  is dominant, whereas above this threshold, the dissipated power during the switching makes  $P_{\rm D}$  bigger than  $P_{\rm A}$ .

Regarding the silicon area required for the DACs, this is mainly defined by the DAC resolution, which in turn is limited by device noise element matching. For DAC relying in resistors, the major noise source is from the CMOS operational amplifier in the output stage<sup>95</sup>, and it can be minimized using larger transistors (both in width and length) for the differential input pair. Similarly, to maximize the matching between the reference resistors, wider devices are encouraged, ultimately contributing to the increase in the silicon area required per DAC.

To minimize silicon area and power consumption, the lower the DAC resolution the better. As a result, apart from amplitude-based encoding for crossbar inputs, time-encoding schemes are also considered 6. For instance, in pulse-width modulation (PWM) schemes, inputs are codified in different pulse widths (0 s,  $T_{READ}/256$  s,  $2 \cdot T_{READ}/256$ 256 s, etc. until  $T_{READ}$ ). This allows overcoming device non-linearity but suffers from low throughput<sup>57</sup>. Alternatively, in the so-called bit-serial encoding<sup>97</sup> approaches, high-resolution crossbar inputs are presented as a stream of voltage pulses with constant amplitude and width<sup>48,56</sup>. For example, to represent 16-bit crossbar inputs, *m*-bit voltage signals are streamed to the crossbar row over 16/m time cycles<sup>98</sup>. After VMM calculation, the partial products (the outputs of each time step) are accumulated together to form the final output value. Also, many papers<sup>55,60,99,100</sup>, have explored the case of ANNs with binarized inputs, as they employ the simplest DACs (1-bit). In the case of the 1-bit input stream, DACs can also be replaced by inverters followed by an output amplifier to allow the inverter to drive all the devices connected to it98. In addition, the computation with time-encoded inputs is less affected by the noise variations, which mostly affect the amplitude of the input signals rather than the pulse width. However, the disadvantage of timeencoding schemes is the reduction of computation speed and hardware overhead required for partial sums computation%.

An alternative to keep a high throughput and still employ a low-resolution DAC is using approximate computing <sup>101</sup>. When using low-resolution DACs (1-, 2- or 3-bit) there is a higher chance of multiple inputs requiring the same driving voltage, which allows sharing DACs among several lines, and thereby saving both power and area. However, one has to keep in mind that the output resistance of the DAC limits the number wordlines that can be biased. Also, this approach requires the use of analogue multiplexers (block 11) in between the input driving circuits and the memristor crossbar which leads to additional control circuit overhead. The problem of using low-resolution DACs at the input of the crossbar is a loss in the accuracy of the VMM operation. Hence, there is an inherent trade-off between all these variables. The accuracy loss can also be reduced by exploiting software-based training techniques for quantized neural networks.

#### VMM core (Block 5)

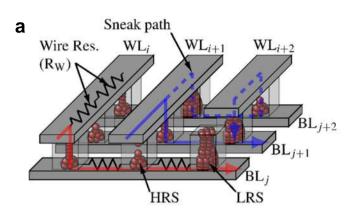

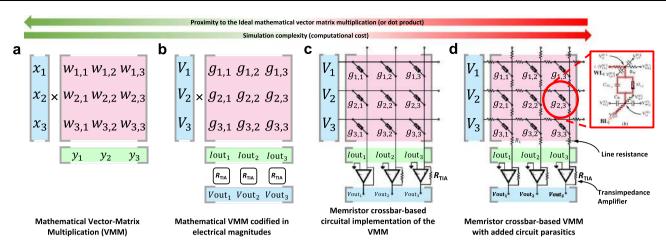

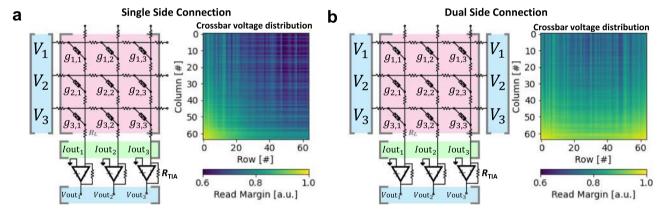

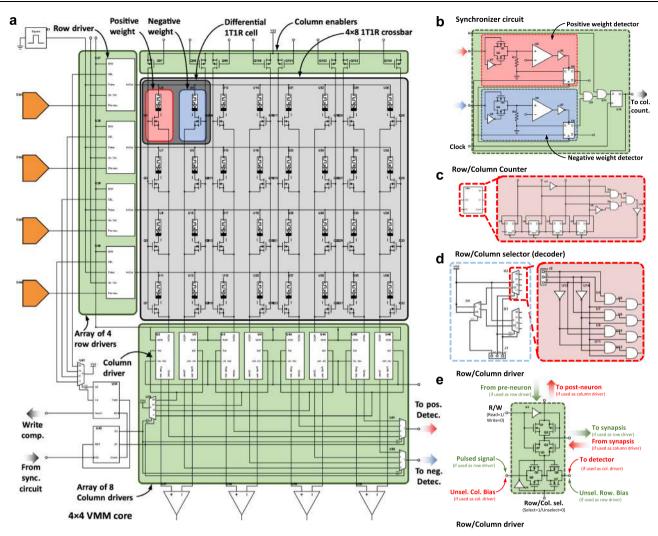

The voltages generated by each DAC (which represent the colour of each pixel of the rescaled  $n^2 \times 1$  image) are applied at the inputs (rows) of the  $n^2 \times m$  crossbar array of memristors. The conductance of each memristor within the crossbar describes the synaptic connection between each input neuron (ith) and each output neuron (jth). This scheme is used in various papers<sup>54,102</sup>. However, some others consider also a bias term added to the weighted sum fed to the neuron<sup>57</sup>. This can be done digitally and off-chip, or in the analogue domain. If done analogue, an additionally row in the crossbar is needed, thereby requiring a crossbar of  $(n^2+1) \times m$ . This operation produces a row vector of size 1 × m (see Eq. 1). In a conventional Von Neumann computing system, VMM is performed by doing each sub-operation (multiplications and sums) sequentially, which is time consuming; moreover the calculation time increases quadratically with the dimensionality of the input arrays<sup>103</sup>, or in the case of using the socalled Big-O notation, the VMM algorithm has a time complexity of  $\sim O(n^2)$ . Memristor crossbars (such as the one shown in Fig. 6a) allow performing VMM much more easily and faster because all the suboperations are carried out in parallel. In the crossbar, the brightness (colour) of each pixel in each image is codified in terms of analogue voltages and applied to the input rows (also called wordlines and connected to the memristor's top electrodes), while the output columns (also called bitlines and connected to the memristor's bottom electrodes) are grounded through a transimpedance amplifier (see Fig. 6b for an idealized representation). Then, the VMM is performed in an analogue fashion, as the current flowing through each memristor will be given by the voltage applied to the line and the conductance of each memristor  $(I_{ij} = g_{ij} \cdot V_i)$ . Note that in a pair  $\{i,j\}$  i stands for the crossbar row, and j for the crossbar column. Then, the currents flowing through the memristors connected to a given bitline are summed and sensed to form the output vector. Let us consider the following notation to better explain this idea:

$$\begin{bmatrix} V_{1} & V_{2} & \cdots & V_{n^{2}} \end{bmatrix} \times \begin{bmatrix} g_{1,1} & g_{1,2} & \cdots & g_{1,m} \\ g_{2,1} & g_{2,2} & \cdots & g_{2,m} \\ \vdots & \vdots & \ddots & \vdots \\ g_{n^{2},1} & g_{n^{2},2} & \cdots & g_{n^{2},m} \end{bmatrix}$$

$$= \begin{bmatrix} \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,1} & \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,2} & \cdots & \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,m} \end{bmatrix}$$

$$(1)$$

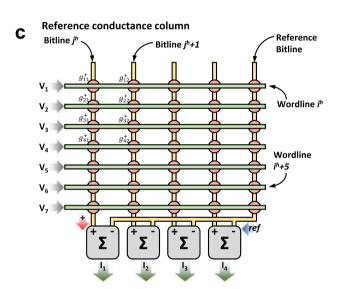

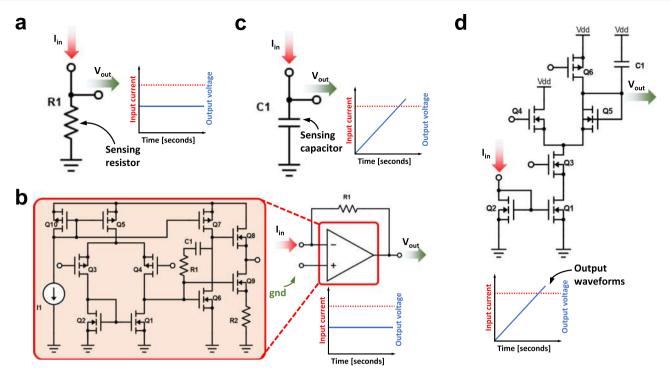

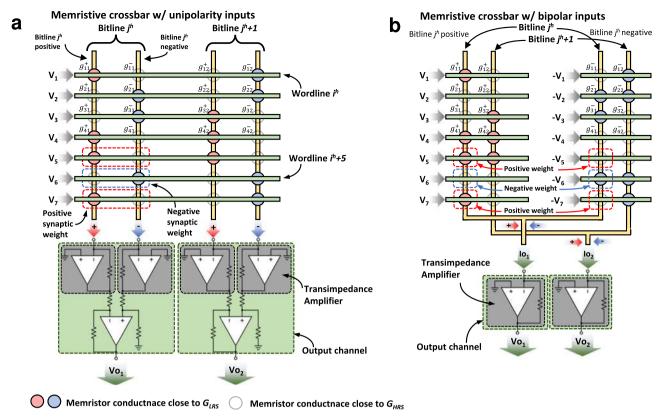

For the classification of the MNIST images with a  $n \times n$  pixel resolution with an ANN, multiple VMM operations are required, in which the matrix of conductances  $g_{ij}$  in Eq. 1 is defined based on the matrix  $\mathbf{W_M}$  of synaptic weights, which has a size of  $n^2 \times 10$ , and all the numbers that form it are real numbers ( $\mathbf{W_M} \in \mathbb{R}^{n^2 \times 10}$ ) with both positive and negative values being possible —the way in which  $\mathbf{W_M}$  is calculated is described in detail in section ANN training and synaptic weight update (Blocks 2, 11-15): Learning algorithm. As the negative values cannot be represented directly with memristors, some strategies have been adopted. Reference 104 added an extra column in the crossbar (named reference column, see blue arrow in Fig. 6c) with all its memristors set to  $0.5 \cdot G_{LRS}$ , so totalling  $n^2 \times (m+1)$  memristors in the crossbar. Then, the total current at the  $\{j\}$  output of the crossbar is obtained by subtracting the current generated by the reference column  $\{ref\}$  to the current generated from a  $\{j\}$  column (see Fig. 6c). This concept is mathematically represented in Eq. 2.

$$\begin{split} & \left[ \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,1} \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,2} \cdots \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,m} \right] \rightarrow \\ & \left[ \sum_{i=1}^{n^{2}} V_{i} \cdot (g'_{i,1} - g_{\text{ref}}) \sum_{i=1}^{n^{2}} V_{i} \cdot (g'_{i,2} - g_{\text{ref}}) \cdots \sum_{i=1}^{n^{2}} V_{i} \cdot (g'_{i,m} - g_{\text{ref}}) \right] \end{split} \tag{2}$$

where  $g_{\rm ref}$  stands for the 0.5· $G_{\rm LRS}$  conductances of the reference column and  $g'_{i,j}$  is calculated in such a way that devices with a conductance above 0.5· $G_{\rm LRS}$  produce positive synaptic weights, and those with a conductance below 0.5· $G_{\rm LRS}$  produce negative synaptic weights<sup>104</sup>. This strategy has two disadvantages: on one hand, one can only employ half of the states exhibited by the memristor for the positive weights and the other half for the negative weights, thus reducing the range between the maximum and minimum weight. On the other hand, routing the reference column to the rest of the crossbar columns to make the corresponding subtraction operation, is not trivial. Another strategy is to use two memristors per synaptic weight, resulting in two crossbars of  $n^2 \times 10$  ( $20n^2$  synapses)<sup>105,106</sup>. Within this approach, Eq. 2 could be re-written as

$$\begin{split} & \left[ \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,1} \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,2} \cdots \sum_{i=1}^{n^{2}} V_{i} \cdot g_{i,m} \right] \\ & \rightarrow \left[ \sum_{i=1}^{n^{2}} V_{i} \cdot (g^{+}_{i,1} - g^{-}_{i,1}) \sum_{i=1}^{n^{2}} V_{i} \cdot (g^{+}_{i,2} - g^{-}_{i,2}) \cdots \sum_{i=1}^{n^{2}} V_{i} \cdot (g^{+}_{i,m} - g^{-}_{i,m}) \right] \end{split}$$

Where the positive and negative conductances are codified by a pair of two adjacent memristors  $(g^+{}_{i,j})$  and  $g^-{}_{i,j})$ , each of them set to a positive value of conductance. This representation method, shown in Fig. 6d, has been chosen in this study because it doubles the range of

**Fig. 6** | **Memristor crossbar structure and electrical connection diagram for signed weights representation. a** Sketch of the crossbar array structure. Red and blue arrows exemplify the electron flow through the memristors connecting the top (Word lines -WL-) and bottom lines (Bit lines -BL-). Different memristor resistance states are schematically represented (High Resistance State -HRS- to Low Resistance State -LRS-). The dashed blue line depicts the so-called sneak path problem. The parasitic wire resistance is indicated for WL<sub>i</sub> and BL<sub>i</sub>. Reproduced

with permission under CCBY 4.0 license from ref. 253. **b** Equivalent circuit representation of the CPA sketched in **a**, showing the input voltages, output currents and TIA blocks that translates the output CPA current to a vector of analogue voltages. In this case the circuit was simplified by ignoring the line resistances. Finally, two different realizations of the memristive-based ANN synaptic layer are shown in  $\bf c$  – unbalanced – and  $\bf d$  – balanced –.

conductance levels of the crossbar, making it less susceptible to noise and variability  $^{104}$ .

To calculate the required conductance value for each of the memristors in the pair, we begin by splitting  $W_M$  into two matrices  $W_M^+$  and  $W_M^-$  as:

$$w_{M_{i,j}}^{+} \begin{cases} w_{M_{i,j}}, & w_{M_{i,j}} > 0 \\ 0, & w_{M_{i,j}} \le 0 \end{cases}$$

$$w_{M_{i,j}}^{-} \begin{cases} 0, & w_{M_{i,j}} \ge 0 \\ -w_{M_{i,j}}, & w_{M_{i,j}} < 0 \end{cases}$$

$$(4)$$

each of them containing only positive weights, so that  $\mathbf{W}_{\mathbf{M}} = \mathbf{W}_{\mathbf{M}}^{+} - \mathbf{W}_{\mathbf{M}}^{-}$ . The matrix in the left side  $(\mathbf{W}_{\mathbf{M}},$  containing both positive and negative values) can be represented as a difference between the two matrices in the right side  $(\mathbf{W}_{\mathbf{M}}^{+})$  and  $\mathbf{W}_{\mathbf{M}}^{-}$ , both containing only positive numbers). Thereby, by applying Eq. 4, we obtain

$\mathbf{W}_{\mathbf{M}}^{+}$  by replacing all the negative elements from  $\mathbf{W}_{\mathbf{M}}$  by 0, while  $\mathbf{W}_{\mathbf{M}}^{-}$  was obtained by first multiplying matrix  $\mathbf{W}_{\mathbf{M}}$  by -1 and then replacing al the negative values by 0.

In the next step, the conductance matrices  $\mathbf{G}_{\mathbf{M}}^{+}$  and  $\mathbf{G}_{\mathbf{M}}^{-}$  (Equation 5) to be mapped into the crossbars are calculated by employing a linear transformation,  $^{107,108}$ :

$$G_{M}^{+} = a \cdot W_{M}^{+} + b = \frac{G_{\max} - G_{\min}}{\max\{W_{M}\} - \min\{W_{M}\}} W_{M}^{+} + \left[ G_{\max} - \frac{(G_{\max} - G_{\min}) \max\{W_{M}\}}{\max\{W_{M}\} - \min\{W_{M}\}} \right]$$

$$G_{M}^{-} = a \cdot W_{M}^{-} + b = \frac{G_{\max} - G_{\min}}{\max\{W_{M}\} - \min\{W_{M}\}} W_{M}^{-} + \left[ G_{\max} - \frac{(G_{\max} - G_{\min}) \max\{W_{M}\}}{\max\{W_{M}\} - \min\{W_{M}\}} \right]$$

(5)

here  $G_{\min}$  and  $G_{\max}$  are the minimal and maximal conductance values of the memristors in the crossbar, and  $\max\{\mathbf{W_M}\}$  and  $\min\{\mathbf{W_M}\}$  are the maximum and minimum values in  $\mathbf{W_M}$ . At this point, it is critical to note that this mapping strategy presents the synaptic weights from  $\mathbf{W_M}$  to a continuum of conductance values in the range  $[G_{\min}, G_{\max}]$ .

However, it has been widely reported 109-111, that the more states one memristor has, the more difficult to identify them, due to the inherent variability. Moreover, depending on the material and fabrication methods, some memristor devices can have only a limited number of stable conductance states. To deal with these non idealities, advanced mapping techniques have been proposed in the literature and they are summarized in Supplementary Note 1 and Supplementary Note 2, the latter focused on mitigating the heat-induced drift of synaptic weights. Thereby, when considering a device with a number x of states, each position of the resulting conductance matrices should have only x possible values. In order to exploit the entire dynamic range of the memristors (which would make easier to identify each conductance value), we consider  $G_{\text{max}} = G_{\text{LRS}}$  and  $G_{\text{min}} = G_{\text{HRS}}$ , being  $G_{\text{LRS}}$  and  $G_{\text{HRS}}$ the conductance of the most and least conductive states (respectively). In this way, the synaptic weights in the  $\mathbf{W}_{\mathbf{M}}^+$  and  $\mathbf{W}_{\mathbf{M}}^-$  matrices are converted to conductance values within the range  $[G_{HRS}, G_{LRS}]$ . The following example illustrates the procedure to convert the  $\mathbf{W}_{\mathbf{M}}$  matrix returned by the MATLAB training phase (i.e., a matrix of real values in the range [-5, 5]) into two crossbar arrays of memristors (considering that each memristor can have 6 linearly distributed resistive states at  $G_{HRS}$ ,  $0.2 \cdot G_{LRS}$ ,  $0.4 \cdot G_{LRS}$ ,  $0.6 \cdot G_{LRS}$ ,  $0.8 \cdot G_{LRS}$  and  $G_{LRS}$ ):

First, the ex-situ training produces a matrix of  $n^2 \times m$  synaptic weights:

$$\mathbf{W_{M}} = \begin{bmatrix} 1.1 & 4.7 & -3.9 & \dots & 4.9 \\ 1.8 & -3 & -1.2 & \dots & 0.2 \\ 4.6 & -4.9 & 0.3 & \dots & 1.3 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ -0.9 & 2.7 & -2.2 & \dots & -4.8 \end{bmatrix}$$

(6)

Second, the synaptic weights are represented as the difference between two matrices:

$$\mathbf{W}_{\mathbf{M}}^{+} - \mathbf{W}_{\mathbf{M}}^{-} = \begin{bmatrix} 1.1 & 4.7 & 0 & \dots & 4.9 \\ 1.8 & 0 & 0 & \dots & 0.2 \\ 4.6 & 0 & 0.3 & \dots & 1.3 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 2.7 & 0 & \dots & 0 \end{bmatrix} - \begin{bmatrix} 0 & 0 & 3.9 & \dots & 0 \\ 0 & 3 & 1.2 & \dots & 0 \\ 0 & 4.9 & 0 & \dots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0.9 & 0 & 2.2 & \dots & 4.8 \end{bmatrix}$$

(7)

Third, the weights are rounded to the closest state among the  $\boldsymbol{x}$  available states:

$$\mathbf{W_{Mq}^{+}} - \mathbf{W_{Mq}^{-}} = \begin{bmatrix} 1 & 5 & 0 & \dots & 5 \\ 2 & 0 & 0 & \dots & 0 \\ 5 & 0 & 0 & \dots & 1 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 3 & 0 & \dots & 0 \end{bmatrix} - \begin{bmatrix} 0 & 0 & 4 & \dots & 0 \\ 0 & 3 & 1 & \dots & 0 \\ 0 & 5 & 0 & \dots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 1 & 0 & 2 & \dots & 5 \end{bmatrix}$$

(8)

Finally, the quantized weights are mapped to a conductance value:

$$\mathbf{G}_{\mathbf{M}}^{+} - \mathbf{G}_{\mathbf{M}}^{-} = \begin{bmatrix} \frac{c_{LIS}}{5} & G_{LRS} & G_{HRS} & \cdots & G_{LRS} \\ \frac{2G_{LRS}}{5} & G_{HRS} & G_{HRS} & \cdots & G_{HRS} \\ G_{LRS} & G_{HRS} & G_{HRS} & \cdots & \frac{G_{LRS}}{5} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ G_{HRS} & \frac{3G_{LRS}}{5} & G_{HRS} & \cdots & G_{HRS} \end{bmatrix} - \begin{bmatrix} G_{HRS} & G_{LRS} & \frac{4G_{LRS}}{5} & \cdots & G_{LRS} \\ G_{HRS} & \frac{3G_{LRS}}{5} & \frac{G_{LRS}}{5} & \cdots & G_{HRS} \\ G_{HRS} & G_{LRS} & G_{LRS} & \cdots & G_{HRS} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ G_{LRS} & G_{HRS} & \frac{2G_{LIS}}{5} & \cdots & G_{LRS} \end{bmatrix}$$

$$(9)$$

The output value caused by a negative synaptic weight is achieved by subtracting the current flowing through the memristors connected

to bitline i in  $G_{\mathbf{M}}^{-}$  matrix from that in the corresponding bitline i in  $G_{\mathbf{M}}^{+}$  matrix.

#### Sensing electronics (Block 6)

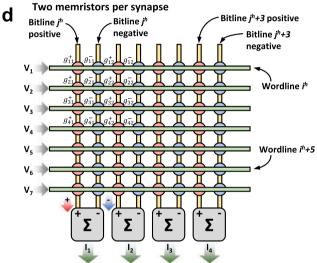

Once the input voltages are applied to the inputs (rows) of the crossbar, currents at the outputs (columns) are almost instantaneously generated. which need to be sensed. There are three widely used sensing modes for the output voltages<sup>112</sup>. The simplest approach is the use of a sensing resistor (Fig. 7a). However, grounding the bitlines through a resistor might alter the potential applied to the bitline, which will no longer be 0 volts, adding variability and thus altering the read over the sensing resistor<sup>100,112</sup>. To sense low currents without this problem, one option is to use trans-impedance amplifiers (TIA, see Fig. 7b). In this case, the crossbar bitlines are grounded through a TIA implemented with an operational amplifier or an operational transconductance amplifier which ensures the bitline potential to remain at 0 V. Although very popular<sup>102,113-116</sup>, this approach might be limited for the case of the smallest technology nodes implementations as the gain and bandwidth of the amplifiers are limited by the intrinsic transistor gain<sup>95,117</sup>. An alternative is to replace the TIA block by a charge-based accumulation circuit. This strategy was used to cope with pulse width modulation encoding that excludes the utilization of one TIA. Note that the same approach could be used along with other encoding techniques such as digitization of inputs and pulse amplitude modulation. In its most basic implementation, it is very similar to the use of a sensing resistor but replacing the resistor by a capacitor (see Fig. 7c). The capacitor then develops a voltage which is proportional to the integrated current flowing through it. As such, this method adds the time-dimension to the process of sensing the outputs: the current must be integrated over a constant and well-defined period of time to generate an output voltage. Note that in many cases, to reduce the current to be integrated (and thus the size of the integration capacitors), current divider circuits<sup>57</sup> or differential pair integrators<sup>118</sup> are considered (see Fig. 7d).

Finally, note that the design choice of the sensing circuit will depend on the input signals to the memristor crossbar, as shown in Fig. 8. Assuming that the input signals of both positive and negative cells are of the same polarity, an independent sensing/transducing circuit is required for both the positive and negative bitline. Then a subtractor circuit (implemented for instance with an operational amplifier, as shown in Fig. 8a) generates an output voltage proportional to the current difference. On the contrary, when it is possible to apply input signals of different polarity to the  $\mathbf{G}_{\mathbf{M}}^-$  and  $\mathbf{G}_{\mathbf{M}}^+$  matrix, the sensing electronics can be simplified, as by connecting the i bitlines from the  $\mathbf{G}_{\mathbf{M}}^-$  and  $\mathbf{G}_{\mathbf{M}}^+$  directly performs the substraction in terms of currents, and thereby only one sensing amplifier is needed (as shown by the single transimpedance amplifier in Fig. 8b).

#### **Activation function (Block 7)**

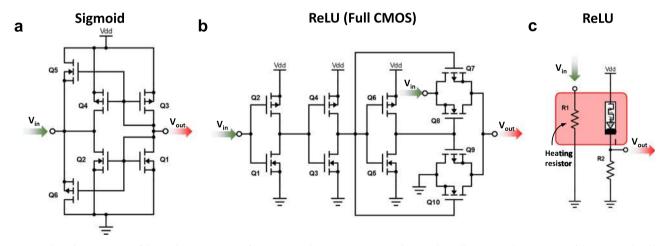

Ideally, the output current of each bitline (column) pair in a crossbar-based implementation of a VMM is a linear-weighted sum of all the wordlines (rows) connected to such column. Since a combination of linear functions results in a new linear function. complex nonlinear relationships could not be replicated by an ANN regardless of the number of the linear neural layers considered. This problem can be overcome by introducing a non-linearity transformation on the weighted sum output by each column. This is done by the so-called neuron activation functions, and the most common are: Sigmoid (also called Logistic)<sup>119,120</sup>, Hyperbolic Tangent<sup>120</sup> and Rectified Linear Unit (ReLU)<sup>120,121</sup>. Also, for the particular case of pattern classification tasks, the output values of the VMM performed by the last neural layer have the added requirement of being mapped to the [-1, 1] or [0, 1] range as they indicate the probability of the input to belong to each class. To this end, the gap difference between the value of the most active output (column) and the rest needs to be compressed and the differences among the less active

**Fig. 7** | **Circuit schematics for the sensing electronics placed in at the output of every column of the memristive crossbar.** In all cases, the goal is to translate a current signal into a voltage signal. **a** The sensing resistor is the simplest case, as it translates current into voltage directly by the Ohm's law. **b** The use of a TIA allows to connect the crossbar columns to 0 volts and operate with lower output currents. As well as in the resistor-based approach, the current voltage conversion is linear when operating the TIA within its linear range and the output voltage signal is immediately available as soon as the output of the TIA settles. **c** For currents

below the nano-ampere regime, charge integration is the most suitable option for current-voltage conversion. This can be achieved by using a capacitor. As such, the measurement is not instantaneous as a constant, controllable integration time is required before the measurement. **d** To minimize the area requirements of the integration capacitor, the use of a current divider allows to further reduce the current and, with it, the size of the required capacitor. The tradeoff in this case is with precision (mainly due to transistor mismatch) and output voltage dynamic range.