**Doctoral Dissertation**

Doctoral Program in Electrical, Electronics and Communications Engineering (34<sup>th</sup>cycle)

# Memristor-based hardware accelerators: from device modeling to AI applications

## Francesco Marrone

\*\*\*\*\*

Supervisor: Prof. Fernando Corinto

**Doctoral Examination Committee:**

Dr. Alon Ascoli, Referee, Technische Universität Dresden Prof. Mauro Di Marco, Referee, Università degli Studi di Siena Prof. Michele Bonnin, Politecnico di Torino Prof. Rodrigo Picos Gayá, Universitat de les Illes Balears Prof. Sung-Mo "Steve" Kang, University of California Santa Cruz

> Politecnico di Torino 2022

## Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Francesco Marrone 2022

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

## Acknowledgements

Exactly ten years ago I entered Politecnico di Torino as a freshman studying Electronics Engineering. Now, ten years later, at the time of defending the four and half years of my research work which are condensed in this manuscript, I cannot be anything but grateful to this institution which has been like a second home to me for quite a long time. I have met lots of amazing people in this school and would like to thank as many as I can fit on these acknowledgements pages.

I consider myself extremely lucky to have had Prof. Fernando Corinto as the advisor of my PhD. He brought me into the Neuromorphic Computing research community during my Master's thesis and has been since then not only my scientific point of reference but also an inspiration for his human kindness. He has always supported me with a mix of good words, freedom and concrete help during all the many crisis along the PhD journey. I will never thank him enough for the polishing work that he has done on my professional attitude by smoothing the perfectionism and fueling the curiosity.

It is very difficult for me to imagine this adventure without Dr. Gianluca Zoppo. He has been not only my PhD buddy but also a true friend. I do thank him from my hearth for his invaluable support through difficult times and for pushing me to do my best while stuck in research discouragement. He will always be a model to me for his work ethic and, with deep gratitude, I wish him good luck for his future career.

Last but not least, I want to thank Dr. Jacopo Secco. I will never forget all the coffee breaks with good conversations we have had during the years. Thanks to him I have had the opportunity to enrich my professional experience with corporate R&D project where to apply the latest advancements in Machine Learning. I have learnt a lot from him and consider him a model for his spirit of enterprise and ambition.

A big thanks is also due to Dr. Abu Sebastian and his team, in particular to Benedikt Kersting, for the opportunity of studying and experiment with their Phase Change Memory technology at IBM Research Zurich. With them I also need to thank Prof. Leon O. Chua for coming up with the idea for this research project and for all the stimulating conversations we had while he was visiting professor in our research group.

A special thanks goes to the group of Prof. R. Stanley Williams at Texas A&M for letting me join their research collaboration with my group during the outbreak of COVID-19 in 2020. I consider the work done during that year the most scientifically productive of my PhD journey. I have learnt a lot from them, in particular from the discussions I had with Anil Korkmaz, and the feedbacks given by Prof. Williams and Prof. Samuel Palermo have taught me a lot on the way to impact as a researcher.

Thanks also to Dr. Alon Ascoli and Prof. Mauro Di Marco for reading and reviewing my thesis. I think your suggestions have substantially improved this manuscript.

A big greeting goes to Dr. Andrea Napolitano, Dr. Riccardo Gervasi and Ada Palamà. I think we have had some of the best lunch breaks together. I have to say that it was a pleasure to meet them in my doctoral years.

A big thanks goes to my family which has always supported me and provided unconditional love. A huge thanks also goes to Gaia who has supported, encouraged, and helped me during this tough year.

I would also need to thank many close friends which have been fundamental during these years and in my life in general but they are probably too many so I ask in advance their pardon if they are not explicitly named here...you all have impacted who I am now.

#### Summary

In recent times, the interest in artificial intelligence algorithms has skyrocketed well out of academia marking a substantial shift in most, if not all, the industrial sectors. This revolution started in the early 2010s and was made possible by the combined availability of very powerful parallel processing units (e.g. GPUs) and more and more abundant "big data". Although the GPU has served well as platform to kick-start this revolution, currently this conventional digital hardware accelerator struggles to satisfy the increasingly high requirements of machine learning algorithms within a reasonable power consumption range. Most of the energy inefficiency which characterizes conventional digital hardware accelerators (e.g. GPU, TPU, FPGA etc) is to blame on the traditional von Neumann architecture they implement which involves data being sent back and forth between memory and the processor. In this context, neuromorphic computing has emerged as an alternative to contemporary processing units' architectural design choices which may rise to the challenges posed by modern AI training and inference tasks. Neuromorphic computing takes inspiration from the biology of the animal brain by putting the storage of information and its processing in very close spatial proximity if not encoded and performed by the same processing element. It is this the case of memristive technologies which have attracted the interest of lots of researchers and companies as good candidates to implement the synaptic function in neuromorphic hardware accelerators. The overall goal of this doctoral thesis is the investigation of memristive based computing architecture exploiting an holistic approach ranging from the modeling of memristive devices to the mapping of advanced machine learning algorithm on crossbar arrays. The first part of the thesis is devoted to memristive technologies modeling techniques while its second part deals with the design and study of meristor-based architectures for machine learning tasks. In particular the thesis contains novel results on the use of DRMs for Phase Change Memory devices, the study of Spiking Neural Networks and the design of advanced memristive crossbar based accelerators for linear algebra problems (Pagerank).

## Contents

| Li | st of l      | Figures |                                                       | ix  |

|----|--------------|---------|-------------------------------------------------------|-----|

| Li | st of [      | Tables  |                                                       | xix |

| In | Introduction |         |                                                       | 1   |

| 1  | Mer          | nristor | Device Modeling: PCM                                  | 5   |

|    | 1.1          | Introd  | uction                                                | 5   |

|    | 1.2          | Comp    | lete second order model                               | 8   |

|    |              | 1.2.1   | Complete Ohm's Law                                    | 9   |

|    |              | 1.2.2   | Complete PCM Dynamics                                 | 10  |

|    | 1.3          | Simpli  | ified first order model derivation                    | 12  |

|    |              | 1.3.1   | Simplified Ohm's Law                                  | 13  |

|    |              | 1.3.2   | Simplified temperature dynamics                       | 14  |

|    | 1.4          | Dynar   | nic Route Maps                                        | 15  |

|    |              | 1.4.1   | Numerically computed DRMs                             | 15  |

|    |              | 1.4.2   | Experimental data acquisition details                 | 18  |

|    |              | 1.4.3   | Comparison between numerical and experimental results | 19  |

|    | 1.5          | Conclu  | usion                                                 | 21  |

| 2  | Mer          | nristor | Device Modeling: ReRAM                                | 25  |

|   | 2.1 | Introd  | luction                                           | 25 |

|---|-----|---------|---------------------------------------------------|----|

|   | 2.2 | Comp    | Plete second order model                          | 27 |

|   |     | 2.2.1   | Complete Ohm's Law                                | 27 |

|   |     | 2.2.2   | Complete ReRAM Dynamics                           | 30 |

|   | 2.3 | Simpl   | ified second order model derivation               | 31 |

|   |     | 2.3.1   | Simplified Ohm's Law                              | 32 |

|   |     | 2.3.2   | Memductance dynamics derivation                   | 34 |

|   |     | 2.3.3   | Simplified temperature dynamics                   | 35 |

|   | 2.4 | Memr    | ristor response to synaptic protocols             | 37 |

|   | 2.5 | Mode    | l robustness study                                | 39 |

|   |     | 2.5.1   | Model accuracy when changing voltages and activa- |    |

|   |     |         | tion energies                                     | 42 |

|   |     | 2.5.2   | Model sensitivity to parameters variation         |    |

|   | 2.6 | Concl   | usion                                             | 47 |

| 3 | Mer | nristor | -based Neural Networks                            | 48 |

|   | 3.1 | Introd  | luction                                           | 48 |

|   | 3.2 | Neuro   | omorphic Applications                             | 51 |

|   |     | 3.2.1   | Artificial Neural Networks                        | 52 |

|   |     | 3.2.2   | Spiking Neural Networks                           | 63 |

|   | 3.3 | Concl   | usion                                             | 77 |

| 4 | Mer | nristor | -based Linear Algebra Accelerators                | 79 |

|   | 4.1 | Introd  | luction                                           | 79 |

|   | 4.2 | Theor   | etical background                                 | 80 |

|   | 4.3 | Solvir  | ng Discrete-Time Markov Chains                    | 84 |

|   | 4.4 | Cross   | bar Implementations                               | 86 |

|   |     | _       | n Precision Analysis                              | 91 |

|    |        | 4.5.1   | Open-Loop Crossbar     | 91  |

|----|--------|---------|------------------------|-----|

|    |        | 4.5.2   | Feedback Crossbar      | 95  |

|    |        | 4.5.3   | Output Precision       | 99  |

|    | 4.6    | System  | n Accuracy Analysis    | 102 |

|    |        | 4.6.1   | Open-Loop Crossbar     | 102 |

|    |        | 4.6.2   | Feedback Crossbar      | 103 |

|    |        | 4.6.3   | Output Accuracy        | 108 |

|    | 4.7    | Case S  | Studies                | 109 |

|    |        | 4.7.1   | Mouse in a Maze        | 110 |

|    |        | 4.7.2   | The Pagerank Algorithm | 111 |

|    | 4.8    | Conclu  | usion                  | 116 |

| 5  | Con    | clusion | IS                     | 118 |

|    | 5.1    | Summ    | nary                   | 118 |

|    | 5.2    | Outloo  | ok                     | 120 |

| Re | eferer | nces    |                        | 122 |

## **List of Figures**

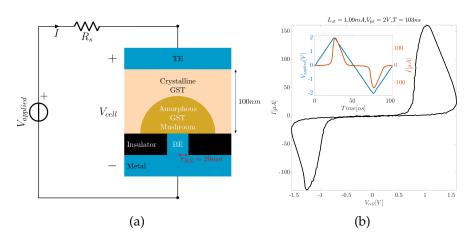

1.1 (a) Schematic representation of a mushroom-type PCM device operated with a current compliance series resistor  $R_s$ . In the RESET state, the amorphous phase blocks the bottom electrode, and the device is in a high-resistance state. The effective thickness of the amorphous region is denoted by  $u_a(t)$ .  $V_{applied}(t)$  is the externally applied input voltage, I(t) is the current flowing through the PCM device and  $V_{cell} = V_{applied} - R_s I$  is the intrinsic voltage drop on the device.(b) Measured pinched hysteresis loop for a mushroom PCM device stimulated by a 103 ns period triangular  $V_{applied}$  pulse of 2V peak voltage  $V_{pk}$ .

6

8

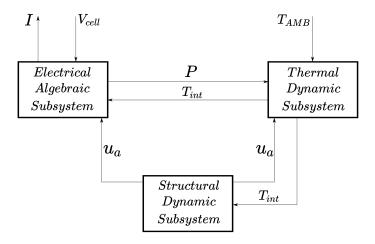

1.2 Simplified block representation of the PCM device subsystems. The system has two inputs respectively  $V_{cell}(t)$  and  $T_{AMB}$  and one output I(t).  $V_{cell}(t)$  is the voltage drop on the PCM device. I(t) is the current flowing through the device.  $T_{AMB}$  is the ambient temperature the PCM device is operated at. P(t) is the algebraic electrical power dissipated by the device and computed as the product current I(t) times voltage  $V_{cell}(t)$ .  $u_a(t)$  is the amorphous mushroom thickness and its evolution is determined by the crystallization dynamics.  $T_{int}(t)$  is the temperature at the amorphous-crystalline interface and its evolution is determined by the heat balance equation. . . . .

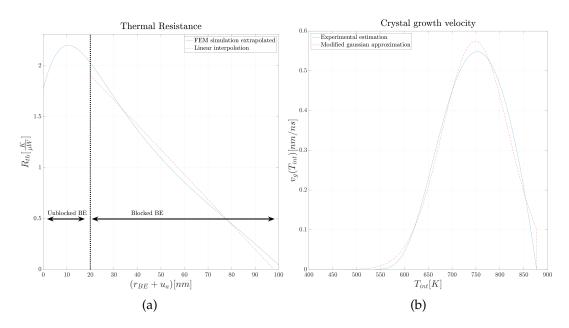

| 1.3 | (a) in continuous blue the effective thermal resistance, extrapolated from FEM simulations, as a function of the amorphous thickness $u_a(t)$ . In dashed red the linear approximation of the effective thermal resistance in the blocked BE condition. (b) in continuous blue the experimentally estimated <i>GST</i> crystal growth velocity $v_g(T_{int})$ as a function of the interface temperature $T_{int}$ . In dashed red its Gaussian approximation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

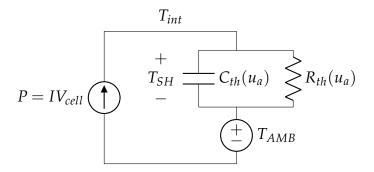

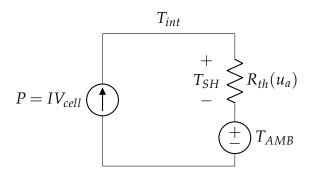

| 1.4 | First order dynamical thermal circuit that takes into account the presence of $C_{th}(u_a)$ . Its dynamics can be described through Equation (1.1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13 |

| 1.5 | For the sake of the presented model the input signals to the PCM device are considered to be at least twice longer in duration than $\tau_{th}$ , for this reason it is taken into account <b>(b)</b> described by Equation (1.7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15 |

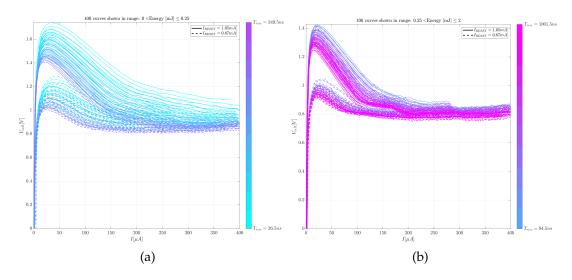

| 1.6 | DSO measured $I - V_{cell}$ characteristics of a <i>GST</i> PCM cell,<br>reset with two different reset currents $I_{RESET}$ , driven by a<br>voltage ramp <i>V</i> supplied by an Arbitrary Waveform Generator<br>through a series resistor $R_S \approx 5.7k\Omega$ . $V_{cell}$ responses computed<br>as $V_{cell} = V - R_S I$ . Rise times $T_{rise}$ spanning in the range<br>[26.5, 1001.5] <i>ns</i> and supplied voltages <i>V</i> in the range [1,4] <i>V</i> .<br>Energy estimated as the trapezoidal approximation of the<br>integral of the dissipated power $P = V_{cell}I$ along the curve<br>from $(I, V_{cell}) = (0,0)$ up to the threshold switching peak. In (a)<br>the $I, V_{cell}$ characteristics for the PCM cell when not sufficiently<br>heated. The final $V_{cell}$ plateau in (a) varies substantially. In (b)<br>the $I - V_{cell}$ characteristics for the PCM cell when sufficiently<br>heated. The final $V_{cell}$ plateau in (b) results to be narrowly |    |

|     | centered around $V_{cell,ON} \approx 0.8V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

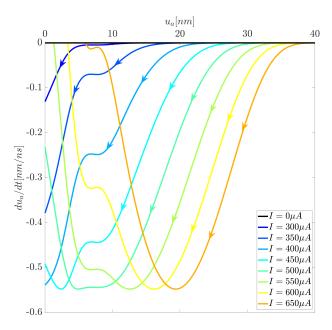

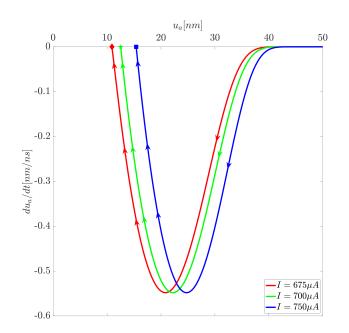

1.7 (a) [Global (i, v) curves] DSO measured  $I - V_{cell}$  characteristics of a *GST* PCM cell, reset with different reset currents *I<sub>RESET</sub>*, showing the same plateau  $V_{cell}$  value for  $I \ge I_{th} \ge 100 \mu A$ . Driving voltage  $V_{applied}$  supplied by an by an Arbitrary Waveform Generator through a series resistor  $R_S \approx 5.7 k\Omega$ .  $V_{cell}$  responses computed as  $V_{cell} = V - R_S I$ . Ramp rise time  $T_{rise} = 3\mu s$ . (b) [READ operation (i, v) curves] SMU measured low-field  $I - V_{cell}$  characteristics of the same PCM cell, reset with the same currents *I<sub>RESET</sub>* as those on the main axes, showing an almost ideal linear behavior for very low current/voltage value. (c) [WRITE set operation (i, v) curves] Zoom-in of the write region  $I - V_{cell}$  characteristics, it is noticeable how  $V_{cell}$  is narrowly concentrated around 0.8V.(d) [Global model] Global model of a PCM device as a nonlinear time-variant dynamical system (e) [READ operation model] READ domain model of a PCM device as a state-dependent linear resistor (f) [WRITE operation model] WRITE domain model of a PCM device as 17 DRM computed, for a fully switched PCM Amorphous Mush-1.8 room cell in the blocked-BE condition, by means of the proposed write model parameterized on various levels of injected 18 current I. . . . . . . . . 1.9 Three dynamic route maps parameterized on different SET current values. Each route, when travelled, leads to a distinct nonzero equilibrium of the first order dynamic state variable  $u_a$ . 21

23

24

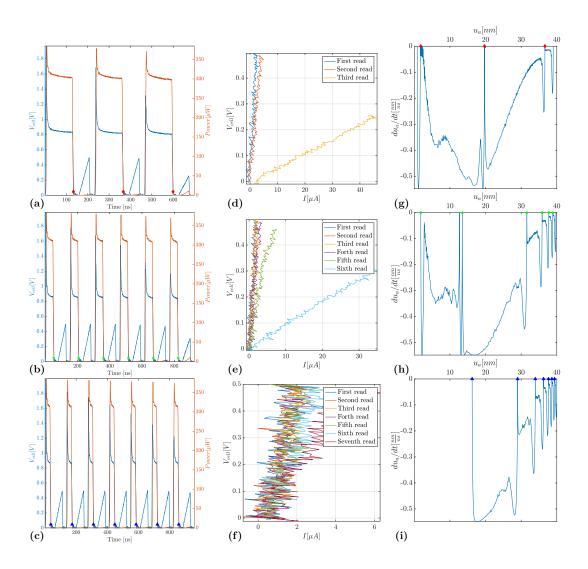

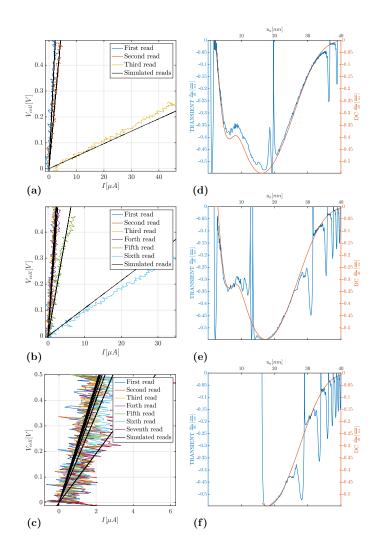

- 1.10 (Left Column) Collection of experimentally measured cell voltage drops  $V_{cell}$  and the corresponding absorbed electrical *Power* for varying write pulse duration *W*. Each square high–current write pulse is interleaved with a below threshold triangular read pulse. (a) Three W = 121ns duration pulses. (b) Six W = 42ns duration pulses. (c) Seven W = 25ns duration pulses. (b) Six W = 42ns duration pulses. (c) Seven W = 25ns duration pulses. (Center Column) Collection of measured read pulses represented on the current–voltage plane for varying pulse duration *W*. The stored memory state  $u_a$  is here directly proportional to the slope of each curve being this a measure of the resistance state. (Right Column) Dynamic Routes, for varying pulse duration *W*, computed by means of the proposed model using as input the measured power signal on the left column.

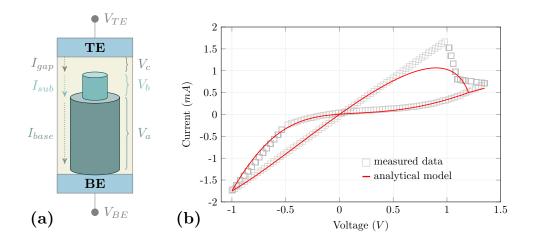

- 2.1 (a) Schematic illustration of the device showing the filament structure. (b) Typical IV loop of a  $Pd/Ta_2O_{5-x}/TaO_y/Pd$  memristor. . . 27

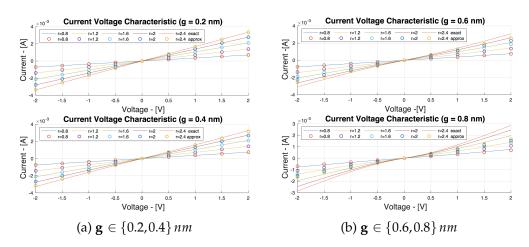

| 2.2 | Current-voltage characteristic, for different values of the radius <b>r</b> (expressed in <i>nm</i> ), and of the length gap ( $\mathbf{g} \in \{0.2, 0.4, 0.6, 0.8\}$ <i>nm</i> ). Solid lines represent the exact characteristic, obtained by numerically inverting the <b>v</b> - <b>i</b> relation (2.4); the current values derived from the approximate expression of the mem-conductance given in (2.12) are represented by circles. Taken from [1] ©2022 IEEE.                                                                                                                                                                                                                                                                                                     | 32 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

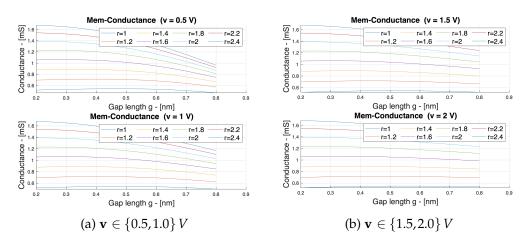

| 2.3 | Memductance, as a function of the gap length <b>g</b> , for different values of the radius <b>r</b> (expressed in <i>nm</i> ), and different voltages <b>v</b> $\in$ {0.5, 1.0, 1.5, 2.0} <i>V</i> . Taken from [1] ©2022 IEEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

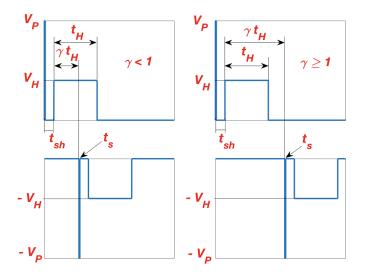

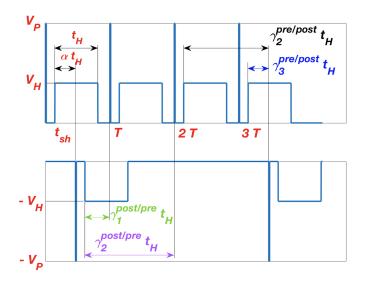

| 2.4 | Input voltage corresponding to a pre/post spike pair. Each spike is<br>represented by the sequence of a programming pulse of duration<br>$t_s$ and a heating pulse of duration $t_H$ , whereas $t_{sh}$ denotes the time<br>shift between the programming and the heating pulse. Left part:<br>the programming pulse of the postsynaptic spike occurs before the<br>end of the heating pulse of the first presynaptic pulse. Right part:<br>the programming pulse of the postsynaptic spike occurs after the<br>end of the heating pulse of the presynaptic pulse. The time interval<br>between two spikes is denoted by $\Delta_t = (\gamma - 1)t_H$ , with $\gamma$ greater<br>than 1 in the first case and less than 1 in the second one. Taken from<br>[1] ©2022 IEEE. | 38 |

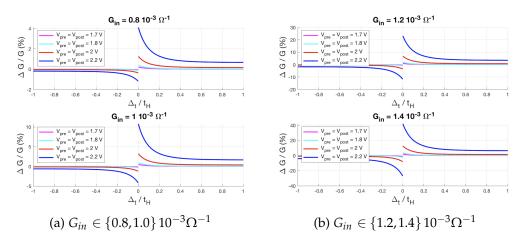

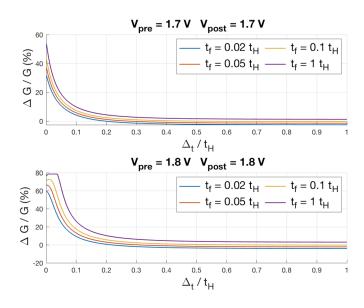

| 2.5 | STDP function corresponding to the mem-conductance variation, generated by a pre/post (post/pre) spike pair, as a function of the time interval $\frac{\Delta_t}{t_H}$ , which separates two subsequent spikes. It is assumed $V_H = 0.8$ V, $\frac{t_H}{\tau_b} = 5.4$ , and $\frac{t_s}{\tau_b} = 0.108$ ; $G_{in}$ denote the initial value of the mem-conductance. Taken from [1] ©2022 IEEE                                                                                                                                                                                                                                                                                                                                                                           | 39 |

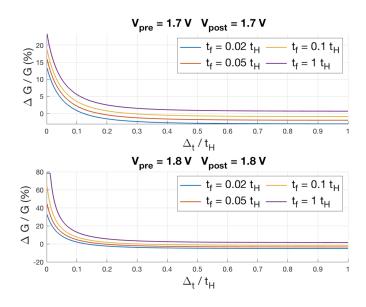

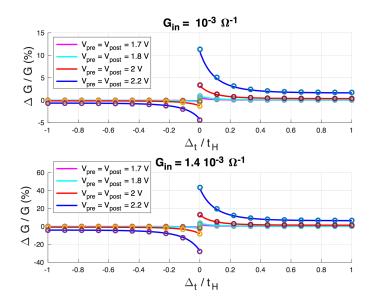

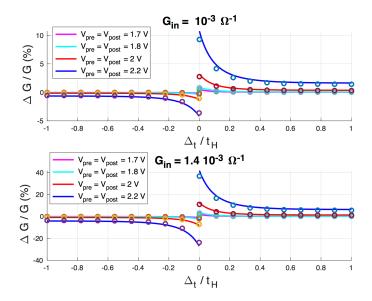

| 2.6 | Mem-conductance change versus $\frac{\Delta_t}{t_H}$ , for 30 cycles of pre-post pairs<br>at different frequencies, and different programming voltages. It is<br>assumed $V_H = 0.8$ V, $\frac{t_H}{\tau_b} = 5.4$ , and $\frac{t_s}{\tau_b} = 0.108$ ; $t_f$ denotes the time<br>interval between two pairs; the initial mem-conductance is $\hat{\mathbf{G}} = 1$ mS.<br>Taken from [1] ©2022 IEEE                                                                                                                                                                                                                                                                                                                                                                       | 40 |

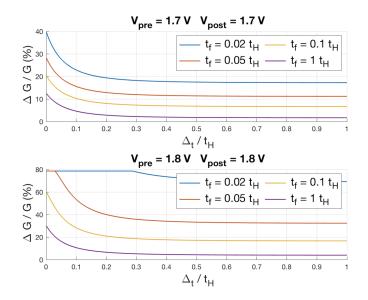

| 2.7  | Mem-conductance change versus $\frac{\Delta_t}{t_H}$ , for 30 cycles of post-pre-post triplets at different frequencies, and different programming voltages.<br>It is assumed $V_H = 0.8$ V, $\frac{t_H}{\tau_b} = 5.4$ , and $\frac{t_s}{\tau_b} = 0.108$ ; $t_f$ denotes the time interval between two triplets; the initial mem-conductance is $\hat{\mathbf{G}} = 1$ mS. Taken from [1] ©2022 IEEE.                      | 40                     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

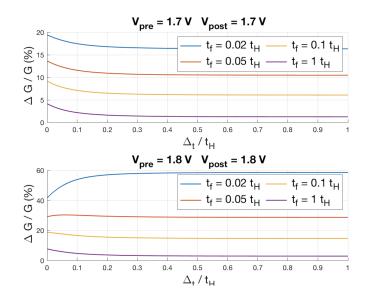

| 2.8  | Mem-conductance change versus $\frac{\Delta_t}{t_H}$ , for 30 cycles of post-pre-pre-<br>post quadruplets at different frequencies, and different program-<br>ming voltages. It is assumed $V_H = 0.8$ V, $\frac{t_H}{\tau_b} = 5.4$ , and $\frac{t_s}{\tau_b} = 0.108$ ;<br>$t_f$ denotes the time interval between two quadruplets; the initial<br>mem-conductance is $\hat{\mathbf{G}} = 1$ mS. Taken from [1] ©2022 IEEE | 41                     |

| 2.9  | Mem-conductance change versus $\frac{\Delta_t}{t_H}$ , for 30 cycles of pre-post-pre triplets at different frequencies, and different programming voltages.<br>It is assumed $V_H = 0.8$ V, $\frac{t_H}{\tau_b} = 5.4$ , and $\frac{t_s}{\tau_b} = 0.108$ ; $t_f$ denotes the time interval between two triplets; the initial mem-conductance is $\hat{\mathbf{G}} = 1$ mS. Taken from [1] ©2022 IEEE.                       | 41                     |

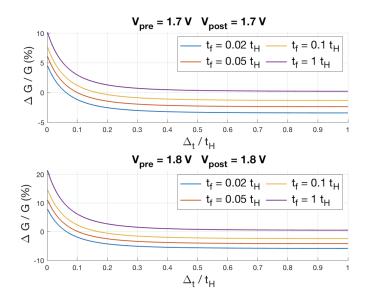

| 2.10 | Mem-conductance change versus $\frac{\Delta_t}{t_H}$ , for 30 cycles of pre-post-post-<br>pre quadruplets at different frequencies, and different programming<br>voltages. It is assumed $V_H = 0.8$ V, $\frac{t_H}{\tau_b} = 5.4$ , and $\frac{t_s}{\tau_b} = 0.108$ ; $t_f$<br>denotes the time interval between two quadruplets; the initial mem-<br>conductance is $\hat{\mathbf{G}} = 1$ mS. Taken from [1] ©2022 IEEE  | 42                     |

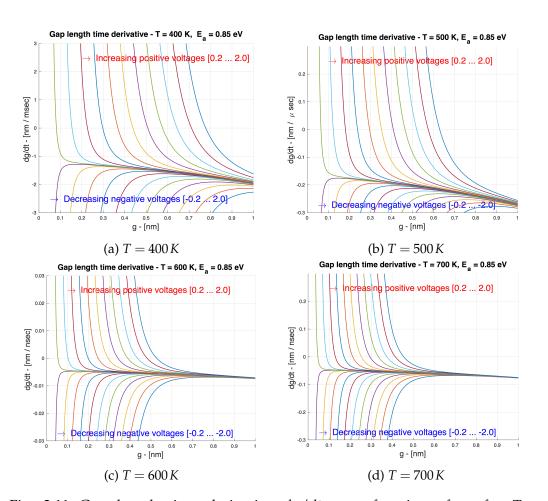

| 2.11 | Gap length time derivative $d\mathbf{g}/dt$ as a function of $\mathbf{g}$ , for $T \in \{400, 500, 600\}$<br>$\mathbf{r}/r_0 = 1$ , $E_a = 0.85  eV$ and different input voltages ranging from $-2V$ to $2V$ . Taken from [1] ©2022 IEEE.                                                                                                                                                                                    | 0,700} <i>K,</i><br>43 |

| 2.12 | Impact on STDP functions of a 5 % variation of the parameter $r_0$ .<br>A continuous line represents nominal values, circles represent per-<br>turbed values. Taken from [1] ©2022 IEEE.                                                                                                                                                                                                                                     | 46                     |

| 2.13 | Impact on STDP functions of a 5 % variation of the parameter $r_m$ .<br>A continuous line represents nominal values, circles represent per-<br>turbed values. Taken from [1] ©2022 IEEE                                                                                                                                                                                                                                      | 46                     |

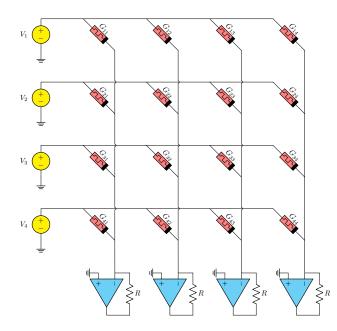

| 3.1  | Example of a $4 \times 4$ memristor crossbar array                                                                                                                                                                                                                                                                                                                                                                           | 50                     |

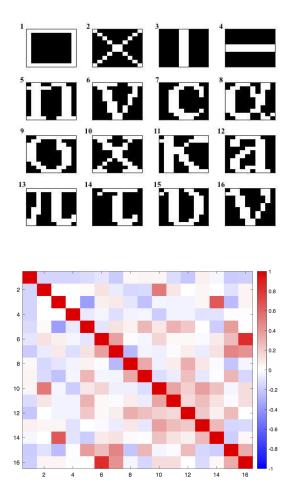

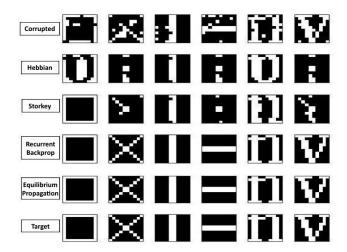

| 3.2  | Dataset of all the patterns to be memorized                                                                                                                                                                                                                                                                                                                                                                                  | 64                     |

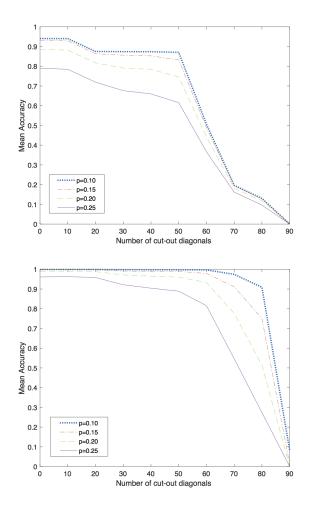

| 3.3  | Accuracy for different radius of connectivity.                                                                                                                                                                                                                                                                                                                                                                               | 65                     |

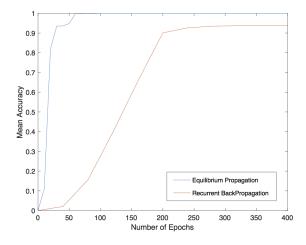

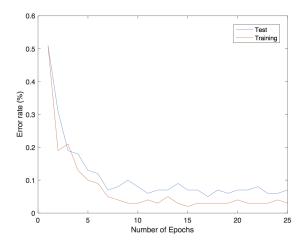

| 3.4 | Mean accuracy for different number of epochs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5 | Pattern reconstruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66 |

| 3.6 | Pattern classification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67 |

| 3.7 | Example of a sequence of presynaptic input spikes of period <i>T</i> (upper figure), giving rise to postsynaptic output of period 3 <i>T</i> . Each pre/post synaptic spike is represented by a programming pulse of magnitude $V_P$ and duration $t_s$ , followed by a heating pulse of duration $t_H$ ; the time interval between the beginning of the programming pulse and the beginning of the heating pulse is denoted with $t_{sh}$ . It is assumed that the postsynaptic spike occurs $\alpha t_H$ time units after the beginning of one presynaptic spike (with $0 \le \alpha \le 1$ ) and the following parameters, reported in (3.31), are shown for some mem-conductances: $\gamma_{1,2}^{post/pre}$ (related to the time shift between the beginning of the presynaptic programming pulses and the beginning pulse) and $\gamma_{2,3}^{pre/post}$ (related to the time shift between the beginning of the presynaptic heating pulse). Taken from [1] ©2022 IEEE. | 71 |

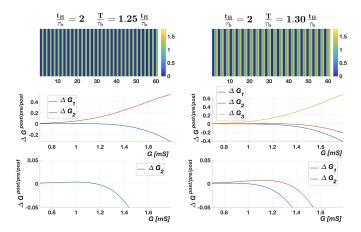

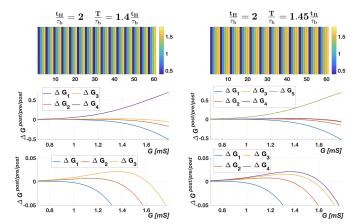

| 3.8 | Spiking network composed by 60 presynaptic neurons and one postsynaptic neuron. Upper part: mem-conductance pattern periodicity (2, for $\frac{T}{\tau_b} = 1.25 \frac{t_H}{\tau_b}$ , and 3, for $\frac{T}{\tau_b} = 1.3 \frac{t_H}{\tau_b}$ ); lower parts: mem-conductance variations, due to a sequence of post/pre/post spikes. Taken from [1] ©2022 IEEE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76 |

| 3.9 | Spiking network composed by 60 presynaptic neurons and one postsynaptic neuron. Upper part: mem-conductance pattern periodicity (4, for $\frac{T}{\tau_b} = 1.4 \frac{t_H}{\tau_b}$ , and 5, for $\frac{T}{\tau_b} = 1.45 \frac{t_H}{\tau_b}$ ); lower parts: mem-conductance variations, due to a sequence of post/pre/post spikes. Taken from [1] ©2022 IEEE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76 |

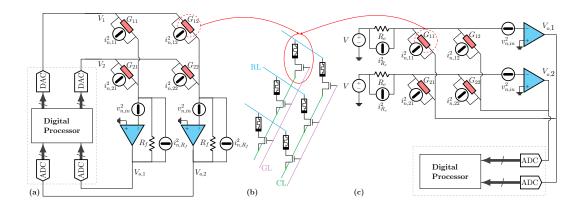

| 4.1 | (a) Illustration of a 2 × 2 open-loop crossbar used to perform<br>matrix-vector multiplication. All thermal noise sources associ-<br>ated with TIAs (formed by an op-amp and a feedback resistor)<br>and crossbar 1T1M cells are shown. (b) The one-transistor<br>one-memristor (1T1M) cell at each junction in a crossbar. GL:<br>Gate Line, RL: Row Line, CL: Column Line. (c) Illustration of a<br>$2 \times 2$ feedback crossbar for solving linear equations. The noise<br>sources are input resistors and TIAs (formed by an op-amp<br>and crossbar cells). Taken from [2] ©2021 IEEE                                                                                        | 81 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

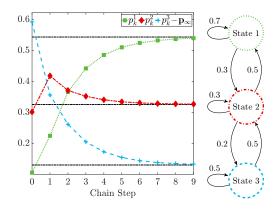

| 4.2 | Graphical representation of a generic regular three-state MC together with Power Method iterations. Black dashed lines correspond to the limiting distribution. Taken from [2] ©2021 IEEE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85 |

| 4.3 | Summary of the architectures and operations in this work. The open-loop crossbar enables the computation of both the next state distribution via an MVM operation and the stationary distribution of the chain by the sequential update provided by the Power Method. The requirements are linear transformations to set the conductance range and recover the correct result. When the evolution of the system is not required, the stationary distribution of the MC can be computed in a single step with the feedback crossbar configuration. After a preliminary linear transformation of the system, the routine does not need a recovering step. Taken from [2] ©2021 IEEE. | 88 |

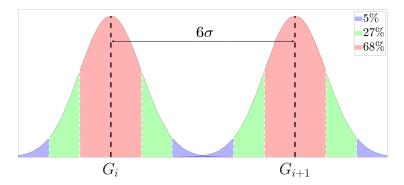

| 4.4 | Normally distributed programming noise model that illus-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00 |

| 1.1 | trates the intended write distribution between two conduc-<br>tance levels separated by the pre-defined bit precision. Taken                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | from [2] ©2021 IEEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93 |

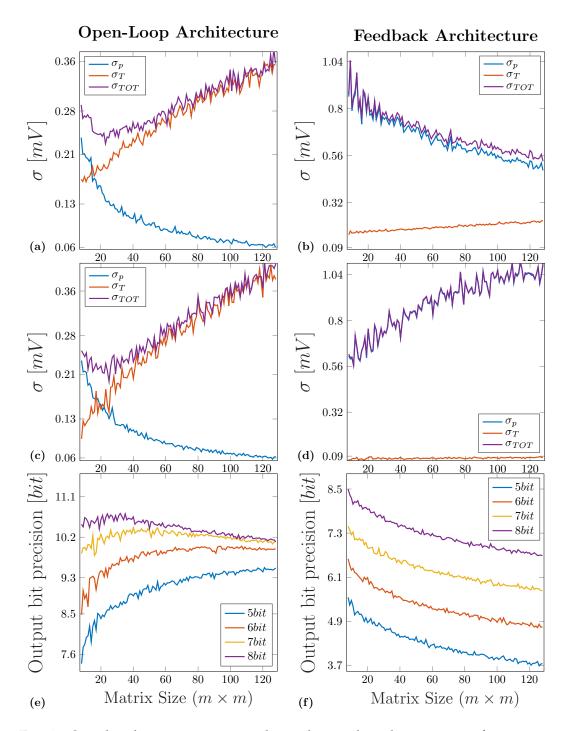

| 4.5 | Simulated programming $\sigma_p$ , thermal $\sigma_T$ and total $\sigma_{TOT}$ noise of a                                        |

|-----|----------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | generic output component for different crossbar sizes using both (a)                                                             |

|     |                                                                                                                                  |

|     | open-loop and (b) feedback architectures and 8 bits precision mem-                                                               |

|     | ristors with a conductance range of $[100\mu S, 1000\mu S]$ . (c) and (d) replicing the first order of $[100\mu S, 1000\mu S]$ . |

|     | cate the first row plots with a conductance range of $[10\mu S, 1000\mu S]$ .                                                    |

|     | (e) and (f) are the equivalent output bit precision for different matrix                                                         |

|     | sizes using open-loop and feedback crossbars, respectively. The total                                                            |

|     | noise contribution of different memristor precision was considered                                                               |

|     | and compared using MATLAB. The $\sigma_p$ estimates were computed by                                                             |

|     | using 1000 perturbations of a random transition matrix. The same                                                                 |

|     | operation was repeated for $\sigma_T$ by perturbing the input vector. The                                                        |

|     | total noise $\sigma_{TOT}$ was calculated by perturbing both transition matrix                                                   |

|     | and input vector. These estimates were then used to evaluate the                                                                 |

|     | output bit precision. To obtain the relationship between precision                                                               |

|     | and noise, systematic errors were excluded. The $\sigma_T$ includes thermal                                                      |

|     | noise contributions of memristors, resistors and op-amps. Taken                                                                  |

|     | from [2] ©2021 IEEE                                                                                                              |

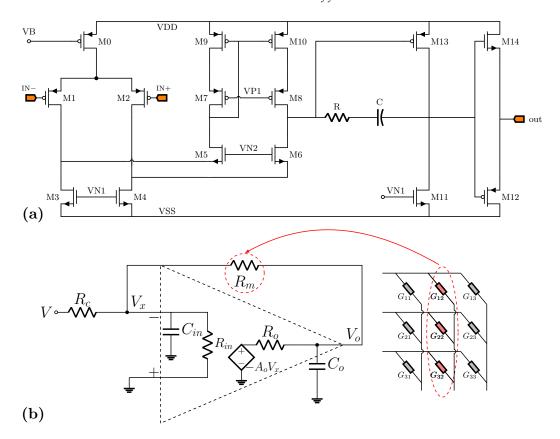

| 4.6 | a) Schematic of the transistor level op-amp. b) Schematic of                                                                     |

|     | a single TIA with the input resistor in a multi-loop feedback                                                                    |

|     | crossbar structure. $R_m$ is the parallel combination of memris-                                                                 |

|     | tors resistances in the feedback path. Taken from [2] ©2021                                                                      |

|     | IEEE                                                                                                                             |

| 4 🗖 |                                                                                                                                  |

| 4.7 | Frequency domain analysis to determine stability of each loop                                                                    |

|     | for the feedback circuit of Fig. 1(c). The plots show the re-                                                                    |

|     | sults for a single loop in a multi-loop system. The stability of                                                                 |

|     | the loop is determined by the intersection point of the open-                                                                    |

|     | loop gain curve of the op-amp ( $A_o(s)$ ) and noise gain curve                                                                  |

|     | $(1/\beta(s))$ . The phase margin is calculated on the LG phase                                                                  |

|     | curve ( $\phi(LG(s))$ ) using this point. DC gain and GBW of the                                                                 |

|     | op-amp are 86 <i>dB</i> and 1.1 <i>GHz</i> , respectively. Taken from [2]                                                        |

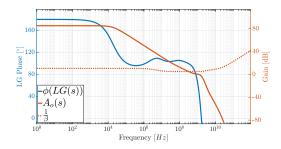

|     | ©2021 IEEE                                                                                                                       |

| 4.8  | Output accuracy in terms of normwise relative error and co-<br>sine similarity versus different memristor programming pre-<br>cisions for (a) open-loop and (b) feedback configurations for<br>a $64 \times 64$ crossbar. Output accuracy versus different matrix<br>sizes is given for (c) open-loop and (d) feedback configura-<br>tions with 8 bits precision memristors and non-ideal op-amps.<br>The expected accuracy is measured using 1000 perturbations                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | of a random matrix. The error bars contain the distributions<br>of each set of runs for 95% of the calculations. The normwise<br>relative error is a more sensitive indicator than cosine similar-<br>ity. The results are mainly affected by the errors arising from<br>memristor precision rather than op-amp non-idealities. Taken<br>from [2] ©2021 IEEE                                                                                                                        |

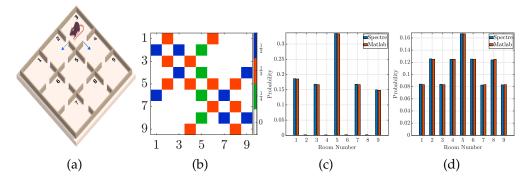

| 4.9  | (a) Example of a mouse trapped in a maze. (b) Transition ma-<br>trix representing the probability that the mouse goes from one<br>room to another. (c) Comparison between the 6-th step proba-<br>bility distribution using MATLAB and the proposed open-loop<br>crossbar with 8-bits precision memristors. (d) Comparison<br>between the stationary distribution using MATLAB and the<br>proposed feedback crossbar with 8-bits precision memristors.<br>Taken from [2] ©2021 IEEE |

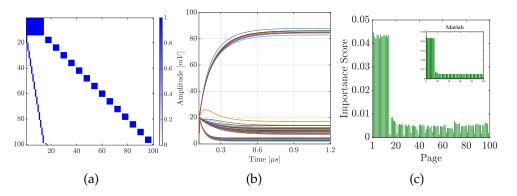

| 4.10 | (a) Adjacency matrix representing the links between the 100 pages of MathWorks dataset. (b) Transient behavior of the feedback system converging to the limiting distribution of the chain. (c) Simulated pageranks provided by the feedback crossbar. Taken from [2] ©2021 IEEE                                                                                                                                                                                                    |

| 4.11 | Taken from [2] ©2021 IEEE.         113                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **List of Tables**

| 2.1 | Parameters used for modeling the memristor dynamics | 29 |

|-----|-----------------------------------------------------|----|

| 3.1 | Accuracy for each single learning rule              | 62 |

## Introduction

## **Motivations**

In the last decade the emergence of big data problems and real world machine learning applications has put harder and harder challenges in front of computer engineers. Sought-after tasks such as speech recognition and image detection, which take fractions of milliwatt for the human brain to accomplish, require many orders of magnitude more power to achieve on traditional Von Neumann digital processors. In the new era of computing, the high inefficiency of the conventional paradigms calls for novel computing approaches. Very promising among those are the physics-based paradigms (e.g. Neuromorphic Computing, Quantum Computing etc.), where the fundamental laws of nature are exploited to carry out the computation. Whereas Quantum Computing exploits the laws of Quantum Mechanics, Neuromorphic Computing exploits the laws of Classical Electrodynamics to build bio-inspired analog computers which are much more energy-efficient and compact than their traditional digital counterparts.

On the neuromorphic computing side, large interest about memristive technologies has grown during the past decade. Memristors, theorized by Chua[3, 4] in 1971 as the 4<sup>th</sup> fundamental circuit elements, are 1–port systems whose electric conductance depends on the past evolution of the port variables (e.g. current and/or voltage)[5]. These fundamental elements take their name by the union of the two words "memory" and "resistor", as such circuit components behave as resistors with memory properties. Although conceived half a century ago, the memristor has been identified with a physical implementation only in 2008 when the research group lead by Stanley Williams at HP Labs recognized the hallmark of memristive behavior[6] in their Titanium Oxide nanodevices [7]. Since then, the numerous and heterogeneous technologies that fall into the memristive class have been widely exploited in analog and digital systems for a broad scope of applications, including amplifiers, filters, oscillators, logic gates and pseudo-random number generators [8–10]. At the time of writing, given memristors' multilevel analogue memory capabilities, mass storage and neuromorphic computing seem to be the most promising among those applications with each technology being best suited for certain problems[11]. In terms of voltage-current characteristic a two terminal memristor device is described by a memductance, which may depend on a set of first and second order state variables, commonly linked to the internal geometric parameters and to the internal temperature.

Fundamental to the development of a memristor-based neuromorphic computing system is the complexity of the physical modeling to be employed in higher-level circuit simulations. Thus, high-level identification techniques, circuit modeling methods and technology specific compact models are needed to analyze analogue computing circuits made of memristors. Although many decades long efforts have been put towards the development of very accurate mathematical models for each technology that can explain the fine grain dynamical behavior of these devices, still the very complex physics based models found in literature do not serve the purpose of providing good prediction on the global behavior of large number of those devices in a short amount of time. Since this is a surging problem for the simulation of large scale neuromorphic systems which may contain at least thousands of those devices, the research and development of novel modeling techniques and technology specific compact models has attracted the interest of many researchers both from the academia and the industry.

Furthermore devices of this kind also pose many challenges when operated in large arrays to perform computations. Each technology has it peculiarity and the device's non-idealities when compared to the ideal memristor theorized by Chua are many, to name a few:

- Nonlinearity of the Ohm's Law

- Drift of the memorized resistance over time

- Cycle-to-cycle variation of the programmed value

- Device-to-device variations

Although most of this nonideal effects have to be taken into account when designing a neuromorphic system, there are also approaches that try to exploit some of them as an advantage for the computation.

## **Thesis organization**

This doctoral thesis is organized as follows. Chapter 1 introduces the Phase Change Memory (PCM) technology and proposes a physics-based compact model that is employed to compute and validate on experimental data the PCM Dynamic Route Maps. Chapter 2 introduces the Resistive Random Access Memory (ReRAM) nonvolatile memory technology and proposes a compact model suitable for memristor-based Spiking Neural Networks (SNN). Chapter 3 brings examples on the modeling of both Spiking/Artificial Neural Networks and more conventional linear algebra accelerators. Chapter 5 concludes the manuscript and gives an overlook on possible future developments of the work.

### **Main Contributions**

The main contributions of this manuscript may be summarized with the following points:

- A novel physic-based current controlled model for Phase Change Memory devices.

- Computation and experimental validation of the PCM technology Dynamic Route Maps.

- Derivation of an almost analytical simplified model of the ReRAM memristor that involves two variables, the memductance, and the temperature, which can be related one-to-one with the synaptic efficacy and the calcium concentration in biological synapses

- Characterization of memristor-based spiking neural networks as discrete time nonlinear dynamical systems whose state variables are the mem-conductances and whose inputs and outputs are pre and postsynaptic spikes respectively.

- A case example of the design procedure for a memristor-based hardware accelerator.

- An in-depth study of the impact of non-idealities on memristor-based hardware accelerators for linear algebra problems solving with a particular focus on trade-offs and comparisons with the state of the art digital alternatives.

All the results presented in this manuscript are based on articles published by the author:

- Marrone, F., Secco, J., Kersting, B. et al. Experimental validation of state equations and dynamic route maps for phase change memristive devices. Sci Rep 12, 6488 (2022). doi: 10.1038/s41598-022-09948-6

- F. Marrone, G. Zoppo, F. Corinto and M. Gilli, "A Dynamic System Approach to Spiking Second Order Memristor Networks," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 4, pp. 1641-1654, April 2022, doi: 10.1109/TCSI.2021.3137713.

- Zoppo Gianluca, Marrone Francesco, Corinto Fernando, Equilibrium Propagation for Memristor-Based Recurrent Neural Networks, Frontiers in Neuroscience, vol. 14, March 2020, doi: 10.3389/fnins.2020.00240

- G. Zoppo, A. Korkmaz, F. Marrone, S. Palermo, F. Corinto and R. S. Williams, "Analog Solutions of Discrete Markov Chains via Memristor Crossbars," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 12, pp. 4910-4923, Dec. 2021, doi: 10.1109/TCSI.2021.3126477.

## Chapter 1

## **Memristor Device Modeling: PCM**

### 1.1 Introduction

Phase Change Memories (PCM) store data as the phase configuration of a layer of material between two metallic electrodes. The typical used materials include many different compounds of Ge, Te and Sb which all show high electrical resistivity in the amorphous phase and far lower resistivity in the crystalline phase. The memristance of a PCM device is tunable by changing the ratio between the amorphous and the crystalline fraction within the device volume usually by means of suitable electrical pulses, thus achieving a continuum of memristance (or memductance) states.

PCM devices show many fascinating nonlinear dynamical behaviors which all arise from the complex interaction between electrical, thermal and structural dynamics inside each device[12]. When a PCM cell is in mostly amorphous state (*OFF-state*), as the applied electrical fields is increased from relatively very low to higher values the conduction in the sandwiched material goes through ohmic, exponential and super-exponential regimes[13]. In the high-field *ON-state*, conduction through the amorphous phase becomes metal-like and the global flow of electrons in the PCM cell becomes dominated by the amorphous-crystalline Schottky barrier[14]. The event switching PCM devices from OFF to ON state is known as threshold switching which involves a feedback–driven thermo–electrical mechanism[15]. It starts when an externally applied field lowers the barrier between two close

Fig. 1.1 (a) Schematic representation of a mushroom-type PCM device operated with a current compliance series resistor  $R_s$ . In the RESET state, the amorphous phase blocks the bottom electrode, and the device is in a high-resistance state. The effective thickness of the amorphous region is denoted by  $u_a(t)$ .  $V_{applied}(t)$  is the externally applied input voltage, I(t) is the current flowing through the PCM device and  $V_{cell} = V_{applied} - R_s I$  is the intrinsic voltage drop on the device.(b) Measured pinched hysteresis loop for a mushroom PCM device stimulated by a 103 ns period triangular  $V_{applied}$  pulse of 2V peak voltage  $V_{pk}$ .

coulombic centers enough to induce an increase in the global conductivity of the device. This allows more current to flow and the temperature inside the PCM cell to rise. For high enough temperature the activation energy is strongly reduced and this in turn allows more electrons to flow through the material. This, in a very short time, leads to the threshold-switching event. Threshold switching plays a crucial role in the operation of PCM devices as it enables the fast *WRITE* operation by means of an abrupt temperature increase. Within the appropriate temperature range the *WRITE* operation can take the form of either a *SET* operation which increases the low-field conductivity by crystallizing the amorphous fraction or a *RESET* operation which does the opposite via the *melt-quenching* process which increases the internal PCM temperature up to the *GST* melting temperature  $T_{MELT} \approx 877K$ [16].

Accurate physical models have exploited integro-differential equations to describe the distinctive characteristic of each operating condition in PCM devices and thus numerical analysis is crucial to precisely capture the experimental observations [15]. In this Chapter the prototypical mushroom-type PCM device[17], depicted in Fig. 1.1a, is modeled as a memristive system as

introduced in 1976 by S. Kang and L. O. Chua [4]. The PCM device studied in this Chapter shows the typical memristive pinched loop under bipolar periodic input, as exemplified in Figure 1.1b, and thus can be casted in the memristive systems class[3]. The aim is to represent PCM devices via a statedependent Ohm's Law  $v = R(\mathbf{x}, i)i$  linking the current *i* through the PCM cell and voltage v across its two terminals and a state equation  $\dot{\mathbf{x}} = f(\mathbf{x}, i)$ which describes the dynamics of internal state variables x. By meas of the memristor state-dependent Ohm's law it is possible to unfold complex dynamic behaviors in PCM devices via the concepts of Dynamic Route Map (DRM)[18]. If the state variable is a scalar  $x \in \mathbf{R}$ , the DRM parameterized by the input *i* consists in the plot of f(x,i) in the plane  $(\dot{x},x)$ . By varying the parameter *i* it is possible to picture the entire family of curves spanning the whole plane  $(\dot{x}, x)$ . Additionally in the last years, DRMs have also been found to be a convenient modeling tool for similar devices. Ascoli et al. have proven that, in principle, DRMs can help to investigate all the cases of switching dynamics in memristor devices[19], [20]. Afterwards others works have demonstrated how DRMs are a powerful tool for modeling of devices such as ReRAMs, or of complex systems such as Cellular Nonlinear Networks [21, 22].

The PCM devices modeled in this Chapter are the ones of mushroomtype kindly made available by Abu Sebastian's group at IBM Research in Zurich, Switzerland. They take their type acronym from the mushroom-like amorphous dome which is created during the melt–quenching process that brings the device in its OFF state. The phase-change layer consists in doped  $Ge_2Sb_2Te_5$ . The bottom metallic electrode (BE) is  $\approx 20$  nm in radius and  $\approx$ 65 nm in length. The phase change material is  $\approx 100$  nm thick and extends up to the top electrode (TE) which is  $\approx 100$  nm in radius. In this Chapter it is shown how the modeling of this kind of devices can be successfully conducted via DRMs.

This Chapter is organized as follows: Section II goes deep into the physics of the device with an overview of the most accurate models for its dynamics and electric conduction, Section III introduces the novel proposed simplifications which enable the compact modeling of the device, Section IV reports the methodology to compute the Dynamic Route Maps of the PCM's first order dynamics, Section V concludes the Chapter and gives some future directions for expand on this work.

The content of this Chapter is a re-elaborated version of a research paper published by the author [23].

### 1.2 Complete second order model

In Figure 1.2 is reported an effective block representation of the intricate interconnection between the various phenomena involved in PCM devices' dynamics. It is composed, on first approximation, of two state variables  $T_{int}$  and  $u_a$  which are the temperature at the Amorphous/Crystalline Interface (ACI) and the amorphous dome effective radius respectively. In addition, the output current I (and the internally dissipated power  $P = V_{cell}I$ ) are expressed via an algebraic relation which relate the input cell voltage drop  $V_{cell}$ , the ambient temperature  $T_{AMB}$  and the state variables.

Fig. 1.2 Simplified block representation of the PCM device subsystems. The system has two inputs respectively  $V_{cell}(t)$  and  $T_{AMB}$  and one output I(t).  $V_{cell}(t)$  is the voltage drop on the PCM device. I(t) is the current flowing through the device.  $T_{AMB}$  is the ambient temperature the PCM device is operated at. P(t) is the algebraic electrical power dissipated by the device and computed as the product current I(t)times voltage  $V_{cell}(t)$ .  $u_a(t)$  is the amorphous mushroom thickness and its evolution is determined by the crystallization dynamics.  $T_{int}(t)$  is the temperature at the amorphous-crystalline interface and its evolution is determined by the heat balance equation.

#### 1.2.1 Complete Ohm's Law

Regarding the conduction mechanism in the amorphous-phase *GST*, more and more precise models have been proposed over the years to capture how it is influenced by the two state variables ( $u_a$ ,  $T_{int}$ ) and the applied voltage  $V_{cell}$ . Most of these models result accurate in specific electric-field domains.

In order to give an overview of the most common electric-field domain specific conduction model it should be introduced, for convenience,  $F_{T}$  as the transition field:

$$F_{\rm T} = \frac{q_{\rm e}}{\pi \epsilon_{\rm r} \epsilon_0 s^2}$$

where  $q_e$  is the fundamental electron charge,  $\epsilon_r \approx 10$  is the relative permittivity of the amorphous phase,  $\epsilon_0$  is the vacuum permittivity and *s* is the average distance between defects in the amorphous phase.

On the one hand for low to moderate electric field regimes (i.e.  $F = \frac{V_{cell}}{u_a} << F_T$ ), the simple Poole [24] results accurate in describing electrical conduction. On the other hand in the high field domain ( $F >> F_T$ ), the Pool-Frenkel [25][26][27] model gives the best approximation.

Below threshold switching (i.e. the device is in OFF state), the 3D Poole-Frenkel [28][29] emission of carriers from a two-center Coulomb potential well was experimentally demonstrated to best describe in an unified manner the conduction through *GST* material for both low and, moderate and high fields *F*.

3D Poole-Frenkel conduction formulates the density of free carriers under an applied field  $F = \frac{V_{cell}}{u_a}$  at an interface temperature  $T_{int}$  via the integral expression:

$$n(F,T_{int}) = \frac{K}{2} \int_0^{\pi} exp(-\frac{E_a(T_{int}) - E_{PF}(F,\theta)}{k_B T_{int}}) sin(\theta) d\theta$$

where  $\theta$  is the angle between the electric field and a possible direction of escape from the potential well and  $E_a(T_{int}) = E_{a,0} - \frac{aT_{int}^2}{b+T_{int}}$  is the interface temperature dependent activation energy and  $E_{PF}(F,\theta) = -max_r\Phi(r,\theta,F)$  is the Poole-Frenkel field-induced energy barrier lowering between two

adjacent potential wells. These are described in this model by the electric potential profile  $\Phi(r,\theta,F) = -qFrcos(\theta) - \frac{\beta^2}{4q}(\frac{1}{r} + \frac{1}{s-r}) + \frac{\beta^2}{qs}$  with  $\beta = \frac{q^2}{\sqrt{q\pi\epsilon_r\epsilon_0}}$ .

The amorphous phase conductivity per unit of area can be then computed as

$$\sigma(F, T_{int}) = q\mu(F)n(F, T_{int})$$

where  $\mu(F) = \frac{\mu_0}{\sqrt{1 + (\mu_0 F / v_{sat})^2}}$  is the field dependent mobility of carriers. The density of current  $j(F, T_{int})$  can be readily obtained as  $j(F, T_{int}) = \sigma(F, T_{int})F$  and the current flowing through the entire cell is found by multiplying the current density  $j(F, T_{int})$  times the effective bottom electrode contact area A. This should be computed via the effective bottom electrode radius and not the physical radius of the heater.

Although 3D Poole-Frenkel emission model captures the conduction in PCM materials up to the threshold switching event, nonetheless it does not hold accurate above threshold switching, i.e. after the amorphous phase is switched to ON state.

Phase Change Memory cells can be *reset* to high memristance states (OFF states) via relatively high current pulses that rises the ACI temperature up to the melting temperature  $T_{MELT}$ . Given that most of the power is dissipated at the BE, higher reset currents flowing through the device imply higher power dissipation which cause  $T_{MELT}$  to be reached further away from the BE. The resulting amorphous mushroom that is created has an effective amorphous thickness  $u_a$  which is proportional to the reset current  $I_{RESET}$ . This is shown in Figure 1.7a where the (i - v) characteristics under a ramp input are plotted for different reset conditions reported in the figure legend.

#### **1.2.2** Complete PCM Dynamics

The thermal dynamics of PCM devices follows the typical Newton's law of cooling. The state variable of interest for this devices is  $T_{int}$  which is the temperature at the ACI and drives the amorphous dome crystallization process. It is algebraically obtained as  $T_{int} = T_{AMB} + T_{SH}$  where  $T_{SH}$  is the intrinsically dynamic part of  $T_{int}$  and physically represents the cell Joule self-heating temperature increment while  $T_{AMB}$  is the constant ambient temperature. The dynamics of  $T_{SH}$  obeys the Ordinary Differential Equation (ODE):

$$\frac{d}{dt}T_{SH}(t) = \frac{1}{\tau_{th}}(R_{th}(u_a(t))P - T_{SH}(t))$$

(1.1)

where  $\tau_{th} = R_{th}(u_a(t))C_{th}(u_a(t))$  is the thermal time constant and  $R_{th}(u_a(t))$ , shown in Figure 1.3a, is the amorphous-thickness-dependent thermal resistance of the amorphous-phase dome that was estimated via FEM simulations in COMSOL [30] as the thermal resistance between the ACI and the external environment. Under the assumption of the BE electrode being being entirely blocked by the amorphous mushroom, an accurate linear approximation of  $R_{th}(u_a)$  can be given, as

$$R_{th}(u_a(t)) = -\kappa u_a(t) + R_{th,0}$$

(1.2)

where,  $\kappa \approx -0.024 \frac{K}{\mu W nm}$  and  $R_{th,0} \approx 1.908 \frac{K}{\mu W}$ .

Given the linearly decreasing approximation of  $R_{th}(u_a(t))$ , as the thermal capacitance  $C_{th}(u_a(t))$  is directly proportional to the amorphous dome volume, it is legitimate to assume  $\tau_{th} \approx const$ . This was found to be on the order of tens of nanoseconds[31].

The complete thermal dynamics of mushroom–type PCM cells, described by  $T_{int} = T_{AMB} + T_{SH}$  and (1.1), can be given a circuital interpretation as reported in Fig. 1.4.

The temperature at the ACI  $T_{int}$  drives the crystallization process, i.e. the reduction in volume of the amorphous dome by the rearrangement of disordered atoms at the interface into a regular lattice. The structural dynamics in PCM cells governs the evolution of the effective amorphous thickness  $u_a(t)$ . It should be pointed out that this differs from the real amorphous thickness which is the distance of the ACI from the center of the amorphous mushroom (see [32]). The evolution of  $u_a(t)$  is described by the ODE:

$$\frac{d}{dt}u_a(t) = -v_g(T_{int}(t)) \tag{1.3}$$

where  $u_a \in [0, 80]nm$ . The function  $v_g(\cdot)$  is the interfacial-temperature-dependent crystal growth velocity which was estimated in [30] and is reported in Figure

Fig. 1.3 (a) in continuous blue the effective thermal resistance, extrapolated from FEM simulations, as a function of the amorphous thickness  $u_a(t)$ . In dashed red the linear approximation of the effective thermal resistance in the blocked BE condition. (b) in continuous blue the experimentally estimated *GST* crystal growth velocity  $v_g(T_{int})$  as a function of the interface temperature  $T_{int}$ . In dashed red its Gaussian approximation.

1.3b. A Gaussian approximation of  $v_g(T_{int})$  has also recently been proposed in [33] as

$$v_g(T_{int}) = A_{v_g} exp(-(\frac{T_{int} - T_0}{\sigma_T})^2)$$

(1.4)

$A_{v_g} \approx 0.57 \frac{nm}{ns}$ ,  $T_0 \approx 749$  K and  $\sigma_T \approx 98$ K. Higher order effects such as structural relaxation dynamics of the amorphous phase GST are not taken into account in this model and their effect can be considered negligible given the narrow observation time window used in collecting the experimental data.

## 1.3 Simplified first order model derivation

In this Section a simplified first order model of the PCM dynamics is derived which is employed, later in this Chapter, to compute the Dynamic Route Maps of the Mushroom type phase change memory device under study.

Fig. 1.4 First order dynamical thermal circuit that takes into account the presence of  $C_{th}(u_a)$ . Its dynamics can be described through Equation (1.1).

#### 1.3.1 Simplified Ohm's Law

The read operation in PCM devices refers to the retrieval of the phaseconfiguration information by means of low amplitude current pulses. By assuming the BE to be fully blocked (i.e.  $u_a > 0$ ) and that the applied field is very low (i.e.  $F = \frac{V_{cell}}{u_a} \rightarrow 0$ ), then the voltage drop between the device electrodes can be well approximated by a linear relation  $V_{cell} = R_m(u_a, T_{int})I$ , as shown from experimental measurements in Fig. 1.7b, where the memristance,  $R_m(u_a, T_{int})$  is given by

$$R_{\rm m}(u_{\rm a}, T_{\rm int}) = K' u_{\rm a} exp(\frac{E_{\rm a}(T_{\rm int})}{k_{\rm B} T_{\rm int}})$$

(1.5)

where  $k_{\rm B}$  is the Boltzmann constant,  $E_{\rm a}(T_{\rm int})$  is the temperature-dependent activation energy and  $K' = \frac{1}{\pi r_{\rm BE}^2 q_e K \mu_0}$ . This formulation of the memristance  $R_{\rm m}(u_{\rm a}, T_{\rm int})$  can be readily derived from the first order expansion of the Poole conduction model for  $F \rightarrow 0$ .

The write operation in PCM devices involves the fast dissipation of power caused by current pulses which induces an amorphous-to-crystalline transition at the ACI. This happens via the threshold switching event, that puts the phase-change material sandwiched between the metal electrodes into a very low resistance state independent of the long–term memory state variable  $u_a$ . The voltage drop  $V_{cell}$ , after a short transient has passed since the threshold switching, is confined to a narrow voltage band around  $V_{cell,ON} \approx 0.8V$  as shown in Fig. (1.7c) and Fig. (1.6). This can be explained as the very-low

after-switching resistance state of the amorphous phase makes the conduction dominated by the barrier at the metal-semiconductor contact junction and by the resistance of the metallic electrodes. A simplified write model can thus be introduced as a reduction of the complex conduction mechanism to a simple nonlinear current-controlled resistor whose behavior, for high enough currents, is fairly well described by an ideal voltage generator of value  $V_{cell,ON}$ .

The two-domain approximation introduced above and illustrated in Fig. (1.7d can be summarized in the following state-dependent Ohm's Law

$$V_{cell} \approx \begin{cases} R_m(u_a, T_{int})I & I \ll I_{TH} \\ 0.8V & I \gg I_{TH} \end{cases}$$

(1.6)

where the well-below-threshold-switching model ( $I \ll I_{TH}$ ), represented with circuital symbolism in Fig. (1.7e), serves the purpose of recovering the phase configuration and the well-above-threshold-switching model ( $I \gg I_{TH}$ ), illustrated with circuital symbolism in Fig. (1.7f), is meant to accurately describe the cell power dissipation during the write phase and thus give good predictions about the temperature rise  $T_{SH}$  at the ACI. This is crucial in order to predict the internal state variables ( $u_a$ ,  $T_{int}$ ) evolution during the information storing phase and therefore it comes very handy to compute and plot the Dynamic Route Maps.

#### **1.3.2** Simplified temperature dynamics

In order to compute the conventional Dynamic Route Maps it is necessary to reduce the second order model to first order. By considering that the input variables (i.e.  $V_{cell}$  and  $T_{AMB}$ ) vary slowly with respect to the PCM cell thermal time constant  $\tau_{th} \approx 10 ns$ , then a first order model can be obtained by reducing (1.1) to the algebraic equation:

$$T_{SH}(t) = R_{th}(u_a(t))P \tag{1.7}$$

This simplification lets the interface temperature to be computed as  $T_{int} = T_{AMB} + T_{SH} = T_{AMB} + R_{th}(u_a)P$  where the input power  $P = IV_{cell}$  as shown by the circuital representation in Fig. (1.5).

Fig. 1.5 For the sake of the presented model the input signals to the PCM device are considered to be at least twice longer in duration than  $\tau_{th}$ , for this reason it is taken into account **(b)** described by Equation (1.7).

### **1.4 Dynamic Route Maps**

In this Section the Dynamic Route Maps of the PCM mushroom cell's first order dynamics are computed by employing the previously developed simplified first order model in conjunction with the simlified Ohm's Law.

#### 1.4.1 Numerically computed DRMs

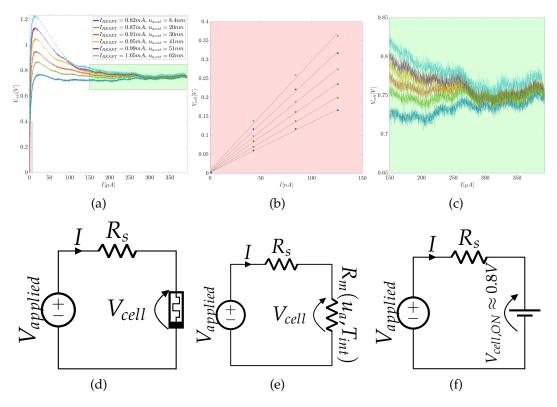

Using the above introduced current–controlled model of PCM cells a set of simulations were performed to compute and plot the theoretical DRMs of a PCM cell. In order to show how DRMs fill the  $(u_a, u_a)$  plane it was performed an input current *I* sweep ranging from  $I = 150 \,\mu\text{A}$  to  $650 \,\mu$  A. The computation was carried out combining Eqs. 1.3 and 1.4 and the results were plotted in Fig. 1.8. In all the reported case the initial  $u_a = 40 \,\text{nm}$  and each DRM corresponds to a different constant current flowing through the cell for an ideally infinite time.

It is possible to observe that the DRMs calculation considered a slight numerical correction inside the relation  $R_{\text{th}}(u_{\text{a}}(t))$  described in 1.2 and shown