# POLITECNICO DI TORINO Repository ISTITUZIONALE

A Comparison of Spread Spectrum and Sigma Delta Modulations to Mitigate Conducted EMI in GaN-Based DC-DC Converters

# Original

A Comparison of Spread Spectrum and Sigma Delta Modulations to Mitigate Conducted EMI in GaN-Based DC-DC Converters / Barbaro, Alberto; Fishta, Markeljan; Raviola, Erica; Fiori, Franco. - ELETTRONICO. - (2024). (Intervento presentato al convegno 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits (EMC Compo 2024) tenutosi a Torino (Italy) nel October 7-9, 2024).

Availability:

This version is available at: 11583/2993410 since: 2024-10-15T11:36:40Z

Publisher:

**IEEE**

**Published**

DOI:

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2024 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A Comparison of Spread Spectrum and Sigma Delta Modulations to Mitigate Conducted EMI in GaN-Based DC-DC Converters

Alberto Barbaro, Markeljan Fishta, Erica Raviola, Franco Fiori

Electronics and Telecommunication Dpt. (DET)

Politecnico di Torino

Turin, Italy

{alberto.barbaro, markeljan.fishta, erica.raviola, franco.fiori}@polito.it

Abstract—GaN power transistors offer significant advantages with respect to Si ones, but introduce challenges in meeting EMC regulations due to their high switching frequencies. This paper compares two modulation schemes, Spread-Spectrum Modulation (SSM) and Sigma-Delta Modulation ( $\Sigma\Delta M$ ), for reducing the conducted Electromagnetic Interference (EMI) delivered by GaN-based DC-DC converters. The study analyzes how these techniques impact converter performance and evaluates their effectiveness in reducing conducted EMI at low frequencies. The findings provide valuable insights for designers seeking the most effective strategy for EMI mitigation.

Index Terms-EMI, Buck, Sigma-Delta, Spread-Spectrum

### I. Introduction

Last-generation GaN power transistors have gained significant interest, particularly in automotive applications, due to their higher power-density, lower switching losses and better thermal performance compared to Si and SiC counterparts [1]. The high switching speed of GaN power transistors has led designers to adopt switching frequencies ranging from 100 kHz to 1 MHz [2]. However, this also results in higher conducted Electro Magnetic Interference (EMI) at low-frequency, meaning below a few MHz. Passive input EMI filters are typically placed at the input of DC-DC converters to meet the strict limits imposed by automotive EMC standards [3]. However, the weight and the volume of these filters are usually significant, thereby limiting the benefits of GaN technology [4].

To reduce the volume of EMI filters and fully leverage the advantages of GaN power transistors, EMI mitigation techniques effective at the source can be employed. Some techniques focus on controlling the switching transients of power transistors [5], however, they are mainly effective for frequencies higher than 10s MHz. To reduce conducted EMI at low frequencies, some propose alterations to the converter topology, such as by inserting an additional switching leg [6]–[8]. To avoid hardware modifications, alternative modulation

This publication is part of the project PNRR-NGEU which has received funding from the MUR-DM 117/2023.

strategies to traditional Pulse Width Modulation (PWM) can be adopted, as they can shape the frequency spectra of disturbance sources at low frequencies.

Among these techniques, the modulation of the switching frequency, also known as Spread-Spectrum Modulation (SSM), has been extensively used in DC-DC converters to reduce the delivered EMI [9]. The SSM is based on the spreading of energy around the harmonics of the switching waveforms, with the result of lowering the magnitude of peaks generated by PWM. Frequency modulation is mainly effective when the harmonics to be reduced are in the MHz range, as in case of GaN-based DC-DC converters, since large frequency deviation can be exploited [10], [11].

In addition to SSM, Sigma-Delta Modulation ( $\Sigma\Delta M$ ) has garnered increasing interest [12], [13], Compared to traditional PWM, a  $\Sigma\Delta$  modulator offers a finer control over the output voltage level, which is particularly advantageous when high switching frequencies are adopted. Additionally,  $\Sigma\Delta$  modulators naturally vary the switching frequency of their output signal, thus leading to a spread spectrum effect [13]. From an EMI perspective, [14] was one of the first to investigate the reduction of conducted EMI in  $\Sigma\Delta M$  modulated DC-DC converters, reporting a reduction of approximately 10 dB. More recently, [12], compared the spectrum of switching waveforms in case of PWM and  $\Sigma\Delta M$ . However, the studied frequency range only partially covers that mandated by automotive standards. Furthermore, no insight is provided on the effects of the modulation parameters on the conducted EMI and converter performance. To sum up, previous studies have not conducted a detailed analysis of the achievable EMI reduction in  $\Sigma\Delta M$  DC-DC converters, nor the impact of modulator parameters on converter performance and conducted EMI has been investigated. Moreover, no comparison has been performed between software-based techniques for EMI reduction, clearly highlighting advantages and disadvantages of each method.

The present paper provides a systematic comparison between two modulation schemes, namely SSM and  $\Sigma\Delta M$ , with particular regard to the conducted EMI mitigation in a GaN-based DC-DC converter. The comparison also includes

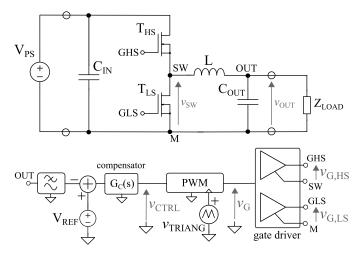

Fig. 1. Block diagram of a synchronous buck converter. The power stage is shown at the top, the controller at the bottom.

the effects of the two techniques on converter performance, providing valuable insights for designers to determine the most effective strategy.

This paper is organized as follows. The conducted EMI delivered by a buck converter are briefly recalled in Sect. II. The SSM and  $\Sigma\Delta$  modulators are then introduced in Sect. III and IV, respectively. Sect. V reports the simulation results when these modulations are applied to the buck converter exploited as test-case. Concluding remarks are in Sect. VI.

# II. CONDUCTED EMI OF A SYNCHRONOUS BUCK CONVERTER

The conducted EMI delivered by DC-DC converters can be discussed, without loss of generality, referring to a synchronous buck converter, as that shown in Fig. 1. The converter is comprised of two main blocks, i.e., the power stage and the controller. The DC input voltage to be regulated  $(V_{PS})$ is provided to a half-bridge consisting of a high-side  $(T_{HS})$ and a low-side  $(T_{\rm LS})$  transistor. Such power switches are turned on and off in complementary fashion, causing the  $v_{\mathrm{SW}}$ voltage to vary between  $V_{PS}$  and  $0 \, \text{V}$ . The inductor L and the output capacitor  $C_{OUT}$  are exploited as a second order low-pass filter to isolate the average value of  $v_{\rm SW}$ . Regarding the controller, a continuous-time architecture is shown in Fig. 1. The output voltage of the buck converter  $(v_{OUT})$  is typically attenuated, low-pass filtered, and subtracted from a reference voltage ( $V_{REF}$ ). The resulting error signal is fed to the compensator  $(G_{\mathbb{C}}(s))$ , which is designed to minimize the DC error and to provide the controller with a given bandwidth. The compensator output  $(v_{\text{CTRL}})$  is an analog signal proportional to the instantaneous duty cycle the voltage  $v_{\mathrm{SW}}$  should have to regulate  $V_{\rm PS}$  to the desired  $V_{\rm OUT}$ . The modulator, represented by the PWM block, compares  $v_{\text{CTRL}}$  with a triangular waveform ( $v_{\text{TRIANG}}$ ) with fixed frequency  $f_{\text{sw}}$ , and outputs a PWM square wave  $(v_G)$ . By exploiting suitable gate driver and dead time insertion circuits, driving signals

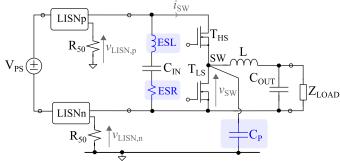

Fig. 2. Setup for measurement of conducted EMI delivered by the synchronous buck converter shown in Fig. 1. The main parasitic elements related to CM and DM disturbances have been enclosed in a box.

of the high-side and low-side power transistors ( $v_{\rm G,HS-LS}$ ) are generated.

To assess the compliance of a such a DC-DC converter with EMC regulations, the setup shown in Fig. 2 is used. Two Line Impedance Stabilization Networks (LISNs) are placed between the input power supply and the Device Under Test (DUT), i.e., the buck converter shown in Fig. 1, as prescribed by the CISPR-25 standard [3]. The conducted disturbances are measured across the  $R_{50}$  resistances, which model the input impedance of the measuring instrument. The conducted EMI can be analyzed by considering the Common Mode (CM) and Differential Mode (DM) disturbances separately. The former is defined as

$$v_{\text{LISN,CM}}(t) \triangleq \frac{v_{\text{LISN,P}}(t) + v_{\text{LISN,N}}(t)}{2},$$

(1)

where  $v_{\rm LISN,P}(t)$  and  $v_{\rm LISN,N}(t)$  are the voltages across the measurement ports of the LISNs, and the latter as

$$v_{\text{LISN.DM}}(t) \triangleq v_{\text{LISN.P}}(t) - v_{\text{LISN.N}}(t).$$

(2)

The main parasitic elements responsible for the CM and DM conducted disturbances are highlighted in Fig. 2, and they are enclosed in a box to be found at a glance. More precisely, DM emissions are related to the equivalent series inductance (ESL) and resistance (ESR) of the input capacitors, modeled by  $C_{\rm IN}$  in Fig. 2. ESL and ESR increase the equivalent impedance of the input capacitors at high frequencies, causing the switching current  $i_{SW}$  not to flow entirely through  $C_{IN}$ . Regarding CM EMI, capacitance  $C_P$  models the coupling of the power devices to the heat-sink, which is typically groundconnected. Due to the high dv/dt experienced by the SW node during the fast commutations of the power transistors, a CM current flows through  $C_{\rm P}$  at every commutation of  $v_{\rm SW}$ [15]. According to this simplified analysis, the primary source of CM (DM) EMI is identified as the switching voltage  $v_{\rm SW}$ (switching current  $i_{SW}$ ).

With power transistors  $T_{\rm LS}$  and  $T_{\rm HS}$  driven by the PWM modulator shown in Fig. 1, the frequency spectra of  $v_{\rm SW}$  and  $i_{\rm SW}$  are characterized by prominent peaks at multiples of the switching frequency  $f_{\rm SW}$ . As a result, the energy of CM and DM conducted disturbances is concentrated/focused

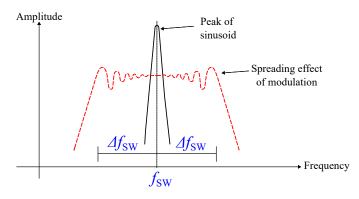

Fig. 3. When SSM is applied to a sinusoid, the energy associated to the fundamental frequency is spread over the Carson's bandwidth.

around the harmonics of  $f_{\rm SW}$ . Assuming  $v_{\rm SW}$  and  $i_{\rm SW}$  to be trapezoidal, the highest peak in their frequency spectra occurs at  $f_{\rm SW}$ . It is worth noting that in the case of GaN-based DC-DC converters,  $f_{\rm SW}$  is typically higher than  $150\,{\rm kHz}$ , meaning that the fundamental frequency falls within the regulated range. To reduce the magnitude of these peaks, which in turn determine the CM and DM conducted EMI levels, modulations different from standard PWM can be adopted.

# III. SPREAD-SPECTRUM MODULATION

A solution adopted both in DC-DC converters and digital systems to reduce the magnitude of peaks at the harmonics is using Spread-Spectrum Modulation (SSM) instead of traditional PWM. Such a technique consists in introducing an intentional variation of the switching frequency  $f_{\rm SW}(t)$ , according to a specific modulation profile. Assuming a sinusoid at the switching frequency, the modulated signal can be written as

$$s(t) = A \cdot \cos \left[ 2\pi f_{\text{SW}} + 2\pi \cdot \int_{0}^{t} \Delta f_{\text{SW}} \cdot \psi(\tau) d\tau \right]$$

(3)

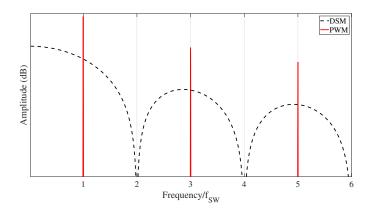

where A is the amplitude,  $\Delta f_{\rm SW}$  is the peak deviation of the instantaneous frequency and  $\psi(t)$  is the periodic modulating profile. The effect of the modulation is that of spreading the energy of the sinusoid in Carson's bandwidth, which is a range of frequencies defined as  $[f_{\rm SW}-\Delta f_{\rm SW},f_{\rm SW}+\Delta f_{\rm SW}]$ , as shown in Fig. 3.

When SSM is applied to modulate the fundamental frequency of a trapezoidal signal, such as  $i_{\rm SW}$  or  $v_{\rm SW}$ , it results in the spreading of each harmonic the signal is comprised of. More precisely, the energy of the  $k^{th}$  harmonic is spread over a frequency band of  $2k\Delta f_{\rm SW}$ . The effective reduction of peak magnitude depends on the parameters of the modulation. Indeed, peak reduction increases with the frequency deviation ( $\Delta f_{\rm SW}$ ). However, practical considerations limit the maximum frequency deviation that can be used in a DC-DC converter [10]. Moreover, if  $\Delta f_{\rm SW}$  is too large, the sidebands of adjacent harmonics may overlap, thus reducing the SSM efficacy [11]. The modulation index parameter is defined as

$$m = \frac{\Delta f_{\rm SW}}{f_{\rm m}} \tag{4}$$

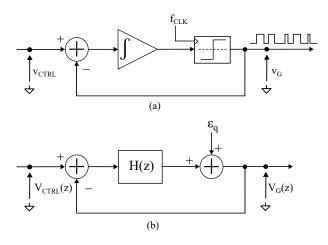

Fig. 4. Block diagram of (a) 1-bit Sigma-Delta modulator of the first order, and in (b) the corresponding linear model.

where  $f_{\rm m}$  is the frequency of the modulation profile  $\psi(t)$ . Previous studies have shown that an optimal m exists for each  $\Delta f_{\rm SW}$ , yielding the maximum peak reduction. Conversely, if the modulation becomes too fast or too slow, its efficacy decreases [10].

In order to implement SSM in the synchronous buck converter shown in Fig. 1, the fixed-frequency triangular generator ( $v_{\rm TRIANG}$ ) can be replaced by one with instantaneous frequency varying according to  $\psi(t)$ . In such a way, all other blocks remain unchanged. Moreover, by choosing  $\Delta f_{\rm SW} << f_{\rm SW}$ , the average current ripple in the inductor L is that of traditional PWM, meaning that the design of the power stage is not affected by SSM. Due to these considerations, periodic SSM can be effortlessly integrated into existing DC-DC converters, and it can provide both DM and CM EMI reduction. However, a critical aspect of using SSM is choosing the proper modulation parameters, i.e, m and  $\Delta f_{\rm SW}$ , which otherwise may result in a negligible EMI reduction.

# IV. SIGMA-DELTA MODULATION

Besides applying SSM to the PWM modulator shown in Fig. 1, the peaks at the  $f_{\rm SW}$  harmonics of the switching waveforms  $i_{\rm SW}$  and  $v_{\rm SW}$  can be reduced by using a different strategy than pulse-width modulation. In the context of power converters, Sigma-Delta ( $\Sigma\Delta$ ) modulators can be exploited as an alternative to PWM. A  $\Sigma\Delta$ M converts an analog signal into a Pulse Density Modulated (PDM) signal. This means that the  $\Sigma\Delta$  output is a digital bitstream where the amplitude of the input signal determines the density of pulses. In a PDM bitstream, the pulse width is a multiple of the  $\Sigma\Delta$  clock period, making the bitstream a frequency-modulated signal.

The block scheme of a 1-bit  $\Sigma\Delta$  modulator is shown in Fig. 4(a). It is a feedback-based structure where the adder performs the difference between the input voltage  $v_{\rm CTRL}$  at step i and the output voltage  $v_{\rm G}$  at step i-1. Such a difference is then fed to the integrator. Finally, the clocked comparator acts as a two levels quantizer, thus providing a bitstream at the output.

Fig. 5. STF of a  $\Sigma\Delta$  modulator (dashed line) compared to the output spectrum of a PWM modulator (solid line). It is assumed that the modulator is clocked with a frequency  $2f_{\rm SW}$ .

The linearized model of the  $\Sigma\Delta$  modulator (see Fig. 4(a)) is shown in Fig. 4(b), where  $\varepsilon_{\rm q}$  is the quantization error introduced by the quantizer and H(z) is the transfer function of the integrator. According to such a model, the modulator output can be written, in the time discrete domain z, as

$$V_{\rm G}(z) = STF(z)V_{\rm CTRL}(z) + NTF(z)\varepsilon_{\rm q},$$

(5)

where the Signal Transfer Function (STF) is

$$STF(z) = \frac{H(z)}{1 + H(z)} \tag{6}$$

and the Noise Transfer Function (NTF) is

$$NTF(z) = \frac{1}{1 + H(z)}. (7)$$

As far as H(z) is concerned, for a first-order discrete-time integrator it is  $H(z)=(z-1)^{-1}$ , yielding a high-pass response of NTF(z). This represents the fundamental property of a  $\Sigma\Delta$  modulator, which is the noise-shaping, namely, the capability to move the quantization noise out of band.

The shape of the STF, which is shown in Fig. 5, suggests that the output spectrum is smooth, with no switching harmonics. Such a behavior can be exploited to reduce the EMI delivered by the converter in Fig. 1, by replacing the PWM block with a  $\Sigma\Delta$  modulator. However, this change affects several figures of merit of the converter, e.g., stability and conversion efficiency. When the clock frequency of the comparator ( $f_{CLK}$ ) equals to the PWM switching frequency  $(f_{\rm SW})$ , the half-bridge control signal  $v_{\rm G}$  generated by a  $\Sigma\Delta$ modulator has fewer commutations than that generated by a PWM modulator, as the  $\Sigma\Delta$  modulator holds the same output value for at least one clock period. This increases the converter efficiency by reducing the switching losses of power transistors, but also increases the current ripple of the power inductor. By setting  $f_{CLK} = k \cdot f_{SW}$ , where k is an integer, previous studies have shown that  $\Sigma\Delta$  and PWM modulators can achieve the same power conversion efficiency provided that  $k \geq 2$  [16]. As far as the stability of the DC-DC converter is concerned, the phase margin decreases when

TABLE I BUCK CONVERTER PARAMETERS

| Parameter                      | Value                | Parameter        | Value              |

|--------------------------------|----------------------|------------------|--------------------|

| $V_{\mathrm{PS}}$              | 48 V                 | L                | 4.7 μΗ             |

| $V_{ m OUT}$                   | $12\mathrm{V}$       | $C_{\rm IN}$     | $125\mu\mathrm{F}$ |

| $I_{ m OUT}$                   | $10\mathrm{A}$       | $C_{ m OUT}$     | $375\mu\mathrm{F}$ |

| $T_{ m LS}, T_{ m HS}$         | [17]                 | $C_{\mathbf{p}}$ | $10\mathrm{pF}$    |

| $f_{ m SW}$                    | $400\mathrm{kHz}$    | ESL              | $28\mathrm{pH}$    |

| $\Delta v_{ m OUT}/V_{ m OUT}$ | $1.37 \cdot 10^{-3}$ | ESR              | $240\mu\Omega$     |

| $\Delta i_L/I_{ m OUT}$        | 0.5                  |                  |                    |

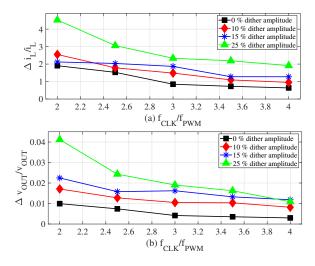

Fig. 6. Inductor current ripple normalized to nominal output current (star) and voltage output ripple normalized to nominal output voltage (square marker) in the case of SSM.

employing a  $\Sigma\Delta$  modulator because the STF in (6) includes a delay factor. Such a delay contributes a phase rotation of  $360^{\circ} \cdot f_{\rm T}/f_{\rm CLK}$ , where  $f_{\rm T}$  is the crossover frequency of the closed-loop converter [16].

First order  $\Sigma\Delta$  modulators are known to suffer from limit cycles. This phenomenon occurs when a constant voltage is present at the input of the modulator, resulting in a repeating pattern in the output bitstream. This leads to idle tones in the output frequency spectrum, worsening EMI performance. The magnitude of the tones can be reduced either by adding of a dither signal at the input of the quantizer or by increasing of the order of the modulator. The former solution introduces noise at the output of the converter, while the latter may worsen the stability of the modulator itself, leading to a more complex design procedure. In contrast, first-order modulators are always stable.

### V. CIRCUIT ANALYSIS

The synchronous buck converter shown in Fig. 1 has been used as case study to compare the aforementioned modulation schemes, i.e., PWM, SSM and  $\Sigma\Delta M$ . To this purpose, PWM, SSM and  $\Sigma\Delta M$  modulator blocks have been utilized with the same power stage and controller. The main parameters of the analyzed converter are listed in Table I for reference. Time-domain simulations have been carried out with Spectre [18], a SPICE-like simulator, to assess EMI reduction, converter efficiency, as well as voltage and current ripple for the various modulation schemes. As far as SSM is concerned, a fixed  $\Delta f_{\rm SW} = 60\,{\rm kHz}$  was employed, and the modulation index

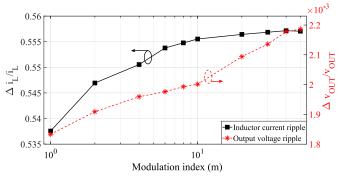

Fig. 7. Inductor current ripple normalized to nominal output current (at the top) and output voltage ripple normalized to nominal output voltage (at the bottom) in the case of  $\Sigma\Delta M$ .

defined in (4) was varied between 1 and 50. Regarding the  $\Sigma\Delta$  modulator, the clock frequency  $f_{\rm CLK}$  was in the 0.8-1.6 MHz range, and different levels of the dither noise were investigated to address the issue of limit cycles.

The inductor current ripple ( $\Delta i_{\rm L}$ ) normalized to the nominal output current  $(I_{OUT})$ , and the output voltage ripple  $(\Delta v_{OUT})$ normalized to the nominal output voltage  $(V_{OUT})$ , are shown in Fig. 6 for the SSM case. More precisely,  $\Delta i_{\rm L}/I_{\rm OUT}$  is plotted on the left y-axis, while  $\Delta v_{\rm OUT}/V_{\rm OUT}$  on the right y-axis. Comparing these normalized normalized ripples with those obtained using traditional PWM with fixed  $f_{SW}$ , as detailed in Table I, the use of SSM results in a 10 % (50 %) increase of the inductor current (output voltage) ripple. Referring to the  $\Sigma \Delta M$  case,  $\Delta i_{\rm L}/I_{\rm OUT}$  and  $\Delta v_{\rm OUT}/V_{\rm OUT}$ are shown in Fig. 7 at the top and the bottom, respectively. The  $\Sigma\Delta$  clock frequency was normalized to that of PWM, i.e.,  $f_{\rm SW}$ =400 kHz. By increasing the clock frequency, voltage and current ripples reduce, as the average switching period decreases. Conversely, current and voltage ripples worsen when increasing the dither amplitude. Regarding the current ripple, a limit case is when  $\Delta i_{\rm L} = I_{\rm OUT}$ , meaning that the current in the inductor reaches 0 A. For such a reason, a maximum dither amplitude of 15 % (circle marker) of the reference signal  $v_{\rm CTRL}$  was considered in what follows.

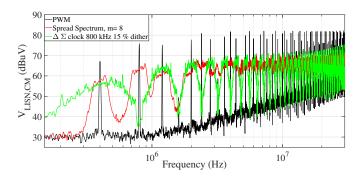

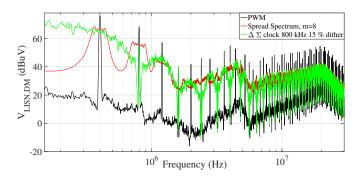

To assess the conducted EMI delivered by the converter when exploiting SSM, PWM and  $\Sigma\Delta$ , the setup shown in Fig. 2 was employed. More precisely, the voltages across the LISNs measurement ports  $(v_{\rm LISN,P})$  and  $v_{\rm LISN,N}$  were analyzed to assess the CM and DM contribution according to (1) and (2). The resulting signals were processed using the virtual EMI receiver described in [19], which was configured with a 9 kHz resolution bandwidth (RBW) and peak detector, as prescribed by the standard [3]. The resulting frequency spectra in the  $150\,\mathrm{kHz}$ -30 MHz range are shown in Fig. 8 and 9 for the CM and DM contribution, respectively. The spectra in case of SSM

Fig. 8. Comparison of frequency spectrum of CM EMI between PWM, SSM with m=8 and  $\Sigma\Delta \rm M$  clocked at 800 kHz.

Fig. 9. Comparison of frequency spectrum of DM EMI between PWM, SSM with m=8 and  $\Sigma\Delta \rm M$  clocked at 800 kHz.

modulator refer to a modulation index (m) equal to 8, those in case of  $\Sigma\Delta$  modulator to a  $800\,\mathrm{kHz}$  clock frequency  $(f_\mathrm{CLK})$  and 15 % dither amplitude. SSM and  $\Sigma\Delta$  modulators exhibit comparable performances in reducing the magnitude of peaks, except when the nulls of the  $\Sigma\Delta$  signal transfer function (see Fig. 5) align with some of the PWM peaks. In such cases, the  $\Sigma\Delta$  modulator exhibits a significant reduction. However, despite the addition of dithering, idle tones remain visible in the EMI spectra, such as at 200 kHz and 600 kHz for the CM EMI in Fig. 8.

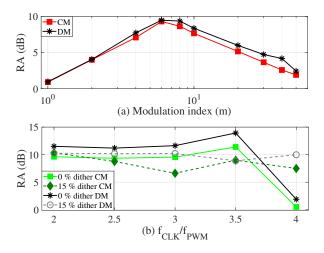

To further compare the two modulation techniques in terms of CM and DM EMI reduction, the Relative Amplitude (RA) was defined as

$$RA = \max_{[f_{sw} - \Delta f, f_{sw} + \Delta f]} (V_{LISN,CM,PWM}) - \max_{[f_{sw} - \Delta f, f_{sw} + \Delta f]} (V_{LISN,CM,Mod})$$

(8)

which represents the difference between the peak of the PWM spectrum and the maximum EMI value achieved with an alternative modulator around  $f_{\rm SW}$ . Such a relative amplitude is shown in Fig. 10 for (a) the SSM and (b)  $\Sigma\Delta M$  cases, with a  $\Delta f$ =20 kHz. For SSM, the achievable reduction depends on the modulation index, with an optimal index m of 8 resulting in an RA of  $9\,\mathrm{dB}$  for both CM (square) and DM (star markers). In contrast,  $\Sigma\Delta$  modulator achieves an RA of around RA=10 dB.

Finally, the conversion efficiency of the DC-DC converter was evaluated and reported in Table II for the considered

Fig. 10. Conducted EMI attenuation around  $400\,\mathrm{kHz}$  when employing SSM (at the top) and  $\Sigma\Delta\mathrm{M}$  (at the bottom) for CM (square) and DM (star) components.

#### TABLE II EFFICIENCY COMPARISON

| Case study                        | Value   | Case study                         | Value   |

|-----------------------------------|---------|------------------------------------|---------|

| PWM                               | 99.03 % | SS (m=8)                           | 99.03 % |

| $\Sigma\Delta$ 800 kHz, 0% dither | 99.21 % | $\Sigma\Delta$ 800 kHz, 15% dither | 98.99 % |

| $\Sigma\Delta$ 1.2 MHz, 0% dither | 99.17 % | $\Sigma\Delta$ 1.2 MHz, 15% dither | 98.98 % |

| $\Sigma\Delta$ 1.6 MHz, 0% dither | 99.06 % | $\Sigma\Delta$ 1.6 MHz, 15% dither | 98.92 % |

modulation schemes. The use of SSM does not impact the efficiency, while increasing the clock frequency in  $\Sigma\Delta$  modulators moderately reduces the efficiency. This observation aligns with what discussed in Sect. IV, as switching losses increase with higher clock frequencies. Additionally, a minor decrease in efficiency is noted with the addition of dithering.

### VI. CONCLUSIONS

This work compares Spread Spectrum Modulation (SSM) and  $\Sigma\Delta$  modulators applied to a DC-DC converter, focusing on their effectiveness in reducing conducted EMI at low frequency compared to traditional PWM modulators. Such an aspect is crucial in GaN-based power converters, which operate at switching frequencies above the lower bound of conducted EMI regulated range, i.e., 150 kHz. The study found that both SSM and  $\Sigma\Delta$  modulators exhibit comparable performance in reducing CM and DM EMI reduction, achieving around 10 dB reduction with optimal parameter settings. However, the output voltage ripple with the  $\Sigma\Delta$  modulator was approximately 10 times higher than that with SSM. The conversion efficiency was marginally affected by the choice of modulator. These findings underscore the importance of selecting appropriate modulator parameters to optimize EMI reduction. These insights are also relevant for power converters using transistors other than GaN, offering a means to reduce conducted EMI at the source by changing the type of modulator used in the controller.

## REFERENCES

- [1] K. S. Boutros, R. Chu, and B. Hughes, "GaN power electronics for automotive application," in 2012 IEEE Energytech, May 2012, pp. 1–4.

- [2] R. T. Yadlapalli, A. Kotapati, R. Kandipati, S. R. Balusu, and C. S. Koritala, "Advancements in energy efficient GaN power devices and power modules for electric vehicle applications: a review," vol. 45, no. 9, pp. 12638–12664. [Online]. Available: https://onlinelibrary.wiley.com/doi/abs/10.1002/er.6683

- [3] "CISPR 25:2021 Vehicles, boats and internal combustion engines -Radio disturbance characteristics - Limits and methods of measurement for the protection of on-board receivers," Dec. 2021.

- [4] B. Narayanasamy and F. Luo, "A Survey of Active EMI Filters for Conducted EMI Noise Reduction in Power Electronic Converters," *IEEE Transactions on Electromagnetic Compatibility*, vol. 61, no. 6, pp. 2040–2049, Dec. 2019.

- [5] E. Raviola and F. Fiori, "An adaptive method to reduce undershoots and overshoots in power switching transistors through a low-complexity active gate driver," *IEEE Transactions on Power Electronics*, vol. 38, no. 3, pp. 3235–3245.

- [6] M. Fishta and F. Fiori, "Volume reduction of traction power inverter EMI filter based on mitigation techniques at the source," in 2024 IEEE Joint International Symposium on Electromagnetic Compatibility, Signal & Power Integrity, pp. 723–726, ISSN: 2640-7469.

- [7] E. Raviola, M. Roman, L. Zai, and F. Fiori, "Reduction of CM conducted emission with a small dummy leg and the delay compensation technique," in 2023 IEEE Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMC+SIPI), pp. 542–547.

- [8] M. Fishta, E. Raviola, and F. Fiori, "EMI Reduction at the Source in WBG Inverters: A Comparative Study of Spread-Spectrum Modulation and Auxiliary Switching Leg Techniques," *IEEE Transactions on Elec*tromagnetic Compatibility, pp. 1–8, 2024.

- [9] B. Deutschmann, "Spread spectrum clocking for emission reduction of charge pump applications," in 2013 9th International Workshop on Electromagnetic Compatibility of Integrated Circuits (EMC Compo), Dec. 2013, pp. 123–128.

- [10] F. Pareschi, R. Rovatti, and G. Setti, "EMI Reduction via Spread Spectrum in DC/DC Converters: State of the Art, Optimization, and Tradeoffs," *IEEE Access*, vol. 3, pp. 2857–2874, 2015.

- [11] D. Gonzalez, J. Balcells, A. Santolaria, J.-C. Le Bunetel, J. Gago, D. Magnon, and S. Brehaut, "Conducted EMI Reduction in Power Converters by Means of Periodic Switching Frequency Modulation," *IEEE Transactions on Power Electronics*, vol. 22, no. 6, pp. 2271–2281, Nov. 2007.

- [12] A. Hirota and M. Nakaoka, "A Suppressed Noise Dc-Dc Buck Converter Introducing A Novel Modulation Scheme with Random Pulse Sequence," in 2019 14th IEEE Conference on Industrial Electronics and Applications (ICIEA), Jun. 2019, pp. 270–275.

- [13] B. F. Bokmans, B. J. Vermulst, and J. M. Schellekens, "Improved Delta-Sigma Modulator for Direct Switch Control of a DC-DC Converter," in 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2023, pp. 2881–2887.

- [14] J. Paramesh and A. von Jouanne, "Use of sigma-delta modulation to control EMI from switch-mode power supplies," *IEEE Transactions on Industrial Electronics*, vol. 48, no. 1, pp. 111–117, 2001.

- [15] H. W. Ott, Electromagnetic Compatibility Engineering. Wiley-IEEE Press, 2009.

- [16] S. Dunlap and T. Fiez, "A noise-shaped switching power supply using a delta-sigma modulator," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 51, no. 6, pp. 1051–1061, 2004.

- [17] Epc2218: 100 v, 231 a enhancement-mode gan power transistor. [Online]. Available: https://epc-co.com/epc/products/ganfets-and-ics/epc2218

- [18] Spectre Circuit Simulator Reference. San Jose, CA, USA: Cadence Design Systems, Inc. (Cadence), Jan. 2020.

- [19] T. K. C. F. S. Bendicks, Andreas; Dörlemann, "MATLAB/Octave function to evaluate time-domain signals according to the measurement bandwidth and average/peak detector of EMI test receivers," in *Proceed*ings Conference Electromagnetic Compatibility, Cologne, Germany, Jul. 2022, pp. 459–466.