### POLITECNICO DI TORINO Repository ISTITUZIONALE

# Analysis and Conceptualization of a 400 V 100 kVA Full-GaN Double Bridge Inverter for Next-Generation Electric Vehicle Drives

Original

Analysis and Conceptualization of a 400 V 100 kVA Full-GaN Double Bridge Inverter for Next-Generation Electric Vehicle Drives / Cittanti, Davide; Vico, Enrico; Armando, ERIC GIACOMO; Bojoi, IUSTIN RADU. - ELETTRONICO. - (2022), pp. 740-747. (Intervento presentato al convegno 2022 IEEE Transportation Electrification Conference & Expo (ITEC) tenutosi a Anaheim, CA, USA nel 15-17 June 2022) [10.1109/itec53557.2022.9813847].

Availability: This version is available at: 11583/2969996 since: 2022-07-28T07:31:43Z

Publisher: IEEE

Published DOI:10.1109/itec53557.2022.9813847

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

## Analysis and Conceptualization of a 400 V 100 kVA Full-GaN Double Bridge Inverter for Next-Generation Electric Vehicle Drives

Davide Cittanti, Enrico Vico, Eric Armando and Radu Bojoi Dipartimento Energia "G. Ferraris", Politecnico di Torino, Italy *Corresponding Author*: Davide Cittanti (davide.cittanti@polito.it)

Abstract-The rising demand for electric vehicles (EVs) is pushing the industry to develop cheaper, lighter and more efficient powertrains. In particular, the drive inverter represents a crucial component of an EV drive train, being responsible for the DC/AC power conversion between the battery and the electrical machine. As a result, advanced converter topologies and modern wide bandgap (WBG) semiconductor devices are being actively evaluated by both industry and academia, aiming to improve the performance of next-generation EV drive inverters. In this context, the double bridge inverter (DBI) represents a promising candidate for 400 V EV powertrains, allowing to increase the machine phase voltage and thus to reduce the inverter phase current for a given power level. Although a three-phase machine with an open-end winding configuration is required, the DBI unlocks significant benefits at the converter level, especially if state-of-theart 600/650 V GaN high electron mobility transistors (HEMTs) are employed. Therefore, this paper proposes the analysis and the conceptualization of a full-GaN 100 kVA 400 V DBI for nextgeneration EV drives. A complete theoretical assessment of the system active and passive component stresses (i.e., semiconductor losses, machine phase flux ripple, DC-link capacitor RMS current and charge ripple) is performed, providing the basis for the converter sizing. Additionally, a DBI design concept is developed, achieving an estimated 99.7 % peak semiconductor efficiency (99.2 % at rated current) and a 192 kVA/dm<sup>3</sup> power density.

*Index Terms*—double bridge inverter; traction inverter; wide bandgap (WBG) devices; gallium nitride (GaN); high electron mobility transistors (HEMTs); electric vehicles (EVs)

#### I. INTRODUCTION

The drive inverter represents a central component of an EV drive train, since it performs the DC/AC power conversion between the battery and the electrical machine (cf. Fig. 1). As a consequence, a great effort is currently being spent to improve the performance of this power electronic converter [1], [2], which requires high power density, high efficiency over a wide load range [3], high temperature operation capability, and high switching frequency (i.e., to provide sufficient control margin and reduce time-harmonic losses in low-inductance, high-speed machines with several pole pairs typically adopted in automotive [3]–[6]).

Two key enabling technologies may play a significant role in addressing these challenging requirements: novel drive inverter topologies (i.e., different from the widely adopted two-level voltage-source inverter) [7]–[9] and modern wide bandgap (WBG) semiconductor devices [9]–[11]. Whereas three-level inverter topologies are excellent candidates for upcoming 800 V EV powertrains [7], [12], [13], as they simultaneously reduce the stress on the supplied machine [6] and enable the adoption

of semiconductor devices with lower blocking voltage (i.e., featuring higher conduction and switching performance [14]), also drive systems based on the widespread 400 V battery architecture can benefit from advanced converter topologies.

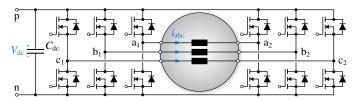

A particularly promising candidate for 400 V powertrains is the double bridge inverter (DBI), which consists of two separate three-phase two-level inverters connected as in Fig. 2 [15], [16]. Even though the electrical machine must feature an openend winding configuration, the DBI allows to increase the machine phase voltage with respect to a two-level inverter (i.e., either by a factor of 2 or  $\sqrt{3} \approx 1.73$ , depending on the two-level inverter modulation strategy), thus reducing the phase current value for a given power level. The lower phase current of the DBI unlocks significant benefits, reducing the RMS current stress and/or charge ripple on the DClink capacitor (i.e., requiring a lower capacitance and thus reducing the inverter size), and allowing for the adoption of semiconductor devices with reduced current rating and enhanced switching properties (i.e., enabling higher switching frequency operation). A further performance enhancement can be obtained by employing modern 600/650 V silicon carbide (SiC) and gallium nitride (GaN) semiconductor devices, which significantly outperform traditional silicon (Si) devices of the same voltage class [10], [11]. Although 600/650 V GaN high electron mobility transistors (HEMTs) are still not well established in the automotive industry, as opposed to SiC MOSFETs (i.e., which are already employed in several EV drive inverters), they promise higher theoretical performance and thus represent excellent candidates for next-generation EVs.

While several papers have already been published on GaNbased high-voltage (> 100 V) inverters, they either target a low power rating (i.e.,  $\leq 10$  kW) [17]–[21] or exploit GaN devices in a multi-level configuration [18]–[23], trading higher performance for increased complexity. To the best of the authors' knowledge, no GaN-based 400 V  $\geq 50$  kW three-phase inverter design has been reported in literature.

Fig. 1. Simplified schematic overview of an electric vehicle (EV) drive train, including the battery, the drive inverter and the electric motor.

Fig. 2. Schematic of the considered double bridge inverter (DBI) drive system.

Therefore, the main goal of this paper is to provide a detailed analysis and conceptualization of a GaN-based high-performance high-power DBI for next-generation 400 V EV drives. In particular, the main contributions of this work are:

- the comprehensive analysis of the stresses applied to the semiconductor devices (i.e., conduction and switching losses), the electrical machine (i.e., differential-mode and common-mode phase flux ripples) and the DC-link capacitor (i.e., RMS current and charge ripple) for all operating conditions;

- the conceptualization of a high-efficiency, high-power density 100 kVA 400 V full-GaN DBI employing state-of-the art semiconductor devices and ceramic capacitors, including the design and/or sizing of all converter components.

This paper is structured as follows. In Section II the operational basics of the DBI are described, including the AC-side voltage formation and the DC-side current generation processes. In Section III the drive system active and passive component stresses are analyzed in detail, providing the basis for the converter design. In Section IV a DBI design concept is proposed and its perfomance is assessed in simulation environment. Finally, Section V summarizes and concludes this work.

#### **II. BASICS OF OPERATION**

The equivalent circuit schematic of the considered 400 V three-phase double bridge inverter (DBI) drive system is illustrated in Fig. 2. The electrical machine features an openend winding configuration and each phase is connected between two independently controlled two-level inverter bridge-legs (i.e., adopting 600/650 V active switches).

The DBI can synthesize an average sinusoidal voltage across the machine phases in several ways, namely providing different modulation references to the two three-phase inverters. In the present work, two modulation strategies are selected and compared, both assuming synchronized and in-phase modulation carriers. The first modulation strategy is referred to as unipolar pulse-width modulation (PWM) [15]. This strategy continuously modulates both three-phase inverters according to opposite sinusoidal references, achieving a frequency doubling effect at the machine phase terminals (i.e., the first harmonic frequency of the machine phase flux ripple is  $2 f_{sw}$ ). The second modulation strategy, referred to as unfolder PWM [15], differentiates the two inverter units by having one three-phase unit continuously modulated at  $f_{sw}$  and the other unit working in six-step operation at the machine fundamental frequency f (i.e., providing the unfolding feature). Notably, the switching losses in the unfolding inverter can typically be neglected (i.e.,  $f \ll f_{sw}$ ). Therefore, unfolder PWM allows to halve the total DBI switching losses at the expense of losing the frequency doubling feature at the

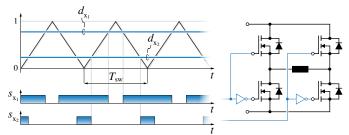

Fig. 3. Generation of the bridge-leg PWM switch signals  $s_{x_1}$  and  $s_{x_2}$ .

machine phase terminals. It is worth noting that unipolar PWM and unfolder PWM both ensure an equal loss distribution among semiconductor devices of the same inverter unit. For instance, another modulation strategy is reported in [15], alternating the unfolding role between the two inverters. Nevertheless, even though this strategy allows to equally distribute the semiconductor losses between the two inverters, it does not ensure an equal loss sharing between devices of the same bridge-leg (i.e., leading to possible thermal issues), therefore it is not considered herein.

The bridge-leg PWM switch signals  $s_{x_1}$  and  $s_{x_2}$  (x = a, b, c) are generated from the comparison between the bridge-leg duty cycles and the modulation carrier, as illustrated in Fig. 3. The DBI modulation references are defined as

$$\begin{cases} m_{\rm a} = \frac{M}{2}\cos(\vartheta) \\ m_{\rm b} = \frac{M}{2}\cos(\vartheta - \frac{2}{3}\pi) \\ m_{\rm c} = \frac{M}{2}\cos(\vartheta - \frac{4}{3}\pi) \end{cases}$$

(1)

where  $M = 2V/V_{\rm dc}$  is the inverter modulation index (i.e.,  $0 \le M \le 2$ ), and the bridge-leg duty cycles are directly obtained from (1), as

$$d_{\mathbf{x}_1} = \frac{1+m_{\mathbf{x}}}{2}, \quad d_{\mathbf{x}_2} = \frac{1-m_{\mathbf{x}}}{2}$$

(2)

for unipolar PWM, and

$$d_{x_1} = \begin{cases} m_x & m_x \ge 0\\ 1 + m_x & m_x < 0 \end{cases} \qquad d_{x_2} = \begin{cases} 0 & m_x \ge 0\\ 1 & m_x < 0 \end{cases}$$

(3)

for unfolder PWM, with x = a, b, c.

#### A. AC-Side Voltage Formation

The AC terminal of each bridge-leg may be actively connected either to the positive (p) or negative (n) DC-link rails. Therefore, the voltage applied to the machine phases can assume three different values:

- $v_{x_1x_2} = +V_{dc}$ , with  $s_{x_1} = 1$  and  $s_{x_2} = 0$ ,

- $v_{x_1x_2} = -V_{dc}$ , with  $s_{x_1} = 0$  and  $s_{x_2} = 1$ ,

- $v_{x_1x_2} = 0$ , with  $s_{x_1} = s_{x_2} = 1$  or  $s_{x_1} = s_{x_2} = 0$ ,

where  $s_{x_1}$  and  $s_{x_2}$  are the switching signals of the two bridgelegs connected across phase x (1 if high-side ON, 0 if low-side ON, cf. Fig. 3). Therefore, the phase voltage can be expressed as

$$v_{x_1x_2} = (s_{x_1} - s_{x_2}) V_{dc}$$

$x = a, b, c.$  (4)

Since the machine features an open-end winding configuration, its phases are subject to both the differential-mode (DM) and the common-mode (CM) components of the phase voltage, as opposed to conventional three-phase machines with an open star point (i.e., only subject to the DM voltage). Analyzing the two three-phase inverters independently, the zero-sequence (i.e., common-mode) voltage of each unit is obtained by averaging the three bridge-leg voltage contributions, as

$$v_{o_1} = \frac{v_{a_1n} + v_{b_1n} + v_{c_1n}}{3} = v_{o_1,LF} + v_{o_1,HF}, \qquad (5)$$

$$v_{o_2} = \frac{v_{a_2n} + v_{b_2n} + v_{c_2n}}{3} = v_{o_2, LF} + v_{o_2, HF}, \qquad (6)$$

and the differential-mode voltages are found by subtracting the zero-sequence component from the bridge-leg voltages, as

$$v_{x_1} = v_{x_1n} - v_{o_1} = v_{x_1,LF} + v_{x_1,HF}$$

$x = a, b, c,$  (7)

$$v_{x_2} = v_{x_2n} - v_{o_2} = v_{x_2,LF} + v_{x_2,HF}$$

x = a, b, c, (8)

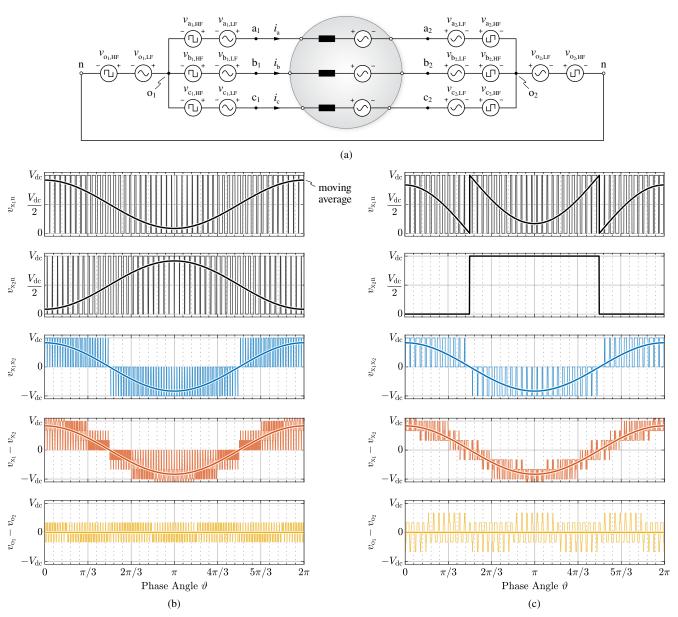

where subscripts LF and HF indicate the low-frequency (i.e., moving average) and high-frequency (i.e., switching frequency harmonics) voltage components, respectively. Therefore, the AC-side voltage formation process of the DBI can be represented with the equivalent circuit illustrated in Fig. 4(a). The low-frequency components of the DM voltage  $v_{x_1,LF}$ ,  $v_{x_2,LF}$  are regulated by means of the duty cycles in (2)–(3) to control the converter phase currents  $i_a$ ,  $i_b$ ,  $i_c$ . The low-frequency components of the CM voltage  $v_{o_1,LF}$ ,  $v_{o_2,LF}$  are equal (i.e.,  $v_{o_1,LF} = v_{o_2,LF}$ ), ensuring that no low-frequency CM voltage is applied across the machine phases. Finally, the high-frequency components of both DM and CM voltages

1

Fig. 4. (a) equivalent circuit schematic of the DBI AC-side voltage formation process. Qualitative overview of the inverter bridge-leg voltages  $v_{x_1n}$ ,  $v_{x_2n}$ , phase voltage  $v_{x_1x_2}$ , differential-mode (DM) voltage  $v_{x_1} - v_{x_2}$  and common-mode (CM) voltage  $v_{o_1} - v_{o_2}$  adopting (b) unipolar PWM and (c) unfolder PWM, assuming M = 5/3. The low-frequency (i.e., moving-average) component of each waveform is also shown for clarity.

$v_{x_1,HF}$ ,  $v_{x_2,HF}$ ,  $v_{o_1,HF}$ ,  $v_{o_2,HF}$  define the stress applied to the machine phases in terms of flux and current ripples, which determine the machine PWM-induced losses [6].

A qualitative overview of the DBI bridge-leg voltages  $v_{x_1n}$ ,  $v_{x_2n}$ , phase voltage  $v_{x_1x_2}$ , DM voltage  $v_{x_1} - v_{x_2}$  and CM voltage  $v_{o_1} - v_{o_2}$  is reported in Fig. 4(a), (b) for unipolar PWM and unfolder PWM, respectively.

#### B. DC-Side Current Generation

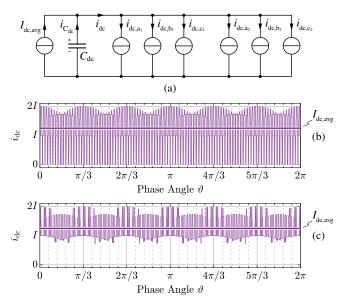

The DC-link current  $i_{dc}$  is defined by the combination of the instantaneous phase current values  $i_a$ ,  $i_b$ ,  $i_c$  and the bridge-leg switching signals  $s_{x_1}$ ,  $s_{x_2}$ , as

$$i_{\rm dc} = i_{\rm dc,a_1} + i_{\rm dc,b_1} + i_{\rm dc,c_1} + i_{\rm dc,a_2} + i_{\rm dc,b_2} + i_{\rm dc,c_2}$$

$$= (s_{\rm a_1} + s_{\rm a_2}) i_{\rm a} + (s_{\rm b_1} + s_{\rm b_2}) i_{\rm b} + (s_{\rm c_1} + s_{\rm c_2}) i_{\rm c}.$$

(9)

Assuming sinusoidal phase currents with peak value I, i.e.,

$$\begin{cases} i_{\rm a} = I\cos(\vartheta) \\ i_{\rm b} = I\cos(\vartheta - \frac{2}{3}\pi - \varphi) \\ i_{\rm c} = I\cos(\vartheta - \frac{4}{3}\pi - \varphi) \end{cases}$$

(10)

the DC-link current average can be calculated as in [24], obtaining 3

$$I_{\rm dc,avg} = \frac{5}{4} M I \cos \varphi. \tag{11}$$

The current flowing into the DC-link capacitor is finally obtained by difference, as

$$i_{\rm C_{dc}} = i_{\rm dc} - I_{\rm dc,avg},\tag{12}$$

leading to the equivalent circuit reported in Fig. 5(a). The instantaneous DC-link current waveforms are qualitatively illustrated in Fig. 5(b), (c) for unipolar PWM and unfolder PWM, respectively.

Fig. 5. (a) equivalent circuit schematic of the DBI DC-side current generation process. Qualitative overview of the DBI DC-link current  $i_{dc}$  waveforms adopting (b) unipolar PWM and (c) unfolder PWM, assuming M = 5/3. The average DC-link current  $I_{dc,avg}$  is indicated.

#### **III. COMPONENT STRESS ANALYSIS**

In this section, the stresses applied to the semicondutor devices, the machine phases and the DC-link capacitor are analyzed, providing useful analytical expressions for the converter design in Section IV.

#### A. Semiconductor Losses

Assuming the adoption of unipolar semiconductor devices (e.g., MOSFETs, HEMTs), the total conduction losses of the DBI can be expressed as [15]:

$$P_{\rm cond,tot} = 3 R_{\rm ds,on} I^2, \tag{13}$$

where  $R_{\rm ds,on}$  is the semiconductor on-state resistance.

Additionally, since fast-switching devices are typically characterized by a linear dependence of the switching energies  $E_{\rm on}$ ,  $E_{\rm off}$  with respect to the switched current  $i_{\rm sw}$  (i.e.,  $E_{\rm on} \approx k_{0,{\rm on}} + k_{1,{\rm on}} i_{\rm sw}$ ,  $E_{\rm off} \approx k_{0,{\rm off}} + k_{1,{\rm off}} i_{\rm sw}$  for  $i_{\rm sw} \ge 0$ , and  $E_{\rm on} = E_{\rm off} \approx 0$  for  $i_{\rm sw} < 0$ ) [7], the average switching losses generated by the DBI can be expressed as [15]

$$P_{\rm sw,tot} = \alpha f_{\rm sw} \left[ \left( k_{0,\rm on} + k_{0,\rm off} \right) + \frac{2}{\pi} I \left( k_{1,\rm on} + k_{1,\rm off} \right) \right], \quad (14)$$

where  $\alpha = 6$  for unipolar PWM and  $\alpha = 3$  for unfolder PWM (i.e., neglecting the losses related to switching transitions at fundamental frequency of the second inverter unit, being  $f \ll f_{sw}$ ).

#### B. Machine Phase Flux Ripple

The high-frequency voltage-time area applied to the machine phases generates a flux linkage ripple  $\Delta \psi$  directly related to the magnetic flux density swing (and losses) within the machine stator/rotor cores and/or magnets. Furthermore,  $\Delta \psi$ translates into a current ripple inversely proportional to the machine inductance, which generates additional winding losses. Therefore,  $\Delta \psi$  is directly responsible for all PWM-induced high-frequency losses in the driven machine [6] and therefore represents a useful and comprehensive machine stress indicator.

Since a DBI drive system features an electrical machine with open-end windings (cf. Fig. 2), both DM and CM voltages fall across the machine phases (cf. Fig. 4). In particular, while the DM voltage sees the relatively large differential-mode phase mutual inductance  $L_{\rm DM}$ , the CM voltage is applied to the much lower common-mode inductance  $L_{\rm CM}$  (i.e., being typically determined by the small leakage flux). Therefore, due to the different DM and CM flux paths within the machine (i.e., affecting core losses differently) and since  $L_{\rm DM} \gg L_{\rm CM}$  (i.e., leading to very different current ripples and winding losses), the machine phase DM and CM flux ripple components

$$\Delta \psi_{\rm DM,x} = \int_0^t \left( v_{\rm x_1,HF} - v_{\rm x_2,HF} \right) dt \qquad x = a, b, c \quad (15)$$

$$\Delta \psi_{\rm CM} = \int_0^t \left( v_{\rm o_1, \rm HF} - v_{\rm o_2, \rm HF} \right) {\rm d}t \tag{16}$$

must be analyzed independently. To take into account the flux ripple amplitude along the complete fundamental period,

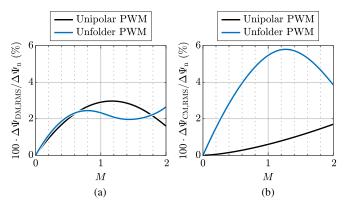

Fig. 6. Normalized DBI machine phase RMS flux ripple components as function of the inverter modulation index M for unipolar PWM and unfolder PWM: (a) differential-mode (DM) flux ripple  $\Delta \Psi_{\rm DM,RMS}$ , (b) common-mode (CM) flux ripple  $\Delta \Psi_{\rm CM,RMS}$ . The results are normalized by  $\Delta \Psi_{\rm n} = V_{\rm dc}/f_{\rm sw}$ .

the global DM and CM RMS flux ripples are considered as performance indices, defined as [25]

$$\Delta \Psi_{\rm DM,RMS}^2 = \frac{6}{T} \int_0^{\frac{T}{6}} \frac{\Delta \psi_{\rm DM,a}^2 + \Delta \psi_{\rm DM,b}^2 + \Delta \psi_{\rm DM,c}^2}{3} \, dt$$

(17)

$$\Delta \Psi_{\rm CM,RMS}^2 = \frac{6}{T} \int_0^{\frac{T}{6}} \Delta \psi_{\rm CM}^2 \, dt$$

(18)

Introducing a flux ripple normalization factor  $\Delta \Psi_n = V_{dc}/f_{sw}$ , the following analytical expressions are derived, respectively

$$\frac{\Delta\Psi_{\rm DM,RMS}^2}{\Delta\Psi_{\rm n}^2} = \frac{M^2}{384} - \frac{M^3}{576} \left(\frac{\sqrt{3}}{\pi} + \frac{7}{3\pi}\right) + \frac{M^4}{2048}$$

(19)

$$\frac{\Delta\Psi_{\rm CM,RMS}^2}{\Delta\Psi_{\rm n}^2} = \frac{M^3}{576} \left(\frac{\sqrt{3}}{\pi} - \frac{5}{3\pi}\right) \tag{20}$$

for unipolar PWM, and

$$\frac{\Delta\Psi_{\rm DM,RMS}^2}{\Delta\Psi_{\rm n}^2} = \frac{M^2}{576} \left(4 - \frac{3\sqrt{3}}{\pi}\right) - \frac{M^3}{576} \left(\frac{4\sqrt{3}}{\pi} + \frac{3}{\pi}\right) + \frac{M^4}{512} + K_{\Psi}$$

(21)

$$\frac{\Delta\Psi_{\rm CM,RMS}^2}{\Delta\Psi_{\rm n}^2} = \frac{M^2}{576} \left(2 + \frac{3\sqrt{3}}{\pi}\right) + \frac{M^3}{576} \left(\frac{4\sqrt{3}}{\pi} - \frac{13}{\pi}\right) - K_{\Psi}$$

(22)

for unfolder PWM, where  $K_{\Psi} = 0$  for  $M \leq 2/\sqrt{3}$  and

$$K_{\Psi} = \frac{1}{18\pi} \operatorname{acos}\left(\frac{2}{\sqrt{3}M}\right) - \frac{11}{216\pi}\sqrt{3M^2 - 4} + \frac{M^2}{576} \left[\frac{36}{\pi} \operatorname{acos}\left(\frac{2}{\sqrt{3}M}\right) - \frac{8}{\pi}\sqrt{3M^2 - 4}\right]$$

(23)

for  $M > 2/\sqrt{3}$ . The results of the analysis are illustrated in Fig. 6, where  $\Delta \Psi_{\rm DM,RMS}$  and  $\Delta \Psi_{\rm CM,RMS}$  are reported in normalized form as functions of the DBI modulation index  $M = 2V/V_{\rm dc}$ for both unipolar PWM and unfolder PWM. It is observed that, while the two modulation strategies show similar values of DM RMS flux ripple, they yield very different CM flux ripple stresses. In particular, unfolder PWM leads to increased common-mode PWM-induced losses over the complete operating range.

#### C. DC-Link Capacitor RMS Current and Charge Ripple

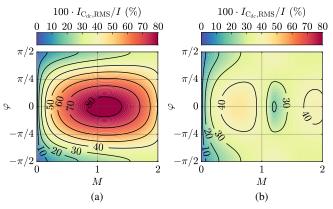

The DC-link capacitor sizing/design is both affected by the RMS current stress  $I_{C_{dc,RMS}}$  and the peak-to-peak charge ripple  $\Delta Q_{C_{dc,pp}}$  (i.e., directly proportional to the DC-link peak-to-peak voltage ripple and thus to the minimum required capacitance). Disregarding the AC-side switching frequency current ripple, both stresses can be analytically calculated.

The RMS current flowing into the DC-link capacitor can be calculated by difference, as

$$I_{\rm C_{dc},RMS}^2 = I_{\rm dc,RMS}^2 - I_{\rm dc,avg}^2,$$

(24)

where  $I_{\rm dc,RMS}^2 = 6/T \int_0^{T/6} i_{\rm dc}^2 dt$  and  $I_{\rm dc,avg}$  is defined in (11). Expanding and simplifying (24), the following analytical expressions are derived, respectively

$$I_{\rm C_{dc},RMS} = I_{\rm V} \left[ \frac{\sqrt{3} - 1}{4\pi} + \cos^2 \varphi \left( \frac{\sqrt{3} + 2}{\pi} - \frac{9}{16} M \right) \right]$$

(25)

for unipolar PWM, and

$$I_{\rm C_{dc},RMS} = I \sqrt{M \left[\frac{\sqrt{3}}{4\pi} + \cos^2\varphi\left(\frac{\sqrt{3}}{\pi} - \frac{9}{16}M\right)\right]} + K_{\rm I} \quad (26)$$

for unfolder PWM, where  $K_{\rm I} = 0$  for  $M \le 2/\sqrt{3}$  and

$$K_{\rm I} = \frac{\sqrt{3}}{8\pi} M \sin\left[2\varphi + 3\alpha\cos\left(\frac{2}{\sqrt{3}M}\right)\right] + \frac{1}{M^2} \left[\sin 2\varphi \,\frac{9M^2 - 16}{12\pi} + \cos 2\varphi \,\sqrt{3M^2 - 4} \,\frac{9M^2 - 16}{8\pi}\right] + \frac{3}{2\pi} \sqrt{3M^2 - 4} - \frac{3}{\pi} \alpha\cos\left(\frac{2}{\sqrt{3}M}\right) \quad (27)$$

for  $M > 2/\sqrt{3}$ . Notably, unfolder PWM yields the same RMS current stress as in the two-level inverter case (i.e., for  $M \le 2/\sqrt{3}$ ) [24]. The two  $I_{C_{dc},RMS}$  expressions are illustrated in normalized form (i.e., divided by the peak phase current I) in Fig. 7 as functions of M and  $\varphi$ . The worst-case value of (25)

Fig. 7. Normalized DBI DC-link capacitor RMS current  $I_{C_{dc},RMS}$  as function of the inverter modulation index M and the load power factor angle  $\varphi$  for (a) unipolar PWM and (b) unfolder PWM. The normalization factor is the peak phase current I.

Fig. 8. Normalized DBI DC-link capacitor peak-to-peak charge ripple  $\Delta Q_{C_{dc},pp}$  as function of the inverter modulation index M and the load power factor angle  $\varphi$  for (a) unipolar PWM and (b) unfolder PWM. The normalization factor is  $\Delta Q_n = I/f_{sw}$ .

(unipolar PWM) is found for  $\varphi = 0$  and  $M = \frac{10\sqrt{3}+14}{9\pi}$ , as

$$I_{\rm C_{dc},RMS,max} = \frac{5\sqrt{3}+7}{6\pi} I \approx 0.83 I,$$

(28)

whereas the worst-case value of (26) (unfolder PWM) is found for  $\varphi = 0$  and  $M = \frac{10\sqrt{3}}{9\pi}$ , as

$$I_{\rm C_{dc},RMS,max} = \frac{5\sqrt{3}}{6\pi} I \approx 0.46 I.$$

(29)

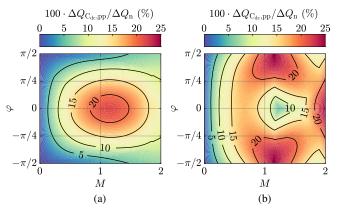

The capacitor charge ripple  $\Delta q_{\rm C_{dc}}$  (i.e., the high-frequency current-time area) can be directly obtained by integrating the DC-link current  $i_{\rm C_{dc}}$ , as

$$\Delta q_{\rm C_{dc}} = \int_0^t i_{\rm C_{dc}} \,\mathrm{d}t,\tag{30}$$

which features a  $^{T/6}$  periodicity. However, since the analytical expression of  $\Delta q_{\rm C_{dc}}$  and the location of its maximum both change with M and  $\varphi$ , the expression of  $\Delta Q_{\rm C_{dc},\rm pp}$  is a complicated piecewise-defined function [26], which is not reported here for reasons of simplicity. Therefore,  $\Delta Q_{\rm C_{dc},\rm pp}$  is calculated numerically and is illustrated in normalized form in Fig. 8 for both unipolar PWM and unfolder PWM, where  $\Delta Q_{\rm n} = I/f_{\rm sw}$  is the normalization factor. The worst-case value of  $\Delta Q_{\rm C_{dc},\rm pp}$  for unipolar PWM is obtained for  $\varphi = 0$  and  $M = 2/\sqrt{3}$ , as

$$\Delta Q_{\rm C_{dc},pp,max} = \frac{\sqrt{3}}{8} \, \Delta Q_{\rm n} \approx 0.216 \, \Delta Q_{\rm n}, \qquad (31)$$

whereas the worst-case  $\Delta Q_{\rm C_{dc, \rm PP}}$  value for unfolder PWM is found for  $\varphi = \pm \pi/2$  and  $M = 2/\sqrt{3}$  (i.e., as in the two-level inverter [26]), as

$$\Delta Q_{\rm C_{dc},pp,max} = \frac{1}{4} \,\Delta Q_{\rm n} = 0.25 \,\Delta Q_{\rm n}. \tag{32}$$

Comparing the two considered modulation strategies, it is observed that unipolar PWM requires a significantly higher DC-link RMS current capability (i.e.,  $\approx 80\%$  higher) with respect to unfolder PWM, meanwhile allowing for a slightly lower peak-to-peak charge ripple (i.e.,  $\approx 16\%$  lower). Therefore, when the DC-link capacitor sizing is limited by the RMS current capability (i.e., typical for film capacitors and/or for high-frequency operation), unfolder PWM can provide a substantial reduction in the overall DC-link capacitance requirement.

#### **IV. CONVERTER DESIGN**

In this section, the complete design of the converter is carried out, describing the selection of the semiconductor devices, the selection/sizing of the DC-link capacitors, the sizing of the thermal dissipation system and the estimation of the semiconductor losses and efficiency. Furthermore, a component disposition and PCB layout are proposed, leading to a three-phase full-GaN 100 kVA 400 V DBI design concept. The design specifications and the nominal operating conditions of the considered drive inverter are reported in Table I.

TABLE I. DBI SPECIFICATIONS AND NOMINAL OPERATING CONDITIONS.

| Parameter    | Description           | Value             |

|--------------|-----------------------|-------------------|

| S            | Apparent Power        | 100 kVA           |

| $V_{\rm dc}$ | DC-Link Voltage       | $400\mathrm{V}$   |

| Ι            | Peak Phase Current    | $167\mathrm{A}$   |

| f            | Fundamental Frequency | $1000\mathrm{Hz}$ |

#### A. Semiconductor Devices

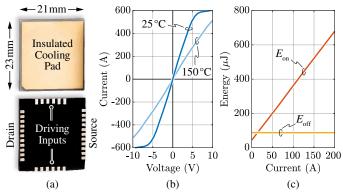

The most suitable semiconductor device for the application is identified by comparing the performance of all commercially available 600/650 V GaN devices and technologies, including e-mode HEMTs, cascode d-mode HEMTs and direct-drive dmode HEMTs [27]. The VisIC V08TC65S2A direct-drive dmode HEMT is selected due to its excellent conduction/switching performance trade-off, its absolute on-state resistance value (i.e.,  $7.8 \text{ m}\Omega$  at 25 °C) and its unparalleled cooling effectiveness (i.e., 0.1 K/w junction-to-case thermal resistance, further enhanced by an embedded electrically insulated cooling pad) [28]. An overview of the device package is provided in Fig. 9(a).

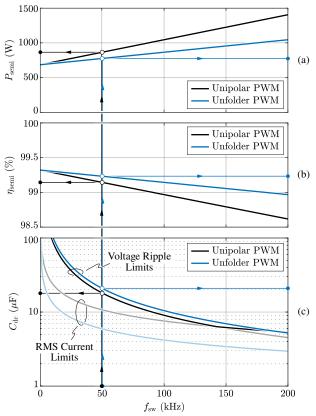

Leveraging the conduction and switching characteristics shown in Fig. 9(b)–(c), assuming a case-to-heatsink specific thermal resistance  $r_{\rm th,c-hs} = 70 \,\mathrm{mm^2 \, ^\circ C}/\mathrm{W}$  (cf. Section IV-C), and considering a typical cooling fluid (i.e.,  $\approx$  heatsink) temperature  $T_{\rm f} = 75 \,^{\circ}$ C, the DBI semiconductor loss and efficiency in nominal operating conditions are estimated as functions of the switching frequency using a coupled electro-thermal model (i.e.,  $R_{\rm ds,on}$  is temperature-dependent). The results are reported in Fig. 10(a)–(b).

Fig. 9. (a) top and bottom view of the selected VisIC V08TC65S2A directdrive d-mode HEMT [28], (b) conduction characteristics ( $R_{\rm ds,on} = 7.8 \,\mathrm{m\Omega}$  at 25 °C,  $R_{\rm ds,on} = 16 \,\mathrm{m\Omega}$  at 150 °C), and (c) switching energies ( $k_{0,\rm on} = 44.3 \,\mu$ J,  $k_{0,\rm off} = 86.5 \,\mu$ J,  $k_{1,\rm on} = 3.18 \,\mu$ J/A,  $k_{1,\rm off} \approx 0 \,\mu$ J/A).

Fig. 10. (a) semiconductor loss and (b) semiconductor efficiency for unipolar and unfolder PWM as functions of  $f_{\rm sw}$  in nominal operating conditions (i.e.,  $V_{\rm dc} = 400$  V, I = 167 A, M = 2) and assuming a cooling fluid temperature  $T_{\rm f} = 75$  °C. (c) DC-link capacitance  $C_{\rm dc}$  worst-case requirement as function of  $f_{\rm sw}$ . The selected design frequency is  $f_{\rm sw} = 50$  kHz.

#### B. DC-Link Capacitor

In typical three-phase drive inverter systems, the DC-link capacitor determines the converter size and weight and is thus a crucial component. To maximize the DBI performance, PLZT ceramic capacitor technology is considered, since it features high RMS current capability, high temperature operation, excellent volumetric/gravimetric capacitance density and improved characteristics with increased switching frequency [29], [30]. In particular, the CeraLink<sup>®</sup> LP series from TDK (i.e., 500 V  $0.6 \,\mu\text{F}$  capacitors [31]) is selected to size the DC-link capacitor according to the approach outlined in [30].

Fig. 10(b) shows the DC-link capacitance  $C_{\rm dc}$  worst-case requirement as function of  $f_{\rm sw}$ , either determined by the maximum peakto-peak voltage ripple (i.e.,  $\Delta V_{\rm pp,max} = 10\% \cdot V_{\rm dc} = 40$  V) or by the maximum RMS current carrying capability (i.e., assuming an ambient temperature of 85 °C) [30]. To best exploit the PCB space available for the placing of the capacitors (i.e., defined by the width of the semiconductor driving and power loops, cf. Section IV-E) and aiming to satisfy the capacitance requirement of both unipolar PWM and unfolder PWM,  $f_{\rm sw} = 50$  kHz is selected as design value, leading to excellent semiconductor efficiency in nominal operating conditions (i.e., 99.1 % for unipolar PWM, 99.2 % for unfolder PWM) and a total capacitance requirement  $C_{\rm dc} \geq 20.8 \,\mu\text{F}$  (i.e., determined by unfolder PWM). In worst-case conditions, the DC-link capacitor must withstand  $\approx 139$  A for unipolar PWM and  $\approx 77$  A for unfolder PWM.

#### C. Heatsink and Thermal Dissipation System

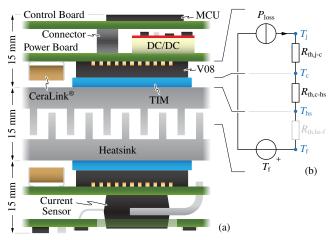

A schematic overview of the considered thermal dissipation system is reported in Fig. 11, where the two three-phase inverter

Fig. 11. (a) schematic cross-section of the proposed DBI design concept and (b) steady-state equivalent circuit of the thermal dissipation system. The heatsink-to-fluid thermal resistance  $R_{\rm th,hs-f}$  is greyed out since it can be neglected (i.e.,  $T_{\rm hs} \approx T_{\rm f}$ ).

units (cf. Section IV-E) are mechanically connected to the opposite sides of the liquid-cooled heatsink (i.e., to reduce the converter volume). Since the top surface of the VisIC V08TC65S2A is electrically insulated [28], a 2 mm-thick graphite-based thermal interface material (TIM) is used to thermally connect the semiconductor devices to the heatsink, achieving a case-to-heatsink thermal resistance  $R_{\rm th,c-hs} \approx 0.15 \,^{\circ}{\rm C/W}$  at  $\approx 100 \,{\rm kPa} \,(15 \,{\rm psi})$  of contact pressure (i.e., to be added to  $R_{\rm th,j-c} \approx 0.1 \,^{\circ}{\rm C/W}$ ). Furthermore, a high-performance 15 mm-thick pin-fin liquid cooled heatsink is considered, providing negligible temperature rise (i.e.,  $T_{\rm hs} \approx T_{\rm f}$ ) due to its excellent specific thermal performance (i.e.,  $< 100 \,{\rm mm}^2 \,^{\circ}{\rm C/W}$ ), the large available surface (i.e.,  $145 \, {\rm x} \, 80 \, {\rm mm}$ , cf. Section IV-E) and the relatively low semiconductor loss (i.e.,  $P_{\rm semi,max} \approx 865 \, {\rm W}$  for unipolar PWM, cf. Fig. 10(a)).

#### D. Performance Estimation

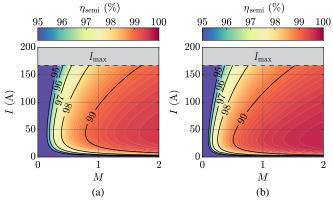

Since the semiconductor devices, the DC-link capacitors, the thermal dissipation system and the operating switching frequency have been defined, an estimation of the inverter semiconductor loss and efficiency is carried out. Fig. 12 shows the semiconductor efficiency of the designed DBI as function of the modulation index M and the AC-side peak phase current I for both unipolar PWM and unfolder PWM. As expected, unfolder PWM achieves the best performance, with an estimated peak efficiency of  $\approx 99.7\%$  at  $\approx 1/4$  of the rated current.

Fig. 12. Estimated semiconductor efficiency of the designed DBI as function of the modulation index M and the peak phase current I, assuming  $V_{\rm dc} = 400$  V,  $f_{\rm sw} = 50$  kHz and  $T_{\rm f} = 75$  °C for (a) unipolar PWM and (b) unfolder PWM.

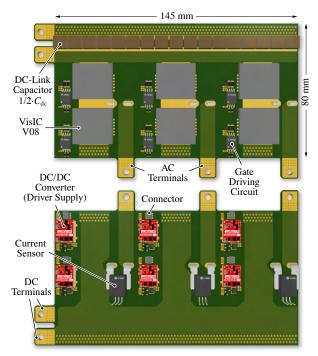

Fig. 13. Top and bottom view of one three-phase power board (i.e., first inverter unit) of the proposed full-GaN 400 V 100 kVA DBI design concept.

#### E. Design and Layout

The proposed DBI design concept consists of two separate threephase inverter units mechanically connected to the opposite sides of a common heatsink (cf. Fig. 11). The power board of the first inverter unit, which includes power semiconductors, capacitors, driving circuits and current sensors, is illustrated in Fig. 13. The PCB features 300 µm thick copper tracks to withstand the current stress in rated conditions and the DC-link capacitor (i.e.,  $C_{\rm dc}/2$ ) consists of 17 CeraLink<sup>®</sup> 500 V 0.6  $\mu$ F units (i.e.,  $C_{\rm dc} = 20.4\,\mu{\rm F}$ ). The power board of the second inverter unit (not shown in Fig. 13) does not include the current sensors and features the DC terminals on the opposite side, to ensure a compact DC-link connection between the two boards. To best exploit the available PCB area and minimize the converter height, only low-profile components are selected, obtaining a total height of  $\approx 45 \,\mathrm{mm}$  (i.e., including the thermal dissipation system and the control boards, cf. Fig. 11). Therefore the proposed DBI concept achieves a total volume of  $145 \times 80 \times 45 \text{ mm} \approx$  $0.52 \,\mathrm{dm^3}$  and an estimated volumetric power density of  $\approx 192 \,\mathrm{kVA/dm^3}$ .

#### V. CONCLUSION

This paper has proposed the analysis and the conceptualization of a full-GaN 100 kVA 400 V three-phase double bridge inverter (DBI) for next-generation EV drives. A comprehensive theoretical assessment of all active and passive component stresses has been carried out, providing useful tools for the converter sizing. Two modulation strategies have been compared, demonstrating a tradeoff among machine phase flux ripple, DC-link capacitor stress and semiconductor losses. While unipolar PWM ensures minimum PWMinduced losses and lower DC-link voltage ripple, unfolder PWM enables higher inverter efficiency and reduced DC-link RMS current. Remarkably, unfolder PWM also unlocks hybrid DBI implementations, i.e. adopting different (optimized) semiconductor technologies for the two three-phase inverter units. Finally, a DBI design concept has been developed, achieving an estimated 99.7 % peak semiconductor efficiency (unfolder PWM) and a 192 kVA/dm3 power density.

#### REFERENCES

- T. M. Jahns and H. Dai, "The Past, Present, and Future of Power Electronics Integration Technology in Motor Drives," *CPSS Transactions on Power Electronics* and Applications, vol. 2, no. 3, pp. 197–216, Sep. 2017. [1]

- J. Reimers, L. Dorn-Gomba, C. Mak, and A. Emadi, "Automotive Traction Inverters: Current Status and Future Trends," *IEEE Transactions on Vehicular Technology*, vol. 68, no. 4, pp. 3337–3350, Apr. 2019. [2]

- A. K. Morya et al., "Wide Bandgap Devices in AC Electric Drives: Opportunities [3] and Challenges," *IEE* pp. 3–20, Mar. 2019. " IEEE Transactions on Transportation Electrification, vol. 5, no. 1,

- D. Gerada *et al.*, "High-Speed Electrical Machines: Technologies, Trends, and Developments," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 6, pp. 2946–2959, Jun. 2014. [4]

- [5] F. Savi et al., "High-Speed Electric Drives: A Step Towards System Design," IEEE Open Journal of the Industrial Electronics Society, vol. 1, pp. 10-21, 2020.

- D. Cittanti et al., "PWM-Induced Losses in Electrical Machines: An Impedance-Based Estimation Method," in International Conference on Electrical Machines [6] and Systems (ICEMS), Oct. 2021, pp. 548-553.

- [7] D. Cittanti et al., "Comparative Evaluation of 800V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives," in International Conference on Electrical Machines and Systems (ICEMS), Nov. 2020, pp. 1699–1704.

- A. Poorfakhraei, M. Narimani, and A. Emadi, "A Review of Multilevel Inverter [8] Topologies in Electric Vehicles: Current Status and Future Trends," IEEE Open Journal of Power Electronics, pp. 155–170, 2021.

- J. W. Kolar *et al.*, "Application of WBG Power Devices in Future 3- $\Phi$  Variable Speed Drive Inverter Systems "How to Handle a Double-Edged Sword";" in 2020 IEEE International Electron Devices Meeting (IEDM), Dec. 2020, pp. 27.7.1– 27.7.4

- [10] J. Millán et al., "A Survey of Wide Bandgap Power Semiconductor Devices," IEEE Transactions on Power Electronics, vol. 29, no. 5, pp. 2155–2163, May 2014.

- [11] N. Keshmiri *et al.*, "Current Status and Future Trends of GaN HEMTs in Electrified Transportation," *IEEE Access*, vol. 8, pp. 70553–70571, 2020.

- R. Teichmann and S. Bernet, "A Comparison of Three-Level Converters versus Two-Level Converters for Low-Voltage Drives, Traction, and Utility Applications," [12] IEEE Transactions on Industry Applications, vol. 41, no. 3, pp. 855 -865, May 2005

- [13] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparative Evaluation of Advanced Three-Phase Three-Level Inverter/Converter Topologies Against Two-Level Sys-tems," IEEE Transactions on Industrial Electronics, vol. 60, no. 12, pp. 5515–5527, Dec. 2013.

- J. A. Anderson, G. Zulauf, J. W. Kolar, and G. Deboy, "New Figure-of-Merit Combining Semiconductor and Multi-Level Converter Properties," *IEEE Open Journal of Power Electronics*, vol. 1, pp. 322–338, 2020. [14]

- [15] M. Antivachis, D. Wu, D. Bortis, and J. W. Kolar, "Analysis of Double-Bridge Inverters for Drive Systems with Open-End Winding Motors," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 2020, (Early Access).

- Z. Huang et al., "Technical Review of Dual Inverter Topologies for More Electric Aircraft Applications," IEEE Transactions on Transportation Electrification, 2021, [16] (Early Access).

- [17] M. Valente, F. Iannuzzo, Y. Yang, and E. Gurpinar, "Performance Analysis of a Single-phase GaN-based 3L-ANPC Inverter for Photovoltaic Applications," in IEEE Southern Power Electronics Conference (SPEC), Dec. 2018

- [18] H. Li et al., "Design of a 10 kW GaN-Based High Power Density Three-Phase Inverter," in IEEE Energy Conversion Congress and Exposition (ECCE), Sep. 2016.

- Y. Lei et al., "A 2-kW Single-Phase Seven-Level Flying Capacitor Multilevel Inverter With an Active Energy Buffer," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8570–8581, Nov. 2017. [19]

- [20] T. Modeer et al., "Design of a GaN-Based Interleaved Nine-Level Flying Capacitor Multilevel Inverter for Electric Aircraft Applications,' IEEE Transactions on Power Electronics, vol. 35, no. 11, pp. 12153–12165, Nov. 2020.

- J. A. Anderson *et al.*, "Three Levels Are Not Enough: Scaling Laws for Multilevel Converters in AC/DC Applications," *IEEE Transactions on Power Electronics*, vol. 36, no. 4, pp. 3967–3986, Apr. 2021. [21]

- N. Pallo et al., "A 10-Level Flying Capacitor Multi-Level Dual-Interleaved Power [22] Module for Scalable and Power-Dense Electric Drives," in *IEEE Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2020, pp. 893–898.

- [23] D. Cittanti, E. Vico, E. Armando, and R. Bojoi, "Analysis and Conceptualization of a 800 V 100 kVA Full-GaN Three-Level Flying Capacitor Inverter for Next-Generation Electric Vehicle Drives," in *International Power Electronics Conference* (IPEC-ECCE Asia), May 2022.

- J. Kolar, H. Ertl, and F. C. Zach, "Calculation of the Passive and Active Component Stress of Three-Phase PWM Converter Systems with High Pulse Rate," in *European* [24] Conference on Power Electronics and Applications, vol. 3, Aachen, Germany, Oct. 1989, pp. 1303–1311.

- [25] D. Cittanti et al., "Analysis and Performance Evaluation of a Three-Phase Sparse Neutral Point Clamped Converter for Industrial Variable Speed Drives," *Electrical Engineering*, vol. 104, no. 2, pp. 623–642, Apr. 2022.

- M. Vujacic et al., "Analysis of DC-Link Voltage Switching Ripple in Three-Phase [26] PWM Inverters," Energies, vol. 11, no. 2, p. 471, Feb. 2018.

- [27] P. L. Brohlin, Y. K. Ramadass, and C. Kaya, "Direct-Drive Configuration for GaN Devices," Tech. Rep., 2018.

[28] VisIC Technologies, "V08TC65S2A," 2021.

- S. Chowdhury, E. Gurpinar, and B. Ozpineci, "High-Energy Density Capacitors for Electric Vehicle Traction Inverters," in *IEEE Transportation Electrification Conference Expo (ITEC)*, Jun. 2020, pp. 644–650. [29]

- [30] D. Cittanti et al., "Analysis and Design of a High Power Density Full-Ceramic 900 V DC-Link Capacitor for a 550 kVA Electric Vehicle Drive Inverter, International Power Electronics Conference (IPEC-ECCE Asia), May 2022.

- [31] TDK, "CeraLink<sup>®</sup> Low Profile (LP) Series," 2019.