# POLITECNICO DI TORINO Repository ISTITUZIONALE

| Original  2022 Roadmap on Neuromorphic Computing and Engineering / Christensen, Dennis Valbjørn; Dittmann, Regina; Linares-Barranco, Bernabe; Sebastian, Abu; Le Gallo, Manuel; Redaelli, Andrea; Slesazeck, Stefan; Mikolajick, Thomas; Spiga, Sabina; Menzel, Stephan; Valov, Ilia; Milano, Gianluca; Ricciardi, Carlo; Liang, Shi-Jun; Miao, Feng; Lanza, Mario; Quill, Tyler J.; Keene, Scott Tom; Salleo, Alberto; Grollier, Julie; Markovic, Danijela; Mizrahi, Alice; Yao, Peng; Yang, J. Joshua; Indiveri, Giacomo; Strachan, John Paul; Datta, Suman; Vianello, Elisa; Valentian, Alexandre; Feldmann, Johannes; Li, Xuan; Pernice, Wolfram HP; Bhaskaran, Harish; Furber, Steve; Neftci, Emre; Scherr, Franz; Walaso Wolfgang; Ramaswany, Srikanth; Japson, Jonathan; Panda, Priyadarshini; Kim, Youngeun; Tanaka, Gouhei; Thorpe, Simon, Balidoczi, Chiara; Cleland, Thomas Af, Posch, Christoph; Liu, Shih-Chii; Panuccio, Gabriella; Mahmud, Mutti; Mazumder, Arnab Neelim; Hosseini, Morteza; Mohsenin, Tinoosh; Donati, Elisa; Tolu, Silvia; Galeazzi, Roberto; Chilstensen, Martin Ejsing; Holm, Sune; Ielmini, Daniele; Pryds, Nini In: NEUROMORPHIC COMPUTING AND ENGINEERING: - ISSN 2634-4386 ELETTRONICO 2:(2022). [10.1088/2634-4386/ac4a83]  Published DOI:10.1088/2634-4386/ac4a83  Terms of use: |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Publisher copyright                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| (Article begins on next page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

#### **ACCEPTED MANUSCRIPT • OPEN ACCESS**

# 2022 roadmap on neuromorphic computing and engineering

To cite this article before publication: Dennis Valbjørn Christensen et al 2022 Neuromorph. Comput. Eng. in press <a href="https://doi.org/10.1088/2634-4386/ac4a83">https://doi.org/10.1088/2634-4386/ac4a83</a>

# Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2022 The Author(s). Published by IOP Publishing Ltd.

As the Version of Record of this article is going to be / has been published on a gold open access basis under a CC BY 3.0 licence, this Accepted Manuscript is available for reuse under a CC BY 3.0 licence immediately.

Everyone is permitted to use all or part of the original content in this article, provided that they adhere to all the terms of the licence <a href="https://creativecommons.org/licences/by/3.0">https://creativecommons.org/licences/by/3.0</a>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions may be required. All third party content is fully copyright protected and is not published on a gold open access basis under a CC BY licence, unless that is specifically stated in the figure caption in the Version of Record.

View the article online for updates and enhancements.

**IOP Publishing**

Journal: Neuromorphic Computing and Engineering

# 2022 Roadmap on Neuromorphic Computing and Engineering

Dennis V. Christensen¹, Regina Dittmann², Bernabé Linares-Barranco³, Abu Sebastian⁴, Manuel Le Gallo⁴, Andrea Redaelli⁵, Stefan Slesazeck⁶, Thomas Mikolajick⁶, Sabina Spiga՞, Stephan Menzelց, Ilia Valovց, Gianluca Milano¹o, Carlo Ricciardi¹¹, Shi-Jun Liang¹², Feng Miao¹², Mario Lanza¹³, Tyler J. Quill¹⁴, Scott T. Keene¹⁵, Alberto Salleo¹⁴, Julie Grollier¹⁶, Danijela Marković¹⁶, Alice Mizrahi¹⁶, Peng Yao¹⊓, J. Joshua Yang¹⊓, Giacomo Indiveri¹³, John Paul Strachan¹ョ, Suman Datta²o, Elisa Vianello²¹, Alexandre Valentian²², Johannes Feldmann²³, Xuan Li²³, Wolfram H.P. Pernice²⁴, Harish Bhaskaran²³, Steve Furber²⁶, Emre Neftci²⊓, Franz Scherr²³, Wolfgang Maass²³, Srikanth Ramaswamy²ョ, Jonathan Tapson³o, Priyadarshini Panda³¹, Youngeun Kim³¹, Gouhei Tanaka³², Simon Thorpe³³, Chiara Bartolozzi³⁴, Thomas A. Cleland³⁵, Christoph Posch³⁶, Shih-Chii Liu¹³, Gabriella Panuccio³¬, Mufti Mahmud³³, Arnab Neelim Mazumder³¬, Morteza Hosseini³¬, Tinoosh Mohsenin³¬, Elisa Donati¹³, Silvia Tolu⁴₀, Roberto Galeazzi⁴₀, Martin Ejsing Christensen⁴¹, Sune Holm⁴², Daniele Ielmini⁴³, and N. Pryds¹,⁴⁴.

<sup>&</sup>lt;sup>1</sup> Department of Energy Conversion and Storage, Technical University of Denmark, DK-2800 Kgs. Lyngby, Denmark

<sup>&</sup>lt;sup>2</sup> Peter Gruenberg Institute 7, Forschungszentrum Juelich GmbH, 52425 Juelich, Germany and JARA-FIT, RWTH Aachen University, 52056 Aachen, Germany

<sup>&</sup>lt;sup>3</sup> Instituto de Microelectrónica de Sevilla (IMSE-CNM), CSIC and Universidad de Sevilla, 41092 Seville, Spain

<sup>&</sup>lt;sup>4</sup> IBM Research – Zurich, Switzerland

<sup>&</sup>lt;sup>5</sup> STMicroelectronics, Agrate, Italy

<sup>&</sup>lt;sup>6</sup> NaMLab gGmbH, 01187 Dresden, Germany

<sup>&</sup>lt;sup>7</sup> Institute of Semiconductors and Microsystems, TU Dresden; Dresden, Germany

<sup>&</sup>lt;sup>8</sup> CNR-IMM, Unit of Agrate Brianza, via C. Olivetti 2, Agrate Brianza (MB), Italy

<sup>&</sup>lt;sup>9</sup> FZ Juelich (PGI-7), Juelich, Germany

<sup>10</sup> Advanced Materials Metrology and Life Science Division, INRIM (Istituto Nazionale di Ricerca Metrologica), Torino, Italy

$<sup>^{11}</sup>$  Department of Applied Science and Technology, Politecnico di Torino, Torino, Italy

<sup>&</sup>lt;sup>12</sup> National Laboratory of Solid State Microstructures, School of Physics, Collaborative Innovation Center of Advanced Microstructures, Nanjing University, Nanjing, China

<sup>&</sup>lt;sup>13</sup> Physical Sciences and Engineering Division, King Abdullah University of Science and Technology (KAUST), 23955-6900 Thuwal, Saudi Arabia.

<sup>&</sup>lt;sup>14</sup> Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305, United States of America

<sup>&</sup>lt;sup>15</sup> Department of Engineering, University of Cambridge, Cambridge CB2 1PZ, United Kingdom.

<sup>&</sup>lt;sup>16</sup> Unité Mixte de Physique, CNRS, Thales, Université Paris-Saclay, 91767 Palaiseau, France

<sup>&</sup>lt;sup>17</sup> Electrical and Computer Engineering Department, University of Southern California, Los Angeles, CA, USA

<sup>&</sup>lt;sup>18</sup> Institute of Neuroinformatics, University of Zurich and ETH Zurich, Switzerland

<sup>&</sup>lt;sup>19</sup> Hewlett Packard Laboratories, Hewlett Packard Enterprise, San Jose, CA, USA

<sup>&</sup>lt;sup>20</sup> Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN, USA

<sup>&</sup>lt;sup>21</sup> CEA, LETI, Université Grenoble Alpes, Grenoble, France

<sup>&</sup>lt;sup>22</sup> CEA, LIST, Université Grenoble Alpes, Grenoble, France

<sup>&</sup>lt;sup>23</sup> Department of Materials, University of Oxford, Parks Road, OX1 3PH Oxford, UK

<sup>&</sup>lt;sup>24</sup> Institute of Physics, University of Münster, Heisenbergstr. 11, 48149 Münster, Germany Heisenbergstr.

<sup>&</sup>lt;sup>25</sup> Center for Soft Nanoscience, University of Münster, 48149 Münster, Germany

<sup>&</sup>lt;sup>26</sup> The University of Manchester, UK

<sup>&</sup>lt;sup>27</sup> Department of Cognitive Sciences, University of California, Irvine, Irvine, CA, USA

<sup>&</sup>lt;sup>28</sup> Institute of Theoretical Computer Science, Graz University of Technology, Graz, Austria

<sup>&</sup>lt;sup>29</sup> École Polytechnique Fédérale de Lausanne, Geneva, Switzerland

<sup>&</sup>lt;sup>30</sup> School of Electrical and Data Engineering, University of Technology, Sydney, Australia

<sup>31</sup> Department of Electrical Engineering, New Haven, Yale University, USA

<sup>32</sup> International Research Center for Neurointelligence (IRCN), The University of Tokyo, 7-3-1 Hongo Bunkyo-ku, Tokyo 113-0033, Japan

<sup>&</sup>lt;sup>33</sup> CerCo, Université Toulouse 3, CNRS, CHU Purpan, Pavillon Baudot, 31059 Toulouse, France

<sup>&</sup>lt;sup>34</sup> Event Driven Perception for Robotics, Italian Institute of Technology, iCub Facility, Genoa, Italy

<sup>35</sup> Dept. of Psychology, Cornell University, Ithaca, NY, USA

<sup>&</sup>lt;sup>36</sup> Prophesee, Paris, France

<sup>&</sup>lt;sup>37</sup> Enhanced Regenerative Medicine, Istituto Italiano di Tecnologia, Italy

<sup>38</sup> Department of Computer Science and Medical Technologies Innovation Facility, Nottingham Trent University, UK

<sup>&</sup>lt;sup>39</sup> University of Maryland, Baltimore County, Catonsville, USA

<sup>&</sup>lt;sup>40</sup> Technical University of Denmark, Denmark

<sup>&</sup>lt;sup>41</sup> The Danish Council on Ethics, Denmark

<sup>&</sup>lt;sup>42</sup> Department of Food and Resource Economics, University of Copenhagen, Denmark

<sup>&</sup>lt;sup>43</sup> Politecnico di Milano, 20133 Milano, Italy

<sup>44</sup> Email: Nini Pryds, nipr@dtu.dk

#### **Abstract:**

Modern computation based on the von Neumann architecture is today a mature cutting-edge science. In the Von Neumann architecture, processing and memory units are implemented as separate blocks interchanging data intensively and continuously. This data transfer is responsible for a large part of the power consumption. The next generation computer technology is expected to solve problems at the exascale with 10<sup>18</sup> calculations each second. Even though these future computers will be incredibly powerful, if they are based on von Neumann type architectures, they will consume between 20 and 30 megawatts of power and will not have intrinsic physically built-in capabilities to learn or deal with complex data as our brain does. These needs can be addressed by neuromorphic computing systems which are inspired by the biological concepts of the human brain. This new generation of computers has the potential to be used for the storage and processing of large amounts of digital information with much lower power consumption than conventional processors. Among their potential future applications, an important niche is moving the control from data centers to edge devices.

The aim of this Roadmap is to present a snapshot of the present state of neuromorphic technology and provide an opinion on the challenges and opportunities that the future holds in the major areas of neuromorphic technology, namely materials, devices, neuromorphic circuits, neuromorphic algorithms, applications, and ethics. The Roadmap is a collection of perspectives where leading researchers in the neuromorphic community provide their own view about the current state and the future challenges for each research area. We hope that this Roadmap will be a useful resource by providing a concise yet comprehensive introduction to readers outside this field, for those who are just entering the field, as well as providing future perspectives for those who are well established in the neuromorphic computing community.

## **Contents:**

#### Introduction

#### Section 1 - Materials and devices:

- 1.1 Phase-change memory

- 1.2 Ferroelectric devices

- 1.3 Valence change memory

- 1.4 Electrochemical metallization cells

- 1.5 Nanowire networks

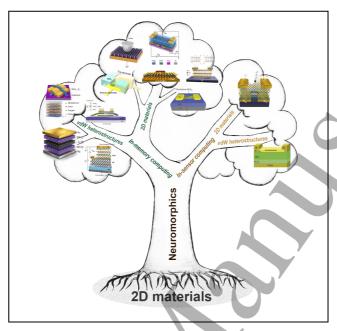

- 1.6 2D materials

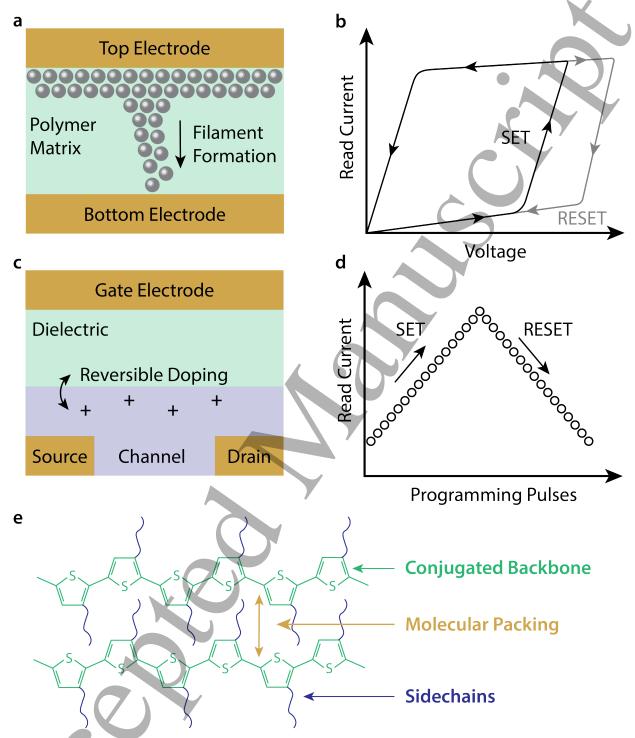

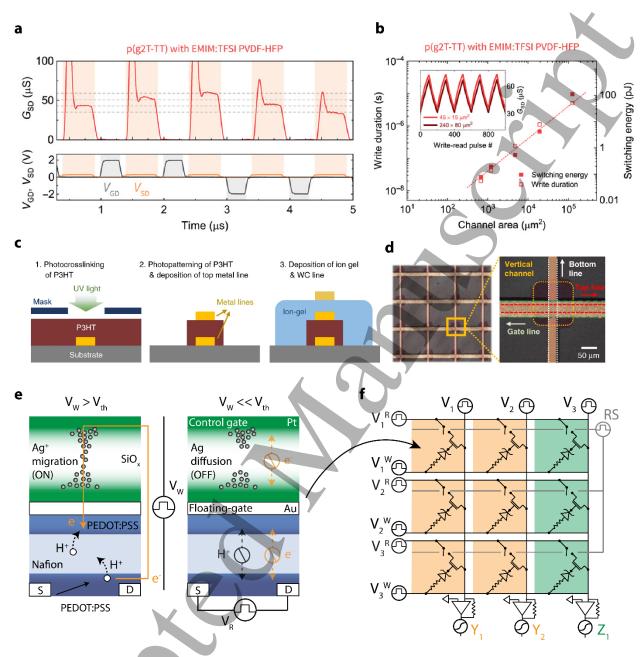

- 1.7 Organic materials

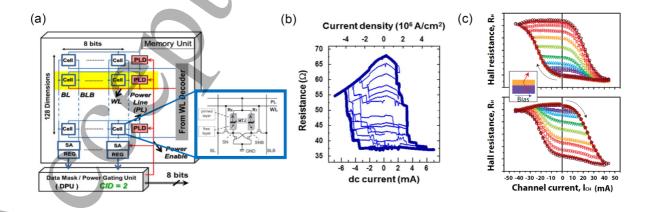

- 1.8 Spintronics

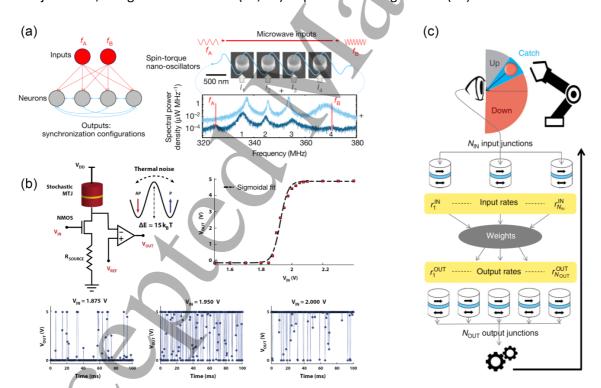

### Section 2 – Neuromorphic circuits:

- 2.1 Deep learning

- 2.2 Spiking neural networks

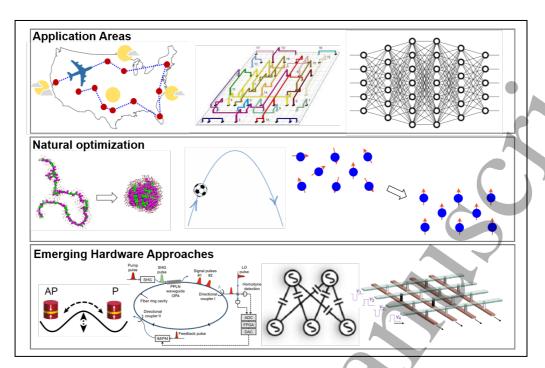

- 2.3 Emerging hardware approaches for optimization

- 2.4 Enabling technologies for the future heterogeneous neuromorphic accelerators

- 2.5 Photonics

- 2.6 Large-scale neuromorphic computing platforms

# **Section 3 – Neuromorphic Algorithms:**

- 3.1 Learning in spiking neural networks

- 3.2 Learning to learn in neuromorphic hardware

- 3.3 Computational neuroscience

- 3.4 Stochastic computing

- 3.5 Convolutional spiking neural networks

- 3.6 Reservoir computing

- 3.7 Computing with spikes

# Section 4 – Applications:

- 4.1 Robotics

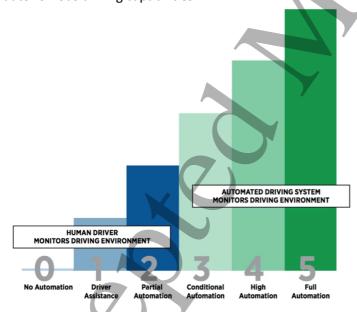

- 4.2 Self-driving cars

- 4.3 Olfaction and chemosensation

- 4.4 Event vision sensors

- 4.5 Neuromorphic audition

- 4.6 Biohybrid systems for brain repair

- 4.7 Embedded devices for neuromorphic time-series assessment

- 4.8 Electromyography processing using wearable neuromorphic technologies

- 4.9 Collaborative autonomous system

# Section 5 – Ethics:

5.1 – The ethics of developing neuromorphic technology

# Introduction

Computers have become essential to all aspects of modern life and are omnipresent all over the globe. Today, the recent data-intensive applications have placed a high demand on hardware performance, in terms of short access latency, high capacity, large bandwidth, low cost, and ability to execute artificial intelligence (AI) tasks. However, the ever-growing pressure for big data creates additional challenges: on the one hand, energy consumption has become a remarkable challenge, due to the rapid development of sophisticated algorithms and architectures. Currently, about 5–15% of the world's energy is spent in some form of data manipulation, such as transmission or processing<sup>1</sup>, and this fraction is expected to rapidly increase due to the exponential increase of data generated by ubiquitous sensors in the era of internet of things. On the other hand, data processing is increasingly limited by the memory bandwidth due to the Von-Neumann's architecture with physical separation between processing and memory units. While the Von Neumann computer architecture has made an incredible contribution to the world of science and technology for decades, its performance is largely inefficient due to the relatively slow and energy demanding data movement.

Conventional Von-Neumann computers based on complementary metal oxide semiconductor (CMOS) technology do not possess the intrinsic capabilities to learn or deal with complex data as the human brain does. To address the limits of digital computers, there are significant research efforts worldwide in developing profoundly different approaches inspired by biological principles. One of these approaches is the development of *neuromorphic systems*, namely computing systems mimicking the type of information processing in the human brain.

The term "neuromorphic" was originally coined in the 1990s by Carver Mead to refer to mixed signal analog/digital very large scale integration computing systems that take inspiration from the neuro-biological architectures of the brain<sup>2</sup>. "Neuromorphic engineering" emerged as an interdisciplinary research field that focused on building electronic neural processing systems to directly "emulate" the bio-physics of real neurons and synapses<sup>3</sup>. More recently, the definition of the term neuromorphic has been extended in two additional directions<sup>4</sup>. Firstly, the term neuromorphic was used to describe spike-based processing systems engineered to explore large-scale computational neuroscience models. Secondly, neuromorphic computing comprises dedicated electronic neural architectures that implement neuron and synapse circuits. Note that this concept is distinct from AI machine learning approaches which are based on pure software algorithms developed to minimize the recognition error in pattern recognition tasks<sup>5</sup>. However, a precise definition of neuromorphic computing is somewhat debated. It can range from very strict high-fidelity mimicking of neuroscience principles where very detailed synaptic chemical dynamics are mandatory, to very vague highlevel loosely brain-inspired principles, such as the simple vector (input) times matrix (synapses) multiplication. In general, as of today, there is a wide consensus that neuromorphic computing should at least encompass some time-, event-, or data-driven computation. In this sense, systems like spiking neural networks (SNN), sometimes referred to as the third generation of neural networks<sup>6</sup>, are strongly representative. However, there is an important cross-fertilization between the technologies required to develop efficient SNNs and those for more traditional non-spiking neural networks, referred to as artificial neural networks (ANN), which are typically more time-step-driven. While the former definition of neuromorphic computing is more plausible, in this Roadmap we aim at broadening the scope to emphasize the cross-fertilization between ANN and SNN.

Nature is a vital inspiration for the advancement to a more sustainable computing scenario, where neuromorphic systems display much lower power consumption than conventional processors, due to the integration of non-volatile memory and analog/digital processing circuits as well as the dynamic learning capabilities in the context of complex data. Building ANNs that mimic a biological counterpart is one of the remaining challenges in computing. If the fundamental technical issues are solved in the next few years, the neuromorphic computing market is projected to rise from \$0.2 billion in 2025 to \$22 billion in 2035<sup>7</sup> as

neuromorphic computers with ultra-low power consumption and high speed advance and drive demands for neuromorphic devices.

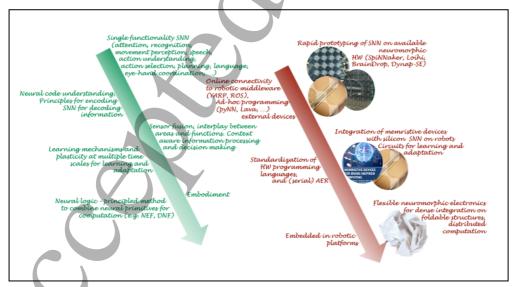

In line with these increasingly pressing issues, the general aim of the *Roadmap on Neuromorphic Computing* and *Engineering* is to provide an overview of the different fields of research and development that contribute to the advancement of the field, to assess the potential applications of neuromorphic technology in cutting edge technologies and to highlight the necessary advances required to reach these. The Roadmap addresses:

- Neuromorphic materials and devices

- Neuromorphic circuits

- Neuromorphic algorithms

- Applications

- Ethics

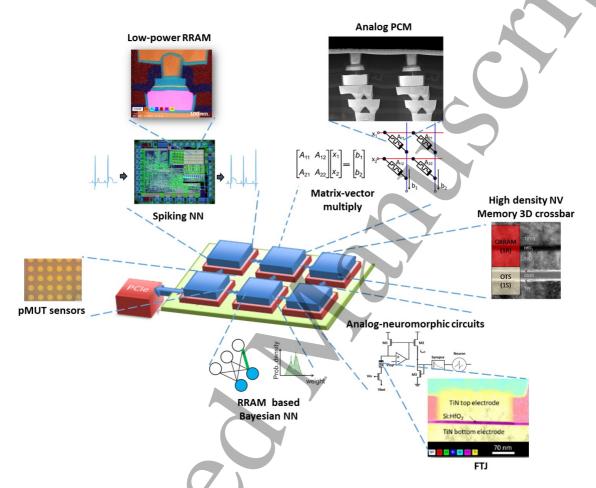

#### Neuromorphic materials and devices:

To advance the field of neuromorphic computing and engineering, the exploration of novel materials and devices will be of key relevance in order to improve the power efficiency and scalability of state-of-the-art CMOS solutions in a disruptive manner<sup>4,8</sup>. Memristive devices, which can change their conductance in response to electrical pulses<sup>9-11</sup>, are promising candidates to act as energy- and space-efficient hardware representation for synapses and neurons in neuromorphic circuits. Memristive devices have originally been proposed as binary non-volatile random-access memory and research in this field has been mainly driven by the search for higher performance in solid-state drive technologies (e.g., Flash replacement) or storage class memory<sup>12</sup>. However, thanks to their analog tunability and complex switching dynamics, memristive devices also enable novel computing functions such as analog computing or the realisation of brain-inspired learning rules. A large variety of different physical phenomena has been reported to exhibit memristive behaviour, including electronic effects, ionic effects as well as structural or ferroic ordering effects. The material classes range from magnetic alloys, metal oxides, chalcogenides to 2D van de Waals materials or organic materials. Within this Roadmap, we cover a broad range of materials and phenomena with different maturity levels with respect to their use in neuromorphic circuits. We consider emerging memory devices that are already commercially available as binary non-volatile memory such as phase-change memory, magnetic randomaccess memory, ferroelectric memory as well as redox-based resistive random-access memory and review their prospects for neuromorphic computing and engineering. We complement it with nanowire networks, 2D materials, and organic materials that are less mature but may offer extended functionalities and new opportunities for flexible electronics or 3D integration.

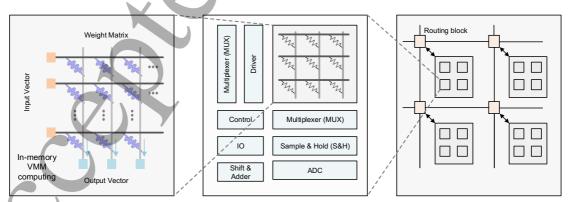

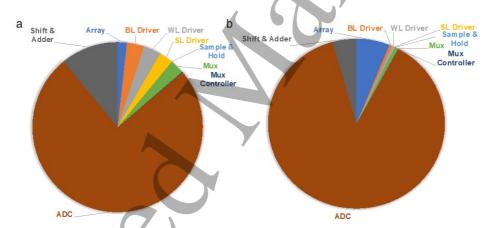

# Neuromorphic circuits:

Neuromorphic devices can be integrated with conventional CMOS transistors to develop fully functional neuromorphic circuits. A key element in neuromorphic circuits is their non-von Neumann architecture, for instance consisting of multiple cores each implementing distributed computing and memory. Both SSNs, adopting spikes to represent, exchange and compute data in analogy to action potentials in the brain, as well as circuits that are only loosely inspired by the brain, such as ANNs, are generally included in the roster of neuromorphic circuits, thus will be covered in this Roadmap. Regardless of the specific learning and processing algorithm, a key processing element in neuromorphic circuits is the neural network, including several synapses and neurons. Given the central role of the neural network, a significant research effort is currently aimed at technological solutions to realize dense, fast, and energy-efficient neural networks by inmemory computing<sup>13</sup>. For instance, a memory array can accelerate the matrix-vector multiplication (MVM)<sup>14</sup>. This is a common feature of many neuromorphic circuits, including spiking and non-spiking networks, and takes advantage of Ohm's and Kirchhoff's laws to implement multiplication and summation in the network. The MVM crosspoint circuit allows for the straightforward hardware implementation of synaptic layers with high density, high real-time processing speed, and high energy efficiency, although the accuracy is challenged

by stochastic variations in memristive devices in particular, and analog computing in general. An additional circuit challenge is the mixed analog-digital computation, which results in the need for large and energy-hungry analog-digital converter circuits at the interface between the analog crosspoint array and the digital system. Finally, neuromorphic circuits seem to take the most benefit from hybrid integration, combining front-end CMOS technology with novel memory devices that can implement MVM and neuro-biological functions, such as spike integration, short-term memory, and synaptic plasticity<sup>15</sup>. Hybrid integration may also need to extend, in the long term, to alternative nanotechnology concepts, such as bottom-up nanowire networks<sup>16</sup>, and alternative computing concepts, such as photonic<sup>17</sup> and even quantum computing<sup>18</sup>, within a single system or even a single chip with 3D integration. In this scenario, a Roadmap for the development and assessment of each of these individual innovative concepts is essential.

#### Neuromorphic algorithms:

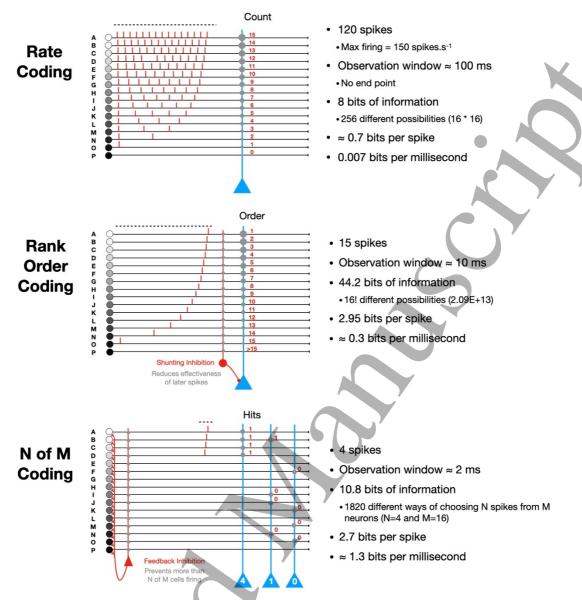

A fundamental challenge in neuromorphic engineering for real application systems is to train them directly in the spiking domain in order to be more energy-efficient, more precise, and also be able to continuously learn and update the knowledge on the portable devices themselves without relying on heavy cloud computing servers. Spiking data tend to be sparse with some stochasticity and embedded noise, interacting with non-ideal non-linear synapses and neurons. Biology knows how to use all this to its advantage to efficiently acquire knowledge from the surrounding environment. In this sense, computational neuroscience can be a key ingredient to inspire neuromorphic engineering, and learn from this discipline how brains perform computations at a variety of scales, from small neurons ensembles, mesoscale aggregations, up to full tissues, brain regions and the complete brain interacting with peripheral sensors and motor actuators. On the other hand, fundamental questions arise on how information is encoded in the brain using nervous spikes. Obviously, to maximize energy efficiency for both processing and communication, the brain maximizes information per unit spike<sup>19</sup>. This means unravelling the information encoding and processing by exploiting spatio-temporal signal processing to maximize information while minimizing energy, speed, and resources.

#### **Applications:**

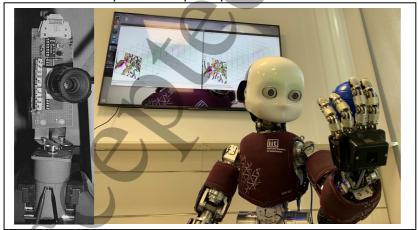

The realm of applications for neuromorphic computing and engineering continues to grow at a steady rate, although remaining within the boundaries of research and development. While it is becoming clear that many applications are well suited to neuromorphic computing and engineering, it is also important to identify new potential applications to further understand how neuromorphic materials and hardware can address them. The Roadmap includes some of these emerging applications as examples of biologically-inspired computing approaches for implementation in robots, autonomous transport capability or in perception engineering where the applications are based on integration with sensory modalities of humans.

#### Ethics:

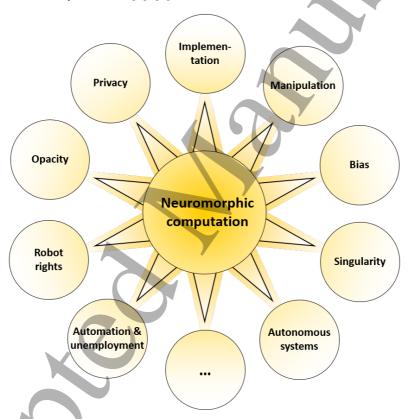

While the future development and application of neuromorphic systems offer possibilities beyond the state of the art, the progress should also be addressed from an ethical point of view where, e.g., lack of transparency in complex neuromorphic systems and autonomous decision making can be a concern. The Roadmap thus ends with a final section addressing some of the key ethical questions that may arise in the wake of advancements in neuromorphic computation.

We hope that this Roadmap represents an overview and updated picture of the current state-of-the-art as well as being the future projection in these exciting research areas. Each contribution, written by leading researchers in their topic, provides the current state of the field, the open challenges, and a future perspective. This should guide the expected transition towards efficient neuromorphic computations and highlight the opportunities for societal impact in multiple fields.

### **Acknowledgements**

D.V.C and N.P. acknowledge the funding from Villum Fonden, for the NEED project (00027993), Danish Council for Independent Research Technology and Production Sciences for the DFF Research Project 3 (Grant No. 00069B), the European Union's Horizon 2020, Future and Emerging Technologies (FET) programme (Grant No. 801267) and Danish Council for Independent Research Technology and Production Sciences for the DFF- Research Project 2 (Grant No. 48293). R.D. acknowledges funding from the German Science foundation within the SFB 917 "Nanoswitches", by the Helmholtz Association Initiative and Networking Fund under project number SO-092 (Advanced Computing Architectures, ACA) and the Federal Ministry of Education and Research (project NEUROTEC grant no. 16ES1133K). B.L.B. acknowledges funding from the European Union's Horizon 2020 (grants 824164, 871371, 871501, and 899559). D.I. acknowledges funding from the European Union's Horizon 2020 (grants 824164, 899559 and 101007321).

Nini Pryds, Professor, Technical University of Denmark

Dennis Valbjørn Christensen, Scientist, Technical University of Denmark

Bernabe Linares-Barranco, Professor, Sevilla Microelectronics Institute, CSIC

Daniele Ielmini, Professor, Politecnico di Milano

Regina Dittmann, Professor, Forschungszentrum Jülich

#### References

- 1. Vidal, J. 'Tsunami of data' could consume one fifth of global electricity by 2025. Climate Home News (2017).

- 2. Mead, C. Neuromorphic electronic systems. *Proc. IEEE* 78, 1629–1636 (1990).

- 3. Chicca, E., Stefanini, F., Bartolozzi, C. & Indiveri, G. Neuromorphic Electronic Circuits for Building Autonomous Cognitive Systems. *Proc. IEEE* **102**, 1367–1388 (2014).

- 4. Chicca, E. & Indiveri, G. A recipe for creating ideal hybrid memristive-CMOS neuromorphic processing systems. *Appl. Phys. Lett.* **116**, 120501 (2020).

- 5. LeCun, Y., Bengio, Y. & Hinton, G. Deep learning. Nature **521**, 436–444 (2015).

- 6. Maass, W. Networks of spiking neurons: The third generation of neural network models. *Neural Networks* **10**, 1659–1671 (1997).

- 7. Neuromorphic computing and sensing 2021. Yole Report 2021 www.yole.fr.

- 8. Zidan, M. A., Strachan, J. P. & Lu, W. D. The future of electronics based on memristive systems. *Nat Electron* **1**, 22–29 (2018).

- 9. Chua, L. Memristor-The missing circuit element. IEEE Trans. Circuit Theory 18, 507-519 (1971).

- 10. Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. *Nature* **453**, 80–83 (2008).

- 11. Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. *Nature Nanotech* 8, 13–24 (2013).

- 12. Dittmann, R. & Strachan, J. P. Redox-based memristive devices for new computing paradigm. *APL Materials* **7**, 110903 (2019).

- 13. Ielmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. Nat Electron 1, 333–343 (2018).

- 14.Li, C. et al. Analogue signal and image processing with large memristor crossbars. Nat Electron 1, 52-59 (2018).

- 15. Ielmini, D., Wang, Z. & Liu, Y. Brain-inspired computing via memory device physics. APL Materials 9, 050702 (2021).

- 16. Milano, G. *et al.* Brain-Inspired Structural Plasticity through Reweighting and Rewiring in Multi-Terminal Self-Organizing Memristive Nanowire Networks. *Advanced Intelligent Systems* **2**, 2000096 (2020).

- 17. Shastri, B. J. et al. Photonics for artificial intelligence and neuromorphic computing. *Nat. Photonics* **15**, 102–114 (2021).

- 18. Marković, D. & Grollier, J. Quantum neuromorphic computing. Appl. Phys. Lett. 117, 150501 (2020).

- 19. Thorpe, S., Fize, D. & Marlot, C. Speed of processing in the human visual system. 381, 3 (1996).

Roadmap on Neuromorphic Computing and Engineering

# 1.1 Phase-change memory devices

Abu Sebastian, IBM Research – Zurich, Switzerland Manuel Le Gallo, IBM Research – Zurich, Switzerland Andrea Redaelli, ST Microelectronics, Agrate, Italy

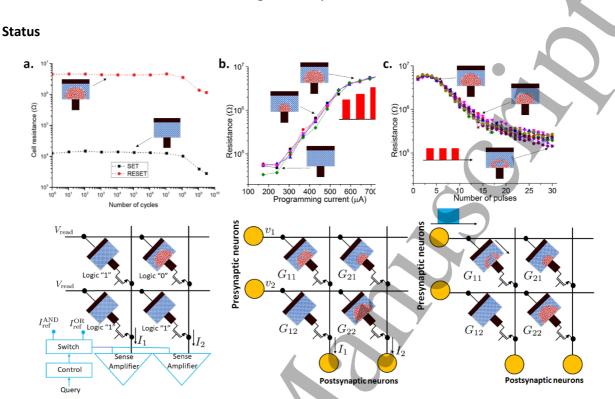

Figure 1. Key physical attributes that enable neuromorphic computing. a. Non-volatile binary storage facilitates in-memory logical operations relevant for applications such as hyper-dimensional computing. b. Analog storage enables efficient matrix-vector multiply operations that are key to applications such as deep neural network inference. c. The accumulative behaviour facilitates applications such as deep neural network training and emulation of neuronal and synaptic dynamics in spiking neural networks.

Phase-change memory (PCM) exploits the behaviour of certain phase-change materials, typically compounds of Ge, Sb and Te, that can be switched reversibly between amorphous and crystalline phases of different electrical resistivity [1]. A PCM device consists of a certain nanometric volume of such phase change material sandwiched between two electrodes.

In recent years, PCM devices are being explored for brain-inspired or neuromorphic computing mostly by exploiting the physical attributes of these devices to perform certain associated computational primitives in-place in the memory itself [2,3]. One of the key properties of PCM that enables such inmemory computing (IMC) is simply the ability to store two levels of resistance/conductance values in a non-volatile manner and to reversibly switch from one level to the other (binary storage capability). This property facilitates in-memory logical operations enabled through the interaction between the voltage and resistance state variables [3]. Applications of in-memory logic include database query [4] and hyper-dimensional computing [5].

Another key property of PCM that enables IMC is its ability to achieve not just two levels but a continuum of resistance values (analogue storage capability) [1]. This is typically achieved by creating intermediate phase configurations through the application of partial RESET pulses. The analogue storage capability facilitates the realization of matrix-vector multiply (MVM) operations in O(1) time complexity by exploiting Kirchhoff's circuit laws. The most prominent application for this is

deep neural network (DNN) inference [6]. It is possible to map each synaptic layer of a DNN to a crossbar array of PCM devices. There is a widening industrial interest in this application owing to the promise of significantly improved latency and energy consumption with respect to existing solutions. This in-memory MVM operations also enable non-neuromorphic applications such as linear-solvers and compressed sensing recovery [3].

The third key property that enables IMC is the accumulative property arising from the crystallization kinetics. This property can be utilized to implement DNN training [7,8]. It is also the central property that is exploited for realizing local learning rules like spike-timing-dependent plasticity in spiking neural networks [9,10]. In both cases, the accumulative property is exploited to implement the synaptic weight update in an efficient manner. It has also been exploited to emulate neuronal dynamics [11].

Note that, PCM is at a very high maturity level of development with products already on the market and a well-established roadmap for scaling. This fact, together with the ease of embedding PCM on logic platforms (embedded PCM) [12] make this technology of unique interest for neuromorphic computing and IMC in general.

### **Current and Future Challenges**

Figure 2. Key challenges associated with PCM devices a. The SET/RESET conductance values exhibit broad distributions which is detrimental for applications such as in-memory logic. b. The drift and noise associated with analogue conductance values results in imprecise matrix-vector multiply operations. c. The nonlinear and stochastic accumulative behaviour result in imprecise synaptic weight updates.

PCM devices have several attractive properties such as the ability to operate them at timescales on the order of tens of nanoseconds. The cycling endurance is orders of magnitude higher for PCM compared to other non-volatile memory devices such as Flash memory. The retention time can also be tuned relatively easily with the appropriate choice of materials, although the retention time associated with the intermediate phase configurations could be substantially lower than that of the full amorphous state.

However, there are also several device-level challenges as shown in Figure 2. One of the key challenges associated with the use of PCM for in-memory logic operations is the wide distribution of the SET states. These distributions could detrimentally impact the evaluation of logical operations. The central challenge associated with in-memory MVM operations is the limited precision arising from the 1/f noise as well as conductance drift. Drift is attributed to the structural relaxation of the melt-quenched amorphous phase [13]. Temperature-induced conductance variations could also pose challenges. One additional challenge is related to the stoichiometric stability during cycling where ion migration effects can occur [14]. Moreover, the accumulative behaviour in PCM is highly nonlinear and stochastic. While one could exploit this intrinsic stochasticity to realize stochastically firing neurons and for stochastic

computing, this behaviour is detrimental for applications such as DNN training in which the conductance must be precisely modulated.

PCM-based IMC has the potential for ultra-high compute density since PCM devices can be scaled to nanoscale dimensions. However, it is not straightforward to fabricate such devices in a large array due to fabrication challenges such as etch damage and deposition of materials in high-aspect ratio pores [15]. The integration density is also limited by the access device, which could be a selector in the backend-of-the-line (BEOL) or front-end bipolar junction transistors (BJT) or Metal-Oxide-Semiconductor Field Effect Transistors (MOSFET). The threshold voltage must be overcome when SET operations are performed, so the access device must be able to manage voltages at least as high as the threshold voltage. While MOSFET selector size is mainly determined by the PCM RESET current, the BJT and BEOL selectors can guarantee a minimum cell size of 4F², leading to very high density [16]. However, BEOL selector-based arrays have some drawbacks in terms of precise current control, while the management of parasitic drops is more complex for BJT-based arrays [17].

### **Advances in Science and Technology to Meet Challenges**

A promising solution towards addressing the PCM nonidealities such as 1/f noise and drift is that of projected phase-change memory (Projected PCM) [18, 19]. In these devices, there is a non-insulating projection segment in parallel to the phase-change material segment. By exploiting the highly non-linear I-V characteristics of phase-change materials, one could ensure that during the SET/RESET process, the projection segment has minor impact on the operation of the device. An increase in the reset current is anyway expected and some work should be done on material engineering side to compensate for that. However, during read, the device conductance is mostly determined by the projection segment that appears parallel to the amorphous phase-change segment. Recently, it was shown that it is possible to achieve remarkably high precision in-memory scalar multiplication (equivalent to 8-bit fixed point arithmetic) using projected PCM devices [20]. These projected PCM devices also facilitate array-level temperature compensation schemes. Alternate multi-layered PCM devices have also been proposed that exhibit substantially lower drift [21].

There is a perennial focus on trying to reduce the RESET current via scaling the switchable volume of the PCM device. Either by shrinking the overall dimension of the device in a confined geometry or by scaling the bottom electrode dimensions of a mushroom-type device. The exploration of new material classes such as single elemental Antimony could help with the scaling challenge [22].

The limited endurance and various other non-idealities associated with the accumulative behaviour such as limited dynamic range, nonlinearity and stochasticity can be partially circumvented with multi-PCM synaptic architectures. Recently, a multi-PCM synaptic architecture was proposed that employs an efficient counter-based arbitration scheme [23]. However, to improve the accumulation behaviour at the device level, more research is required on the effect of device geometries as well as the randomness associated with crystal growth.

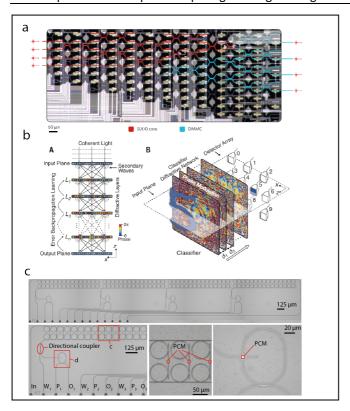

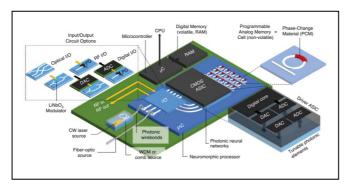

Besides conventional electrical PCM devices, photonic memory devices based on phase-change materials, which can be written, erased, and accessed optically, are rapidly bridging a gap towards all-photonic chip-scale information processing. By integrating phase-change materials onto an integrated photonics chip, the analogue multiplication of an incoming optical signal by a scalar value encoded in

the state of the phase change material was achieved [24]. It was also shown that by exploiting wavelength division multiplexing, it is possible to perform convolution operations in a single time step [25]. This creates opportunities to design phase-change materials that undergo faster phase transitions and have a higher optical contrast between the crystalline and amorphous phases [26].

# **Concluding Remarks**

The non-volatile binary storage, analogue storage and accumulative behaviour associated with PCM devices can be exploited to perform in-memory computing. Compared to other non-volatile memory technologies, the key advantages of PCM are the well understood device physics, volumetric switching and easy embeddability in a CMOS platform. However, there are several device and fabrication-level challenges that need be overcome to enable PCM-based IMC and this is an active area of research.

It will also be rather interesting to see how PCM-based neuromorphic computing will eventually be commercialized. Prior to true IMC, a hybrid architecture where PCM memory chips are used to store synaptic weights in a non-volatile manner while the computing is performed in a stacked logic chip is likely to be considered as an option by the industry. Despite the tight interconnect between the stacked chips, data transfer will remain a bottleneck for this approach. A better solution could be PCM directly embedded with the logic itself (BEOL) without any interconnect bottleneck and eventually we could foresee full-fledged non-von Neumann accelerator chips where the embedded PCM is also used for analogue in-memory computing.

#### **Acknowledgements**

This work was supported in part by the European Research Council through the European Union's Horizon 2020 Research and Innovation Programme under grant no. 682675.

#### References

- 1. M. Le Gallo and A. Sebastian, "An overview of phase-change memory device physics," Journal of Physics D: Applied Physics, vol. 53, no 21, p. 213002, 2020.

- 2. D. Ielmini and H.-S. P. Wong, "In-memory computing with resistive switching devices", Nature Electronics, 1, pp. 333-343, 2018.

- 3. A. Sebastian, M. Le Gallo, R. Khaddam-Aljameh, E. Eleftheriou, "Memory devices and applications for in-memory computing", Nature Nanotechnology, 15, pp. 529-544, 2020.

- 4. I. Giannopoulos, A. Singh, M. Le Gallo, V. P. Jonnalagadda, S. Hamdioui and A. Sebastian, "In-Memory Database Query," Advanced Intelligent Systems, Vol. 2, no. 12, p. 2000141, 2020.

- 5. G. Karunaratne, M. Le Gallo, G. Cherubini, L. Benini, A. Rahimi and A. Sebastian, "In-memory hyperdimensional computing," Nature Electronics, Vol. 3, pp. 327–337, 2020.

- 6. V. Joshi, M. Le Gallo, S. Haefeli, et al. "Accurate deep neural network inference using computational phase-change memory," Nature Communications, Vol. 11, no. 2473, 2020.

- 7. H. Tsai, S. Ambrogio et al., "Recent progress in analog memory-based accelerators for deep learning", J. Phys. D: Appl. Phys., 51(28), 2018.

- 8. S. R. Nandakumar, M. Le Gallo, C. Piveteau, et al. "Mixed-precision deep learning based on computational memory," Frontiers in Neuroscience, vol. 14, p. 406, 2020.

- 9. A. Sebastian, M. Le Gallo, G. Burr et al., "Brain-inspired computing using phase-change memory devices", J. Appl. Phys., 124(11), pp. 111101, 2018.

- 10. S. Ambrogio, N. Ciocchini, M. Laudato, V. Milo, A. Pirovano, P. Fantini, and D. Ielmini, "Unsupervised learning by spike timing dependent plasticity in phase change memory (PCM) synapses," Frontiers in neuroscience, Vol. 10, p. 56, 2016.

- 11. T. Tuma, A. Pantazi, M. Le Gallo, et al. "Stochastic phase-change neurons," Nature Nanotechnology, vol. 11, no 8, p. 693, 2016.

- 12. P. Zuliani, A. Conte and P. Cappelletti, "The PCM way for embedded Non Volatile Memories applications," 2019 Symposium on VLSI Technology, pp. T192-T193, 2019.

- 13. M. Boniardi, D. Ielmini, S. Lavizzari, A. L. Lacaita, A. Redaelli and A. Pirovano, "Statistics of Resistance Drift Due to Structural Relaxation in Phase-Change Memory Arrays," in IEEE Transactions on Electron Devices, vol. 57, no. 10, pp. 2690-2696, 2010.

- 14. L. Crespi et al., "Modeling of Atomic Migration Phenomena in Phase Change Memory Devices," 2015 IEEE International Memory Workshop (IMW), pp. 1-4, 2015.

- 15. M. BrightSky et al., "Crystalline-as-deposited ALD phase change material confined PCM cell for high density storage class memory," 2015 IEEE International Electron Devices Meeting (IEDM), pp. 3.6.1-3.6.4, 2015.

- 16. D. Kau et al., "A stackable cross point phase change memory", 2009 IEEE International Electron Devices Meeting (IEDM), pp. 27.1.1-27.1.4, 2009.

- 17. F. Arnaud et al., High density embedded PCM cell in 28nm FDSOI technology for automotive micro-controller applications, 2020 IEEE International Electron Devices Meeting (IEDM), pp. 24.2.1-24.2.4, 2020

- 18. A. Redaelli, F. Pellizer and A. Pirovano, "Phase change memory device for multibit storage", EP Patent 2,034,536, 2012

- 19. W. W. Koelmans, A. Sebastian, V. P. Jonnalagadda, D. Krebs, L. Dellmann and E. Eleftheriou, "Projected phase-change memory devices", Nature Communications, vol. 6, no. 8181, 2015

- 20. I. Giannopoulos et al., "8-bit Precision In-Memory Multiplication with Projected Phase-Change Memory," 2018 IEEE International Electron Devices Meeting (IEDM), pp. 27.7.1-27.7.4, 2018.

- 21. K. Ding, J. Wang, Y. Zhou, et al. "Phase-change heterostructure enables ultralow noise and drift for memory operation," Science, vol. 366, no 6462, p. 210-215, 2019.

- 22. M. Salinga, B. Kersting, I. Ronneberger, et al. "Monatomic phase change memory," Nature Materials, Vol. 17, pp. 681–685, 2018.

- 23. I. Boybat, M. Le Gallo, S. R. Nandakumar, et al. "Neuromorphic computing with multimemristive synapses," Nature Communications, Vol. 9, no. 2514, 2018.

- 24. C. Rios, N. Youngblood, Z. Cheng, M. Le Gallo, W. H. Pernice, C. D. Wright, A. Sebastian, H. Bhaskaran, "In-memory computing on a photonic platform", Science Advances, 2019

- 25. J. Feldmann, N. Youngblood, M. Karpov, et al. "Parallel convolutional processing using an integrated photonic tensor core," Nature, Vol. 589, pp. 52–58, 2021.

- 26. Z. Cheng, T. Milne, P. Salter, J. S. Kim, S. Humphrey, M. Booth and H. Bhaskaran, "Antimony thin films demonstrate programmable optical nonlinearity", Science Advances, 2021

### 1.2 – Ferroelectric Devices

Dr.-Ing. Stefan Slesazeck<sup>1</sup>, Prof. Dr.-Ing. Thomas Mikolajick<sup>1,2</sup>

<sup>1</sup> NaMLab gGmbH; <sup>2</sup> Institute of Semiconductors and Microsystems, TU Dresden; Dresden, Germany

#### **Status**

Ferroelectricity was firstly discovered in 1920 by Valasek in Rochelle salt [1] and describes the ability of a non-centrosymmetric crystalline material to exhibit a permanent and switchable electrical polarization due to the formation of stable electric dipoles. Historically, the term ferroelectricity stems from the analogous behavior with the magnetization hysteresis of ferromagnets when plotting the ferroelectric polarization versus the electrical field. Regions of opposing polarization are called domains. The polarization direction of such domains can be switched typically by 180° but based on the crystal structure also other angles are possible. Since the discovery of the stable ferroelectric barium titanate (BTO) in 1943 ferroelectrics found application in capacitors in electronics industry. Already in the 1950s ferroelectric capacitor (FeCAP) based memories (FeRAM) have been proposed [2], where the information is stored as polarization state of the ferroelectric material. Read and write operation are performed by applying an electric field larger than the coercive field  $E_C$ . The destructive read operation determines the switching current of the FeCAP upon polarization reversal, thus requiring a write-back operation after readout. Thanks to the development of mature processing techniques for ferroelectric lead zirconium tantalate (PZT) FeRAMs are commercially available since the early 1990s [3]. However, the need for a sufficiently large capacitor together with the limited thin-film manufacturability of the perovskite materials so far restricted their use to niche applications [4].

The ferroelectric field effect transistors (FeFET) that was proposed in 1957 [5] features a ferroelectric capacitor as gate insulator, modulating the transistor's threshold voltage that can be sensed non-destructively by measuring the drain-source current. Perovskite based FeFET memory arrays with up to 64kBit have been demonstrated [6]. But due to difficulties in the technological implementation, limited scalability and data retention issues, no commercial devices became available.

The ferroelectric tunneling junction (FTJ) was proposed by L. Esaki et al. in 1970s as a "polar switch" [7] and was firstly demonstrated in 2009 using a BaTiO3 ferroelectric layer [8]. The FTJ features a ferroelectric layer sandwiched between two electrodes, thus modifying the tunneling electro-resistance. A polarization-dependent current is measured non-destructively when applying electrical fields smaller than  $E_C$ .

Since the fortuitous discovery of ferroelectricity in hafnium oxide (HfO<sub>2</sub>) in 2008 and its first publication in 2011 [9] the well-established and CMOS-compatible fluorite-structure material has been extensively studied and recently gained a lot of interest in the field of nonvolatile memories and beyond von-Neumann computing [10] [11].

### Roadmap on Neuromorphic Computing and Engineering

**Figure 1.** The center shows two typical ferroelectric crystals and the corresponding PV-hysteresis curve. The top figure illustrates a FeCAP based FeRAM, the figure on the bottom left shows a FeFET and the bottom right an FTJ.

# **Current and Future Challenges**

Very encouraging electrical results of fully front-end-of-line (FEOL) integrated FeFET devices featuring switching speeds <50ns at <5V pulse voltage have been reported recently based on >1Mbit memory arrays [12]. The ability of fine-grained co-integration of FeFET memory devices together with CMOS logic transistors paves the way for the realization of brain-inspired architectures to overcome the limitations of the van-Neumann bottleneck, which restricts the data transfer due to limited memory and data bus bandwidth [13]. However, one of the main challenges for the FeFET devices and topic of intense research is the formation of ferroelectric HfO<sub>2</sub>-based thin films featuring a uniform polarization behavior at nano-scale as an important prerequisite for the realization of small scaled devices with feature sizes <100nm.

Another important challenge for many application cases is the limited cycling endurance of silicon-based FeFETs that is typically in the range of  $10^5$  cycles. This value is mainly dictated by the breakdown of the dielectric  $SiO_2$  interfacial layer that forms between the Si channel and the ferroelectric gate insulator.

Ferroelectric capacitors have been successfully integrated into the back-end-of-line (BEOL) of modern CMOS technologies and operation of a  $HfO_2$ -based based FeRAM memory array at 2.5V and 14ns switching pulses was successfully demonstrated [14]. At this point the main challenge is the decrease of the ferroelectric layer thickness well below 10nm to allow scaling of 3D capacitors towards the 10nm node. Moreover, phenomenon such as the so called "wake-up effect" with increasing of  $P_r$  for low cycle counts as well as the "fatigue effect" resulting in a reduction of  $P_r$  at high cycle counts due to oxygen vacancy redistribution [15] and defect generation have to be tackled. That is especially important for fine-grained circuit implementations where the switching properties of single ferroelectric devices impact the designed operation point of analogue circuits.

### Roadmap on Neuromorphic Computing and Engineering

One of the most interesting benefits of FTJ devices is the small current density making them very attractive for applications requiring massive parallel operations such as analogue matrix-vector-multiplications in larger cross-bar structures [16]. However, increasing the ratio between the on-current density and the self-capacitance of the FTJ devices turns out as one of the main challenges to increase the reading speed for these devices. The tunneling current densities depend strongly on the thickness of the ferroelectric layer and the composition of the multi-layer stacks. The formation of very thin ferroelectric layers is hindered by unintentional formation of interfacial dead layers towards the electrodes and increasing leakage currents due to defects and grain-boundaries in the poly-crystalline thin films.

# **Advances in Science and Technology to Meet Challenges**

Although ferroelectricity in hafnium oxide has been extensively studied for over one decade now, there are still many open questions in understanding the formation of the ferroelectric  $Pca2_1$  phase and regarding the interaction with material layers such as electrodes, dielectric tunneling barriers in multi-layer FTJs or interfacial layers in FeFETs. Moreover, the interplay between charge trapping phenomenon and ferroelectric switching mechanisms [17], the trade-off between switching speed and voltage of the nucleation limited switching and its impact on device reliability or the different behavior of abrupt single domain switching [11] and smooth polarization transitions in negative capacitance devices that were observed in the very similar material stacks are still not completely understood. However, that knowledge will be an important ingredient for proper optimization of material stacks as well as electrical device operation conditions.

On the materials side the stabilization of the ferroelectric orthorhombic Pca21 phase in crystallized HfO2 thin films has to be optimized further. Adding dopants, changing oxygen vacancy densities or inducing stress by suitable material stack and electrode engineering are typical measures. In most cases a poly-crystalline material layer is attained consisting of a mixture of different crystalline ferroelectric and non-ferroelectric phase fractions. Moreover, ferroelectric grains that differ in size or orientation of the polarization axis, electronically active defects as well as grain size dependent surface energy effects give rise to the formation of ferroelectric domains that possess different electrical properties in terms of coercive field  $E_c$  (typical values ~1 MV/cm) or remnant polarization  $P_r$  (typical values 10 – 40  $\mu$ C/cm<sup>2</sup>) with impact on the device-to-device variability and the gradual switching properties that are important especially for analog synaptic devices. Some drawbacks of the poly-crystallinity of ferroelectric HfO<sub>2</sub>- and ZrO<sub>2</sub>-based thin films could be tackled by the development of epitaxial growth of monocrystalline ferroelectric layers [18] where domains might extend over a larger area. Especially in the case of FTJs the effect of domain wall motion might allow a more gradual and analogue switching behavior even in small scaled devices. The utilization of an anti-ferroelectric hysteretic switching that was demonstrated in ZrO2 thin films bears the potential to overcome some limitations that are related to the high coercive field of ferroelectric HfO<sub>2</sub>, such as operation voltages being larger than the typical core voltages in modern CMOS technologies or the limited cycling endurance [19].

Finally, besides the very encouraging results adopting ferroelectric HfO<sub>2</sub> in 2019 another promising material was realized. The AlScN is a semiconductor processing compatible and already utilized piezoelectric material that was made ferroelectric [20].

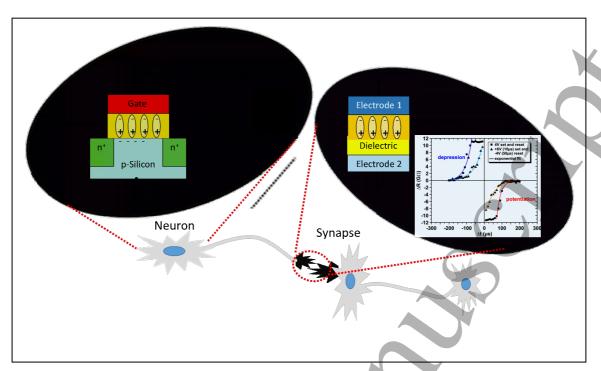

Figure 2. Main elements of a neural network. Neurons can be realized using scaled down FeFETs [11] while synapses can be realized using FTJs [10] or medium to large scale FeFETS. Adapted with permission from [10] Copyright (2020) American Chemical Society and [11] Copyright (2018) The Royal Society of Chemistry.

# **Concluding Remarks**

The discovery of ferroelectricity in hafnium oxide has led to a resumption in the research on ferroelectric memory devices, since hafnium oxide is a well-established and fully CMOS compatible material in both front end of line and back end of line processing. Besides the expected prospective realization of densely integrated non-volatile and ultra-low-power ferroelectric memories in near future, this development directly leads to the adoption of the trinity of ferroelectric memory devices – FeCAP, FeFET and FTJ - for beyond von Neumann computing. While in the memory application the important topic of reliability on the array level is yet to be solved, for neuromorphic applications the linear switching to many different states, especially in scaled down devices, is a topic that needs further attention. Moreover, very specific properties of the different ferroelectric device types demand for the development of new circuit architectures that facilitate a proper device operation taking into account the existing non-idealities. A thorough design technology co-optimization will be the key to fully exploit their potential in neuromorphic and edge computing. Finally, large scale demonstrations of ferroelectrics based neuromorphic circuits need to be investigated to identify all possible issues.

# Acknowledgements

This work was financially supported out of the State budget approved by the delegates of the Saxon State Parliament.

#### References

- [1] J. Valasek, "Piezo-electric and allied phenomena in Rochelle salt," Phys. Rev., Bd. 17, p. p. 475, 1921.

- [2] D. A. Buck, "Ferroelectrics for Digital Information Storage and Switching," *MIT Digital Computer Laboratory Report*, 1952.

- [3] D. Bondurant, "Ferroelectronic RAM Memory Family for Critical Data Storage," *Ferroelectrics 112*, pp. 273-282, 1990, doi.org/10.1080/00150199008008233.

- [4] T. Mikolajick, U. Schroeder and S. Slesazeck, "The Past, the Present, and the Future of Ferroelectric Memories," *IEEE Transactions on Electron Devices, vol. 67, no. 4, pp. April 2020, doi:* 10.1109/TED.2020.297614, vol. 67, no. 4, pp. 1434-1443, 2020.

- [5] I. Ross, "Semiconductive translating device". USA Patent 2791760 A, 1957.

- [6] X. Zhang, M. Takahashi, K. Takeuchi and S. Sakai, "64 kbit ferroelectric-gate-transistor-integrated NAND flash memory with 7.5 V program and long data retention," *Japanese Journal of Applied Physics*, 51(4S), 04DD01, 2012.

- [7] L. Esaki, R. Laibowitz and P. Stiles, "Polar switch.," IBM Tech. Discl. Bull. 13, 2161, 1971.

- [8] V. Garcia, S. Fusil, K. Bouzehouane, S. Enouz-Vedrenne, N. Mathur, A. Barthelemy and M. Bibes, "Giant tunnel electroresistance for non-destructive readout of ferroelectric states," *Nature*, *460*, 2009.

- [9] T. Böscke, J. Müller, D. Bräuhaus, U. Schröder and U. Böttger, "Ferroelectricity in hafnium oxide thin films," *Applied Physics Letters*, vol. 99, no. 10, pp. 102903-102903-3, 2011.

- [10] B. Max, M. Hoffmann, H. Mulaosmanovic, S. Slesazeck and T. Mikolajick, "Hafnia-Based Double-Layer Ferroelectric Tunnel Junctions as Artificial Synapses for Neuromorphic Computing," *ACS Appl. Electron. Mater.*, vol. 2, no. 12, p. 4023–4033, 2020.

- [11] H. Mulaosmanovic, E. Chicca, M. Bertele, T. Mikolajick and S. Slesazeck, "Mimicking biological neurons with a nanoscale ferroelectric transistor," *Nanoscale*, vol. 10, no. 46, pp. 21755-21763, 2018, DOI:10.1039/C8NR07135G.

- [12] S. Beyer et al., "FeFET: A versatile CMOS compatible device with game-changing potential," *IEEE International Memory Workshop (IMW)*,, pp. 1-4, 2020.

- [13] A. Sally, "Reflections on the memory wall," Proc. Conf. Comput. Front., p. p. 162., 2004.

- [14] J. Okuno, T. Kunihiro, K. Konishi, H. Maemura, Y. Shuto, S. Materano, T. Ali, K. Kuehnel, K. Seidel, U. Schroeder, T. Mikolajick and M. Tsukamo, "SoC compatible 1T1C FeRAM memory array based on ferroelectric Hf0.5Zr0.5O2," *VLSI Technology*, pp. pp. 1-4, 2020.

- [15] M. Pešić, F. Fengler, L. Larcher, A. Padovani, T. Schenk, E. Grimley, X. Sang, J. LeBeau, S. Slesazeck, U. Schroeder and T. Mikolajick, "Physical Mechanisms behind the Field-Cycling Behavior of HfO2-Based Ferroelectric Capacitors," *Adv. Funct. Mater*, vol. 26, no. 25, pp. 4601-4612, 2016.

- [16] S. Slesazeck and T. Mikolajick, "Nanoscale resistive switching memory devices: a review," *Nanotechnology*, vol. 30.35, no. 352003, 2019.

- [17] S. Deng, Z. Jiang, S. Dutta, H. Ye, W. Chakraborty, S. Kurinec, S. Datta and K. Ni, "Examination of the Interplay Between Polarization Switching and Charge Trapping in Ferroelectric FET," in *International Electron Device Meeting (IEDM)*, San Francisco, 2020.

- [18] Y. Wei, P. Nukala, M. Salverda, S. Matzen, J. Zhao, J. Momand, A. S. Everhardt, G. Agnus, G. R. Blake, P. Lecoeur, B. J. Kooi, J. Íñiguez, B. Dkhil and B. Noheda, "A rhombohedral ferroelectric phase in epitaxially strained Hf0.5Zr0.5O2 thin films," *Nature Materials*, Vols. vol. 17, no. 12,, pp. pp. 1095-1100, 2018.

- [19] M. Pešić, U. Schroeder, S. Slesazeck and T. Mikolajick, "Comparative Study of Reliability of Ferroelectric and Anti-Ferroelectric Memories," *IEEE Transactions on Device and Materials Reliability Vol. 18, No. 2*, pp. 154 162, 2018, doi: 10.1109/TDMR.2018.2829112.

- [20] S. Fichtner, N. Wolff, F. Lofink, L. Kienle and B. Wagner, "AlScN: A III-V semiconductor based ferroelectric," *Journal of Applied Physics*, vol. 125, no. 11, p. 114103, 2019.

# 1.3 Valence change memory

Sabina Spiga, CNR-IMM, Unit of Agrate Brianza, via C. Olivetti 2, Agrate Brianza (MB), Italy

Stephan Menzel, FZ Juelich (PGI-7), Juelich, Germany

#### **Status**

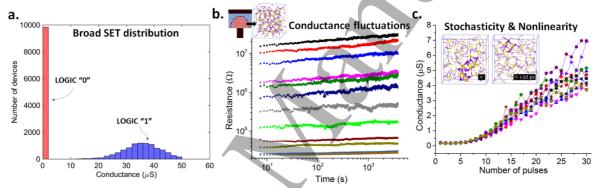

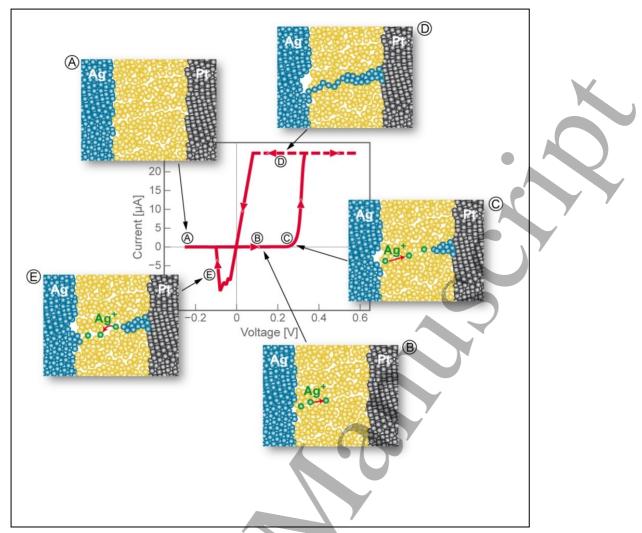

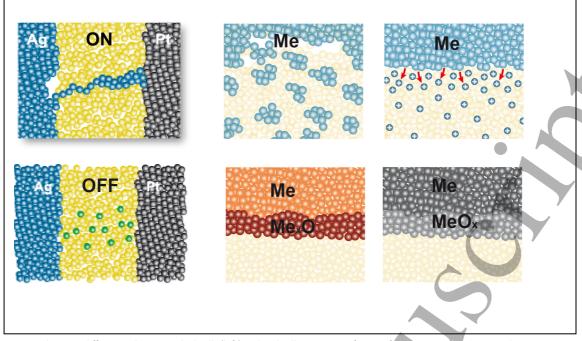

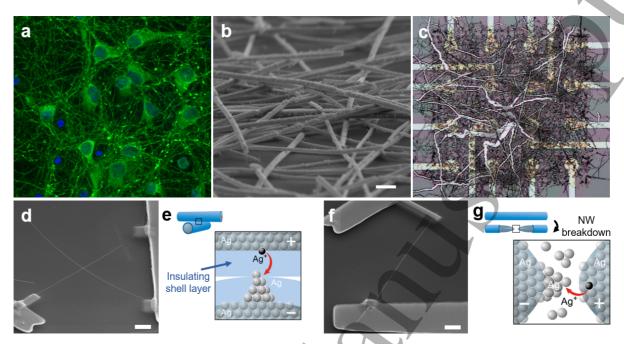

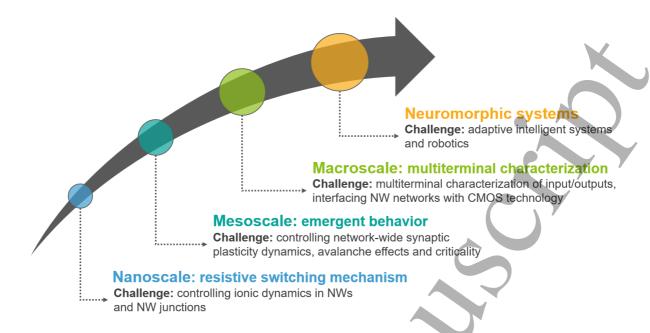

Resistive random access memories (RRAMs), also named memristive devices, change their resistance state upon electrical stimuli. They can store and compute information at the same time, thus enabling in-memory and brain-inspired computing [1, 2]. RRAM devices relying on oxygen ion migration effects and subsequent valence changes are named valence change memory (VCM) [3]. They have been proposed to implement electronic synapses in hardware neural networks, due to the ability to adapt their strength (conductance) in an analogue fashion as a function of incoming electrical pulses (synaptic plasticity), leading to long-term (short-term) potentiation and depression. In addition, learning rules such as spike-time or spike-rate dependent plasticity, paired-pulse facilitation or the voltage threshold-based plasticity have been demonstrated; the stochasticity of the switching process has been exploited for stochastic update rules [4-6]. Most of the VCM devices are based on a twoterminal configuration, and the switching geometry involves either confined filamentary, or interfacial regions (Fig.1A). Filamentary VCMs are today the most advanced in terms of integration and scaling. Their switching mechanism relies on the creation and rupture of conductive filaments (CF), formed by a localized concentration of defects, shorting the two electrodes. The modulation/control of the CF diameter and/or CF dissolution can lead to two or multiple stable resistance states [7, 8]. Prototypes of neuromorphic chips have been recently shown, integrating HfOx and TaOx-based filamentary-VCM as synaptic nodes in combination with CMOS neurons [9-11]. In interfacial VCM devices, the conductance scales with the junction area of the device, and the mechanism is related to a homogenous oxygen ion movement through the oxides, either at the electrode/oxide or oxide/oxide interface. Reference material systems are based on complex oxides, such as bismuth ferrite [12] and praseodymium calcium manganite [13]; or bilayers stacks, e.g. TiO<sub>2</sub>/TaO<sub>2</sub> [14] and a-Si/TiO<sub>2</sub> [15]. Finally, 3-terminal VCM redox transistors have been recently studied (Fig.1A-right), where the switching mechanism is related to the control of the oxygen vacancy concentration in the bulk of the transistor channel [16, 17]. While interfacial and redox-transistor devices are today at low technological readiness, and most of the studies are reported at single device level, they promise future advancement in neuromorphic computing in terms of analogue control, higher resistance values, improved reliability, reduced stochasticity with respect to filamentary devices [18]. To design neuromorphic circuits including VCM devices, compact models are requested. For filamentary devices compact models including variability are available [18, 19], but lacking for interfacial VCM and redoxbased transistors.

# **Current and Future Challenges**

VCM devices have been developed in the last 15 years mainly for storage applications, but for neuromorphic applications the required properties differ. In general, desirable properties of memories for neural networks include (i) analogue behaviour or controllable multilevel states, (ii) compatibility with learning rules supporting also online learning, (iii) tuneable short-term and long-term stability of the weights to implement various dynamics and timescales in synaptic and neuronal circuits [4-6]. A significant debate still refers to the linear/non-linear and symmetric/asymmetric

conductance update of experimental devices, synaptic resolution (number of resistance levels), and how to exploit or mitigate these features (Figs1-B,C).

**Filamentary** devices are the most mature type of VCMs. Nevertheless, many issues are pending: e.g. control of multi-level operation, device variability, intrinsic stochasticity, program and read disturbs, and the still too low resistance level range for neuromorphic circuits [20]. Moreover, the understanding/modelling of their switching mechanism is still under debate. Whereas first models including switching variability and read noise are available [18, 19], retention modelling, and the modelling of volatile effects and device failures are current challenges. First hybrid CMOS-VCM chips have been developed demonstrating inference application, but so far they do not support on-chip learning [9-11].

Interfacial VCM devices show in general less variability, less (no) read instability and a very analogue tuning of the conductance states, which can leads to a more deterministic and linear conductance update compared to filamentary devices [13]. Still these properties are not characterized on a high statistical basis. The retention, especially for thin oxide devices, is lower than for filamentary devices, which may be still compatible with some applications. As the conductance scales with area, the achievable high resistance levels promise a low power operation. Typical devices, however, have a large area or thick switching oxides, and scaling them to the nanoscale is an open issue. Moreover, devices showing a large resistance modulation require high switching voltages, not easily compatible with scaled CMOS nodes. The fabrication and characterization of interfacial VCM arrays needs to be further addressed. Simulation models for interfacial VCM are not available yet and need to be developed.

**Redox-based VCM transistors** have been only shown on a single device level [16, 17]. Thus, reliable statistical data on cycle-to-cycle variability, device-to-device variability and stability of the programmed states is not available yet. Moreover, the trade-off between switching speed and voltage has not been studied in detail. Another challenge is the understanding of the switching mechanism and the development of suitable models for circuit design.

The open challenges for all three types of VCM devices are summarized in Table I.

# **Advances in Science and Technology to Meet Challenges**

The current challenges for VCM-type devices push the research in various but connected directions, which span from material, to theory, devices and architecture. A better understanding of material properties and microscopic switching mechanisms is definitely required. However, the key step is to demonstrate the device integration in complex circuits and hybrid CMOS-VCM hardware neuromorphic chips. While VCMs are not ideal devices, many issues can be solved or mitigated at circuit level still taking advantage of their properties in term of power, density, and dynamic properties.

In this context, **filamentary** VCM devices are the most mature technology, but their deployment into neuromorphic computing hardware is still at its infancy. A comprehensive compact model, depicting complete dynamics including retention effects, e.g. to accurately simulate online learning, is required for the development of optimized circuits. On the material level, the biggest issues are read noise and switching variability. Due to the inherent Joule heating effect, the transition time of the conductance switching is very short and depends strongly on the device state [21]. This makes it hard to control the conductance update. Future research could explore very fast pulses in the range of the transition time to update the cell conductance, or use thermal engineering of the device stacks to increase the

transition time. Finally, to achieve low power operation, resistance state values should be moved to the  $M\Omega$  regime.

For interfacial and redox-transistor VCM devices, one of the next important steps is to shift from single device research to large arrays, possibly co-integrated with CMOS. This step enables to collect a large amount of data, which is required for modelling and demonstrating robust neuromorphic functions. It would be highly desirable to identify a reference material system with a robust switching mechanism supported by a comprehensive understanding and modelling from underlying physics to compact and circuits modelling. Indeed, the modelling of these devices are still at its infancy. One open question for both devices is the trade-off between data retention and switching speed. In contrast to the filamentary devices, the velocity of the ions are probably not accelerated by Joule heating. Thus, the voltage needs to be increased more than in filamentary devices, to operate the devices at fast speed [22]. This might limit the application of these device to a certain time domain as the CMOS might not be able to provide the required voltage. By using thinner device layers or material engineering this issue could be addressed.

# **Concluding Remarks**

The VCM device technologies can integrate novel functionalities in hardware as key elements of the synaptic nodes in neural networks, i.e. to store the synaptic weight. Moreover, they can enable new learning algorithms that enable bio-plausible functions over multiple timescales. At the moment, it is still not clear which can be the best "final" VCM material system and/or VCM device type, having each of them advantages and disadvantages. The missing "killer" system, with consolidated properties/understanding/easy manufacturing, prevents to concentrate the efforts of the scientific community in single direction to bring VCM device to industrial real applications beyond a niche market. While filamentary VCMs are already been implemented in neuromorphic computing hardware, interfacial VCM or redox transistor can open new perspectives in the long term. To this end, there is an urgent request to further develop VCM devices enhancing new properties through a combined synergetic development based on materials design, physical and electrical characterizations and multiscale modelling to support the microscopic understanding of the link between the device structure and the electrical characteristics. Moreover, the device development targeting braininspired computing systems can only go hand-in-hand with theory and architectures design in a holistic view.

# Acknowledgements

This work was partially supported by the Horizon 2020 European projects MeM-Scales (Grant No. 871371), MNEMOSENE (Grant No.780215), and NEUROTECH (Grant No. 824103); in part by the Deutsche Forschungsgemeinschaft (SFB 917); in part by the Helmholtz Association Initiative and Networking Fund under project number SO-092 (Advanced Computing Architectures, ACA) and in part by the Federal Ministry of Education and Research (BMBF, Germany) in the project NEUROTEC (project numbers 16ES1134 and 16ES1133K).

# References

- [1] S. Spiga, A. Sebastian, D. Querlioz and B. Rajendran, *Memristive Device for Brain-Inspired Computing: From Materials, Devices, and Circuits to Applications Computational Memory, Deep Learning and Spiking Neural Networks* Woodheat Publishing, 2020.

- [2] D. Ielmini and H. P. Wong, "In-memory computing with resistive switching devices," *Nature Electronics*, vol. 1, pp. 333-343, 2018.

- [3] R. Waser, R. Dittmann, G. Staikov and K. Szot, "Redox-Based Resistive Switching Memories Nanoionic Mechanisms, Prospects, and Challenges," *Adv. Mater.*, vol. 21, pp. 2632-2663, 2009.

- [4] S. Brivio, D. R. B. Ly, E. Vianello and S. Spiga, "Non-linear Memristive Synaptic Dynamics for Efficient Unsupervised Learning in Spiking Neural Networks," *Front. Neurosci.*, vol. 15, pp. 580909, 2021.

- [5] M. Payvand, Y. Demirag, T. Dalgaty, E. Vianello and G. Indiveri, "Analog Weight Updates with Compliance Current Modulation of Binary ReRAMs for On-Chip Learning,", 2020, pp. 1-5.

- [6] E. Covi, R. George, J. Frascaroli, S. Brivio, C. Mayr, H. Mostafa, G. Indiveri and S. Spiga, "Spike-driven threshold-based learning with memristive synapses and neuromorphic silicon neurons," *J. Phys. D Appl. Phys.*, vol. 51, pp. 344003, 2018.

- [7] W. Zhang, B. Gao, J. Tang, X. Li, W. Wu and H. Qian, "Analog-Type Resistive Switching Devices for Neuromorphic Computing," *PSS-RRL*, vol. 13, pp. 1900204, 2019.

- [8] E. Covi, S. Brivio, A. Serb, T. Prodromakis, M. Fanciulli and S. Spiga, "Analog Memristive Synapse in Spiking Networks Implementing Unsupervised Learning," *Frontiers in Neuroscience*, vol. 10, pp. 6-13, 2016.

- [9] R. Mochida, K. Kouno, Y. Hayata, M. Nakayama, T. Ono, H. Suwa, R. Yasuhara, K. Katayama, T. Mikawa and Y. Gohou, "A 4M Synapses integrated Analog ReRAM based 66.5 TOPS/W Neural-Network Processor with Cell Current Controlled Writing and Flexible Network Architecture," 2018 IEEE Symposium on VLSI Technology, 18-22 June 2018, Honolulu, HI, USA, 2018, pp.

- [10] A. Valentian, F. Rummens, E. Vianello, T. Mesquida, C. L. M. de Boissac, O. Bichler and C. Reita, "Fully Integrated Spiking Neural Network with Analog Neurons and RRAM Synapses," 2019 IEEE International Electron Devices Meeting (iedm), 2019, pp.

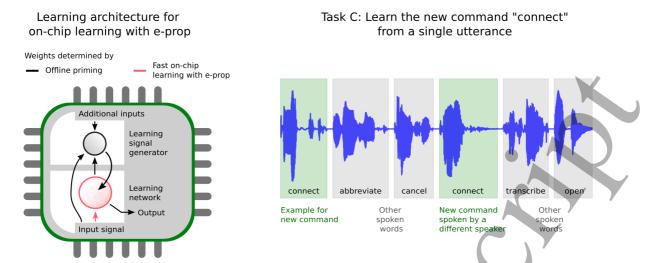

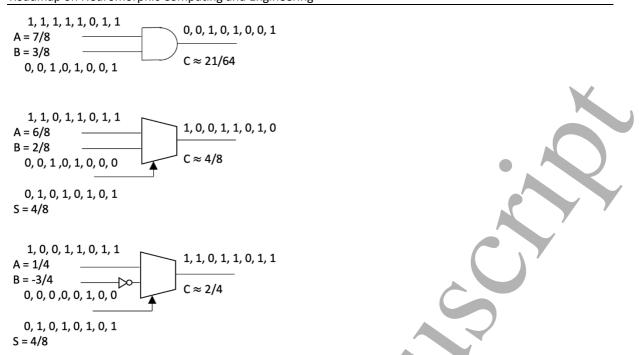

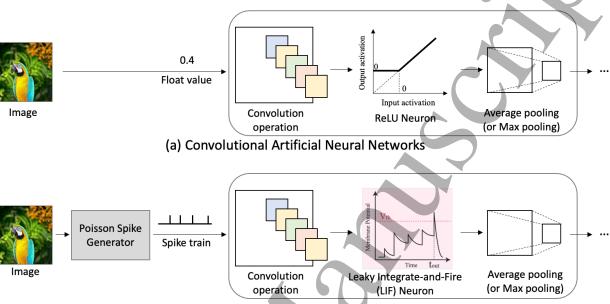

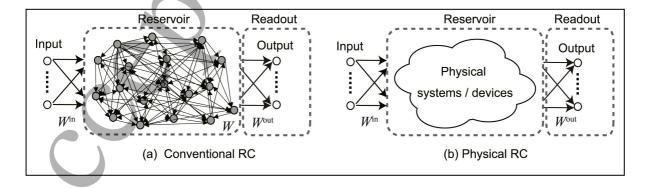

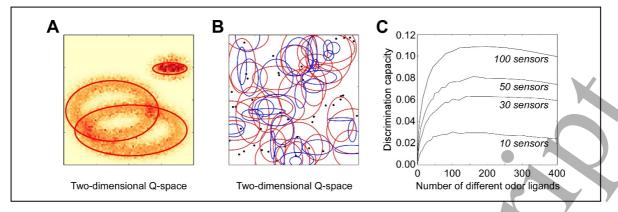

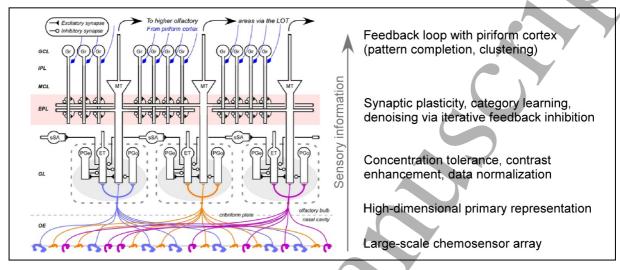

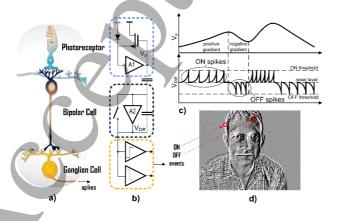

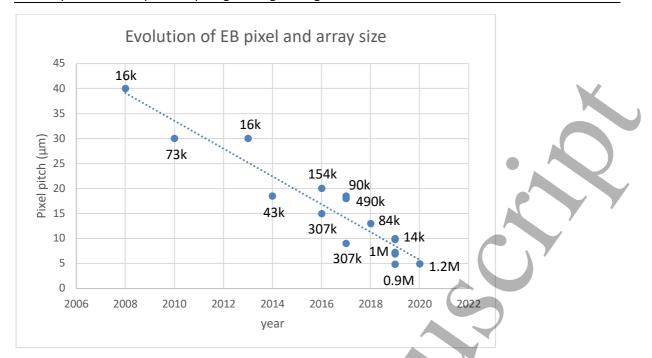

- [11] P. Yao, H. Wu, B. Gao, J. Tang, Q. Zhang, W. Zhang, J. J. Yang and H. Qian, "Fully hardware-implemented memristor convolutional neural network," *Nature*, vol. 577, pp. 641-646, 2020.