Doctoral Dissertation Doctoral Program in Computer Engineering ( $34^{th}$ cycle)

# Vertical Optimizations of Convolutional Neural Networks for Embedded Systems

Ву

## Antonio Cipolletta

\*\*\*\*\*

#### Supervisor(s):

Prof. Enrico Macii Prof. Andrea Calimera

#### **Doctoral Examination Committee:**

Prof. Ibrahim Elfadel, Referee, Khalifa University Prof. Fatih Ugurdag, Referee, Ozyegin University Prof. Andrea Acquaviva, Università di Bologna Prof. Alberto Bosio, École Centrale de Lyon Prof. Andrea Bottino, Politecnico di Torino

> Politecnico di Torino 2022

## Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Antonio Cipolletta 2022

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

## Acknowledgements

First, I would like to thank my supervisor Enrico Macii for letting me pursue a doctorate in his research group. Special thanks go to my supervisor Andrea Calimera for the endless sessions of discussions of research ideas and for helping me drive my efforts and enthusiasm in the right direction.

I would also like to thank all the people at LAB4 with whom I have interacted during this period. Above all, I thank my colleagues Luca and Matteo for sharing their passion for the research topic and for helping me go through all the ups and downs of these last few years. Next, I thank all the students of the Synthesis and Optimization of Digital Systems course, especially Giorgio and Nicole, who ended up doing a master thesis under my supervision: you taught me how to be a better communicator and mentor.

Finally, I would like to thank my family and my friends for their support during these years. To my friends, I still believe that friendship is not important, but it is the only thing that matters. To my parents, Maria Letizia and Martino, I cannot be grateful enough for the environment you created to let me grow up. To my grandparents and my uncle Luca, you have been my role models. To my brother Enzo, you can always count on me. To Elisa, quando sei qui con me, questa stanza non ha più pareti...

#### Abstract

The need for high levels of user privacy, low latency, and low cost has recently required moving the Deep Convolutional Neural Network (CNN) inference process from the cloud to "the edge", that is, on lightweight resource-constrained embedded systems. Such a paradigm shift creates a huge technical challenge: filling the gap between the computational and memory requirements of modern CNNs and the limited hardware and energy resources of embedded systems.

This dissertation tackles this challenge through vertical and automated optimizations across the entire software stack, focusing on how to build small, fast, and energy-efficient CNNs. After reviewing the most adopted memory allocation algorithms in CNN compilers, the first part of this thesis introduces the dataflow restructuring, a novel functionality-preserving method for minimizing the activation memory footprint of CNNs. Then, a new compression pipeline is presented, which combines weight pruning with dataflow restructuring to deploy more accurate CNNs on tiny MCU devices. The second part of this dissertation presents an optimization framework based on neural architectural design, quantization, and optimized integer kernels to accelerate CNNs on mobile-friendly CPUs and MCUs. The framework is evaluated in the context of a key use case for embedded computer vision, namely, monocular depth estimation, demonstrating the importance of a vertical approach to meet stringent application and hardware constraints. Finally, the last part of the dissertation deals with the deployment of energy-quality scalable CNNs. To this end, first, an energy-quality scalable system for monocular depth estimation named EQPyD-Net is described and characterized. Then, Nested Sparse CNNs, a class of low footprint, dynamic CNNs, are proposed to tackle inference tasks at the edge of the Internet-of-Things.

Overall, the contribution of this dissertation is threefold. Novel automated optimization techniques are presented to improve the efficiency of state-of-the-art CNNs with minimal to no accuracy loss. New dynamic knobs are introduced to extend the achievable accuracy-complexity trade-off at run time. Finally, the proposed optimizations show that working across multiple levels of the optimization stack pushes further the boundary of accurate CNNs that can be deployed on tiny embedded devices.

## Contents

| List of Figures |       |        |                                                 |   | viii |

|-----------------|-------|--------|-------------------------------------------------|---|------|

| Li              | st of | Table  | ${f s}$                                         |   | xii  |

| 1               | Intr  | oduct  | ion                                             |   | 1    |

|                 | 1.1   | Conte  | xt and Motivation                               |   | 1    |

|                 | 1.2   | Neura  | l Network Optimization Stack                    |   | 3    |

|                 |       | 1.2.1  | Neural Architecture Design                      |   | 4    |

|                 |       | 1.2.2  | Algorithmic-level Optimizations                 |   | 8    |

|                 |       | 1.2.3  | Graph-level Optimizations                       |   | 11   |

|                 |       | 1.2.4  | Operator-level Optimizations                    |   | 12   |

|                 | 1.3   | Objec  | tives and Contributions                         |   | 13   |

| 2               | Me    | mory ( | Optimizations for Convolutional Neural Networks |   | 17   |

|                 | 2.1   | Introd | luction and Motivation                          |   | 17   |

|                 | 2.2   | Memo   | ory Allocation Algorithms for CNNs              |   | 19   |

|                 |       | 2.2.1  | Motivation                                      |   | 19   |

|                 |       | 2.2.2  | Problem Formulation                             |   | 21   |

|                 |       | 2.2.3  | Memory Allocation Algorithms                    |   | 23   |

|                 |       | 2.2.4  | Experimental Results                            |   | 31   |

|                 |       | 2.2.5  | Discussion                                      | _ | 35   |

vi Contents

|   | 2.3 | Datafl  | ow Restructuring for Activation Memory Reduction in CNNs | 37 |

|---|-----|---------|----------------------------------------------------------|----|

|   |     | 2.3.1   | Background                                               | 38 |

|   |     | 2.3.2   | Related Works                                            | 39 |

|   |     | 2.3.3   | Restructuring Algorithm                                  | 41 |

|   |     | 2.3.4   | Experimental Results                                     | 46 |

|   |     | 2.3.5   | Discussion                                               | 49 |

|   | 2.4 | Sparse  | e-Tiled Tensor Graph Processing                          | 49 |

|   |     | 2.4.1   | Optimization Pipeline                                    | 50 |

|   |     | 2.4.2   | Experimental Results                                     | 52 |

|   |     | 2.4.3   | Discussion                                               | 56 |

|   | 2.5 | Conclu  | usions                                                   | 57 |

| 3 | Ena | bling I | Monocular Depth Estimation on Low Power Devices          | 58 |

| • | 3.1 | Ü       | uction and Motivation                                    |    |

|   | 3.2 |         | Learning for Depth Estimation                            |    |

|   | 3.3 |         | ing Depth Estimation on ARMv7a CPUs                      |    |

|   | 0.0 | 3.3.1   | Related Works                                            | 63 |

|   |     | 3.3.2   | PyD-Net Design and Training                              | 63 |

|   |     | 3.3.3   | Optimization Framework                                   |    |

|   |     | 3.3.4   | Experimental Results                                     |    |

|   |     | 3.3.5   | Discussion                                               | 76 |

|   | 3.4 |         | ing Depth Estimation on Microcontrollers                 | 76 |

|   | 3.1 | 3.4.1   | Practical Use Cases                                      | 78 |

|   |     | 3.4.2   | $\mu$ PyD-Net architecture                               | 80 |

|   |     | 3.4.3   | Proxy Supervision                                        | 81 |

|   |     | 3.4.4   | Optimization Stack                                       | 83 |

|   |     | 3.4.5   | Experimental Results                                     | 85 |

|   |     | 0.7.0   |                                                          | 00 |

| Contents | vii |

|----------|-----|

|----------|-----|

|              |       | 3.4.6   | Discussion                                                | 97      |

|--------------|-------|---------|-----------------------------------------------------------|---------|

|              | 3.5   | Concl   | usions                                                    | 98      |

| 4            | Ene   | ergy-Q  | uality Scalable Convolutional Neural Networks             | 99      |

|              | 4.1   | Introd  | luction and Motivation                                    | 99      |

|              | 4.2   | Energ   | y-Quality Scaling Knobs                                   | 101     |

|              | 4.3   |         | y-Quality Scalable Monocular Depth Estimation on End CPUs |         |

|              |       | 4.3.1   | Training and Optimization Flow for EQPyD-Net              | 103     |

|              |       | 4.3.2   | Experimental Results                                      | 106     |

|              |       | 4.3.3   | Discussion                                                | 114     |

|              | 4.4   | Energ   | y-Quality Scalable CNNs on Tiny Devices via Nested Spar   | sity114 |

|              |       | 4.4.1   | Related Works                                             | 116     |

|              |       | 4.4.2   | Building Nested Sparse CNNs                               | 117     |

|              |       | 4.4.3   | Experimental Results                                      | 123     |

|              |       | 4.4.4   | Discussion                                                | 130     |

|              | 4.5   | Concl   | usions                                                    | 130     |

| 5            | Cor   | ıclusio | ns and Future Works                                       | 132     |

|              | 5.1   | Futur   | e Perspectives                                            | 134     |

| Li           | st of | Publi   | cations                                                   | 137     |

| $\mathbf{R}$ | efere | nces    |                                                           | 139     |

# List of Figures

| 1.1 | Top-1 accuracy on ImageNet [8] vs. number of floating point                                                                                                                                                 |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | operations (FLOPs) vs. model size. Image taken from [9]                                                                                                                                                     | 2  |

| 1.2 | DNN optimization stack                                                                                                                                                                                      | 4  |

| 1.3 | a) A pictorial representation of a DNN; b) main parameters of a                                                                                                                                             |    |

|     | convolutional layer; c) three common neural modules                                                                                                                                                         | 5  |

| 1.4 | Pictorial representation of the dissertation outline                                                                                                                                                        | 14 |

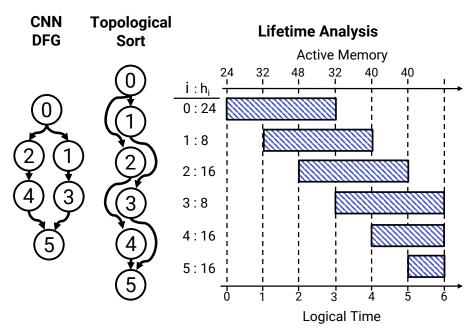

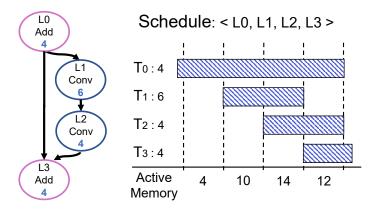

| 2.1 | On the left, the DFG representation of a CNN. In the middle, the topological order $\sigma$ as a linearization of the DFG. On the right, the lifetime analysis and the active memory for the ordered DFG    | 21 |

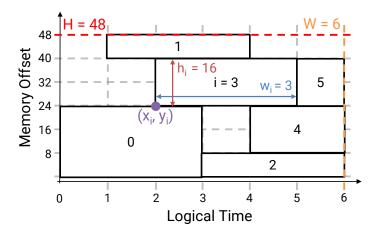

| 2.2 | Example of a memory allocation for the sorted DFG reported in Fig. 2.1                                                                                                                                      | 22 |

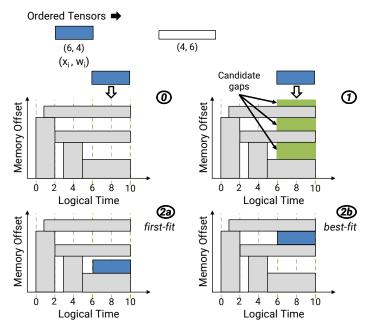

| 2.3 | Schematic view of the tensor-first heuristic algorithm. The picture refers to a <i>by-size</i> tensor policy. The bottom row shows the first-fit (step 2a) and best-fit (step 2b) offset indexing policies. | 26 |

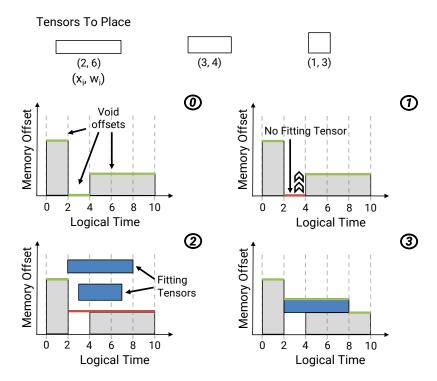

| 2.4 | Schematic view of the offset-first heuristic algorithm                                                                                                                                                      | 28 |

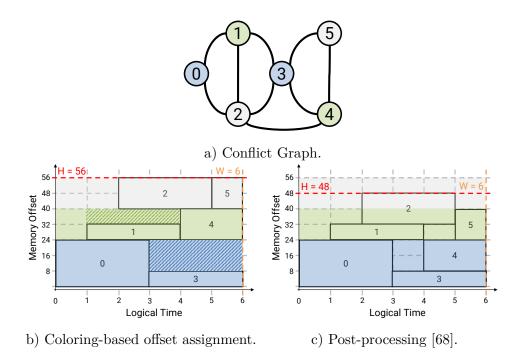

| 2.5 | Schematic view of memory allocation with graph coloring                                                                                                                                                     | 30 |

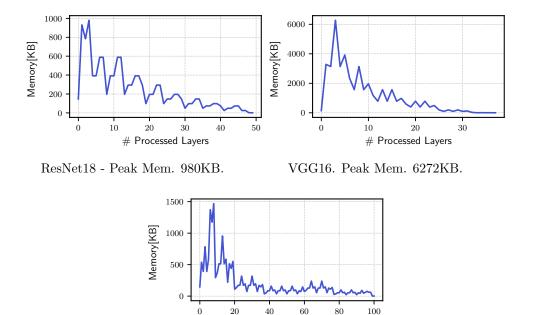

| 2.6 | Memory profile of three different CNNs during the forward pass.<br>Input tensor resolution is 3x224x224 (i.e., ImageNet [8] standard                                                                        |    |

|     | resolution)                                                                                                                                                                                                 | 37 |

List of Figures ix

| 2.7  | On the left, the DFG of a residual block [1]; on the right, the conflict graph of its intermediate tensors $T_i$ . Each node is labeled with an ID, the tensor operation performed, and the size of the output tensor                | 39  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

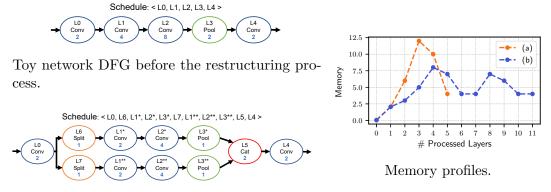

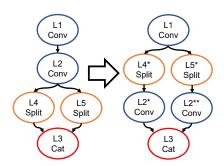

| 2.8  | Example of the dataflow restructuring process on a linear DFG.                                                                                                                                                                       | 42  |

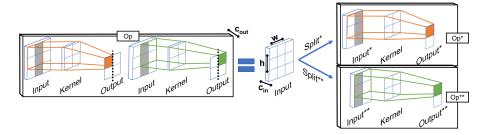

| 2.9  | The split of a stencil operator into two smaller independent operators                                                                                                                                                               | 43  |

| 2.10 | Graph-rewriting that propagates the split operators in the DFG.                                                                                                                                                                      | 44  |

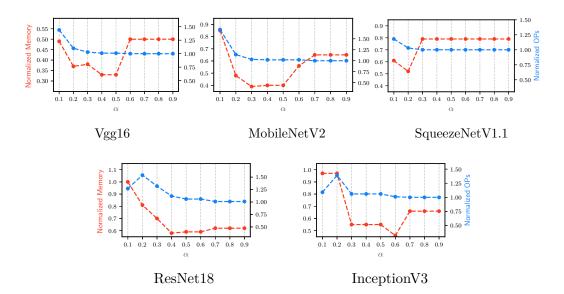

| 2.11 | Normalized memory and number of operations for $\alpha \in [0.1, 0.9]$ and $n\_slices=\{2h, 2w\}.$                                                                                                                                   | 46  |

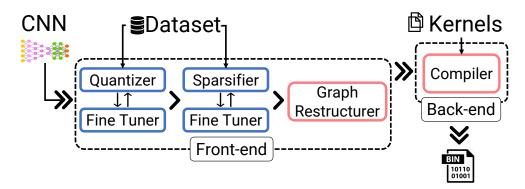

| 2.12 | The proposed optimization pipeline. The blue boxes indicate data-driven passes, while the red boxes data-independent passes.                                                                                                         | 51  |

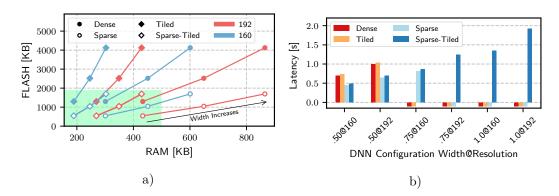

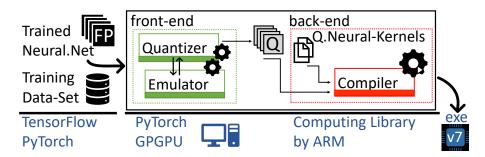

| 2.13 | a) FLASH and RAM requirements for different configurations of MobileNetV1. Width values are 0.50, 0.75, 1.00. b) Latency measurements for MobileNetV1. Bars sorted for accuracy, from least accurate (left) to most accurate (right) | 55  |

| 2.14 | a) FLASH and RAM requirements for different configurations of MobileNetV2. Width values are 0.50, 0.75, 1.00. b) Latency measurements for MobileNetV2. Bars sorted for accuracy, from least accurate (left) to most accurate (right) | 56  |

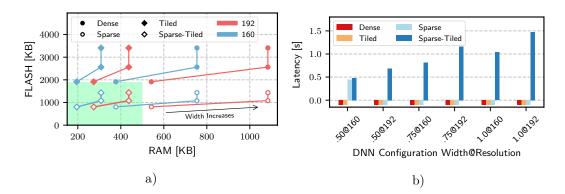

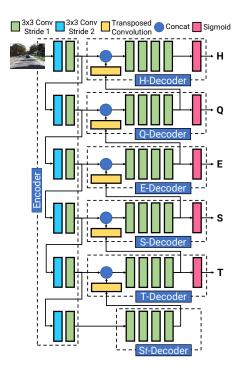

| 3.1  | PyD-Net architecture. H stands for $\frac{1}{2}$ of the input resolution, Q for $\frac{1}{4}$ , E for $\frac{1}{8}$ , S for $\frac{1}{16}$ , T for $\frac{1}{32}$                                                                    | 64  |

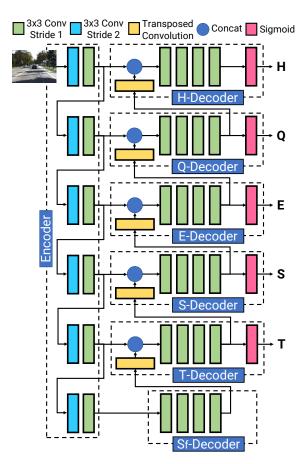

| 3.2  | Optimization and deployment flow targeting ARMv7a cores                                                                                                                                                                              | 66  |

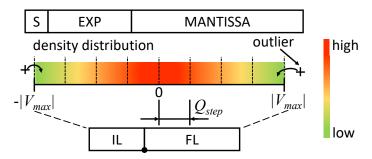

| 3.3  | Floating-Point to Fixed-point quantization                                                                                                                                                                                           | 68  |

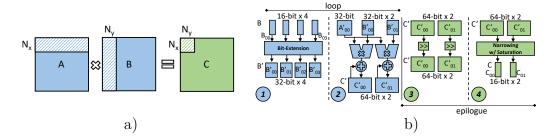

| 3.4  | Q.Neural-Kernel: execution flow for 16-bit fixed-point                                                                                                                                                                               | 70  |

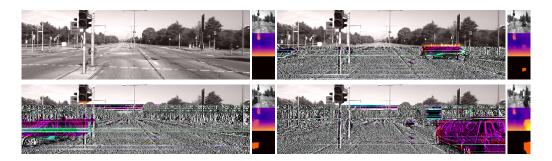

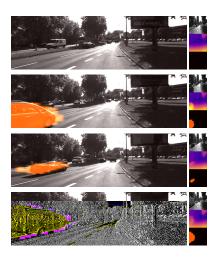

| 3.5  | Top row: Input image from KITTI dataset (left) and depth map H@FP32 computed by the original PyD-Net network [122] (right). Bottom row: depth maps H@FX16-ft (left) and H@FX8-ft (i.i.t.)                                            | 7.4 |

|      | ft (right)                                                                                                                                                                                                                           | 74  |

**x** List of Figures

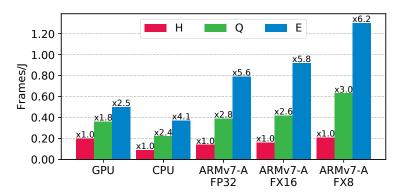

| 3.6  | Energy efficiency vs. Resolution using GPU, CPU and the ARMv7-A                                                                                                                                                                                                                                                                     | 76  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.7  | Example of traffic monitoring system based on $\mu PyD$ -Net                                                                                                                                                                                                                                                                        | 78  |

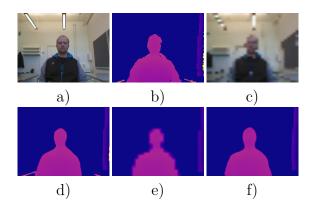

| 3.8  | Results on a testing image of the VAP dataset [136]. a) RGB original frame, b) ground-truth depth acquired using Kinect, c) RGB input image resized to 32 $\times$ 32, d) maps predicted by PyD-Net, e) maps predicted by $\mu\text{PyD-Net}$ , and f) outcome of the super-resolution network fed with the $\mu\text{PyD-Net}$ map | 79  |

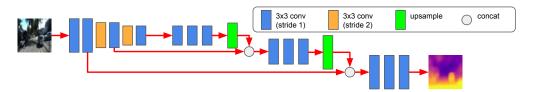

| 3.9  | $\mu$ PyD-Net architecture                                                                                                                                                                                                                                                                                                          | 80  |

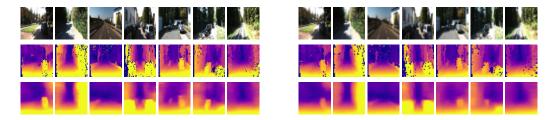

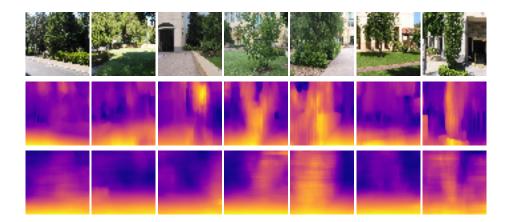

| 3.10 | Examples of self-sourced proxy labels on $48\times48$ (left) and $32\times32$ (right) images. From top to bottom, reference images, disparity maps produced by SGM [100], and predictions by $\mu$ PyD-Net                                                                                                                          | 82  |

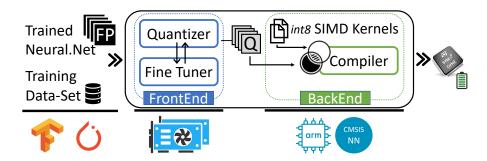

| 3.11 | Optimization framework                                                                                                                                                                                                                                                                                                              | 84  |

| 3.12 | Qualitative results concerning traffic monitoring. For each example, we show the high-resolution frame, followed by $32\times32$ images processed by $\mu\text{PyD-Net.}$                                                                                                                                                           | 91  |

| 3.13 | Qualitative results on Make<br>3D. From top to bottom, reference images, inverse depth maps by MonoRes<br>Match [114] and by $48\times48~\mu\text{PyD-Net.}$                                                                                                                                                                        | 94  |

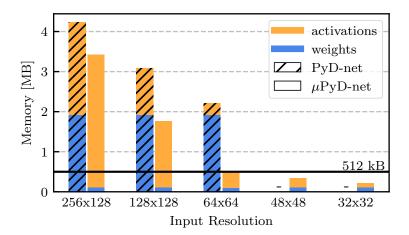

| 3.14 | Memory breakdown of PyD-Net and $\mu$ PyD-Net at different input resolutions. The dash (-) indicates that the resolution is not compliant with the network topology                                                                                                                                                                 | 96  |

| 4.1  | PyD-Net architecture. H stands for $\frac{1}{2}$ of the input resolution, Q for $\frac{1}{4}$ , E for $\frac{1}{8}$ , S for $\frac{1}{16}$ , T for $\frac{1}{32}$                                                                                                                                                                   | 104 |

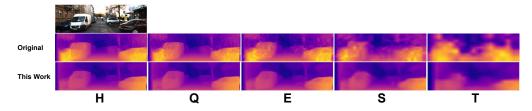

| 4.2  | Depth estimated at different output resolutions for an input taken from the KITTI dataset. On top [122], on the bottom EQPyD-Net                                                                                                                                                                                                    | 105 |

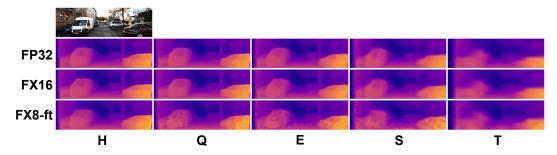

| 4.3  | Depth images obtained for each value of precision and output resolution for an input taken from the KITTI dataset. The last row illustrates depth images inferred after fine-tuning (-ft)                                                                                                                                           | 110 |

List of Figures xi

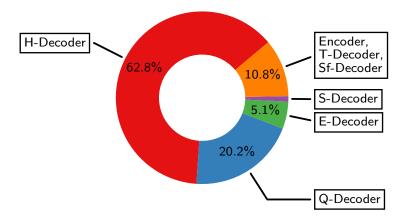

| 4.4  | Energy breakdown of different modules of EQPyD-Net at FX16. Similar values have been observed also for FX8                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

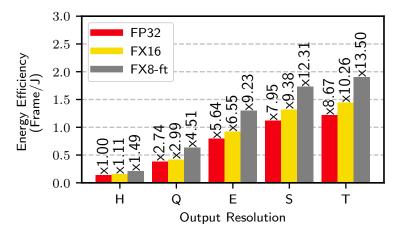

| 4.5  | Energy efficiency at different output scales and precision configurations. Annotations indicate the relative improvement with respect to H@FP32 (0.141 Frame/J)                                       |

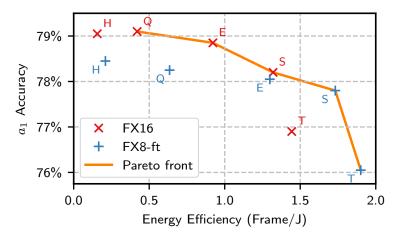

| 4.6  | Energy and accuracy at different output resolutions (from left to right $H \rightarrow T$ ) and precision configurations (FX16 and FX8-ft). The orange curve connects Pareto-optimal solutions        |

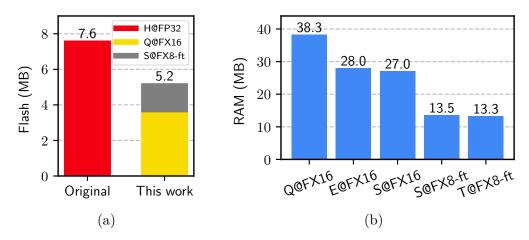

| 4.7  | Flash (a) and RAM (b) requirements for Energy-Quality scaling with EQPyD-Net                                                                                                                          |

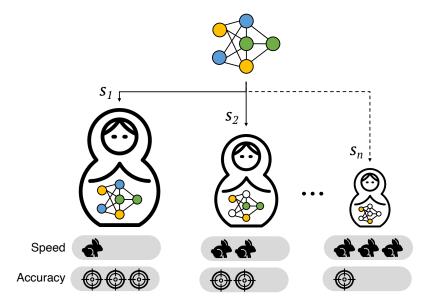

| 4.8  | A pictorial representation of a Nested Sparse CNN                                                                                                                                                     |

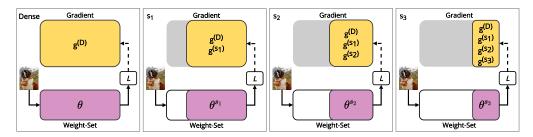

| 4.9  | Training step: full weight-set $(\theta)$ and the sub-nets $(\theta^{s_i})$ sorted with an increasing order of sparsity (i.e $s_1 < s_2 < s_3$ )                                                      |

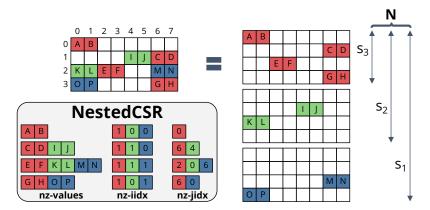

| 4.10 | Example of the proposed NestedCSR format applied to a $1\times 2$ block sparse matrix $W$ that can work in three sparsity levels $\{s_1, s_2, s_3\}$                                                  |

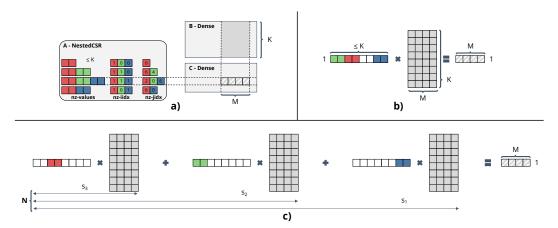

| 4.11 | Example of the proposed compute kernel performing a sparse matrix-matrix multiplication between a $1\times 2$ block sparse matrix $A$ encoded using the NestedCSR format and a dense matrix $B$ . 122 |

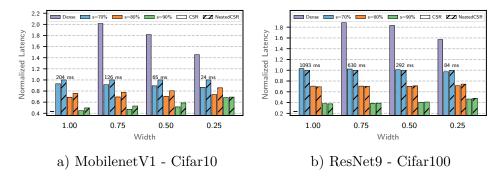

| 4.12 | Latency values normalized for each width to the NestedCSR@ $s=70\%$ . The latency of the dense model at $w=1.00$ is not shown as it exceeds the FLASH memory of the adopted device (2MB) 126          |

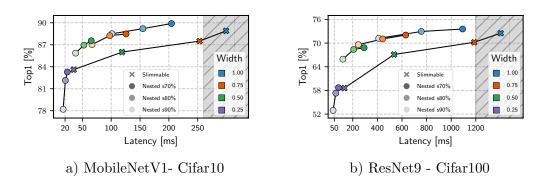

| 4.13 | Latency-accuracy scaling for Slimmable CNNs and Nested Sparse CNNs. Grey area shows the unfeasible solution space for the adopted MCU, i.e., FLASH footprint $> 2MB$                                  |

## List of Tables

| 2.1  | Notation adopted for the main variables and parameters of the memory allocation problem                                                                                                                           | 23 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Taxonomy of the existing heuristic algorithms proposed as memory allocators for CNNs. ↓ indicates decreasing sorting order, whereas ↑ ascending sorting order                                                     | 25 |

| 2.3  | Overview of the six hand-crafted CNNs adopted as benchmarks.                                                                                                                                                      | 32 |

| 2.4  | Overview of the 845 NAS-Bench-101 CNNs adopted as benchmarks.                                                                                                                                                     | 33 |

| 2.5  | Memory pool size $(H)$ in MB and execution time (Time) in s for different allocation algorithms. Solutions achieving optimal memory $(H=H_{\min})$ are highlighted in bold                                        | 33 |

| 2.6  | Percentage of optimal solutions, average and maximum overhead (Avg. Ovhd. and Max. Ovhd.), Worst-Case Execution Time (WCET) and Average-Case Execution Time (ACET) for each algorithm over the NAS-Bench-101 CNNs | 35 |

| 2.7  | Taxonomy of related works                                                                                                                                                                                         | 40 |

| 2.8  | Memory saving and computational overhead for $\alpha = \alpha_{opt}$ and $n\_slices = \{2h, 2w\}. \dots \dots \dots \dots \dots \dots \dots \dots$                                                                | 47 |

| 2.9  | Computational overhead and memory saving for the optimal setting of $n\_slice$ when $\alpha = \alpha_{opt}$                                                                                                       | 48 |

| 2.10 | Baseline Characterization. Accuracy on ImageNet taken from tensorflow repositories <sup>1</sup>                                                                                                                   | 53 |

List of Tables xiii

| 3.1  | Evaluation metrics. $y$ denotes the predicted depth, $y^*$ the ground-truth depth. N represents the amount of valid pixels in the ground-truth depth map                                                                                                                                                                  | 61  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2  | Experimental results concerning depth estimation accuracy. Comparison between original PyD-Net [122] (FP32) and optimized architectures at different resolutions                                                                                                                                                          | 73  |

| 3.3  | Non-functional metrics of PyD-net at different resolutions and precisions on ARMv7-A                                                                                                                                                                                                                                      | 75  |

| 3.4  | Proxy labels accuracy on the test set of KITTI dataset [56] using the split of Eigen et al. [105], maximum depth set to 80m. $$                                                                                                                                                                                           | 87  |

| 3.5  | Ablation study on the test set of KITTI dataset [56] using the split of Eigen et al. [105], maximum depth set to 80m                                                                                                                                                                                                      | 88  |

| 3.6  | Quantitative evaluation on the test set of KITTI dataset [56] using the split of Eigen et al. [105] with maximum depth set to 80m. Methods with * run post-processing [95]                                                                                                                                                | 90  |

| 3.7  | Quantitative evaluation on the test set of KITTI dataset [56] using the split of Eigen et al. [105] with maximum depth set to 80m                                                                                                                                                                                         | 90  |

| 3.8  | Evaluation of $\mu PyD$ -Net and quantized variants at different ranges. Comparison with state-of-the-art [114] on the same ranges.                                                                                                                                                                                       | 92  |

| 3.9  | Quantitative evaluation on Make3D dataset [107]                                                                                                                                                                                                                                                                           | 93  |

| 3.10 | Extra-functional metrics of $\mu PyD$ -Net at different input resolutions on the NUCLEO-F767ZI board                                                                                                                                                                                                                      | 95  |

| 4.1  | Number of parameters (# Params) and multiply&accumulate operations (# MACs) of the most common encoders and PyD-net encoder                                                                                                                                                                                               | 105 |

| 4.2  | Error metrics and accuracy scores on the KITTI raw data using the Eigen split [105] at different scales and precision options. For each resolution, the first row refers to PyD-Net trained with the single-scale loss [96]. The best results at each resolution are highlighted in bold, while the absolute bests in red | 107 |

xiv List of Tables

| 4.3 | Quantitative evaluation of KITTI test set using the split of Eigen et al. [105] with maximum depth set to 80m |

|-----|---------------------------------------------------------------------------------------------------------------|

| 4.4 | Accuracy results. Best results for each sparsity level are highlighted in bold                                |

| 4.5 | Storage footprint of ResNet9 trained on Cifar100 and MobileNetV1 trained on CIFAR10                           |

| 4.6 | SSD-MobileNetV2. Best results for each sparsity level are highlighted in bold                                 |

## Chapter 1

## Introduction

#### 1.1 Context and Motivation

The field of Deep Learning (DL), and more specifically a class of DL algorithms, the Deep Neural Networks (DNNs), has achieved astonishing results in the last decade. In 2015, a Deep Convolutional Neural Network (CNN) architecture, ResNet, achieved super human-level accuracy in the ImageNet classification task [1]. Only one year later, in 2016, a DL-based agent named AlphaGo won against the world champion Lee Sedol in the game of Go [2], and in 2018, the challenging task of translating a Chinese text to English was performed automatically by a DNN with human-level performance [3]. Thus, DNNs have become the standard backbones of data reasoning tasks in many different domains, like image and video processing [4], speech recognition and translation [5], and sensor data analysis [6].

Traditionally, DL-based applications have been deployed in cloud infrastructures running on large-scale datacenters, where both DNN training and inference are performed on powerful devices [7]. However, the proliferation of mobile and Internet-of-Things (IoT) applications has recently demanded moving the inference process from the cloud to "the edge", that is, on lightweight resource-constrained embedded systems. The need for high levels of user privacy, low latency, and low-cost requirements represent the main driving factors of such a paradigm shift. For example, the users of a healthcare application dealing with biometric information may have privacy concerns in sending their

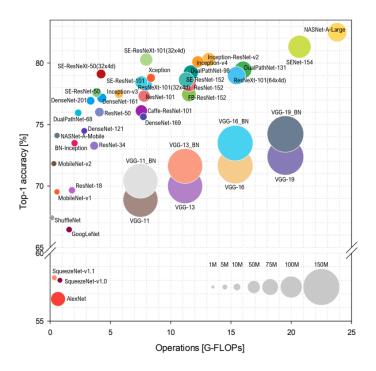

Fig. 1.1 Top-1 accuracy on ImageNet [8] vs. number of floating point operations (FLOPs) vs. model size. Image taken from [9].

data to the cloud. Applications relying on real-time sensing of the environment to perform fast decision-making, such as autonomous driving and augmented reality, cannot sustain the round-trip latency of the data transfer to the cloud. Finally, in the case of IoT applications based on a large-scale sensor network, the cost of transmitting data to a centralized server is simply unaffordable. Processing the DNN inference on-device guarantees higher levels of user privacy, as data stay local, and higher quality of service, as latency is much more deterministic. Moreover, the network congestion and the volume of data exchanged are highly reduced, lowering energy consumption and cutting down the infrastructure cost for distributed applications.

However, modern DNNs require massive computing power and considerable memory resources, making their deployment on resource-constrained embedded systems very challenging. Fig. 1.1 shows the relationship between the Top-1 classification accuracy on the ImageNet dataset and the computational and memory intensity for different DNN architectures. Most models require tens of GFLOPs and hundreds of MBs to achieve high accuracy. Unfortunately, mobile and IoT systems are usually battery-powered, with severe thermal, area,

and power constraints that limit the number of computational units and the on-chip memory resources. Therefore, bringing intelligence to such systems relies on the availability of small, fast, and energy-efficient DNNs.

This dissertation stems from the idea that the key to small, fast, and energy-efficient DNNs is vertical and automated optimizations across the entire software stack. Optimizations must act vertically across the different layers to holistically combine the benefits of specialization, from the algorithmic and neural architecture design process to compiler passes and computational strategies. Such a cross-layer approach not only can bring more remarkable gains but also allows the non-functional figures of merit to be co-optimized with the model accuracy. Optimizations must be automated to free embedded designers from the burden of manually dealing with the wide variety of DNN architectures used in different tasks and with the diversity of embedded platforms employed at the edge. Toward this goal, this dissertation presents a set of novel automated optimization techniques working across different levels of the software stack to improve the efficiency of DNNs on embedded systems. Specifically, this dissertation focuses mainly on CNNs as they were the dominant DNN architecture when the works presented here were developed. As the main outcome, the works presented in this thesis contribute to the state-of-the-art by pushing further the boundary of accurate CNNs that can be deployed on tiny embedded devices.

This chapter first discusses the optimization challenges involved in deploying DNNs on embedded systems, also introducing the minimal background needed to understand the rest of the dissertation (Section 1.2). Then, it introduces the main contributions of our research, together with the overall organization of the dissertation (Section 1.3).

### 1.2 Neural Network Optimization Stack

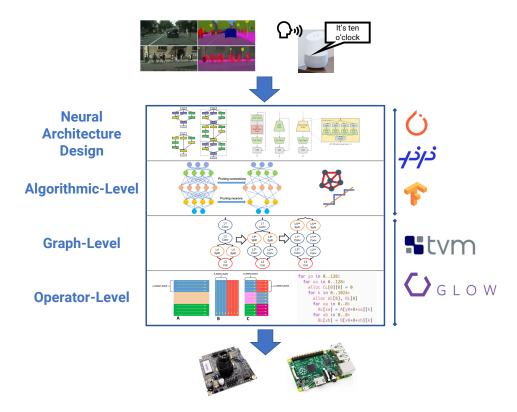

As shown in Fig. 1.2, the DL design, optimization, and deployment stack is usually structured in four main layers. At the highest level stands the neural architecture design process. This step aims at designing efficient DNN architectures, and it is usually carried out in a DL framework, like PyTorch [10], Tensorflow [11], or Paddle Paddle [12], together with other learning-related

Fig. 1.2 DNN optimization stack.

steps, such as data preparation, data preprocessing, and training. Then, further optimizations can be performed at algorithmic-level by exploiting the intrinsic redundancy of DNNs and the statistical nature of DL. At this point, the trained and optimized model is fed as input to a DL compiler, like TVM [13] or GLOW [14]. Such compilers first translate the DL model into a high-level computational graph representation, then apply graph-level rewritings to generate an optimized graph, and finally perform operator-level optimizations to generate efficient code for each operator of the graph. This section briefly describes each layer of the stack, introducing the main optimization passes.

### 1.2.1 Neural Architecture Design

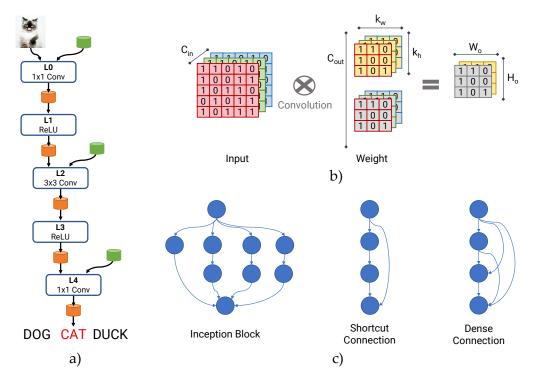

In its general embodiment, a DNN is a graph of tensor operators called *layers*. Fig. 1.3a reports an example of a generic DNN. A layer operates on one or multiple activation tensors, which are either fed as inputs to the network, e.g., the input image to classify, or are produced by previous layers — the orange

Fig. 1.3 a) A pictorial representation of a DNN; b) main parameters of a convolutional layer; c) three common neural modules.

boxes in Fig. 1.3a. The most commonly-used DNN layers are the convolutional, the fully connected, and the neural activation layers, like ReLU, Leaky ReLU, and Sigmoid. Apart from the activation tensors, the convolutional and fully-connected layers also accept one other tensor as input, usually called the weight tensor — the green boxes in Fig. 1.3a. The weight tensors are learned during the training phase but are constant during the inference stage.

In general, a DNN architecture is defined by the types and number of layers, the graph topology, and the dimensions of each layer. From Fig. 1.1, it is evident that different DNN architectures set a different trade-off in terms of accuracy, computational complexity, and model size. For this reason, several manual [15, 16] or automatic [17, 18] design methodologies have been recently proposed to find the DNN architecture that maximizes the accuracy while meeting latency, storage, or energy efficiency constraints. The following paragraphs introduce the main architectural parameters, highlighting their effect on performance.

#### Kernel size

A convolutional layer is defined by the number of input channels  $(C_{in})$ , the number of output channels  $(C_{out})$ , also called filters, and the kernel size  $(k_h \times k_w)$ , also called the receptive field. All these parameters contribute to the computational complexity (FLOPs  $\propto 2 \cdot H_{out} \cdot W_{out} \cdot k_w \cdot k_h \cdot C_{in} \cdot C_{out}$ , where  $H_{out}$ and  $W_{out}$  are height and width of the output activation tensor) and to the parameter count ( $|W| \propto k_w \cdot k_h \cdot C_{in} \cdot C_{out}$ ). A pictorial representation of a convolutional layer and its parameters is shown in Fig. 1.3b. Early CNN architectures, like AlexNet [19] or InceptionNet [20], used various kernel sizes, from  $3\times3$  and  $5\times5$  up to  $11\times11$ . However, the authors of VGG [21] demonstrated that convolutional layers with smaller receptive fields but more activation layers outperform architectures with bigger receptive fields. Thus, VGG [21] replaces the large convolutional kernels used in AlexNet with multiple  $3\times3$  convolutional layers stacked together. Moreover, VGG also features 1×1 convolutions to increase the number of layers, hence the nonlinearity of the model, with a small computational cost. For this reason, virtually all modern CNN architectures adopt small filter sizes, namely,  $1\times1$  and  $3\times3$ , to reduce both the computational complexity and the parameter count.

#### Depth

The depth of a network refers to the maximum number of layers traversed from the primary inputs to the primary outputs. Increasing the depth of the network enlarges the learning capacity of the model and hence allows the model to achieve higher accuracy [21]. However, it is intuitive that having more layers increases the computational cost and the number of parameters. Moreover, the training of very deep networks is rather challenging, as it suffers from stability issues due to the gradient vanishing during backpropagation [1]. The authors of InceptionNet [20] addressed such issues by having multiple auxiliary classifiers present in different parts of the model at training time and by adopting a more complex topology with parallel layers (see Fig. 1.3c). The authors of ResNet [1], instead, tackled the gradient vanishing problem by introducing the shortcut connection, which is a by-pass connection summing two tensors at different depths of the network (see Fig. 1.3c). The shortcut connection

allows very deep networks with hundreds of layers to be trained. Other recent works have proposed to modulate at run time the number of layers traversed using attention modules or gating blocks [22], possibly with the addition of intermediate classifiers called early-exit branches [23]. In this case, the latency of the DNN can be tuned at run time based on the difficulty of the inputs or on some external user-defined constraints, but at the cost of storing additional weights for the auxiliary modules.

#### Width

The width of the model refers to the number of filters of the convolutional layers  $(C_{out} \text{ in Fig. 1.3b})$ . Reducing the number of convolutional filters lowers the size of the activation tensors, the number of parameters, and the computational complexity. Playing with the width of the convolutional layers is a simple but powerful architectural design trick, and it can be combined with other knobs to be even more effective. For example, the bottleneck module, proposed in InceptionNet [20] and ResNet [1], has become a standard module in modern CNNs. The bottleneck module comprises three stacked  $1\times1$ ,  $3\times3$ , and  $1\times1$ convolutional layers (see Fig. 1.3a). The first  $1\times1$  convolutional operation lowers the number of channels to alleviate the computational load of the intermediate  $3\times3$  layer. Then, the last  $1\times1$  layer recovers the original number of channels. Similar architectural tricks have been used in other efficient CNN architectures targeting embedded systems such as MobileNet [15] and SqueezeNet [16]. The pioneering work by Howard et al. [15] proposed to scale the number of filters across all the layers according to a predefined ratio  $\alpha$ , called the width multiplier [15]. In this way, different CNNs can be built starting from the same architectural template, which can be resized depending on memory and performance requirements. Follow-up works, e.g., Slimmable Networks [24], have elaborated on the concept of width scaling, enabling its use at run time to dynamically tune the latency of the model.

#### Resolution

The resolution of the intermediate feature maps is another important architectural knob ( $H_{out}$  and  $W_{out}$  in Fig. 1.3b). High-resolution feature maps

may contain fine-grain details, which help achieve high accuracy. However, processing high spatial resolution tensors significantly affects the computational complexity and the run-time working memory needed to process the network. For this reason, CNN architectures use pooling layers or the stride parameter of the convolutional layers to reduce the spatial resolution of the network. For instance, in CNN architectures for classification tasks, to balance the overall computational workload, the first layers operate on high-resolution feature maps with a small number of channels, whereas the last layers operate on low-resolution feature maps with a large number of channels. Scaling the resolution of the input tensors fed to the network [15] represents another way of controlling the resolution of the network. For this reason, similarly to the width multiplier, Howard et al. [15] proposed to scale the resolution of the input using a predefined ratio  $\rho$ , called the resolution multiplier, to build a family of CNNs from the same architectural template.

#### **Graph Connectivity**

While early CNN architectures, like AlexNet [19] and VGG [21], relied on a linear sequential topology, where all layers are stacked on top of each other, more recent CNN architectures have adopted more complex topologies to achieve higher accuracy with fewer parameters and fewer computations. For example, Fig. 1.3c shows the inception block with 4 parallel branches used in InceptionNet [20], the skip connection used in ResNet [1], and the skip connection added between all convolutional layers used in DenseNet [25]. Playing with the graph connectivity to improve the overall performance of the model has been largely used in automatic neural architectural design algorithms, e.g., [26]. Such algorithms are, in fact, usually formulated as search optimization algorithms aimed at finding the best connectivity among a pool of basic modules, like the one previously described, that maximizes the accuracy of the model under latency or memory constraints.

### 1.2.2 Algorithmic-level Optimizations

Once the neural architecture has been fixed, additional optimizations can be performed at the algorithmic level. There are two main techniques in this

space: *pruning*, aimed at removing the redundant parameters of the network, and *quantization*, aimed at reducing the complexity of the network through the use of low-precision arithmetic.

#### Pruning

Based on the assumption that DNNs are over-parametrized, pruning strategies aim to seek and remove the weights with a negligible contribution to the accuracy of the model. The existing methods differ in the policy used to identify the less important weights and the level of granularity at which they are applied [27]. In terms of policy, even if complex methods have been recently proposed, e.g., gradient or Hebbian-based methods [28], the magnitude-based [29] are the preferred option in many modern training pipelines due to the ease of their implementation. For what concerns the granularity, there exist three main classes. Unstructured pruning plays at the lowest level, namely, on the individual weights of the model [30], providing a high degree of flexibility to the learning process of the sparse model. Such flexibility comes at the cost of more complex processing for the remaining non-zero elements. Specifically, since non-zero elements are scattered across the tensor, they induce irregular data reading, processing, and writing patterns, which could be challenging to efficiently manage in systems with a cache-based memory hierarchy or wide SIMD compute units. Therefore, fully exploiting such unstructured sparsity necessitates additional hardware mechanisms to extract, communicate, and compute only with the non-zero elements [31]. At a coarser granularity, Block pruning techniques [32] group neighboring weights in specific patterns to decrease the indexing overhead and to ease the adoption of sparse compute kernels on general-purpose cores [33, 34]. At the coarsest level, Filter pruning drops entire convolutional filters [35], achieving aggressive storage savings and speed-up at the cost of substantial accuracy loss due to fast information removal.

#### Quantization

Pioneering works have shown that a 32-bit floating-point representation of weights and activations is redundant at inference time [30]. In fact, for many

tasks, existing DNNs can be quantized to a fixed-point representation with 16-bit or 8-bit integers [36] with no or minimal loss on the accuracy. More recent works have also proposed more extreme quantization, i.e., using 2 bits in ternary DNNs [37], or even 1 bit in binary DNNs [38]. However, ternary and binary DNN still suffer from a substantial accuracy drop, depending on the application and the network topology. In general, floating-point numbers can be discretized using either linear or non-linear schemes, as investigated over the years in the field of classic Digital Signal Processing (DSP). According to the linear scheme, the distance between two adjacent fixed-point values, called the quantization step, is constant across the entire input value range. Then, the mapping between real and integer values can be symmetric, if the integer distribution is centered around zero, or asymmetric, if it is shifted by a given offset. The first choice is simpler to implement, whereas the second can fit better the original floating-point value distribution but at the cost of additional processing stages to manage the offset at run time. Finally, the scaling factor used in the mapping can be a power-of-two, an arbitrary floating-point factor, or a fixed-point one. The former requires simple shift operations to be implemented [39], whereas the latter might be more accurate but at the cost of additional and more complex operations [40]. In the case of non-linear quantization, a non-linear function is used to map the real value range in the discrete set of integer values. Common approaches use logarithmic functions [41] or more complex clustering procedures [30]. Non-linear quantization schemes shine when the original data distribution is highly non-uniform. Obviously, their implementation introduces additional overhead, requiring more complex procedures to perform arithmetic operations between quantized numbers. Another key aspect for quantizing DNNs is the granularity of the quantization. Coarse-grain approaches [42] use the same fixed-point format for all the layers of the DNN, whereas more fine-grain approaches tune the format per-layer or per-channel [43]. Hybrid strategies may use a static bit-width for the whole model and a per-layer or per-channel fixed-point scaling factor [44]. Unfortunately, a one-size-fits-all solution does not exist, and so the quantization scheme to adopt depends on the task, the specific DNN architecture, the underlying hardware characteristics, and the latency and memory constraints.

#### 1.2.3 Graph-level Optimizations

Early machine learning frameworks, like Caffe [45], simply iterated over the layers of the DNN to perform the inference stage. Unfortunately, this node-visitor processing method is inefficient, as it misses several optimization opportunities. As a result, modern machine learning frameworks, like PyTorch [10] and Tensorflow [11], hand over the DNN graph to domain-specific DL compilers [46, 14, 13], which perform a series of optimization passes to make the inference process on the target hardware more efficient.

When a DNN model is loaded into a DL compiler, it is first translated into a high-level Intermediate Representation (IR), which usually corresponds to a Dataflow Graph Representation (DFG). Several optimization passes are applied at this level to orchestrate the flow of macro operations, rather than the implementation of the single layer, i.e., the internal code organization. Such passes remove, modify, or add nodes to the graph while preserving the overall functionality. The following paragraphs briefly review the main graph-level optimization passes proposed in the literature, while the reader can refer to [47] for a more detailed overview.

#### Node simplification

These optimizations simplify one or more nodes to reduce the computational workload [48] or the memory requirements [49]. Such simplifications exploit the algebraic rules, namely, commutativity, associativity, and distributivity, in the case of linear algebra operators, or hand-written rewriting rules in the case of DL-specific operators, e.g., reshape, transpose, and pooling operations. Additional simplifications can be performed extending classic compiler optimizations, such as common sub-expression elimination (CSE) and dead code elimination (DCE), to work on the graph IR.

#### Layout assignment and transformation

The data layout assignment pass aims at finding the best data layouts for storing the intermediate activation tensors, adding layout transformation nodes if necessary. As data layouts of the input and output tensors have a considerable

influence on the final performance of an operator and the transformation operations may add significant overhead, the layout assignment is a challenging problem, which has been tackled either through heuristic [46, 14] or search-based algorithms [50].

#### Static memory allocation

As virtually all DNNs have static shapes, the memory allocation step can be entirely carried out at compile time. Specifically, one contiguous memory region, called the memory pool, is allocated and partitioned through a simple offset assignment to obtain the memory buffers for all the concurrently active tensors. The static memory allocation is usually formulated as an optimization problem aimed at finding the placement of the memory buffers in the pool that minimizes the overall memory requirement. Additional memory optimizations could be performed by reusing the same memory for both the input and the output tensors of an operation, usually known as the in-place optimization, and by scheduling the nodes such that the peak activation memory footprint is minimized [49].

### 1.2.4 Operator-level Optimizations

Once the graph-level optimizations have been performed, DL compilers usually lower the graph-level IR into a low-level IR to perform additional hardware-specific optimizations. Specifically, a series of passes are used to optimize the implementation of each operator, i.e., each node of the graph. The commonly applied passes include hardware-intrinsic mappings, memory latency hiding, parallelization, and loop-oriented optimizations, like loop tiling, loop reordering, and vectorization. Operator-level passes are usually highly specialized for the target platform, as different hardware architectures may require different implementation choices. Code optimizations can be performed automatically by the compiler using code generation techniques based on auto-scheduling, e.g., using the polyhedral model [51], or on auto-tuning [52]. Alternatively, the compiler can map the operators of the graph on the most suitable implementation extracted from highly-optimized libraries provided by the hardware vendors, e.g., cuDNN [53], ARM Compute Library [54], CMSIS-NN [39].

Note that there also exist some optimizations spanning multiple levels of the stack. For example, operator fusion bridges the graph-level and the operator-level of the stack by combining multiple operators into one. Operator fusion eliminates intermediate allocations and reduces memory bandwidth requirements, launch, and synchronization overhead. TVM [13] and BrainSlug [55] perform operator fusion based on pre-defined fusion rules, whereas Tensor comprehensions [51] exploits the polyhedral representation. However, how to identify and fuse more complicated sub-graphs is still an open challenge, especially considering its interaction with other optimization passes, such as layout assignment and tensor rematerialization [50].

## 1.3 Objectives and Contributions

This dissertation proposes to tackle the design and deployment of small, fast, and energy-efficient CNNs on embedded systems from a holistic system perspective. The objectives of this dissertation can be summarized as follows:

- Develop novel automated optimization techniques to reduce the memory footprint, lower the inference processing time, and increase the energy efficiency of state-of-the-art CNNs with minimal to no accuracy loss.

- Devise dynamic knobs to extend the achievable accuracy-complexity trade-off of a CNN at run time while still fulfilling the strict compute and memory constraints of embedded platforms.

- Demonstrate that the combination of different optimizations working across multiple levels of the optimization stack opens up new regions of the solution space, pushing further the boundary of accurate CNNs that can be deployed on embedded devices.

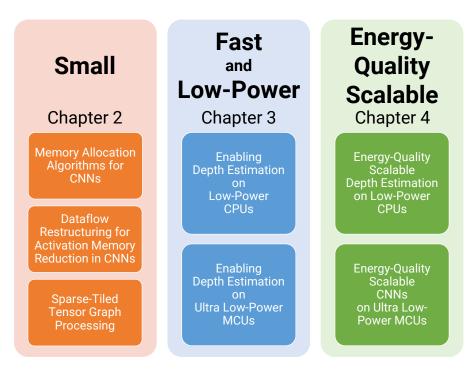

Fig. 1.4 shows the organization of the thesis, which is divided into three main chapters, each one focusing on a specific optimization objective.

Chapter 2 focuses on how to build *small* CNNs, i.e., on memory-driven optimizations. First, it reviews the problem of memory allocation in DL compilers, surveying the most adopted problem formulations and presenting a

Fig. 1.4 Pictorial representation of the dissertation outline.

quantitative assessment of the underlying optimization methods. The results collected over 851 benchmarks reveal that the most recent heuristics integrated into state-of-the-art compilers often fail to achieve the global optimum, with a substantial memory penalty (up to 33.6%). On the other hand, a mixedinteger linear programming method finds the optimal solution with a negligible run time (1.69s on average). Such findings suggest the need to revisit the dominant trends in memory allocation for CNNs, shifting the focus of memory optimization on higher levels of the optimization stack (see Fig. 1.2). To this end, the second part of the chapter introduces a novel, automated method for minimizing the memory footprint of the intermediate activations of a CNN. Specifically, the proposed technique relies on graph-rewriting rules, which exploit algorithmic-level characteristics of CNNs, namely, the spatial locality of tensor operators and the change of the spatial resolution across the layers, to lower the activation memory footprint without affecting the functionality. Results collected on a representative class of different CNN architectures show that the proposed method is widely applicable and highly effective, achieving remarkable memory savings (62.9% on average) with low computational overhead (8.6% on average). The last part of the chapter presents a new compression pipeline, which plays at the algorithmic level by pruning the unimportant weights of the network and at the graph level with the dataflow restructuring technique to reduce both weights and activations footprint with minimum accuracy loss. The collected results reveal that the proposed pipeline opens up a new feasible region of the memory-accuracy solution space, showing fast configurations of MobileNets deployed at full scale on tiny MCU devices, like an ARM M7 core equipped with 512KB of RAM and 2MB of FLASH memory.

Chapter 3 focuses on how to build fast CNNs suitable for tackling challenging inference tasks on low-power devices like ARM Cortex-A CPUs and ARM Cortex-M MCUs. In this chapter, we present an end-to-end optimization framework based on neural architectural design, quantization, and optimized integer kernels. The framework is evaluated in the context of a key use case for embedded computer vision, namely, monocular depth estimation, to demonstrate the importance of a vertical approach when targeting stringent application and hardware constraints. Specifically, we first introduce a comprehensive design and optimization framework aimed at accelerating the inference of PyD-Net, a lightweight CNN capable of achieving close to state-of-the-art accuracy with ultra-low resource usage. The accuracy driven optimization framework combines a hardware-friendly fixed-point quantization method with integer neural kernels custom-tailored to the specific target platform. The experimental evaluation performed on a multi-core ARM Cortex A53 CPU shows marginal accuracy loss on the KITTI dataset [56] with 16-bit (8-bit) integers, latency reduction up to  $1.16 \times (1.64 \times)$ , and memory footprint reduction up to  $2 \times (4 \times)$ compared to single-precision floating-point. The second part of the chapter deals with the scaling of monocular depth estimation "at the very edge", i.e., on tiny MCU-powered platforms. In particular, it introduces  $\mu$ PyD-Net, a lightweight CNN vertically designed to be deployed on microcontrollers. The neural architecture design process of  $\mu$ PyD-Net is driven by the need to meet hard memory and latency constraints. At the algorithmic level, the network is trained in a peculiar self-supervised manner, leveraging proxy labels obtained through a traditional stereo algorithm, and is quantized to 8-bit data. At the operator level, the network is mapped to low-level layers custom-tailored to the target microcontroller architecture. Experimental results on standard datasets and an in-depth evaluation with an ARM Cortex-M7 MCU prove the feasibility

of obtaining sufficiently accurate monocular depth cues even on ultra low-power microcontrollers.

Chapter 4 focuses on the deployment of energy-quality scalable CNNs on embedded systems. Specifically, this chapter builds upon the idea that by leveraging the error resilience of many real-life applications, the quality-ofresult can be gracefully degraded at run time to achieve higher energy efficiency, depending on the specific task, the external context, or the battery level. The first part of the chapter describes and characterizes an energy-quality scalable system for monocular depth estimation, named EQPyD-Net. It describes the architecture of the CNN and the optimization flow, covering the knobs that enable the dynamic scaling, namely, the scalable neural topology and the variable arithmetic precision of the custom operators. Tested on an offthe-shelf ARM Cortex A53, EQPyD-Net can be shifted across five operating points, ranging from a maximum accuracy of 82.2% on the KITTI dataset with 0.4 Frame/J up to 92.6% of energy savings with 6.1% of accuracy loss. Nevertheless, EQPyD-Net still has a minimal memory footprint of 5.2 MB for the weights and 38.3 MB (in the worst-case) for the run-time processing. The second part of the chapter introduces jointly-designed training and compression techniques to build Nested Sparse CNNs, a class of dynamic CNNs suited for inference tasks deployed at the edge of the IoT. A Nested Sparse CNN consists of a single CNN containing N sparse sub-networks with nested weights subsets, like a Matryoshka doll, and can trade accuracy for latency at run time, using the model sparsity as a dynamic knob. When tested on image classification and object detection tasks on an off-the-shelf ARM-M7 Micro Controller Unit (MCU), Nested Sparse CNNs outperform dynamic solutions naively built assembling single sparse models and state-of-the-art dynamic strategies, like dynamic pruning and layer width scaling.

Finally, Chapter 5 concludes the dissertation, summarizing the main findings of our research.

## Chapter 2

## Memory Optimizations for Convolutional Neural Networks

#### 2.1 Introduction and Motivation

As discussed in chapter 1, the quest for CNNs that can be deployed on a wide variety of embedded architectures has accelerated the development of multi-stage pipelines where not just accuracy but also non-functional metrics, such as energy consumption, latency, and memory footprint, play as concurrent variables to optimize. Among all performance factors, the memory footprint of a CNN represents one of the biggest concerns as memory is the most expensive hardware resource. Specifically, the memory cost of a CNN is split among two components: weights and activations. The weight footprint depends on the number of parameters of the network, whereas the activation footprint depends on the memory needed to store the intermediate results, i.e., the feature maps produced during the inference process.

While reducing the number and the bitwidth of the learned weights has been treated initially as the crucial (and in many cases the only) aspect of the memory optimization problem, lowering the activation footprint has lately become even more critical. There are three main factors behind this new trend. First, CNNs have been successfully applied to novel applications, like image demosaicing [57] or depth estimation [58], where the feature maps resolution is much higher than that required by image classification tasks. Second, hardware-aware auto-ML

tools have become more commonly used to design efficient but irregular neural architectures [59] where the weight-to-activation ratio has reduced substantially. For instance, SwiftNet [60], one of the winning submissions of the Visual Wake Words competition [61], occupies 250 KB for the weights and 200 KB for the activations<sup>1</sup>. Third, off-the-shelf MCUs used in many IoT systems (such as the ARM Cortex-M cores [62]) are characterized by minimal memory resources: 1–2MB of FLASH for storing the weights of the model and tens to hundreds of KBs of on-chip SRAM to store the feature maps. The availability of such few memory resources results in strict constraints that must be satisfied to make the deployment of a CNN feasible on an MCU-powered device. Moreover, the available memory to reserve for the CNN inference can be further reduced due to other routines running concurrently on the same device.

In order to reduce the memory footprint of a CNN, several techniques have been proposed in the last few years, and they can be divided into two main categories: data-driven and data-independent. The data-driven techniques attack the problem by leveraging the statistical nature of DL, and hence they usually work at the neural architectural design and algorithmic level of the stack (see Section 1.2). Lightweight neural architectural design [16], resolution and topology scaling [15], quantization to low-precision integers [40, 63], and weight pruning [33, 64], represent the most adopted and effective optimization strategies belonging to this category. Such techniques require access to the training data as they must be embedded in the training procedure, they are model- and taskdependent, and, in some cases, they may cause an unrecoverable accuracy loss. On the other hand, data-independent methods tackle the memory reduction problem from a computational perspective, namely, applying data-independent transformations during the compilation pipeline, and hence they work at the graph- and operator-level of the stack (see Section 1.2). For instance, they play with the scheduling of the tensor graph [49], or with the layout of the tensor operators [65]. Data-independent techniques are training-free, hence model- and task-agnostic, and can be superimposed to data-driven optimizations without any accuracy loss.

This chapter first surveys the optimization algorithms adopted in several state-of-the-art DL compilers to solve the memory allocation problem (Sec-

<sup>&</sup>lt;sup>1</sup>https://github.com/newwhitecheng/vwwc19-submission

tion 2.2). Then, it introduces a novel data-independent technique, named the dataflow restructuring, that performs a functionality-preserving, automated graph restructuring procedure to reduce the activation memory requirements of a CNN (Section 2.3). Finally, it presents a novel memory optimization pipeline that combines data-driven DL techniques with a data-independent technique, the dataflow restructuring, to enable the deployment of accurate CNNs on tiny devices powered by MCUs (Section 2.4).

The content of this chapter is an extended, improved version of our previous publications found in [66, 67].

### 2.2 Memory Allocation Algorithms for CNNs

#### 2.2.1 Motivation

Memory allocation is a crucial pass in any compiler infrastructure, but it is even more critical when memory-intensive workloads, such as CNNs, are deployed on resource-constrained embedded devices. Achieving the optimal memory allocation is, in fact, paramount as even a small overhead may prevent the deployment of a given CNN. In the case of CNNs with static shapes, one contiguous region of the memory, referred to as the memory pool, is reserved at initialization time and statically partitioned to make space for the input and output tensors of each layer. Specifically, partitioning the memory pool involves assigning to each tensor an offset address, which defines the portion of the pool reserved for the tensor during its lifetime. Since tensors are accessed by a limited number of layers scheduled sequentially, the memory space assigned to a tensor can be reused over time to store other non-conflicting tensors. Therefore, in ML compilers, the memory allocation step usually takes the form of an optimization problem aimed at finding the placement of tensors in the memory pool that minimizes its size.

Some recent works [68–72] have addressed the problem by proposing and implementing different greedy heuristics, some of which had also been integrated into commercial inference engines (e.g., TensorFlow Lite [73], PyTorch Mobile [74], Arm NN [75], and ONNC [76]). Unfortunately, these heuristics were validated on simple hand-crafted CNNs with a regular linear graph topology.

However, more recent studies in DL theory have promoted an emerging class of CNNs generated via Automated Machine Learning (AutoML), e.g., Neural Architecture Search [77]. AutoML CNNs achieve higher accuracy with fewer weights and fewer operations than hand-crafted models, guaranteeing better performance with fewer hardware resources, particularly memory. However, they also present an irregular graph topology characterized by complex connectivity, making the memory allocation problem much more challenging to solve efficiently in practice. Therefore, it is natural to ask whether prior heuristics can still achieve optimality as reported in the recent literature, and if not, how far they are from the global optimum. To this end, in this section:

- We review different formulations of the memory allocation problem introducing two widely adopted options. The first one relies on a constrained version of the two-dimensional strip packing problem; the second treats the memory allocation as a graph coloring problem.

- We survey existing algorithms proposed to solve the presented formulations. Our analysis includes both heuristic algorithms and an exact method relying on a MILP solver.

- Finally, we evaluate the discussed methods quantifying their efficiency in terms of memory minimization and processing time. The numerical results were collected from a large set of CNNs, including both hand-crafted and automatically generated architectures. About the latter, we picked 845 CNNs from the NAS-Bench-101 database [26] with different connectivity and depth (from 77 to 204 layers).

As the primary outcome, the experimental evaluation results demonstrate the sub-optimality of existing heuristic methods, currently the most common choice in standard tensor graph compilers, revealing substantial overhead (up to 33.6%) when tested on AutoML CNNs. Moreover, they empirically demonstrate that a MILP method can consistently achieve optimal solutions in a reasonable run time (1.69 s on average, 28.31 s in the worst case<sup>2</sup>).

<sup>&</sup>lt;sup>2</sup>On a standard CPU-based server machine.

#### 2.2.2 Problem Formulation

For memory allocation purposes, a CNN can be modeled as a DFG  $\mathcal{G}(T, E)$ , where  $T = \{t_i | i = 0, ..., N-1\}$  is the set of nodes representing the N tensors read and written at run time, and  $E = \{e_{i,j} | t_i, t_j \in T, i \neq j\}$  is the set of edges describing the dependencies among tensors. Fig. 2.1 shows the DFG for a simple CNN with six tensors. Each tensor  $t_i$  has a memory size  $h_i$  equal to the product of its cardinality with the adopted data type (e.g., 32-bit floating-point or 8-bit integer).

Fig. 2.1 On the left, the DFG representation of a CNN. In the middle, the topological order  $\sigma$  as a linearization of the DFG. On the right, the lifetime analysis and the active memory for the ordered DFG.

Inference engines for embedded systems, e.g., TensorFlow Lite [73] or PyTorch Mobile [74], process a CNN layer by layer sequentially, following a valid order obtained by a topological sort of the DFG. We denote the topological sort with the ordered set of tensors  $\sigma = (t_i|t_i \in T)$ , such that for any edge  $e_{i,j} \in E$ ,  $t_i$  precedes  $t_j$  in  $\sigma$ ; in Fig. 2.1,  $\sigma = (t_0, t_1, t_2, t_3, t_4, t_5)$ . For a given  $\sigma$ , the resulting lifetime  $w_i$  of each tensor  $t_i$  is the difference between its end- and start-time. The start-time  $x_i$  is defined as the position of  $t_i$  in the topological order  $\sigma$ , while the end-time is the start-time of its latest successor  $t_j$  ( $e_{i,j} \in E$ ).

Fig. 2.2 Example of a memory allocation for the sorted DFG reported in Fig. 2.1.

The end-time of the last tensor in  $\sigma$  defines the overall processing time W of the DFG (W = 6 for the example in Fig. 2.1).

As stated previously, each tensor  $t_i$  is placed in a contiguous memory region called the memory pool. Allocating a tensor  $t_i$  within the memory pool corresponds to defining its address offset  $y_i$ . The total size of the tensors concurrently alive within a given logical time sets the active memory, whereas the total memory footprint H is equal to the maximum active memory. Fig. 2.2 shows a possible memory allocation for the sorted DFG of Fig. 2.1, highlighting the main variables and parameters of the problem (also summarized for the sake of clarity in Tab. 2.1).

The memory allocated for a tensor can be freed once the tensor is not accessed anymore, and it can be used for hosting other tensors. For instance,  $t_4$  (starting at time 4) can reuse a fraction of the memory previously allocated for  $t_0$  (ending at logical time 3); the same is not valid for  $t_1$  or  $t_3$  which are alive together. Thus, the memory allocation involves the following optimization problem: search the optimal set  $\mu = \{y_i | t_i \in T\}$  that minimizes the memory footprint H while guaranteeing that the intersection between the memory regions of concurrently active tensors is empty.

The trivial solution is to place tensors into dedicated disjoint regions of the memory pool. The resulting memory pool size H is the sum of all the tensors size: this is the upper bound  $H_{\text{max}}$  in the solution space of the memory allocation problem ( $H_{\text{max}} = 88$  for the example of Fig. 2.1). The lower bound  $H_{\text{min}}$  is defined by the group of concurrent tensors with the highest memory

Table 2.1 Notation adopted for the main variables and parameters of the memory allocation problem.

| Notation                        | Definition                                |

|---------------------------------|-------------------------------------------|

| $N \in \mathbb{Z}^+$            | Number of tensors.                        |

| $T = \{t_0, \dots, t_{N-1}\}$   | Set of tensors.                           |

| $w_i \in \mathbb{Z}^+$          | Lifetime of tensor $t_i$ .                |

| $h_i \in \mathbb{Z}^+$          | Size of tensor $t_i$ (in bytes).          |

| $x_i \in \mathbb{N}$            | Start-time of tensor $t_i$ .              |

| $y_i \in \mathbb{N}$            | Memory offset of tensor $t_i$ .           |

| $W \in \mathbb{Z}^+$            | Total logical time.                       |

| $H \in \mathbb{Z}^+$            | Memory pool size.                         |

| $H_{\min} \in \mathbb{Z}^+$     | Theoretical lower bound of the pool size. |

| $H_{\max} \in \mathbb{Z}^+$     | Upper bound of the pool size.             |

| $\sigma$                        | Topological order of the tensors.         |

| $\mu = \{y_0, \dots, y_{N-1}\}$ | Memory allocation.                        |

demand ( $H_{\text{min}} = 48$  in Fig. 2.1).  $H_{\text{min}}$  can be easily computed from the result of the liveness analysis. In general,  $H_{\text{min}}$  depends on the topological order  $\sigma$ , and many topological orders may exist for a given DFG. For instance, in Fig. 2.1 an alternative topological order is  $\sigma = (t_0, t_2, t_4, t_1, t_3, t_5)$  with  $H_{\text{min}} = 56$ . In our study, we consider the topological order as an input, and all the algorithms under analysis are compared using the same topological order (more details in Section 2.2.4).

Since most CNNs are static and the size of each tensor is fixed, the memory allocation problem can be solved at compile time before deploying the model on the target device. Then, the obtained memory offsets can be off-loaded into the target device in the form of a table, which is used at run time during the processing of the CNN.

#### 2.2.3 Memory Allocation Algorithms

In this subsection, we first describe the formulation based on the two-dimensional strip packing problem and the related optimization strategies. Then, we present the graph coloring formulation, showing its intrinsic limitations.

#### 2D Strip Packing Formulation and Methods