Doctoral Dissertation Doctoral Program in Electrical, Electronics and Communications Engineering (30<sup>th</sup>cycle)

# Power Management Circuits for Front-End ASICs

### **Employed in High Energy Physics Applications**

By

Junying Chai

\*\*\*\*\*

#### Supervisor(s):

Prof. A. Rivetti, Supervisor Prof. S. Marcello, Co-Supervisor Dr. M. Da Rocha Rolo, Co-Supervisor

#### **Doctoral Examination Committee:**

Prof. Valerio.Re, Referee, University of Bergamo, ItalyProf. Michela.Chiosso, Referee, University of Turin, ItalyProf. E.F, University of...Prof. G.H, University of...Prof. I.J, University of...

Politecnico di Torino 2018

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Junying Chai 2018

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my loving parents Dongwen Chai and Fengzhi Zhao, my loving wife Yanying Zheng, my loving son Haoze Chai and the imminent child.

### Acknowledgements

I would like to acknowledge my tutors, my colleagues and my friends.

My gratitude is sincere.

Marco Maggiora helped me driving my work at the INFN Torino in Italy.

Angelo Rivetti, one of my supervisor, guided my doctoral project and research direction.

Simonetta Marcello, as one of my supervisor gave me a lot of help in my study in Politecnico and my life in Italy.

Mannel Rolo, as one of my supervisor appreciated me to improve my skills in developing analogue electronics and gave me good advices.

I also thank Ennio, Gianni, Lino, Huashen, Chongyang who gave me many help in my study and research.

#### Abstract

The instrumentation of radiation detectors for high energy physics calls for the development of very low-noise application-specific integrated-circuits and demanding system-level design strategies, with a particular focus on the minimisation of interference noise from power management circuitry. On the other hand, the aggressive pixelisation of sensors and associated front-end electronics, and the high radiation exposure at the innermost tracking and vertex detectors, requires radiation-aware design and radiation-tolerant deep sub-micron CMOS technologies.

This thesis explores circuit design techniques towards radiation tolerant power management integrated circuits, targeting applications on particle detectors and monitoring of accelerator-based experiments, aerospace and nuclear applications. It addresses advantages and caveats of commonly used radiation-hard layout techniques, which often employ Enclosed Layout or H-shaped transistors, in respect to the use of linear transistors.

Radiation tolerant designs for bandgap circuits are discussed, and two different topologies were explored. A low quiescent current bandgap for sub-1 *V* CMOS circuits is proposed, where the use of diode-connected MOSFETs in weak-inversion is explored in order to increase its radiation tolerance.

An any-load stable LDO architecture is proposed, and three versions of the design using different layout techniques were implemented and characterised.

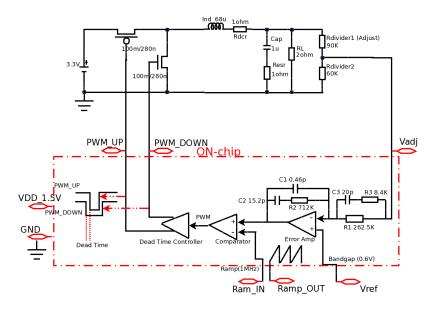

In addition, a switched DC-DC Buck converter is also studied. For reasons concerning testability and silicon area, the controller of the Buck converter is onchip, while the inductance and the power transistors are left on-board.

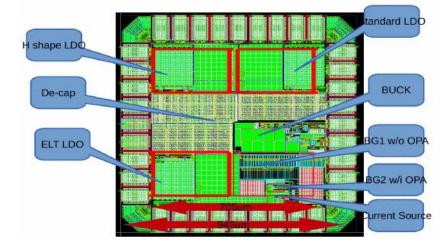

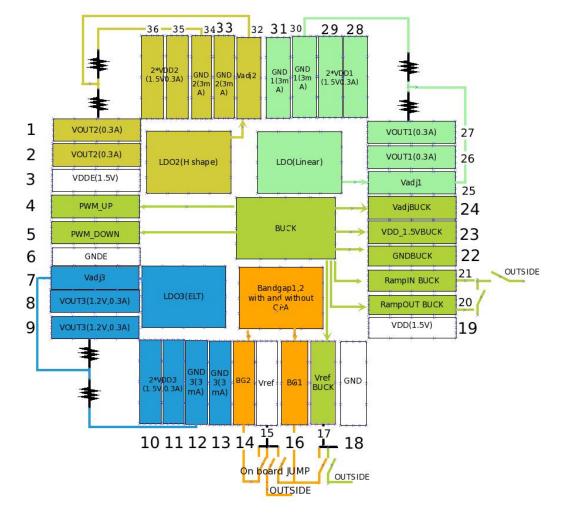

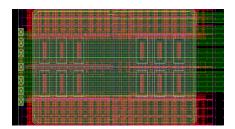

A prototype test chip with power management IP blocks was fabricated, using a TSMC 65 *nm* CMOS technology. The chip features Linear, ELT and H-shape LDO designs, bandgap circuits and a Buck DC-DC converter. We discuss the design, layout and test results of the prototype.

The specifications in terms of voltage range and output current capability are based on the requirements set for the integrated on-detector electronics of the new CGEM-IT tracker for the BESIII detector. The thesis discusses the fundamental aspects of the proposed on-detector electronics and provides an in-depth depiction of the front-end design for the readout ASIC.

**Key words:** LDO, Bandgap, DC-DC, ASIC, CMOS, Power Management, High Energy Physics.

# Contents

| Li | List of Figures xi |         |                                                               |     |  |

|----|--------------------|---------|---------------------------------------------------------------|-----|--|

| Li | List of Tables xx  |         |                                                               |     |  |

| No | Nomenclature xxii  |         |                                                               | xii |  |

| 1  | The                | Develop | oment of the Front-End ASICs in High Energy Physics           | 1   |  |

|    | 1.1                | High E  | nergy Physics Research                                        | 1   |  |

|    | 1.2                | Power   | management status in front-end ASICs                          | 4   |  |

|    |                    | 1.2.1   | Radiation-aware Demands in High Energy Physics Applica-       | 9   |  |

|    | 1.3                | Contex  | t and Motivation                                              | 10  |  |

|    | 1.4                | Thesis  | Outline and Original Contributions                            | 11  |  |

| 2  | The<br>Phys        |         | on-Aware Methods on CMOS Technology in High Energy            | 14  |  |

|    | 2.1                |         | tion between High Energy Particles and Semiconductor Material |     |  |

|    | 2.2                | Radiati | ion Effects on CMOS Semiconductor                             | 18  |  |

|    |                    | 2.2.1   | TID Effects on CMOS Technology Devices                        | 19  |  |

|    |                    | 2.2.2   | SEE Effects on CMOS Technology Devices                        | 26  |  |

|    | 2.3                | Radiati | ion-Aware Methods on CMOS Technology Devices                  | 31  |  |

|    |                    | 2.3.1   | Radiation-Aware Methods for TID Effects                       | 31  |  |

|   |      | 2.3.2   | Radiation-Aware Methods for SEU/SEL Effects              | 36 |

|---|------|---------|----------------------------------------------------------|----|

| 3 | Bias | and Po  | ower Management Issues in Front-End ASICs                | 43 |

|   | 3.1  | Power   | Management in Front-End ASICs                            | 43 |

|   | 3.2  | Currer  | nt and Voltage Biases                                    | 47 |

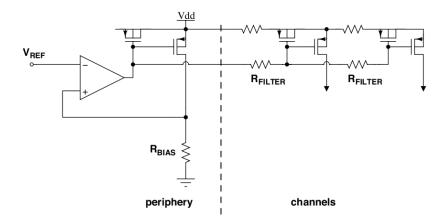

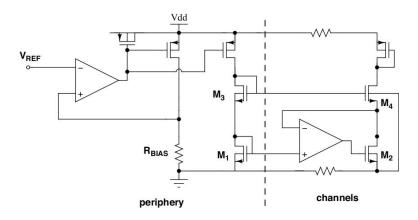

|   |      | 3.2.1   | Current Bias Design in Multichannel Front-Ends           | 47 |

|   |      | 3.2.2   | Voltage Bias Design in Multichannel Front-Ends           | 50 |

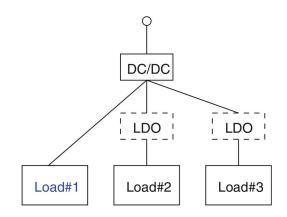

|   | 3.3  | Power   | Supply in Front-End ASICs                                | 51 |

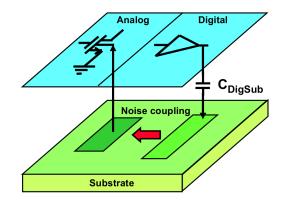

|   | 3.4  | Auxili  | ary Power Management in Front-End ASICs                  | 54 |

| 4 | The  | Transis | stor Design of the LDO and Bandgap IP Blocks Using 65 nm |    |

|   | CM   | OS Tecl | hnology                                                  | 59 |

|   | 4.1  | The D   | esign of LDO                                             | 60 |

|   |      | 4.1.1   | Introduction                                             | 60 |

|   |      | 4.1.2   | Conventional Linear Regulator Topology                   | 61 |

|   |      | 4.1.3   | Circuit Design Description                               | 63 |

|   |      | 4.1.4   | Radiation-Aware Design                                   | 64 |

|   |      | 4.1.5   | Simulation and Layout                                    | 66 |

|   |      | 4.1.6   | Conclusions                                              | 70 |

|   | 4.2  | The D   | esign of Bandgap                                         | 71 |

|   |      | 4.2.1   | Introduction                                             | 71 |

|   |      | 4.2.2   | Architecture of Bandgap                                  | 76 |

|   |      | 4.2.3   | Radiation-Aware Design                                   | 83 |

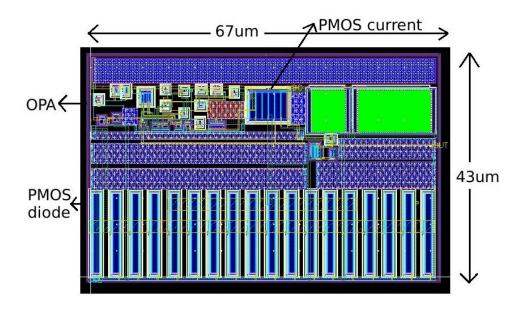

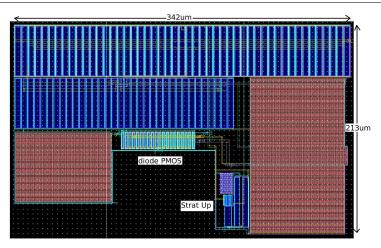

|   |      | 4.2.4   | Simulation and Layout                                    | 84 |

|   |      | 4.2.5   | Conclusions                                              | 92 |

| 5 | The  | Transis | stor Design of the BUCK IP Block Using 65 nm CMOS Tech-  |    |

# nology 95

|    | 5.1    | Introdu | uction                                             | . 95  |

|----|--------|---------|----------------------------------------------------|-------|

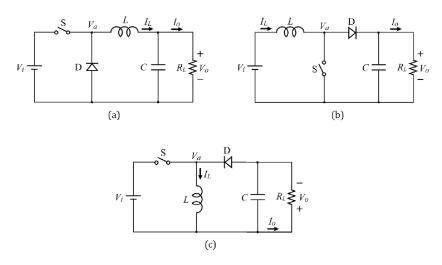

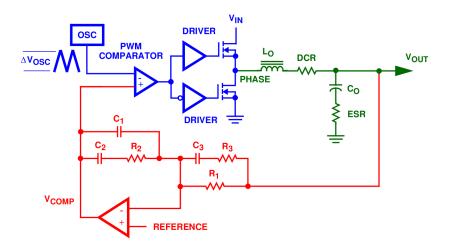

|    | 5.2    | Archit  | ecture of the BUCK                                 | . 96  |

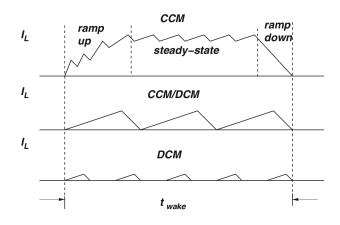

|    |        | 5.2.1   | CCM and DCM Mode                                   | . 98  |

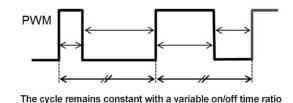

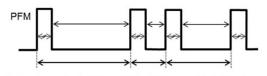

|    |        | 5.2.2   | PWM and PFM Mode                                   | . 99  |

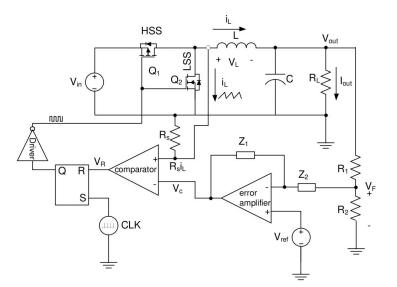

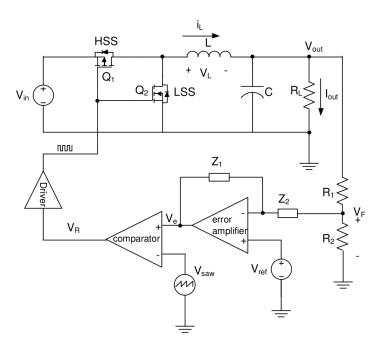

|    |        | 5.2.3   | VMC and CMC Feedback Mode                          | . 100 |

|    | 5.3    | Transi  | stor-Level Design of the BUCK                      | . 103 |

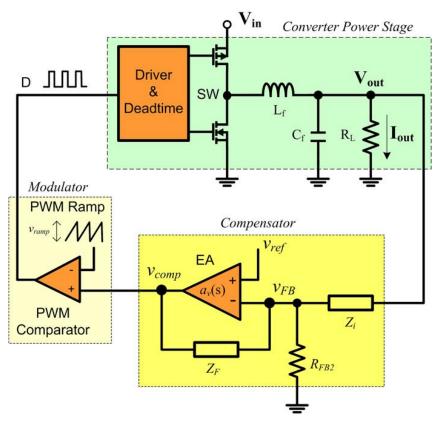

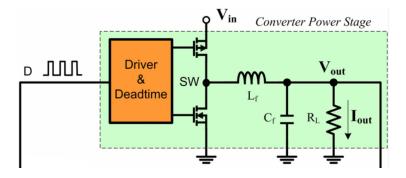

|    |        | 5.3.1   | Converter Power Stage                              | . 104 |

|    |        | 5.3.2   | Transfer Function and the Feedback Compensation    | . 122 |

|    |        | 5.3.3   | Radiation-Aware Design                             | . 141 |

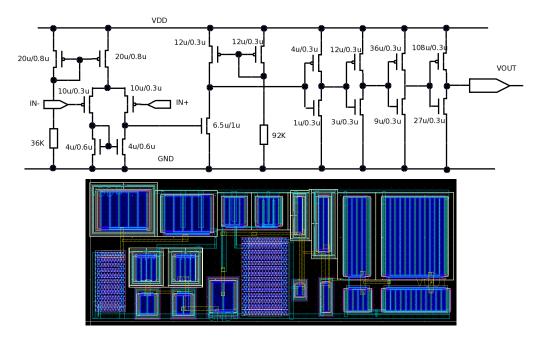

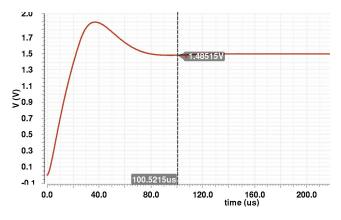

|    | 5.4    | Simula  | ation Results                                      | . 142 |

|    |        | 5.4.1   | Simulation of the Modulator Architecture           | . 142 |

|    |        | 5.4.2   | Simulation of the Error Amplifier and Compensation | . 146 |

| 6  | Test   | Setup a | and Characterization Results                       | 150   |

|    | 6.1    | Chip f  | for TSMC 65 <i>nm</i> Power Management IP Blocks   | . 150 |

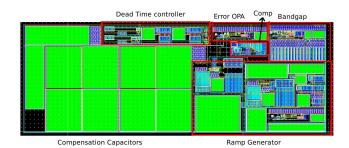

|    |        | 6.1.1   | Floor Plane of the Chip                            | . 150 |

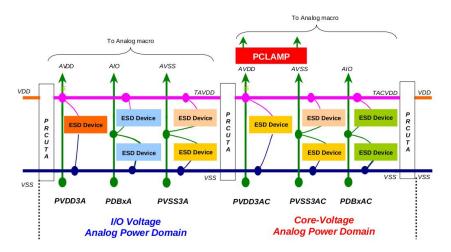

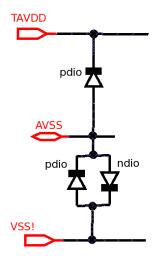

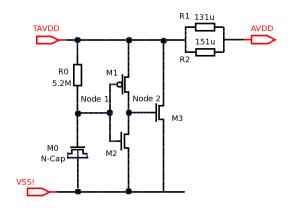

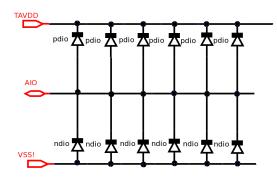

|    |        | 6.1.2   | Anti-ESD and I/O Design Strategy                   | . 156 |

|    | 6.2    | Electri | ical Test Results                                  | . 163 |

|    |        | 6.2.1   | LDO Electrical Tests                               | . 164 |

|    |        | 6.2.2   | Bandgap Electrical Tests                           | . 170 |

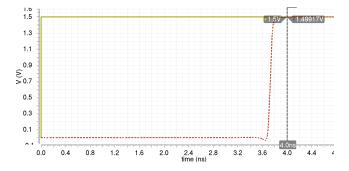

|    |        | 6.2.3   | BUCK Electrical Tests                              | . 172 |

|    | 6.3    | The Fu  | urther Radiation Test                              | . 175 |

| 7  | Con    | clusion | s and Outlook                                      | 177   |

|    | 7.1    | Conclu  | usions                                             | . 177 |

|    | 7.2    | Outloc  | 0k                                                 | . 178 |

| Re | eferen | ices    |                                                    | 179   |

| Appendix A A Custom IC Dsign for the Readout of the BESIII CGEM-IT |                                   |       |

|--------------------------------------------------------------------|-----------------------------------|-------|

| Dete                                                               | ector                             | 184   |

| A.1                                                                | The CGEM-IT Project               |       |

| A.2                                                                | Readout System of the CGEM-IT     |       |

| A.3                                                                | Detector Conditions and FEE Indic | ators |

| A.4                                                                | Front-End ASIC Design             |       |

|                                                                    | A.4.1 Preamplifier Design         |       |

|                                                                    | A.4.2 Shaper Design               |       |

\_\_\_\_\_

# **List of Figures**

| 1.1  | LHC including the CMS, ALICE, LHCb and ATLAS detectors                         | 2  |

|------|--------------------------------------------------------------------------------|----|

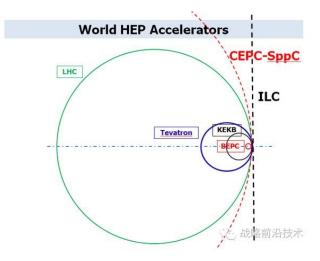

| 1.2  | Comparision of CEPC, ILC and the present accelerators                          | 2  |

| 1.3  | AMS installed in the International Space Station                               | 3  |

| 1.4  | Illustration of the payload configuration on the HXMT satellite                | 3  |

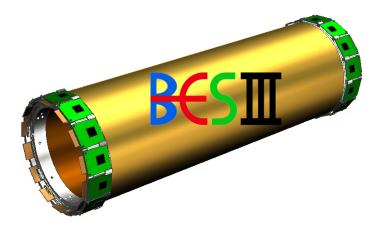

| 1.5  | Cylindrical GEM detector Inner Tracker (CGEM-IT)                               | 10 |

| 1.6  | TIGER chip bonded to the board                                                 | 11 |

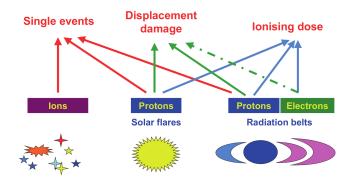

| 2.1  | Space radiation source and the possible damage effect                          | 14 |

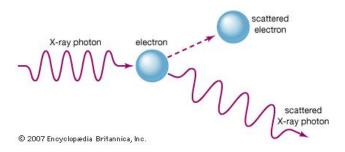

| 2.2  | Compton effect diagram                                                         | 15 |

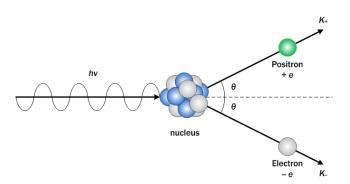

| 2.3  | Pair production effect diagram                                                 | 16 |

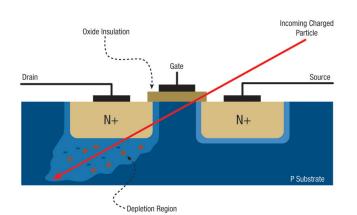

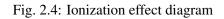

| 2.4  | Ionization effect diagram                                                      | 18 |

| 2.5  | Schematic view of the density of $e$ - $h$ pairs caused by different radiation | 18 |

| 2.6  | Radiation effects on the semiconductor devices                                 | 19 |

| 2.7  | TID effect on the gate oxide                                                   | 20 |

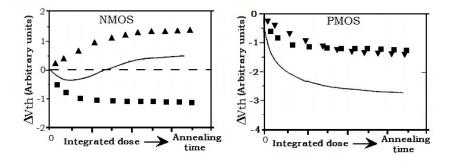

| 2.8  | Threshold voltage variation under the TID                                      | 22 |

| 2.9  | Tunneling effect on the interface                                              | 23 |

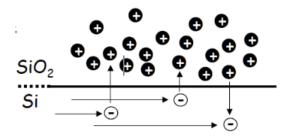

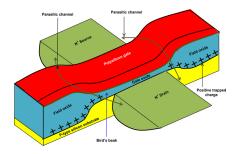

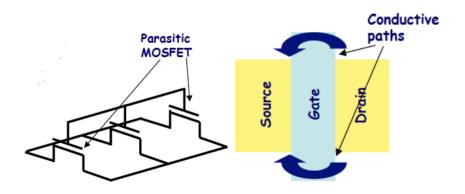

| 2.10 | Parasitic CMOS formed by Bird's beak                                           | 24 |

| 2.11 | Parasitic CMOS schematic                                                       | 24 |

| 2.12 | STI architecture and the parasitic channel                                     | 25 |

| 2.13 | Cross-sectional diagram indicating: (1) drain-to-source leakage and<br>(2) leakage between the n+ source/drain region of an n-channel |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

|      | device and the n- well region of an adjacent p-channel device                                                                         | 26 |

| 2.14 | Single Event Upset (corruption of logic state)                                                                                        | 27 |

| 2.15 | Fission of $({}^{10}B)$ induced by the neutron                                                                                        | 28 |

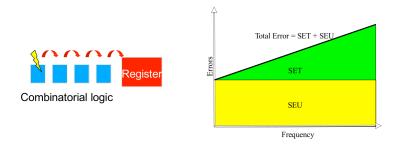

| 2.16 | SET source and the result                                                                                                             | 29 |

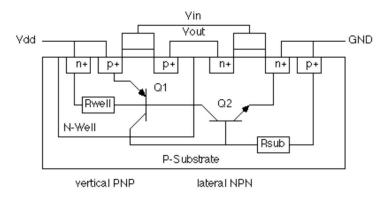

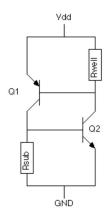

| 2.17 | Cross section of parasitic transistors                                                                                                | 29 |

| 2.18 | Schematic of parasitic transistors                                                                                                    | 30 |

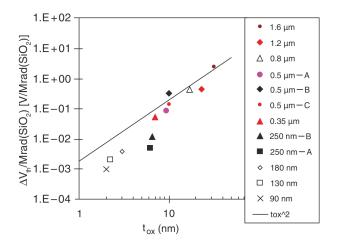

| 2.19 | Threshold voltage shift in different CMOS technologies                                                                                | 32 |

| 2.20 | Standard transistor (left) and the typical enclosed layout transistor(right)                                                          | 33 |

| 2.21 | 130 <i>nm</i> technology transistor leakage current under the different radiations                                                    | 34 |

| 2.22 | A new kind of radiation-aware structure                                                                                               | 35 |

| 2.23 | Guard ring effects cutting the leakage current of the different N+                                                                    |    |

|      | diffusion parts                                                                                                                       | 36 |

| 2.24 | Guard ring anti-leakage current effects                                                                                               | 37 |

| 2.25 | Structure of the Shallow Trench Isolation                                                                                             | 38 |

| 2.26 | Reducing the sensitivity to Latch up by guard rings                                                                                   | 39 |

| 2.27 | Epitaxial wafers profile                                                                                                              | 39 |

| 2.28 | Triple Module Redundancy (TMR)                                                                                                        | 40 |

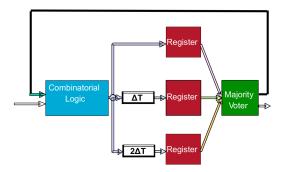

| 2.29 | Time redundancy with TMR                                                                                                              | 41 |

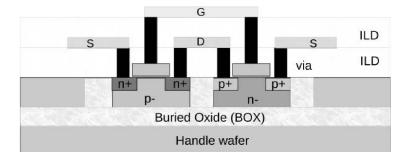

| 2.30 | Cross view of the SOI structure                                                                                                       | 41 |

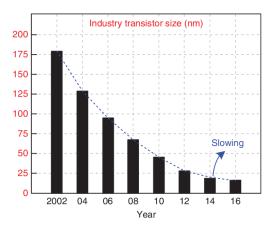

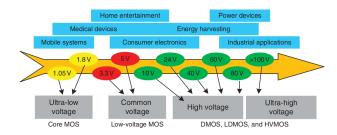

| 3.1  | Moore's law in recently years                                                                                                         | 45 |

| 3.2  | Power supply variation as the advanced process                                                                                        | 45 |

| 3.3  | A simple current bias schematic                                                                                                       | 48 |

| 3.4  | An excellent current bias schematic[1]                                                                                                | 49 |

| 3.5  | Combination of the switch DC-DC and the LDO                                | 53 |

|------|----------------------------------------------------------------------------|----|

| 3.6  | Noise couple through the substrate                                         | 54 |

| 3.7  | Power supply influenced by the digital circuit                             | 55 |

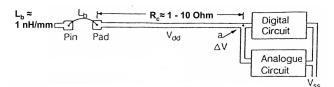

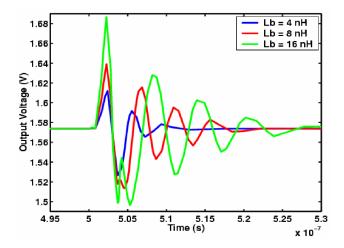

| 3.8  | Different bonding wires inductance simulation results                      | 55 |

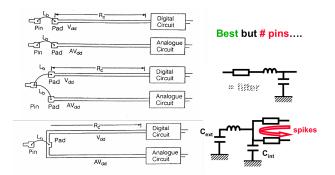

| 3.9  | Pads strategy between the analogue and digital circuits                    | 56 |

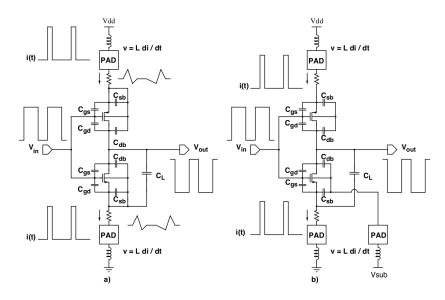

| 3.10 | Noise couple caused by the bonding wires                                   | 57 |

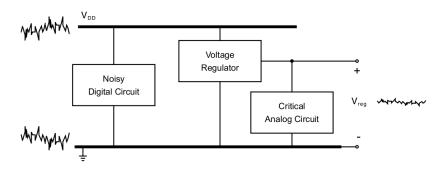

| 4.1  | LDO output to the analogue circuit with lower noise                        | 60 |

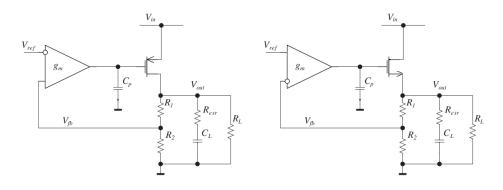

| 4.2  | Classical LDO architecture: PMOS (left) and NMOS (right) power transistors | 61 |

| 4.3  | A new LDO architecture                                                     | 63 |

| 4.4  | LDO radiation simulation comparison                                        | 65 |

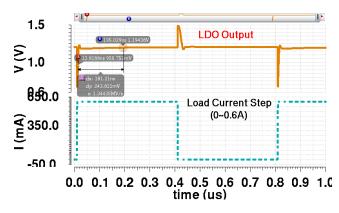

| 4.5  | Load transient response                                                    | 66 |

| 4.6  | Drop out voltage with output $0A$                                          | 67 |

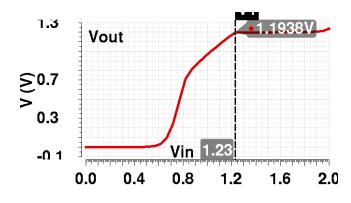

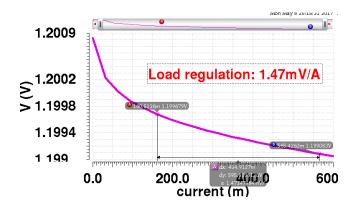

| 4.7  | Load regulation of the LDO                                                 | 67 |

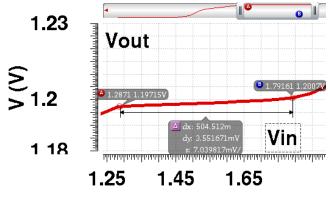

| 4.8  | LDO line regulation                                                        | 68 |

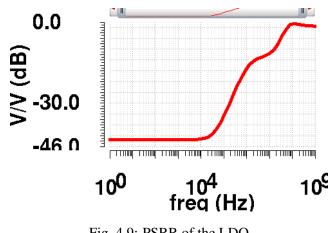

| 4.9  | PSRR of the LDO                                                            | 69 |

| 4.10 | The H shape and ELT transistors                                            | 69 |

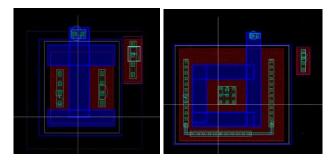

| 4.11 | The H shape LDO layout                                                     | 70 |

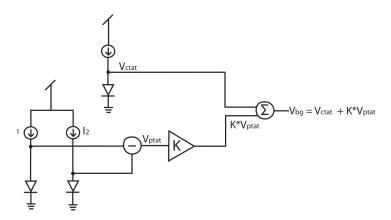

| 4.12 | Positive TC architecture                                                   | 72 |

| 4.13 | Bandgap principle diagram                                                  | 73 |

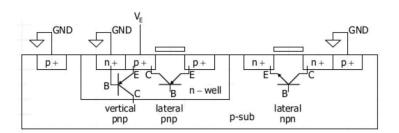

| 4.14 | Special triode using CMOS technology                                       | 74 |

| 4.15 | Classical bandgap technology                                               | 74 |

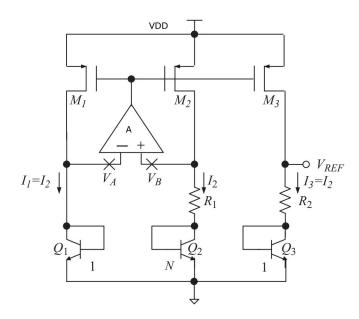

| 4.16 | Banba low power supply bandgap architecture                                | 77 |

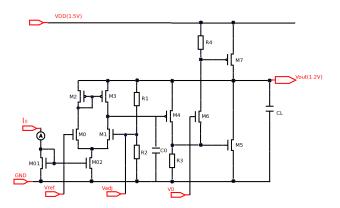

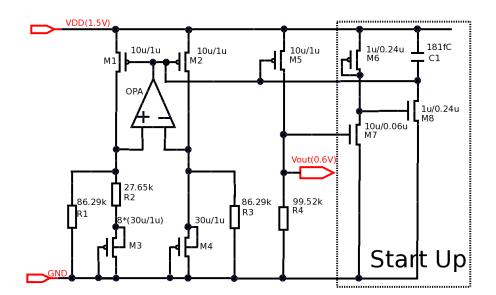

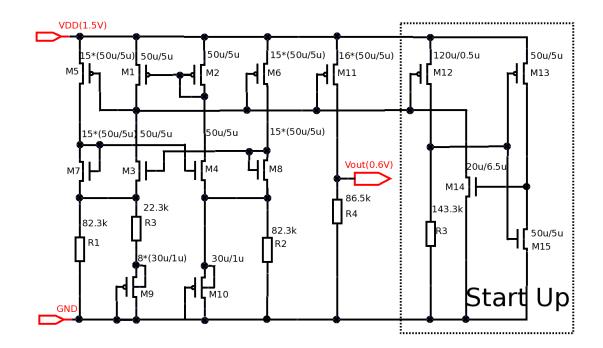

| 4.17 | Transistor level bandgap schematic                                         | 78 |

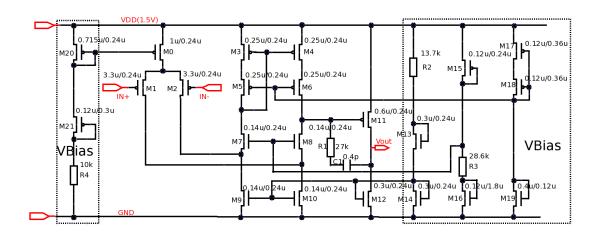

| 4.18 | Transistor level OPA schematic used in the bandgap                         | 80 |

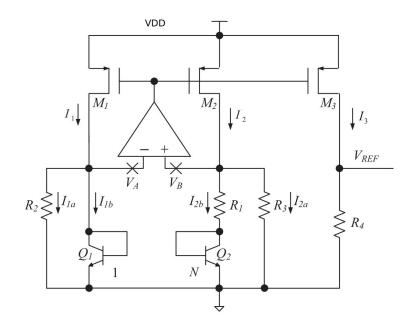

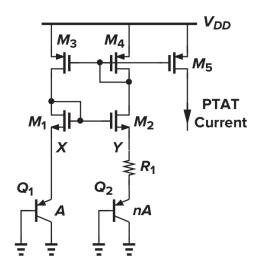

| 4.19 | Alternative method of the PTAT current without OPA                         | 81 |

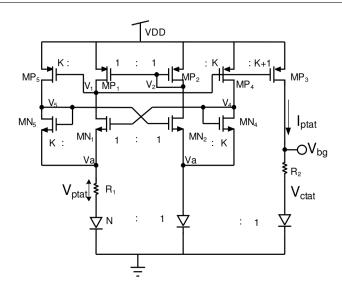

| 4.20 | Improved PTAT current circuit without OPA                                                   |

|------|---------------------------------------------------------------------------------------------|

| 4.21 | A new architecture of bandgap without OPA                                                   |

| 4.22 | Bandgap radiation simulation comparison                                                     |

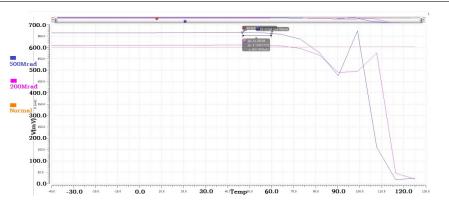

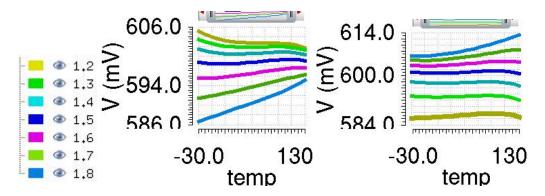

| 4.23 | Temperature coefficient of the bandgaps, left bandgap without OPA,right bandgap with OPA85  |

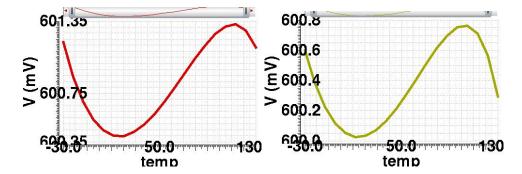

| 4.24 | PSRR of the bandagps, left bandgap without OPA, right bandgap      with OPA                 |

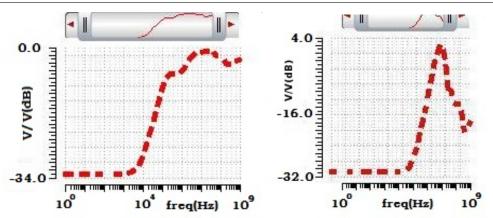

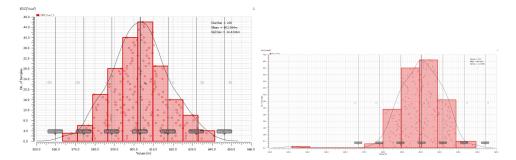

| 4.25 | MC simulation results of the bandagps, left: bandgap without OPA, right: bandgap with OPA   |

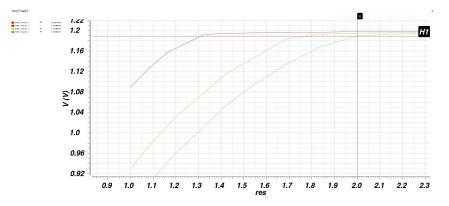

| 4.26 | Output voltage versus the input voltage, left bandgap without OPA,right bandgap with OPA87  |

| 4.27 | TC at different power supplies, left bandgap without OPA, right bandgap with OPA            |

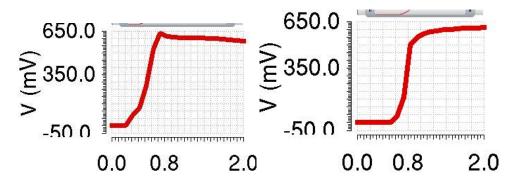

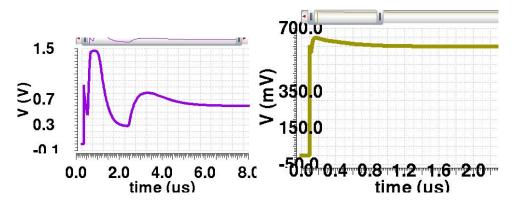

| 4.28 | Start-up effect of the bandagps, left bandgap without OPA, right bandgap with OPA           |

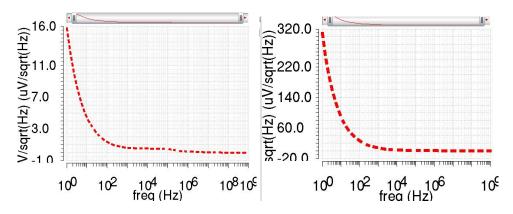

| 4.29 | Noise simulation result of the bandagps, left: bandgap without OPA, right: bandgap with OPA |

| 4.30 | Layout of the bandgap with OPA                                                              |

| 4.31 | Layout of the bandgap without OPA                                                           |

| 5.1  | Typical DC-DC converters                                                                    |

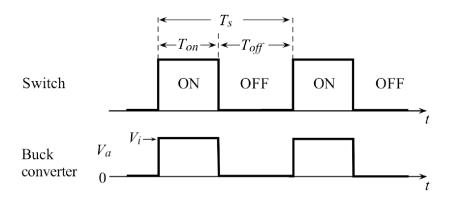

| 5.2  | Relationship between the switch and $V_a$                                                   |

| 5.3  | CCM and DCM modes                                                                           |

| 5.4  | PWM regulate mode                                                                           |

| 5.5  | PFM regulate mode                                                                           |

| 5.6  | Current control mode structure                                                              |

| 5.7  | Voltage control mode structure                                                              |

| 5.8  | Simple buck architecture mode                                                               |

| 5.9  | On-chip and off-chip components distribution                                                |

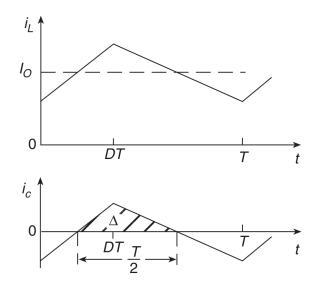

| 5.10 | Diode asynchronous buck inductor currents                                                 |

|------|-------------------------------------------------------------------------------------------|

| 5.11 | MOSFET synchronous buck inductor currents                                                 |

| 5.12 | Current at the CCM/DCM boundary                                                           |

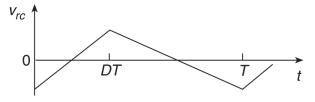

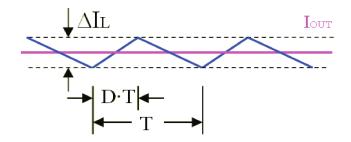

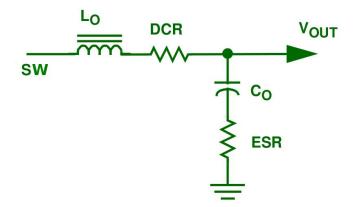

| 5.13 | Output capacitor with ESR                                                                 |

| 5.14 | AC current of the output capacitor                                                        |

| 5.15 | ESR resistor voltage                                                                      |

| 5.16 | Output capacitor voltage variation caused by the AC current 111                           |

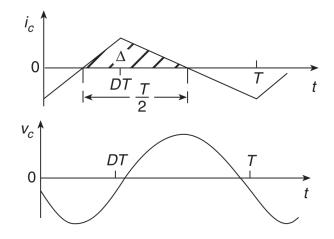

| 5.17 | Current variation of the inductor                                                         |

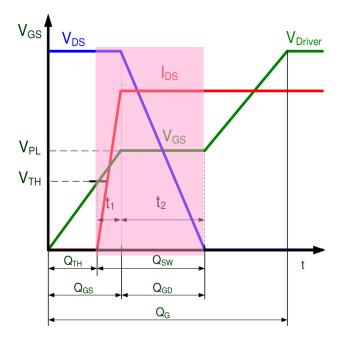

| 5.18 | High side MOSFET switching on process                                                     |

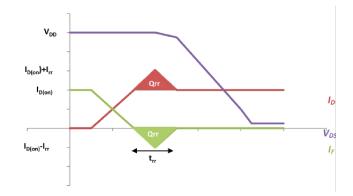

| 5.19 | Low side MOSFET body diode reverse recovery process 117                                   |

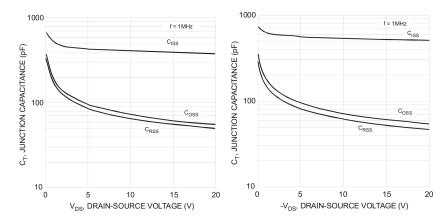

| 5.20 | DMC2038LVT Q1 NMOS parasitic capacitance (left) and Q2 PMOS parasitic capacitance (right) |

| 5.21 | Switch MOSFET gate power loss                                                             |

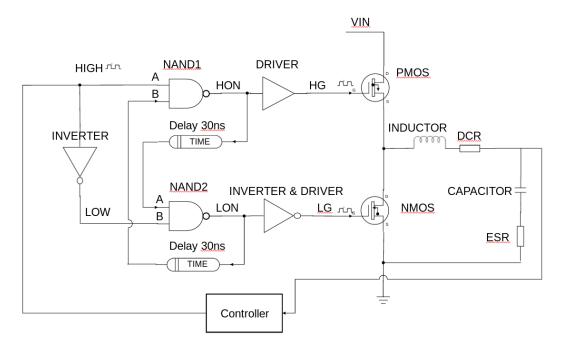

| 5.22 | Dead time controller architecture                                                         |

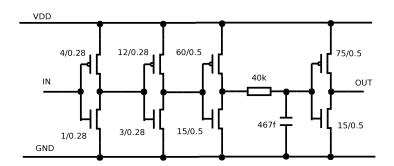

| 5.23 | Delay function schematic                                                                  |

| 5.24 | Converter power stage block                                                               |

| 5.25 | The second part of the converter power stage block                                        |

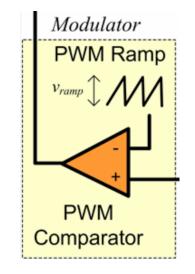

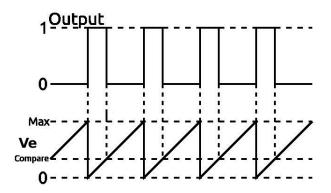

| 5.26 | Illustration of the modulator block                                                       |

| 5.27 | Illustration of the PWM generator                                                         |

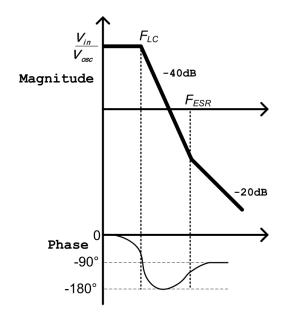

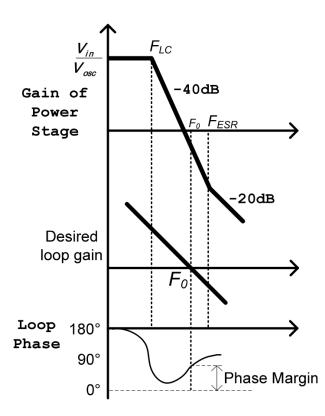

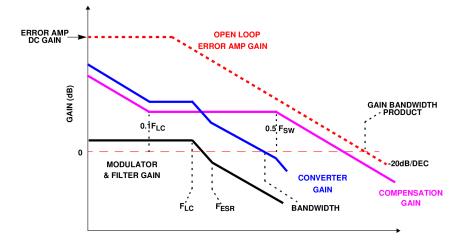

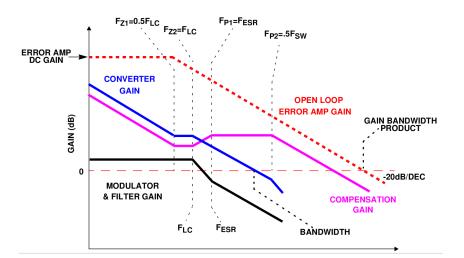

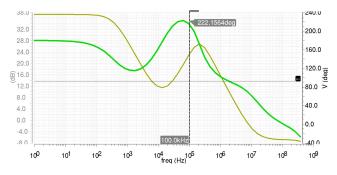

| 5.28 | Bode plot of the open-loop system                                                         |

| 5.29 | Bode plot of the desired loop gain and phase                                              |

| 5.30 | Matching slope (up) and the no matching slope (down) voltage error 128                    |

| 5.31 | State space mean method disposing the PWM                                                 |

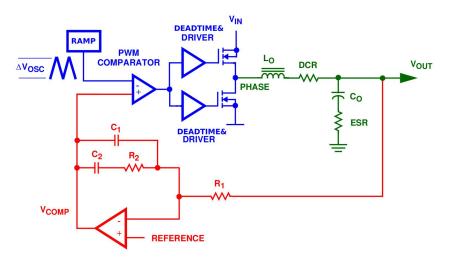

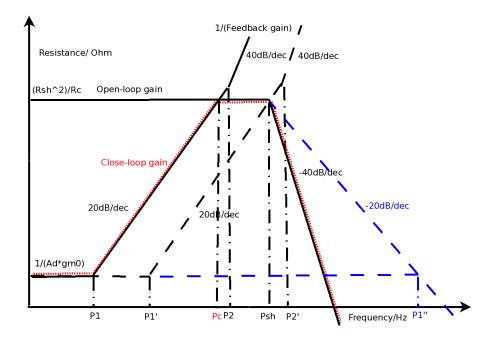

| 5.32 | Schematic of the compensation type II                                                     |

| 5.33 | Amplitude and phase of the type II compensation                                           |

| 5.34 | Compensated system amplitude bode plot using the type II compen-<br>sation                |

|      |                                                                                           |

| 5.35 | Whole closed-loop schematic using the type II compensation $\ldots$ 134                      |

|------|----------------------------------------------------------------------------------------------|

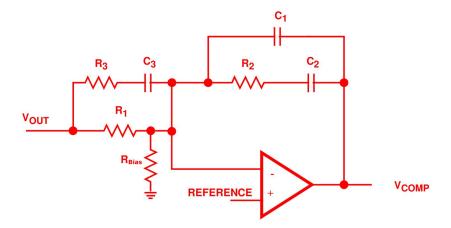

| 5.36 | Type III compensation schematic                                                              |

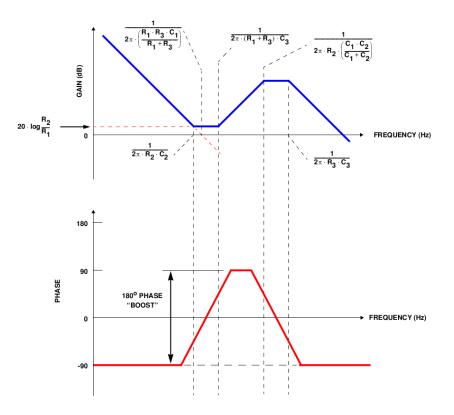

| 5.37 | Type III compensation bode plot                                                              |

| 5.38 | Compensated system amplitude bode plot using the type III-A and the poles zeros distribution |

| 5.39 | Whole closed-loop schematic using the type III-A compensation 138                            |

| 5.40 | Comparator schematic and layout                                                              |

| 5.41 | Comparator delay time                                                                        |

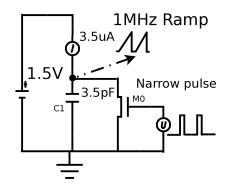

| 5.42 | Architecture of the ramp                                                                     |

| 5.43 | Layout of the ramp                                                                           |

| 5.44 | Narrow pulse generator schematic                                                             |

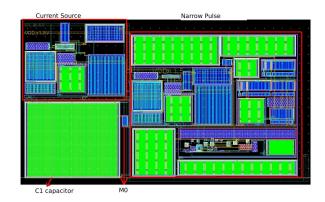

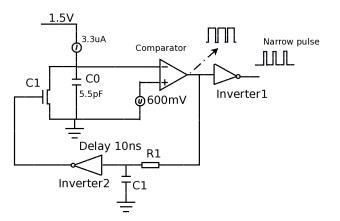

| 5.45 | Simulation result of the PWM wave generator                                                  |

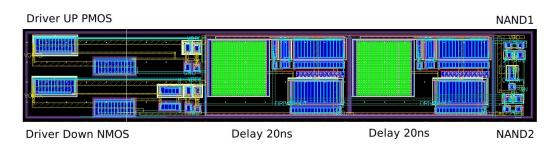

| 5.46 | Layout of the dead time controller                                                           |

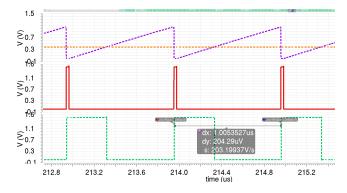

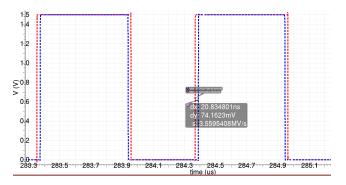

| 5.47 | Simulation result of the dead time controller                                                |

| 5.48 | Layout of the error amplifier                                                                |

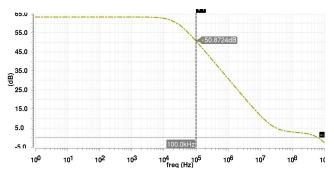

| 5.49 | Open-loop bode plot of the OPA                                                               |

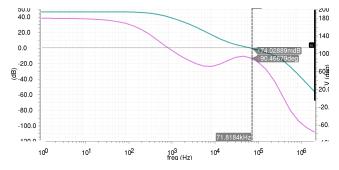

| 5.50 | Compensated error amplifier bode plot                                                        |

| 5.51 | Closed-loop bode plot of the buck converter                                                  |

| 5.52 | Output voltage simulation result of buck converter with 1 A load 148                         |

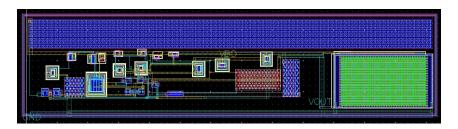

| 5.53 | Buck PWM generator and the compensation layout                                               |

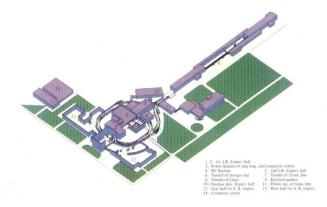

| 6.1  | Whole layout of the chip                                                                     |

| 6.2  | Structure of the NMOS varactor capacitor and the C-V relationship . 152                      |

| 6.3  | TSMC PVSS3A pad layout                                                                       |

| 6.4  | Large current part layout covering the standard I/O pads 153                                 |

| 6.5  | Pads distribution of the chip                                                                |

| 6.6  | Limited current by the power lines                                                           |

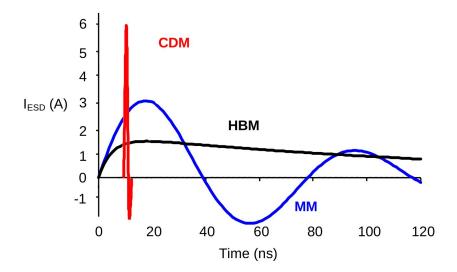

| 6.7  | ESD effects, the left for CDM, the middle for HBM, and the right for MM                                       |

|------|---------------------------------------------------------------------------------------------------------------|

| 6.8  | Simulation ESD currents of CDM, HBM, and MM models under the same outside conditions                          |

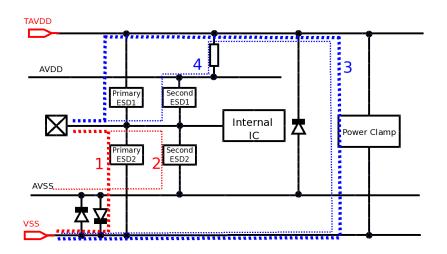

| 6.9  | Anti-ESD network of the chip                                                                                  |

| 6.10 | Anti-ESD design in the pads                                                                                   |

| 6.11 | Structure of the PVSS3A pad                                                                                   |

| 6.12 | Structure of the PVDD3A pad                                                                                   |

| 6.13 | Structure of the PDB3A pad                                                                                    |

| 6.14 | The second anti-ESD device                                                                                    |

| 6.15 | Anti-ESD breakdown clamp of the GGNMOS                                                                        |

| 6.16 | Power management chip test schematic                                                                          |

| 6.17 | Bonding board and test board                                                                                  |

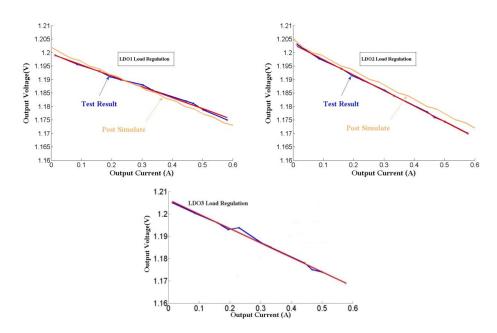

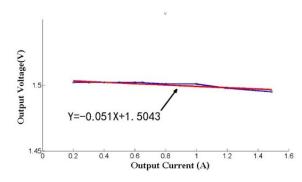

| 6.18 | LDO1 (top left), LDO2 (top right), LDO3 (lower) load regulations . 166                                        |

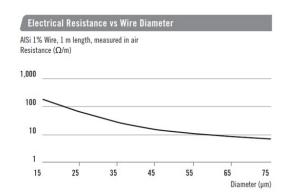

| 6.19 | Bonding wire resistance (Logarithmic coordinates)                                                             |

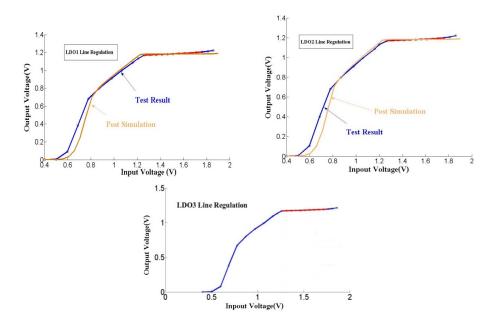

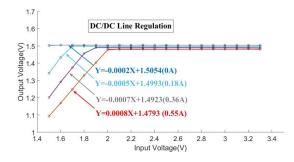

| 6.20 | LDO1 (top left), LDO2 (top right), LDO3 (lower) line regulations with the output current $0.6 A$              |

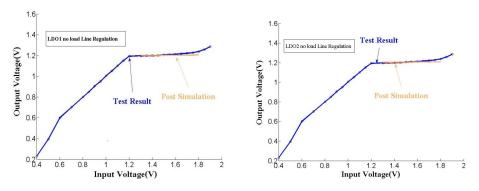

| 6.21 | LDO1 (left), LDO2 (right) line regulations with no load 168                                                   |

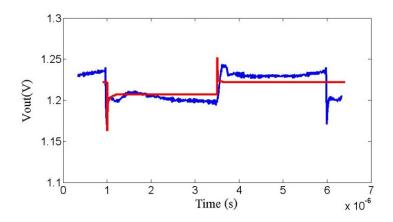

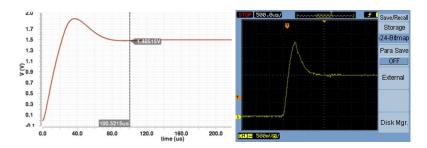

| 6.22 | LDO1 transient load recovery time simulation                                                                  |

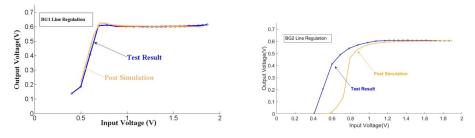

| 6.23 | Bandgap line regulations, left is the bandgap without OPA, right is the bandgap with OPA                      |

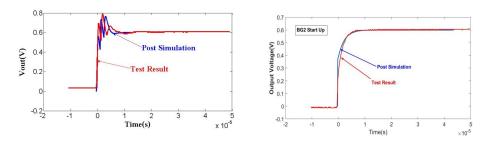

| 6.24 | Bandgap start-up simulation and test results, left: the bandgap with-<br>out OPA, right: the bandgap with OPA |

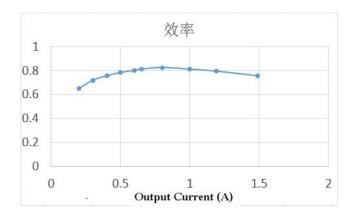

| 6.25 | DC-DC power efficiency figure                                                                                 |

| 6.26 | DC-DC power load regulation                                                                                   |

| 6.27 | DC-DC power line regulation                                                                                   |

| 6.28 | DC-DC power start-up simulation result (left) and test result (right) . 175                                   |

|      |                                                                                                               |

| A.1  | Layout of BEPC                                                                                    |

|------|---------------------------------------------------------------------------------------------------|

| A.2  | The word record of BEPC II                                                                        |

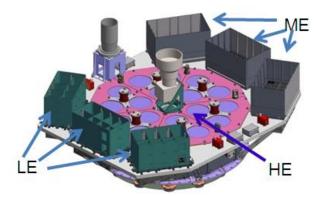

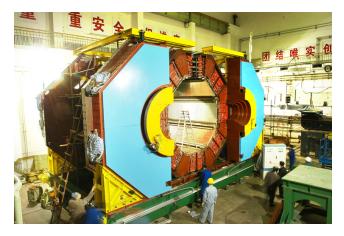

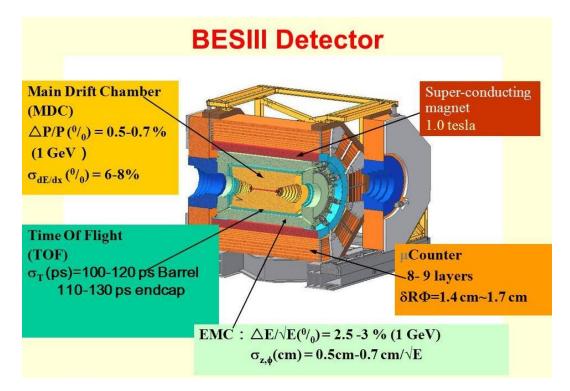

| A.3  | BESIII actual picture                                                                             |

| A.4  | Detectors of BESIII                                                                               |

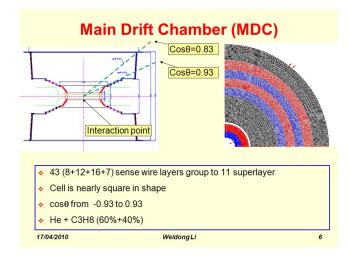

| A.5  | MDC architecture of BESIII                                                                        |

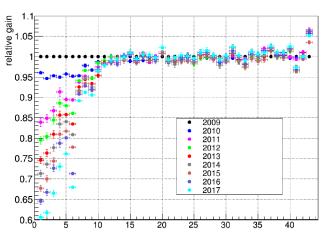

| A.6  | Anode aging of the MDC (up to 2017)                                                               |

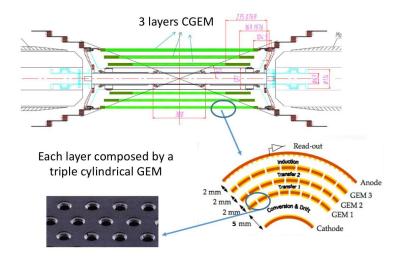

| A.7  | Three layers architecture of CGEM-IT                                                              |

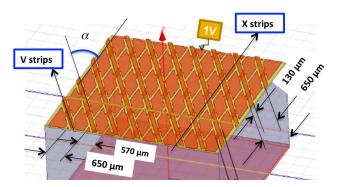

| A.8  | Two-dimensional readout method                                                                    |

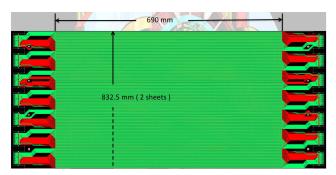

| A.9  | Anode PCB board of the second layer                                                               |

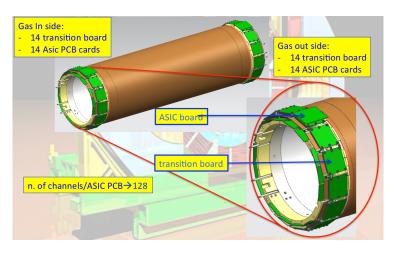

| A.10 | Signal readout terminal cards of the second layer                                                 |

| A.11 | Signal readout system of the CGEM-IT                                                              |

| A.12 | Illustration of the charge centroid for path through tracks with mag-<br>netic field B off        |

| A.13 | Worse situations by the charge centroid                                                           |

| A.14 | Combined resolution with different incident angles                                                |

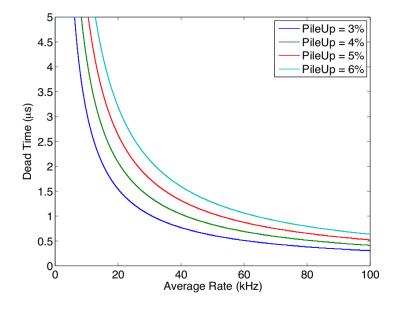

| A.15 | Dead time versus the rate for different pile-up probabilities 195                                 |

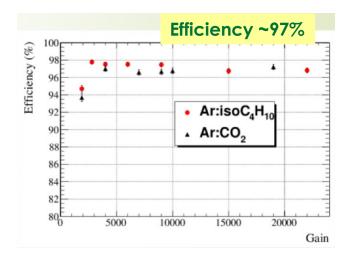

| A.16 | Relationship between the gain and the efficiency                                                  |

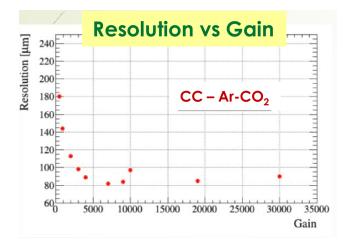

| A.17 | Relationship between the gain and the resolution                                                  |

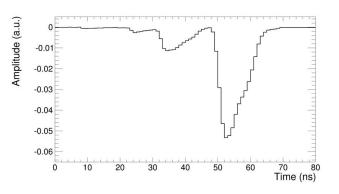

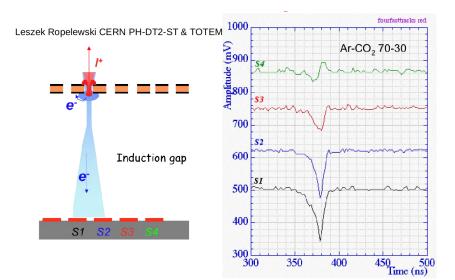

| A.18 | Typical triple GEM signal shape                                                                   |

| A.19 | A CGEM output signal shape                                                                        |

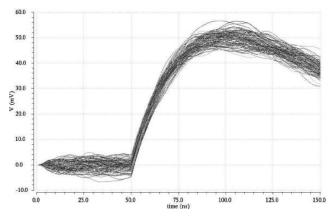

| A.20 | Rising edge shape with noise                                                                      |

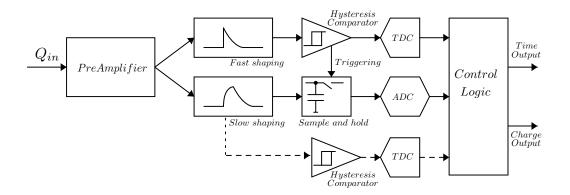

| A.21 | FEE architecture with two outputs                                                                 |

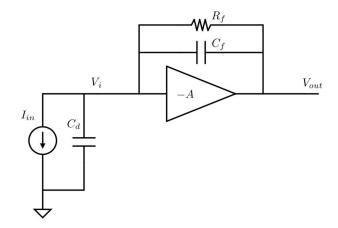

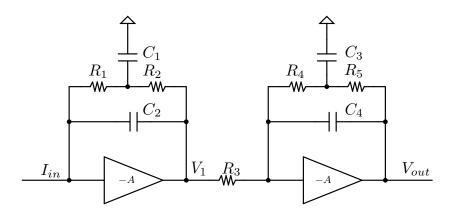

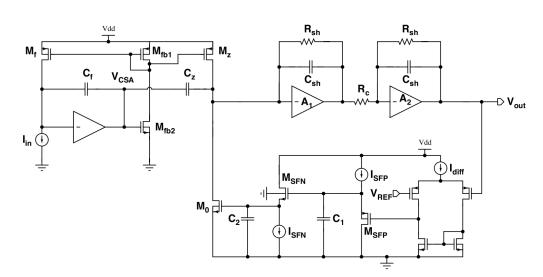

| A.22 | A CSA architecture used as the preamplifer                                                        |

| A.23 | CSA architecture bode plot                                                                        |

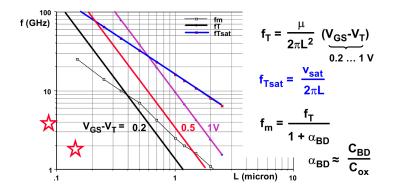

| A.24 | The maximum intrinsic frequency $f_T$ versus the channel length $L[2]$ 205                        |

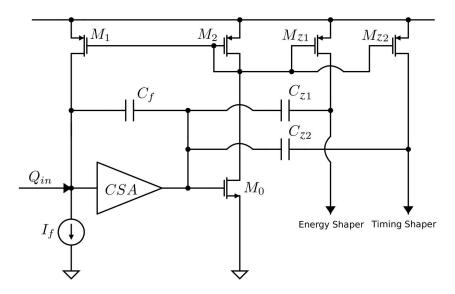

| A.25 | Feedback capacitor and equivalent resistor $(M_0, M_1, M_2)$ of the Charge<br>Sensitive Amplifier |

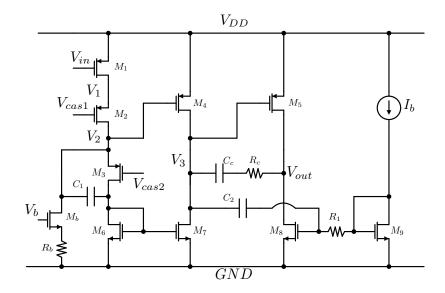

| A.26 Transistor level design of the CSA                                 |

|-------------------------------------------------------------------------|

| A.27 Current effect versus the inversion coefficient[2]                 |

| A.28 Ratio between the pulse width and the peaking time for the shapers |

| with different orders                                                   |

| A.29 Open-loop gain and bandwidth of the CSA                            |

| A.30 Timing branch schematic with the CSA                               |

| A.31 Energy branch shaper schematic                                     |

| A.32 Full front-end chain with the baseline holder                      |

| A.33 Amplitude bode plot of the baseline                                |

# **List of Tables**

| 1.1 | Power management comparison table 1 in front-end ASICs of highenergy physics[3]6        |

|-----|-----------------------------------------------------------------------------------------|

| 1.3 | Power management comparison table 2 in front-end ASICs of highenergy physics[3]7        |

| 1.4 | Power management comparison table 3 in front-end ASICs of high<br>energy physics[3]     |

| 4.1 | Different power transistors                                                             |

| 4.2 | External and internal compensations table                                               |

| 4.3 | Transistor sizes for the circuit of the new LDO (W/L unit: $\mu m$ ; R unit: $\Omega$ ) |

| 4.4 | Parameters comparing of different LDOs                                                  |

| 4.5 | Temperature coefficient at different power supply                                       |

| 4.6 | Both bandgaps noise table                                                               |

| 4.7 | Parameters comparison between the two bandgaps 90                                       |

| 4.8 | Performance comparison with others bandgaps                                             |

| 5.1 | Truth table of the S-R latch                                                            |

| 5.2 | Truth table of the NAND logic                                                           |

| 5.3 | Different compensation types according to the ESR zero position 129                     |

| 6.1 | LDO output load regulations table                                                       |

| 6.2 | LDO output line regulations table $(0.6 A)$ |

|-----|---------------------------------------------|

| 6.3 | LDO minimum power supply comparing table    |

| 6.4 | LDO output line regulations table $(0 A)$   |

| 6.5 | Bandgap line regulations comparison table   |

| 6.6 | Bandgaps minimum input voltages table       |

| 6.7 | Bandgap start-up time table                 |

| 6.8 | DC-DC output load variation test table      |

|     |                                             |

| A.1 | Different layer strips numbers              |

| A.2 | Detector condition parameters for the FEE   |

| A.3 | FEE demand indicators                       |

# Nomenclature

### **Roman Symbols**

| Cox             | the specific gate capacitance                                                            |

|-----------------|------------------------------------------------------------------------------------------|

| p <sub>em</sub> | emission probability of an electron from the valence band of $S_{\rm i}O_2$ to the traps |

| Т               | absolute temperature                                                                     |

| X <sub>m</sub>  | density of the holes at the depth of m                                                   |

| A               | relative atomic mass                                                                     |

| С               | speed of light                                                                           |

| е               | electron charge                                                                          |

| k <sub>B</sub>  | Boltzmann constant                                                                       |

| m <sub>e</sub>  | rest mass of electron                                                                    |

| Ми              | Molar mass constant                                                                      |

| N <sub>A</sub>  | Avogadro number                                                                          |

| q               | an electron charge $1.6 \times 10^{-19} C$                                               |

| Ζ               | atomic number                                                                            |

| Х               | X-rays                                                                                   |

|                 |                                                                                          |

### **Greek Symbols**

$\beta \qquad \frac{v}{c}$ , relative speed for light

- $\Delta V_{in}$  threshold shift caused by the interface state

- $\Delta V_{ox}$  threshold shift caused by the gate oxide

- $\Delta N$  density of the trapped holes

- $\varepsilon_0$  vacuum permittivity

- $\gamma$  gamma rays

- $\rho$  density of the material

- $\varphi$  energy difference between the trap level and the valence band

- *e-h* electron-hole pair

#### **Acronyms / Abbreviations**

- AC Alternating Current

- AMS Alpha Magnetic Spectrometer

- ASIC Application-Specific Integrated Circuit

- ATICE A Large Ion Collider Experiment

- ATLAS A Toroidal LHC Apparatus

- BEPCII Beijing Electron-Positron Collider II

- BeppoSAX Satellite per Astronomia X, Beppo in honer of Giuseppe Occhialini

- **BESIII** Beijing Electron Spectrometer III

- BJT Bipolar Junction Transistor

- CEPC Circular Electron Positron Collider

- CERN The European Organization for Nuclear Research

- CGEM Cylindrical Gas Electron Multiplier

- CGEM-IT Cylindrical Gas Electron Multipliers Inner Tracker

- CMC Current Mode Control

- CMS Compact Muon Solenoid

- CTAT Complementary to Absolute Temperature

- DAMPT Department of Applied Mathematics and Theoretical Physics

- DC Direct Current

- DC-DC Direct Current to Direct Current

- DCR Direct Current Resistance

- DTMOST Dynamic Threshold MOSFET

- EMC Electro-Magnetic Calorimeter

- ESR Equivalent Series parameter Resistor

- EXOSAT European X-ray Observatory Satellite

- FEE Front-End Electronics

- FIT The Failure In Time

- HEP High Energy Physics

- HERD High Energy cosmic Radiation Detection facility

- HXMT Hard X-ray Modulation Telescope

- IHEP Institute of High Energy of Physics Chinese Academy of Sciences

- INFN Istituto Nazionale di Fisica Nucleare

- IS International System

- KCL Kirchhoff's Circuit Laws

- KCL Kirchhoff's Circuit Laws

- KEK The High Energy Accelerator Research Organization

- LDO Low Drop Out Regulator

- LET The Linear Energy Transfer

- LHC Large Hadron Collider

- LHCb LHC beauty

- LOCOS LOCal Oxidation of Silicon

- MC Monte Carlo simulation

- MDC Main Drift Chamber

- MRI Magnetic Resonance Imaging

- MTBF The Mean Time Between Failures

- MUC Muon Chamber

- NATO North Atlantic Treaty Organization

- NIEL Non-Ionizing Energy Loss

- OPA OPeration Amplifier

- PET Positron Emission Yomography

- PID Particle Identification

- PMT PhotoMultiplier Tubes

- PS Proton Synchrotron

- PSRR Power Supply Ripple Rejection

- PTAT Proportional to Absolute Temperature

- SEE Single Event Effects

- SOI Silicon On Insulator

- SRAM Static Random Access Memory

- STI Shallow Trench Isolation

- TC Temperature Coefficient

- TID Total Ionizing Dose

#### TIGER Torino Integrated GEM Electronics for Readout

- TMR Triple Module Redundancy

- TOF Time Of Flight system

- VMC Voltage Mode Control

## Chapter 1

# The Development of the Front-End ASICs in High Energy Physics

### **1.1 High Energy Physics Research**

The object of high energy physics is to research the high energy photons and particles. One of the purposes is to research the origin of the world. For example, what is the matter composed of, how does the mass produce and so on. The normal research method is using an experimental application to detect the high energy photons and particles directly or indirectly.

Normally, the high energy photons and particles have two kinds of sources. One source comes from the high energy accelerator with the collider, the other source comes from the space. Up to now, the biggest and the highest energy collider is the LHC (Large Hadron Collider) at CERN, as shown in Figure 1.1. There are four experiments: CMS, ALICE, ATLAS and LHCb.

The LHC is about 27 kilometers long and 100 meters under the ground. The protons are accelerated up to 1.4 *GeV*, and through the Proton Synchrotron (PS), they can be accelerated up to 26 *GeV*. In 2012, the Higgs boson particle has been detected for the first time at LHC.

Other high energy accelerators with experimental application are for instance the BEPCII with BESIII (at IHEP, Beijing, China), the SuperKEKB with BELLEII (at KEK, Tsukuba, Japan), and so on. The higher energy accelerators experiments

Fig. 1.1: LHC including the CMS, ALICE, LHCb and ATLAS detectors

planed in the near future include the CEPC in China and the ILC in Japan, as shown in Figure 1.2.

Fig. 1.2: Comparision of CEPC, ILC and the present accelerators

Besides the collider, there are also other kinds of physics applications, such as the synchrotron radiation source, the spallation neutron source and so on. High energy physics applications benefits all of us in many aspects, especially in the nuclear medicine such as the magnetic resonance imaging (MRI), the positron emission tomography (PET), the Gamma Knife, the Proton knife and so on.

High energy physics investigates also the high energy photons and particles coming from the space. The main purpose is the history of the evolution and the origin of the universe. Because of the presence of the high energy photons and particles in the cosmic rays, this kind of research does not need accelerates and just need detectors. Research can be classified space detectors, ground detectors and underground detectors.

For space detectors, the platform includes the space station, satellite, and the ball based. Such as the AMS, HXMT, DAMPE and so on. The AMS is shown in Figure 1.3.

Fig. 1.3: AMS installed in the International Space Station

The newest detector facing the space high energy photons and particles is the HXMT satellite, which is made by IHEP, Beijing, China. The HXMT has been launched in June, 2017, and is shown in Figure 1.4. The HXMT can detect the low energy, the middle energy and the high energy *X* rays from 1 *keV* up to the 250 *keV*.

Fig. 1.4: Illustration of the payload configuration on the HXMT satellite

The ground detectors are mainly built on the high plateau area where the air is thin and dry. Such as the ARGO which is in the Tibet, China, which can detect the high energy particle indirectly.

The underground detectors are built in very deep places, the main purpose is to detect the high energy particles which can be filtered by the mountain and the ground, such as the neutrinos, the dark matter particles and so on.

The development of high energy physics requires the use of the detectors and the corresponding front-end readout electronics. Because of each is unique, the front-end electronics is not available in the market. This need to design a custom Application-Specific Integrated Circuit (ASIC) to be used in the detectors. Next section is about the front-end ASIC suitable for high energy physics detectors.

#### **1.2** Power management status in front-end ASICs

By investigating the ASIC of high-energy physics front-end electronics, it is found that most of the ASIC chips do not integrate power management and use external power supply. Comparing with the external power supply, the on-chip power management system has three advantages:

The first advantage is that it can improve the load respond ability of the front-end electronic. Off-chip power supply will have the parasitic inductance brought by the pins and bonding wires, which is about between a few nH to a few tens of nH. When the front-end electronic current changes rapidly, not only the interference voltage is generated by the parasitic inductance, but also the reaction speed is delayed. The on-chip power supply is more suitable in such situations.

The second advantage is that the power supply area can be reduced. The on-chip power supply system can save the additional package area, so it is suitable for area sensitive applications.

The third advantage is that the common power management chips have poor radiation resistance. Even if there is the commercial shelf chip with good antiradiation capability, it will be expensive, long delivery period or difficult to buy (later discussing further). Designing one new power management can integrate radiation-aware methods. In order to understand the current state of power management in front-end electronics in the field of high energy physics, this thesis researched the main high energy physics experiments. The following three tables are for the ASICs being used and ready to be used in some of the world's major high energy physics experiments.

| Experiment Sub- | t Sub-                 | Name        | Description             | Frontier | Frontier Institution Type | Type   | Technology Power       | Power | State                                     |

|-----------------|------------------------|-------------|-------------------------|----------|---------------------------|--------|------------------------|-------|-------------------------------------------|

|                 | moneke                 |             |                         |          |                           |        |                        |       |                                           |

| ATLAS           | pixel                  | FE-I3       | pixel front end<br>chip | Energy   | LBNL                      | mixed  | 250nm<br>CMOS          | Outer | Running exper-<br>iment                   |

| ATLAS           | pixel                  | FE-14       | pixel front end<br>chin | Energy   | LBNL                      | mixed  | 130 <i>nm</i><br>CMOS  | Inner | Approved ex-<br>neriment                  |

| ABCD            | strips                 | ABCD        | strip front end         | Energy   | UCSC                      | mixed  | 0.8 <i>um</i>          | Outer | Running exper-<br>iment                   |

| ATLAS           | strips                 | ABCn        | strip front end<br>chip | Energy   | UCSC,Penn mixed           | mixed  | 250nm<br>CMOS          | Inner | Candidate for<br>Approved ex-             |

| ATLAS           | upgrade                | ABC-        | strip front end         | Energy   | Penn,UCSC mixed           | mixed  | 130 <i>nm</i>          | Outer |                                           |

| ATLAS           | upgrade                | 130<br>HCC- | chip<br>strip front end | Energy   | Penn,UCSC mixed           | mixed  | CMOS<br>130nm          | Outer | Approved ex-<br>periment<br>Candidate for |

|                 | )                      | 130         | chip                    | 3        |                           |        | CMOS                   |       | Approved ex-<br>periment                  |

| ATLAS           | TRT                    | ASDBLR      | Rstraw front end        | Energy   | Penn                      | analog | 0.8 <i>um</i><br>DMILL | Outer | Running exper-<br>iment                   |

| ATLAS           | Muon<br>Samll<br>Wheel | VMM         | front end               | Energy   | BNL                       | mixed  | 130nm<br>CMOS          | Outer | Approved ex-<br>periment                  |

| ATLAS           | Muon<br>CSC            | ASM1        | preamp                  | Energy   |                           | analog | 0.5um<br>CMOS          | Outer | Running exper-<br>iment                   |

Table 1.1: Power management comparison table 1 in front-end ASICs of high energy physics[3]

### The Development of the Front-End ASICs in High Energy Physics

| Experiment Sub-<br>systemNameSystemSystemPHENIXstripsSVX4PHENIXstripsFPHXCLAS12stripsFSSR2CLAS12stripsFSSR2CMS&stripsFSSR2BellellPixelPSI46CMSpixelPSI46CMSECALFENIX | Description                     | ŗ                 | •                         | [      | -                     | ſ     | č                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|---------------------------|--------|-----------------------|-------|-----------------------------------------|

| ,                                                                                                                                                                    |                                 | Frontier          | Frontier Institution Type | Type   | Technology Power      | Power | State                                   |

| ,                                                                                                                                                                    | strip front end<br>chip         | Nuclear<br>Pvsics | LBNL,FNAImixed            | Imixed | 250nm<br>CMOS         | Outer | Running exper-<br>iment                 |

| L                                                                                                                                                                    | strip front end<br>chip         | Nuclear<br>Pysics | FNAL                      | mixed  | 250nm<br>CMOS         | Outer | Running exper-<br>iment                 |

|                                                                                                                                                                      |                                 | Nuclear<br>Pysics | FNAL                      | mixed  | 250nm<br>CMOS         | Outer | Approved ex-<br>periment                |

| L                                                                                                                                                                    |                                 | Energy/intensity  | tensity                   | mixed  | 250nm<br>CMOS         | Outer | Approved ex-<br>periment                |

|                                                                                                                                                                      | pixel front end<br>chip         | Energy            | ı                         | mixed  | 250nm<br>CMOS         | Outer | Running exper-<br>iment                 |

|                                                                                                                                                                      | front end,<br>tri <u>e</u> &DAO | Energy            | ı                         | analog | 250nm<br>CMOS         | Outer | Running exper-<br>iment                 |

| Calorimeter GCFE                                                                                                                                                     | calorimeter<br>front end        | Cosmic            | SLAC                      | analog | 500nm<br>CMOS         | Outer | Running exper-<br>iment                 |

| Tracker GTFE                                                                                                                                                         | strip front end<br>chip         | Cosmic            | UCSC,SLAGnixed            | Gnixed | 500nm<br>CMOS         | Outer | Running exper-<br>iment                 |

| Anti Coin- GAFE cidence                                                                                                                                              | PMT front end                   | Cosmic            | SLAC                      | analog | 500nm<br>CMOS         | Outer | Running exper-<br>iment                 |

| TPC nEXO-<br>FE                                                                                                                                                      | front end                       | Intensity SLAC    | SLAC                      | analog | 180 <i>nm</i><br>CMOS | Outer | Candidate<br>for proposed<br>experiment |

| Experiment Sub- | Sub-         | Name             | Description                 | Frontier         | Frontier Institution Type | Type  | Technology Power | y Power | State          |

|-----------------|--------------|------------------|-----------------------------|------------------|---------------------------|-------|------------------|---------|----------------|

|                 | system       |                  |                             |                  |                           |       |                  |         |                |

| LHC             | pixel        | CHIPIX65         | pixel front end Energy INFN | Energy           | INFN                      | mixed | 65 <i>nm</i>     | Inner   | Approved ex-   |

|                 |              |                  | chip                        |                  |                           |       | CMOS             |         | periment       |

| KLOE-2          | strips       | <b>GASTONE64</b> | GASTONE64 strip front end   | Energy           | INFN                      | mixed | 130nm            | Outer   | Running exper- |

|                 |              |                  | chip                        |                  |                           |       | CMOS             |         | iment          |

| Belle II        | Muon         | TARGET6B         | scin                        | intensity Hawaii | Hawaii                    | mixed | 250nm            | Outer   | Approved ex-   |

|                 | System       |                  | strip/MPPC                  |                  |                           |       | CMOS             |         | periment       |

|                 |              |                  | readout                     |                  |                           |       |                  |         |                |

| CTA             | Camera       | Camera TARGET5/7 | scin                        | cosmic           | Hawaii                    | mixed | 250nm            | Outer   | Candidate      |

|                 | trig/readout | out              | strip/MPPC/MA               |                  |                           |       | CMOS             |         | for proposed   |

|                 |              |                  | PMT readout                 |                  |                           |       |                  |         | experiment     |

8

From these tables above, it can be seen that the main front-end electronics ASIC chips running in high-energy physics experiments are off-chip power management systems (red fonts). Among the next-generation experiments, there are three on-chip power management systems for front-end electronics ASICs, integrating DC/DC and LDO circuits (blue fonts) on-chip. The table reflects that the integrating power management system on the front-end chips is a relatively new direction and is a field worthy of research and exploration.

### **1.2.1 Radiation-aware Demands in High Energy Physics Applications**

Because of the main purpose of high energy physics application, which is detecting the photons and particles, the radiation effect is inevitable. Different surroundings have different radiation-aware demands. So the front-end design must consider the special radiation environment.

Before the design of the electronics, the demand of the radiation must be clear. Some radiation effect depends on the continuous working time, some radiation effect are random but depends on the LET. For example, the applications used in space must consider the radiation from the sun, the cosmic rays, and so on, different orbits (height and inclination) have different radiation-aware demand. The LHC at CERN demands the anti-radiation effect up to 1 Grad(Si) and  $10^{16} Neutrons/cm^2$  in 10 years.

From the applications environment, the kinds of high energy particles and photons should be clear, and the quantity and density state can also be gotten from the simulation or from real measurement data. According to the real radiation situation, what kinds of radiation-aware components and what kinds of ASIC technology can be selected.

Another important situation should be taken into account. The United States has a national law, which is the "Export Administration Regulations" of the Bureau of Industry and Security. This national law forbids the American components, which have the above 100 *krad*(Si) anti-radiation ability, to export to the non-NATO organization including P.R.C. But most of the radiation-aware components comes from the United States. So when buying these components from the United States

and using it the projects in P.R.C, there will be some problems even through the third part country.

### **1.3** Context and Motivation

The radiation-aware power management circuit for the front-end ASIC is motivated by the need of the CGEM-IT detector which is shown in Figure 1.5. It is used in the BESIII project at IHEP, Beijing, China. The CGEM-IT multichannel front-end ASIC is named TIGER and it is made using the UMC 110 *nm* technology.

Fig. 1.5: Cylindrical GEM detector Inner Tracker (CGEM-IT)

When designing this CMOS front-end circuit, there was not enough space for the LDO on-chip and just integrated the voltage and current bias circuit. So the radiation-aware components are needed for the power supply of the TIGER, as shown in Figure 1.6. But because of the USA law mentioned in the last section, the high-quality anti-radiation power supply components cannot be imported to P.R.C., even through the third country. So it is necessary to design the radiation-aware power supply ASICs.

At the same time, the voltage and current bias circuit in the first version TIGER have not been designed properly, affecting the baseline holder. The result is the baseline voltage uncontrolled shift. So the power management including the power

Fig. 1.6: TIGER chip bonded to the board

supply and bias circuit should be investigated carefully. The result of the research can be used in the TIGER likely front-end circuits in high energy physics applications.

The CHIPIX65 project is another motivation for this power management design. This project uses the TSMC 65 *nm* technology, and its purpose is to exploit the 65 *nm* CMOS advanced technology used in the new generation pixel detectors. This innovative 65 *nm* CMOS chip will be used in the experiment with extreme particle rates and radiation at future High Energy Physics colliders.

This CHIPIX65 project gives the opportunity to tape out for verifying the power management CMOS design on-chip, and the new power management chip is the CHIPIX65-LDO-BUCK. If this kind of power management is successful, it not only can be used in the CHIPIX65 project but also can be used to other similar projects.

The TSMC 65 *nm* technology has another superiority about the radiation-aware design. That is the radiation transistor model. This model is made by Mohsine Menouni and his colleagues [4] at CERN, and though this radiation transistor model the 200 *Mrad*(Si) and 500 *Mrad*(Si) Total Ionizing Dose (TID) radiation effect can be simulated.

### **1.4 Thesis Outline and Original Contributions**

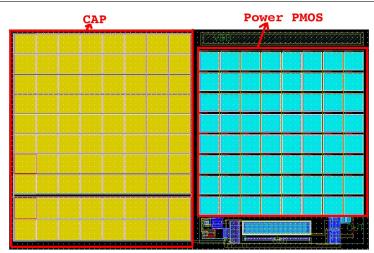

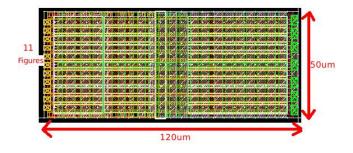

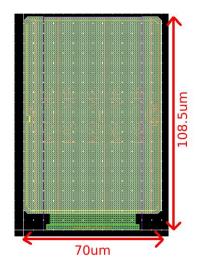

the main content of the thesis is designing one radiation-aware power management ASIC named CHIPIX65-LDO-BUCK, which can supplies the TIGER front-end chip used in the BESIII experiment. And this thesis deals with the design by TSMC 65 *nm* technology, which includes three kinds of LDOs, two kinds of bandgaps,

one kind of switch DC-DC and one current source. The three kinds of LDOs use three kinds of NMOS transistors: the standard transistor, the H shape transistor and the ELT transistor. The two kinds of bandgaps use two different circuit structures, which can used in the advanced technology. The DC/DC type is buck, and it works together with three LDOs, two bandgaps, to get one good power management for the front-end circuit.

This thesis consists of seven chapters and one appendix.

The Chapter 1 introduces the development of high energy physics applications and the main stream front-end ASICs are introduced. Then the power management system, used in such front-end ASICs based on the features of high energy physics, is introduced. At last, the context and motivation for this thesis are introduced.

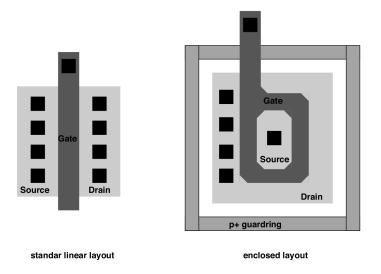

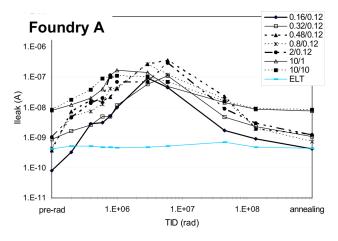

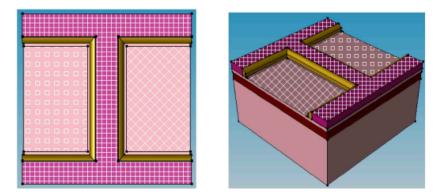

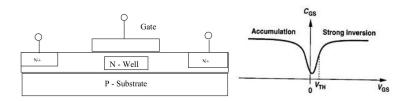

The Chapter 2 mainly focuses on the radiation effect on CMOS technology such as the TID, SEE. Based on this analysis, some radiation-aware methods are introduced. This chapter offers a new kind of shape transistor, the H shape transistor, which has a good radiation-aware ability. This transistor has some advantages such as the smaller size, and the better symmetry. Although the radiation-aware ability of H shape transistor is less than the Enclosed Layout Transistor (ELT), it is enough for the most radiation applications.

The Chapter 3 introduces the bias and the power management issues in the multichannel front-end. As the nuclear detector channels developing, the multichannel front-end becomes the mainstream. This needs the special bias circuit including the voltage and current bias. After that, the power supply to the front-end is described, which provides different kinds of power supplies. At the end, the auxiliary issues in the front-end are studied.

The Chapter 4 goes through the building blocks of the CHIPIX-LDO-BUCK: the radiation-aware LDO and bandgap. Differently from the classical LDO, this chapter uses the new architecture to design the LDO, which is suitable for the analogue digital mixed circuit. Then the bandgaps are described, and a new type of bandgap is introduced, which does not use the OPA, so the bandgap saves a lot of power consumption.

The Chapter 5 talk about the BUCK block of the power management. The BUCK is the most used switch DC-DC conversion in the front-end, and this chapter designs the Pulse Width Modulation (PWM) generator, the comparator with the compensation

circuit. These circuits can work together with the off-chip inductor, capacitor, and the power MOSFETs, and output the lower voltage with high efficiency.

The Chapter 6 covers the layout design of the power management CMOS ASIC which uses the TSMC 65 *nm* technology. The pads distribution with the anti-ESD design is also included. Then the test board is designed. At last, test of the ASIC, read out the data, and compare the post simulation result with the test data.

The Chapter 7 deals with the outlook and conclusion.

The Appendix A introduces the CGEM-IT front-end design, which is the application background of the power management. This chapter describes the CGEM-IT detector principle, and gives out the design details of the preamplifier and the shaper with the baseline holder.

The original contributions of this thesis are as following. The first one is the H shape transistor. This is one new structure which have some radiation-aware ability for the TID radiation. Comparing the ELT structure, the H shape structure have less anti-radiation ability, but it uses less area, and it can get more flexible size (CMOS ratio). It can also use the normal simulation model to extract parasitic parameters for the post simulation, and contrasting to this, the ELT need special simulation model. The H shape transistor is more suitable for the radiation-aware (light anti-radiation) design.

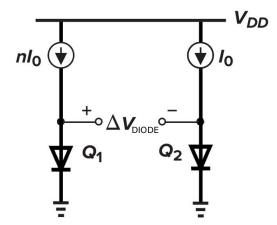

The second original contribution is the new structure bandgap without OPA. This kind of bandgap not only can work in very low supply voltage (low to 0.9 V), but also use very few current. Comparing the bandgap with OPA, all the current is used for the temperature compensation, this new structure has more current efficiency. Moreover, this kind structure uses the PMOS, instead of the parasitic triode, as the negative temperature coefficient generator. Comparing the classic triode, the PMOS has better anti-radiation ability. This kind of structure is more suitable for the advanced technology ASIC in high energy physics application.

# Chapter 2

# The Radiation-Aware Methods on CMOS Technology in High Energy Physics

In high energy physics applications, most of the electronics is exposed to the high energy photons and particles. Generally, there are two kinds of high energy physics application situations. One is to detect high energy particles in space such as the space station (AMS, HERD etc.) or the dedicated satellite (EXOSAT, BeppoSAX, DAMPE, HXMT etc); the other is to detect high energy particles at accelerators such as at LHC at CERN, BELLE at KEK, BESIII at IHEP etc. The electronic equipment will encounter different high energy photons and particles according to the different situations. The space radiation effect is shown in Figure 2.1.

Fig. 2.1: Space radiation source and the possible damage effect

## 2.1 Interaction between High Energy Particles and Semiconductor Material

The nature of the radiation effects is due to high energy photons and particles interacting with the material such as the semiconductor, and changes the electron or atomic nucleus of the semiconductor, then changes the character of the semiconductor. So the first thing is to explain the interaction between the high energy radiation and the material.

The high energy photons, such as X-rays or gamma rays, can produce photoelectric effect, Compton scattering effect and pair production effect in the semiconductor material. And the high energy particles will mainly produce the ionization effect in the semiconductor material.

When the energy of the photons is about several keV, the main effect is the photoelectric effect. Some electron-hole pairs can be generated when a high energy photon is absorbed in the material. In the photoelectric effect the photon energy is fully absorbed by one of the electrons of the inner shells (K and L shells). Therefore the electron gets a large kinetic energy which will be lost crossing the material, causing the creation of electron-hole pairs.

When the energy of the photons is about several hundred keV (corresponding to an X-ray or gamma ray), the main effect is the Compton scattering effect. When a high energy photon interacts with a quasi-free electron (of the external shells) a Compton scattering occurs, as shown in Figure 2.2. Some energy is transferred from the photon to the electron and on the contrary the photon energy is lowered.

Fig. 2.2: Compton effect diagram

When the energy of the photons is above  $1024 \ keV$ , the main effect is the pair production effect. If the energy of the photons is high enough, when the photons go

through the nucleus, under the nuclear coulomb field, the high energy photon will create a pair of one positron and one negative electron. And then the positron stops in the material, and annihilates with an electron of the material, producing a photon pair. The secondary energy photons will continue to interact with the semiconductor, and thus form the showering, get a lot of low energy photons and electrons. Pair production effect is shown in Figure 2.3.

Fig. 2.3: Pair production effect diagram

All these three effects result in the production of one electron with a certain kinetic energy (depending on the effect and on the energy of the photon), which has been, partially or totally, transferred by the photon. Then this electron will deposit its energy in the medium. In a semiconductor material the deposited energy during the slowing down of the electron can produce a small or a large number of electron-hole pairs.

The high energy particles which can radiate the semiconductor are divided into two classes: charged particles and neutral particles, such as neutrons. When the neutron occurs the elastic collision with the nucleus in the semiconductor lattice, if the neutron kinetic energy is high enough, it will hit the nucleus out and make the lattice having some defect. The defect lattice will influence the character of the semiconductor.

The high energy charged particles are mainly electrons, protons, and heavy ions. The effect between the charged particles and the semiconductor is the electromagnetic interaction, including the ionization, hit out, coulomb scattering and so on. Among them, the main radiation effect is the ionization. When the incident charged particle interact with the orbital electrons, by means of Coulomb interaction, a loss of the energy occurs. At the same time, the orbiting electron get some energy. When the orbiting electron gets enough energy to overcome the bond of the nucleus, the orbiting electron becomes a free electron. This is the ionization. The result of the ionization is positive ions and free electrons. If the inner shell electrons are thrown out, the outer electron will transfer into the inner shell for filling, at the same time an X-ray or an Auger electron is emitted. If the orbiting electron gets fewer energy and thus cannot overcome the bond of the nucleus, the orbiting electron will transfer to an higher energy level. This is the excitation of the atom. The atoms of the excited state are not stable, so after a short time, they will go back to the ground state. When this course happens, the released energy will be in the form of fluorescence.

To measure the ionization effect, the normal method is to measure the lost energy (-dE/dx) of particles through some material. The -dE/dx can be expressed by the Bethe Bloch formula (2.1).

$$-\frac{dE}{dx} = \frac{4\pi}{m_e c^2} \cdot \frac{nz^2}{\beta^2} \cdot \left(\frac{e^2}{4\pi\varepsilon_0}\right)^2 \cdot \left[\ln\left(\frac{2m_e c^2\beta^2}{I\cdot(1-\beta^2)}\right) - \beta^2\right]$$

(2.1)

where *c* is the speed of light,  $\varepsilon_0$  is the vacuum permittivity,  $\beta = v/c$  is the particle speed, *e* and *m<sub>e</sub>* are the electron charge and rest mass respectively. Here, the electron density of the material can be calculated by

$$n = \frac{N_A \cdot Z \cdot \rho}{A \cdot M_{\mu}} \tag{2.2}$$

where  $\rho$  is the density of the material, Z is the atomic number, A is the relative atomic mass number,  $N_A$  is the Avogadro number and  $M\mu$  is the Molar mass constant. The high energy charged particle ionizing the semiconductor is shown in Figure 2.4.

In addition, the main radiation damage caused by the high energy photons is also ionizing effect. Because these high energy photons (X rays or  $\gamma$  rays) will be converted into high energy electrons, protons, and ions in a very short time. These second charged particles will ionize the semiconductors and result in the main radiation damage. The different radiation effects caused by the particles and photons are shown in Figure 2.5. The more electron-hole (*e-h*) pairs means the more radiation damage.

From Figure 2.5, it can be found that the heavy ions will give the largest radiation damage. But the heavy ions are rare. The protons will be often a lot in these

### 18 The Radiation-Aware Methods on CMOS Technology in High Energy Physics

Fig. 2.5: Schematic view of the density of *e*-*h* pairs caused by different radiation

situations, and the proton can also create a large number of *e*-*h* pairs. So the protons often cause the main radiation damage.

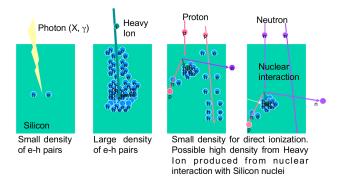

### 2.2 Radiation Effects on CMOS Semiconductor

According to the radiation process, the radiation effect can be divided into two classes. One is the accumulation radiation effect, and the other is the non-accumulation radiation effect. The slow accumulation effect includes the ionization effect (Total Ionizing Dose, TID) and the non-ionization effect (Non-Ionizing Energy Loss, NIEL). The non-accumulation radiation effect is named the Single Event Effects (SEE). The TID and NIEL depend on the time, but the SEEs are random. The SEEs depend on the position of the hits, the energy, the ionization state of the particles and the working state of the circuit. The NIELs are often caused by the high-speed neutrons and can kick the nucleus out of the lattice, therefore resulting in the displacement effects. The displacement effects often happen in the bipolar technologies and the optoelectronic devices. CMOS technology devices will not be influenced. The CMOS devices are mainly affected by the TID and the SEE. The radiation effects on the electron devices can be seen in Figure 2.6.

Fig. 2.6: Radiation effects on the semiconductor devices

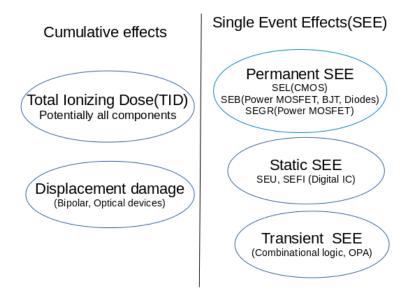

### 2.2.1 TID Effects on CMOS Technology Devices

TID is the measurement of the total dose, which is the deposited energy in the material. The unit is *Gray* in the International System (IS), but the radiation effects community still often uses the old unit, rad(Si). One should get used to both of them, because the dosimeter persons speak about *Gray*, whilst electronic engineers working on the effects always speak about rad(Si). Luckily, the equivalence between the two is easy to count:

$$1 \operatorname{Gray}(\operatorname{Gy}) = 100 \operatorname{rad} \tag{2.3}$$

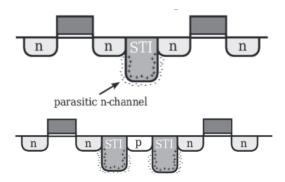

In CMOS technology devices, the TID is mainly caused by the ionizing radiation effect. The high energy photons and charged particles will produce many electronhole pairs in the CMOS device, especially in the oxide place. The TID mainly happen in two places. One is the gate oxide, and the other is the insulating oxide (or the field oxide). The insulating oxide is the LOCOS in the old technology and the STI in the recent technology.

#### **Threshold Voltage Shifts**

The TID effect course in the gate oxide is shown in Figure 2.7. The charged particles ionize the oxide of the gate, and then the electron-hole pairs are produced.

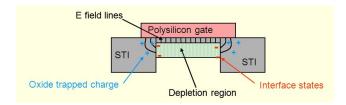

Fig. 2.7: TID effect on the gate oxide

The ionized electrons will go to the gate side easily under the electric field, and at the end go out of the CMOS. In contrast, because of the ionized holes bigger size and slower moving speed, most of the holes will stay in the oxide. In absence of electrons, the hole cannot recombine and are trapped in the oxide. Therefore, the gate oxide will accumulate plenty of holes with much positive charge.

To the transistors, this positive charge will change the threshold voltage. To the NMOS transistors, the threshold voltage is positive, so the trapped positive will reduce the threshold voltage. To the PMOS transistors, the trapped positive holes will also reduce the threshold. But because the threshold voltage is negative, the absolute value increases. The changed threshold voltage  $V_{ox}$  is

$$\Delta V_{ox} = -\frac{q}{C_{ox}} \left( \Delta N \right) \tag{2.4}$$

where q is the electron charge  $1.6 \times 10^{-19} C$ ; C<sub>ox</sub> is the specific gate capacitance, the unite is  $F/m^2$ ;  $\Delta N$  is the surface density of the trapped holes; the unit is  $m^{-2}$ .

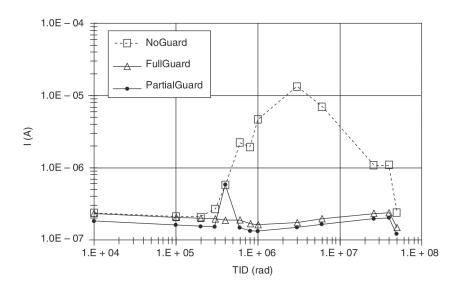

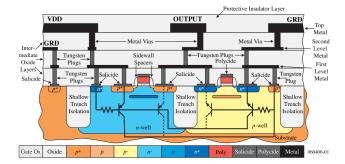

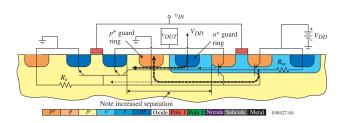

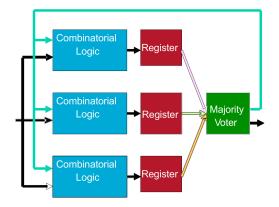

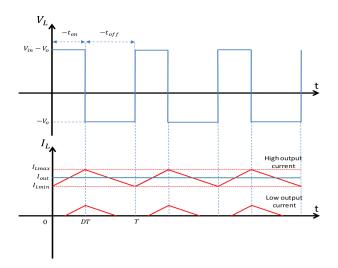

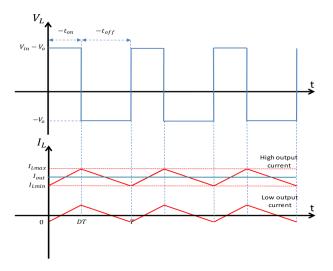

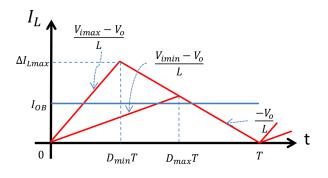

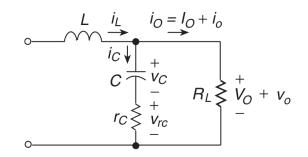

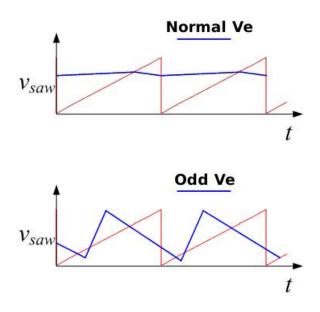

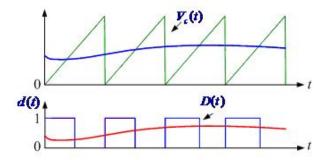

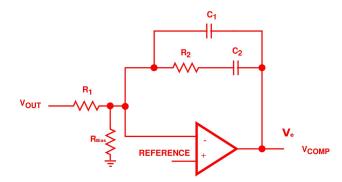

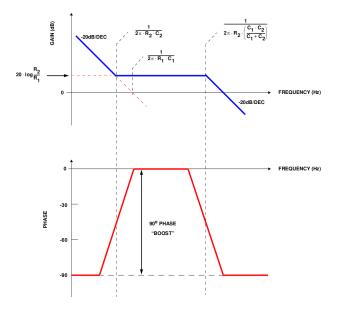

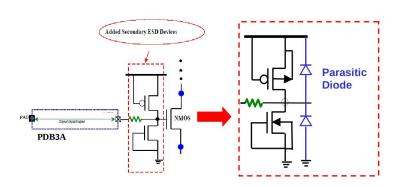

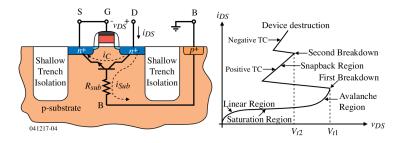

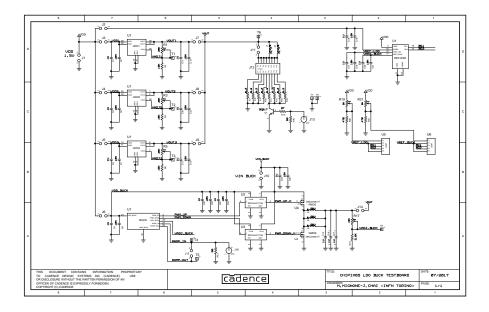

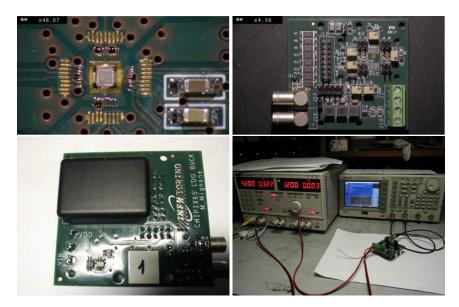

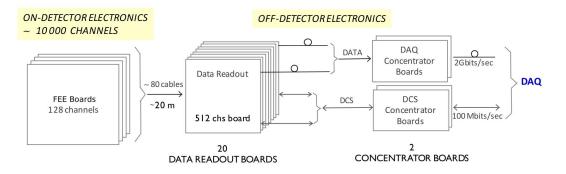

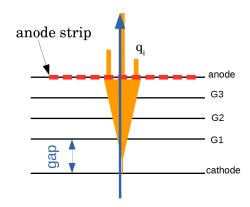

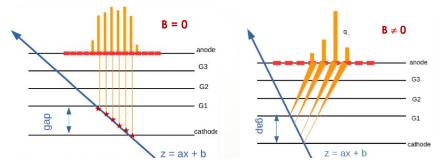

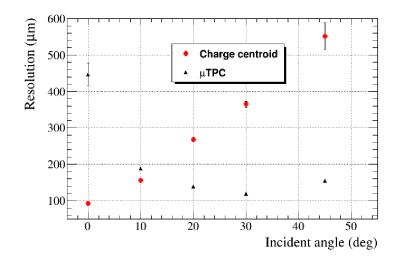

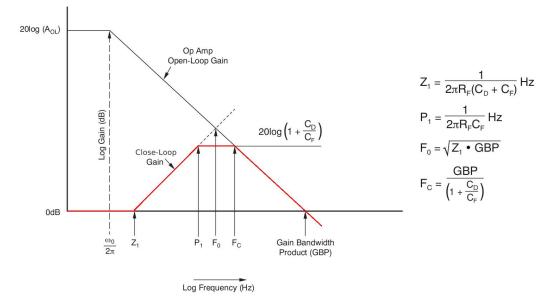

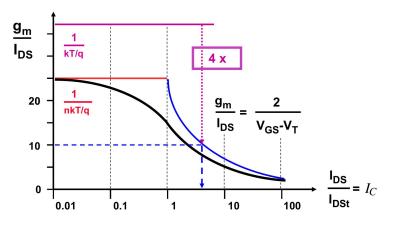

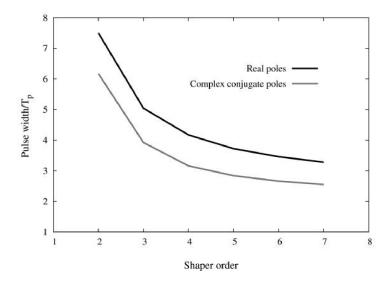

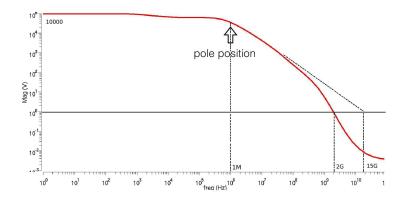

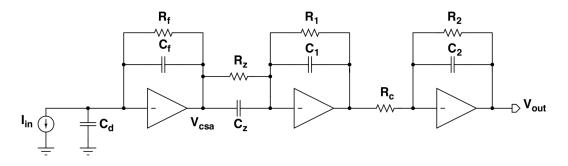

Besides the trapped holes in the gate, the radiation also creates the interface states between the oxide and the crystalline silicon. The build-up course of the interface states is very slower than the direct hole trapping, so the device characteristics will change continue even if the irradiation action has stopped [1].