# Doctoral Dissertation Doctoral Program in Computer and Control Engineering ( $30^{th}$ cycle)

# Visual Analysis Algorithms for Embedded Systems

By

## Syed Tahir Hussain Rizvi

\*\*\*\*\*

### **Supervisor(s):**

Prof. Gianpiero Cabodi

### **Doctoral Examination Committee:**

Prof. M. Grangetto, Referee, Università degli Studi di Torino, Italy

Prof. A. J. Telmoudi, Referee, University of Sousse, Tunisia

Prof. M. Matteucci, Politecnico di Milano, Italy

Prof. A. G. Bottino, Politecnico di Torino, Italy

Prof. S. Mattoccia, Università di Bologna, Italy

Politecnico di Torino 2018

## **Declaration**

Syed Tahir Hussain Rizvi 2018

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

| I would like to dedicate this thesis | s to my loving family for their constant support and encouragement. |

|--------------------------------------|---------------------------------------------------------------------|

|                                      |                                                                     |

|                                      |                                                                     |

|                                      |                                                                     |

|                                      |                                                                     |

|                                      |                                                                     |

## Acknowledgements

I would like to thank my thesis supervisor, Prof. Gianpiero Cabodi, for allowing me to work under his supervision and constantly supporting me during my Ph.D. studies. I would also like to thank my research group members at the Joint Open Lab (JOL) Visible, especially Gianluca Francini and Alfonso Di Salvo, for all the help they provided. I am grateful to TIM, former Telecom Italia for financing my Ph.D. studies. I must also thank Denis Patti for his help regarding the realization of proposed framework on Android devices.

### **Abstract**

The main contribution of this thesis is the design and development of an optimized framework to realize the deep neural classifiers on the embedded platforms. Deep convolutional networks exhibit unmatched performance in image classification. However, these deep classifiers demand huge computational power and memory storage. That is an issue on embedded devices due to limited onboard resources. The computational demand of neural networks mainly stems from the convolutional layers. A significant improvement in performance can be obtained by reducing the computational complexity of these convolutional layers, making them realizable on embedded platforms.

In this thesis, we proposed a CUDA (Compute Unified Device Architecture)-based accelerated scheme to realize the deep architectures on the embedded platforms by exploiting the already trained networks. All required functions and layers to replicate the trained neural networks were implemented and accelerated using concurrent resources of embedded GPU. Performance of our CUDA-based proposed scheme was significantly improved by performing convolutions in the transform domain. This matrix multiplication based convolution was also compared with the traditional approach to analyze the improvement in inference performance.

The second part of this thesis focused on the optimization of the proposed framework. The flow of our CUDA-based framework was optimized using unified memory scheme and hardware-dependent utilization of computational resources. The proposed flow was evaluated over three different image classification networks on Jetson TX1 embedded board and Nvidia Shield K1 tablet. The performance of proposed GPU-only flow was compared with its sequential and heterogeneous versions. The results showed that the proposed scheme brought the higher performance and enabled the real-time image classification on the embedded platforms with lesser storage

requirements. These results motivated us towards the realization of useful real-time classification and recognition problems on the embedded platforms.

Finally, we utilized the proposed framework to realize the neural network-based automatic license plate recognition (ALPR) system on a mobile platform. This highly-precise and computationally demanding system was deployed by simplifying the flow of trained deep architecture developed for powerful desktop and server environments. A comparative analysis of computational complexity, recognition accuracy and inference performance was performed.

# **Contents**

| Li | st of I | Figures                                 | X    |

|----|---------|-----------------------------------------|------|

| Li | st of T | Tables                                  | xiii |

| 1  | Intr    | oduction                                | 1    |

|    | 1.1     | Problem Statement                       | 2    |

|    | 1.2     | Contribution                            | 2    |

|    | 1.3     | Organization of the thesis              | 3    |

|    | 1.4     | Publications                            | 4    |

| 2  | Dee     | p Learning for Image Classification     | 6    |

|    | 2.1     | Deep Architectures                      | 9    |

|    |         | 2.1.1 AlexNet                           | 9    |

|    |         | 2.1.2 OverFeat                          | 10   |

|    |         | 2.1.3 VGG Net                           | 10   |

|    |         | 2.1.4 GoogLeNet                         | 11   |

|    |         | 2.1.5 ResNet                            | 11   |

| 3  | Ove     | rview of GPGPU Programming              | 14   |

|    | 3.1     | Programming Languages for GPU Computing | 14   |

|    | 3 2     | Arrangement of Computing Resources      | 15   |

viii Contents

|   | 3.3 | CUDA                                                  | Memory Model and Hierarchy                                           | 17 |

|---|-----|-------------------------------------------------------|----------------------------------------------------------------------|----|

| 4 | Neu | ural Architecture and CUDA-based Proposed Realization |                                                                      |    |

|   | 4.1 | Introdu                                               | action                                                               | 20 |

|   | 4.2 | Related                                               | d Work                                                               | 21 |

|   | 4.3 | Adopte                                                | ed Methodology                                                       | 23 |

|   | 4.4 | Archite                                               | ecture of the Convolutional Neural Networks                          | 25 |

|   |     | 4.4.1                                                 | Convolutional Layer                                                  | 25 |

|   |     | 4.4.2                                                 | Pooling Layer                                                        | 29 |

|   |     | 4.4.3                                                 | Batch Normalization                                                  | 29 |

|   |     | 4.4.4                                                 | Activation Functions (ReLu, Tanh and Threshold)                      | 29 |

|   |     | 4.4.5                                                 | Linear or Fully Connected Layers                                     | 30 |

|   |     | 4.4.6                                                 | Sizing Convolutional Neural Networks                                 | 30 |

|   | 4.5 | CUDA                                                  | -based Proposed Framework                                            | 31 |

|   |     | 4.5.1                                                 | GPGPU-accelerated Fully Convolutional Layer                          | 31 |

|   |     | 4.5.2                                                 | Heterogeneously Accelerated ConvMM Layer                             | 33 |

|   |     | 4.5.3                                                 | GPU-only ConvMM Layer                                                | 34 |

|   |     | 4.5.4                                                 | GPU-Accelerated Max and Average Pooling Layers                       | 36 |

|   |     | 4.5.5                                                 | GPU-Accelerated Batch Normalization and Other Layers                 | 36 |

|   |     | 4.5.6                                                 | Neural Network Architectures implemented in CUDA                     | 36 |

|   | 4.6 | Experi                                                | ments and Results                                                    | 38 |

|   |     | 4.6.1                                                 | Performance Evaluation of Proposed Scheme on Jetson TX1 Board        | 38 |

|   |     | 4.6.2                                                 | Performance Evaluation of Proposed Scheme on Mobile Shield K1 Tablet | 45 |

|   | _   |                                                       |                                                                      |    |

| 5 | _   |                                                       | on of Deep Neural Classifiers for Embedded GPUs                      | 51 |

|   | 5.1 | Introdu                                               | action                                                               | 51 |

| Contents |  | ix |

|----------|--|----|

|          |  |    |

| • |      |                                                                                        |            |

|---|------|----------------------------------------------------------------------------------------|------------|

| 7 | Con  | clusions and Future Work                                                               | 88         |

|   | 6.5  | Experiments and Results                                                                | 83         |

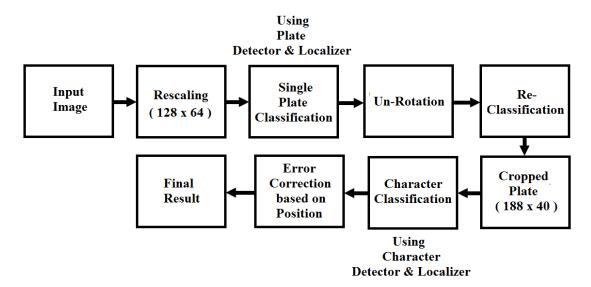

|   |      | 6.4.2 Simplified flow for Character Classification                                     | 81         |

|   |      | 6.4.1 Simplified flow for Plate Classification                                         | 80         |

|   | 6.4  | Simplified Flow for Mobile Platform                                                    | 78         |

|   | 0.5  | ronments                                                                               | 76         |

|   | 6.3  | Plate Recognition System Developed for Desktop and Server Envi-                        |            |

|   | 6.2  | Related Work                                                                           | 74         |

| - | 6.1  | Introduction                                                                           | 73         |

| 6 | Auto | omatic License Plate Recognition System on Mobile Platform                             | <b>7</b> 3 |

|   |      | 5.5.3 Performance Comparison with Torch framework                                      | 70         |

|   |      | GPUs having C.C. < 3.5)                                                                | 67         |

|   |      | 5.5.2 Performance Evaluation on Nvidia Shield K1 tablet (For                           |            |

|   |      | 5.5.1 Performance Evaluation on Jetson TX1 embedded board (For GPUs having C.C. > 3.5) | 62         |

|   | 5.5  | Experiments and Results                                                                | 62         |

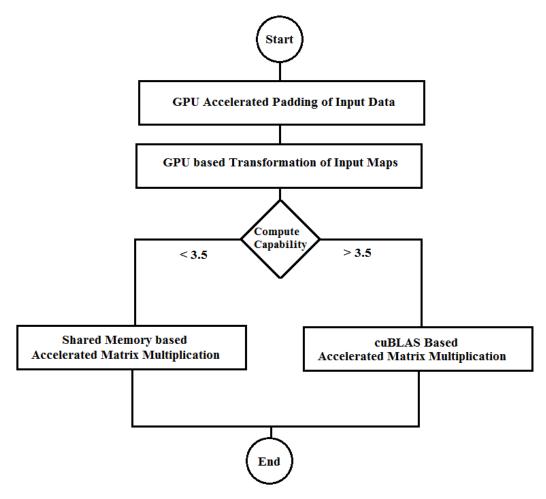

|   | 5.4  | GPU architecture based Exploitation                                                    | 61         |

|   | 5 A  | 5.3.2 Shared Memory-based Matrix Multiplication Convolution .                          | 59         |

|   |      | 5.3.1 cuBLAS-Accelerated Matrix Multiplication Convolution                             | 57         |

|   |      | layer                                                                                  | 57         |

|   | 5.3  | Accelerated Matrix Multiplication for GPU-only Unified ConvMM                          |            |

|   |      | 5.2.2 Proposed flow using Unified Memory-based Allocations                             | 54         |

|   |      | 5.2.1 Data Anocations using I finited Memory                                           | 55         |

|   |      | 5.2.1 Data Allocations using Pinned Memory                                             | <b>5</b> 3 |

# **List of Figures**

| 2.1 | A single neuron of ANN                                         | 6  |

|-----|----------------------------------------------------------------|----|

| 2.2 | Feedforward neural network                                     | 7  |

| 2.3 | The architecture of a typical CNN                              | 8  |

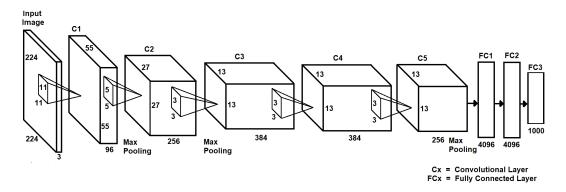

| 2.4 | AlexNet                                                        | 9  |

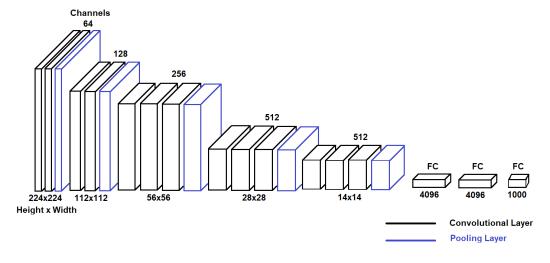

| 2.5 | Architecture of VGG-16                                         | 10 |

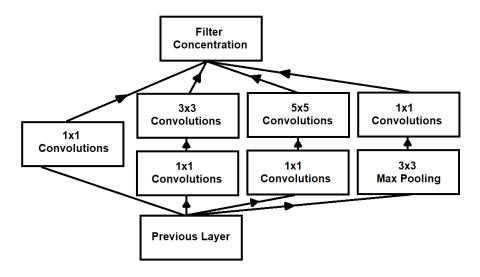

| 2.6 | The inception module                                           | 11 |

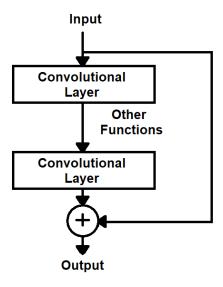

| 2.7 | Residual block                                                 | 12 |

| 2.8 | Evolution of deep convolutional neural networks                | 13 |

| 3.1 | Structure of a CUDA program                                    | 16 |

| 3.2 | Arrangement of GPU resources                                   | 17 |

| 3.3 | CUDA memory types                                              | 18 |

| 3.4 | CUDA hierarchy of threads, blocks and grids with corresponding |    |

|     | memory spaces                                                  | 19 |

| 4.1 | Block diagram of the CUDA-based neural classifier for embedded |    |

|     | platform                                                       | 24 |

| 4.2 | Multi-dimensional full convolution                             | 27 |

| 4.3 | Matrix multiplication based convolution (ConvMM)               | 28 |

| 4.4 | Effect of stride length on the size of output maps             | 30 |

| 4.5 | Effect of padding and stride length on the size of output maps | 31 |

List of Figures xi

| 4.6  | Flow of GPGPU-based convolutional and pooling layers                                                                       | 32 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 4.7  | (a) Flow of heterogeneous ConvMM layer; (b) Flow of full convolutional layer                                               | 34 |

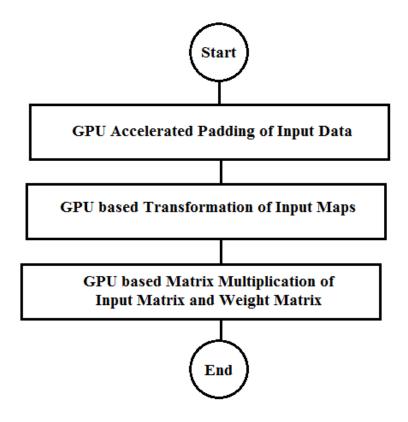

| 4.8  | Flow of GPU-only ConvMM layer                                                                                              | 35 |

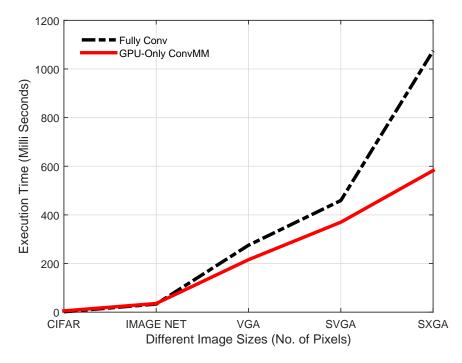

| 4.9  | Full convolution vs. GPU-only ConvMM as a function of input image size (Jetson TX1 Board)                                  | 39 |

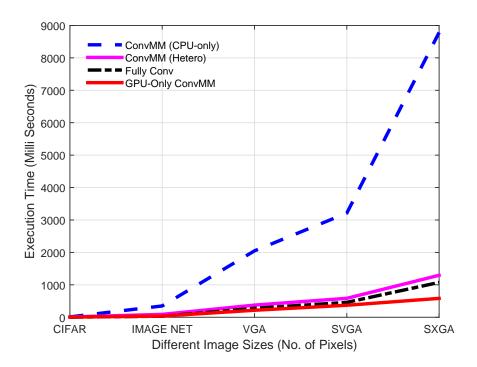

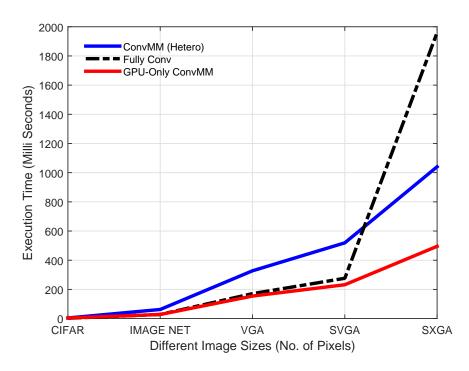

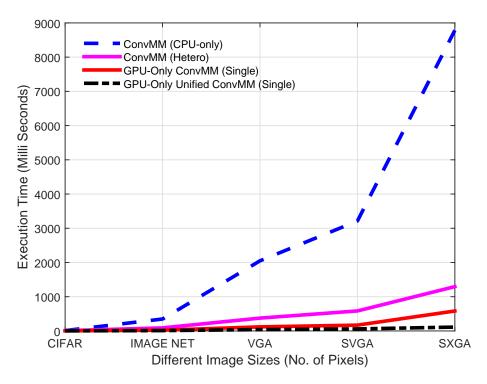

| 4.10 | Comparison of different versions of convolution operation as a function of the input image size (Jetson TX1 Board)         | 40 |

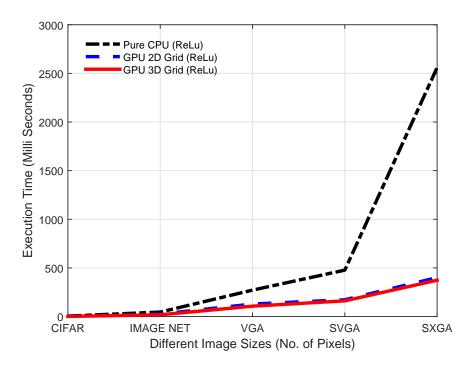

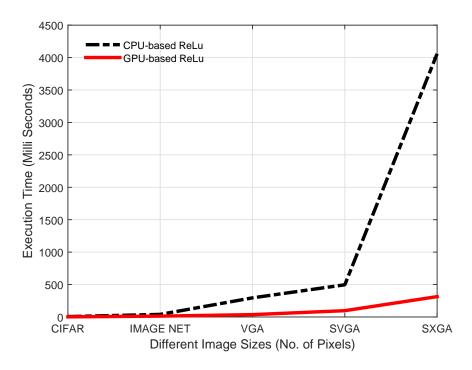

| 4.11 | Performance comparison of rectifier linear unit on Jetson TX1 board as a function of input image size.                     | 41 |

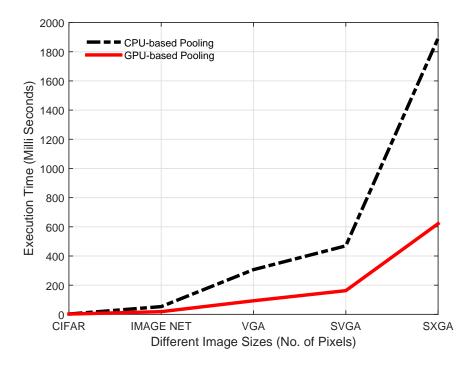

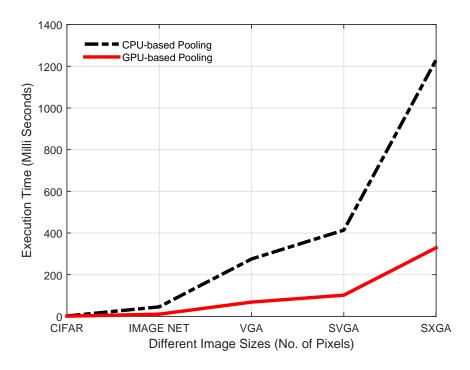

| 4.12 | Performance comparison of pooling layers on Jetson TX1 board as a function of input image size                             | 42 |

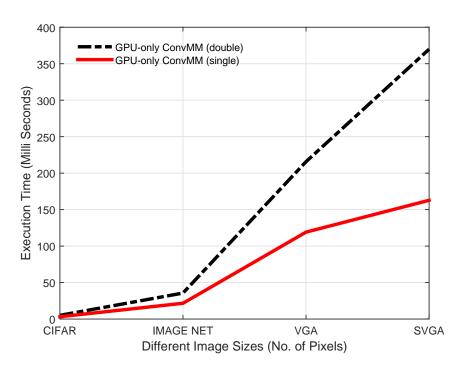

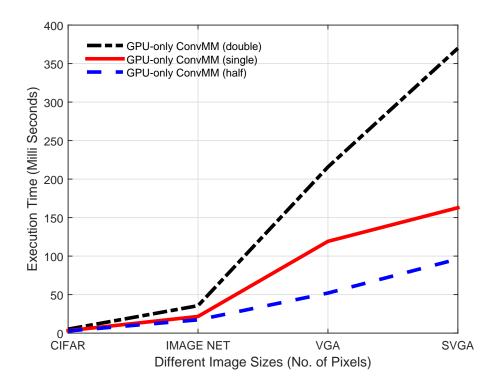

| 4.13 | Performance comparison of double- and single-precision ConvMM layers on Jetson TX1 Board as a function of input image size | 44 |

| 4.14 | Comparison of different versions of convolution operation as a function of input image size (Nvidia Shield Tablet)         | 46 |

| 4.15 | Performance comparison of rectifier linear unit on Nvidia Shield K1 tablet as a function of input image size               | 47 |

| 4.16 | Performance comparison of pooling layers on Nvidia Shield K1 tablet as a function of the input image size                  | 48 |

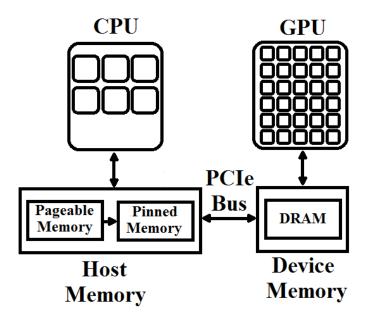

| 5.1  | Pinned and pageable memories on the host (CPU) side                                                                        | 53 |

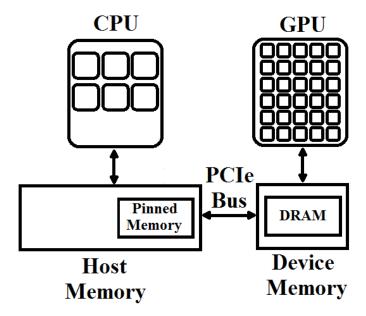

| 5.2  | Data transfer directly from the Pinned memory                                                                              | 54 |

| 5.3  | Physically separate Host and device memories                                                                               | 55 |

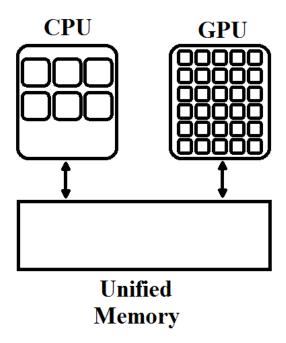

| 5.4  | Shared pool of Unified memory                                                                                              | 56 |

| 5.5  | The flow of GPU-only Unified ConvMM Layer                                                                                  | 56 |

| 5.6  | Flow of the accelerated matrix multiplication based ConvMM layer with unified memory                                       | 58 |

| 5.7  | (a) Naive matrix multiplication approach; (b) Shared memory-based matrix multiplication approach.                          | 60 |

xii List of Figures

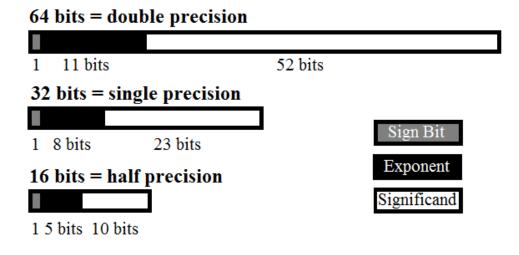

| 5.8  | Format of floating point representation (IEEE754)                                                                                                                                                                                      | 61 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

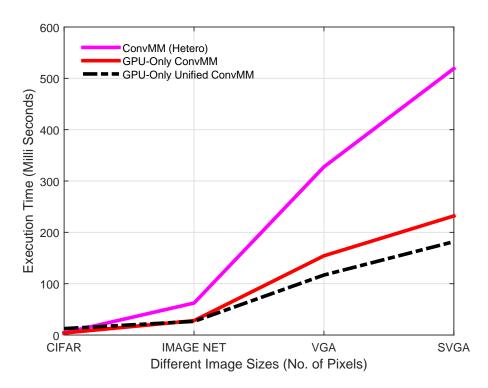

| 5.9  | Performance Comparison of GPU-only Unified ConvMM layer and other versions of Convolutional layer on Jetson TX1 Board as a function of input image size                                                                                | 63 |

| 5.10 | Performance Comparison of double-, single- and half-precision ConvMM layers on Jetson TX1 Board as a function of input image size                                                                                                      | 66 |

| 5.11 | Comparison of Hetero, GPU-only and memory optimized ConvMM layers on Nvidia Shield K1 tablet as a function of input image size                                                                                                         | 68 |

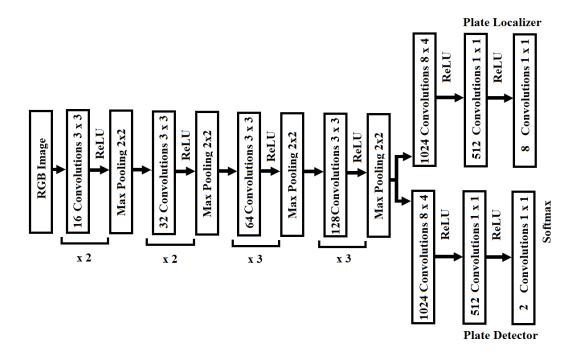

| 6.1  | Italian plate detector and localizer                                                                                                                                                                                                   | 76 |

| 6.2  | Character detector and localizer                                                                                                                                                                                                       | 77 |

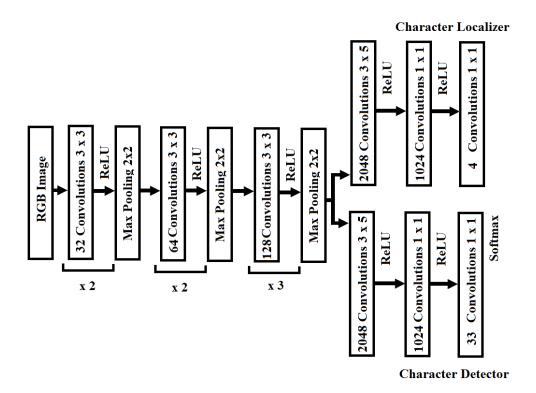

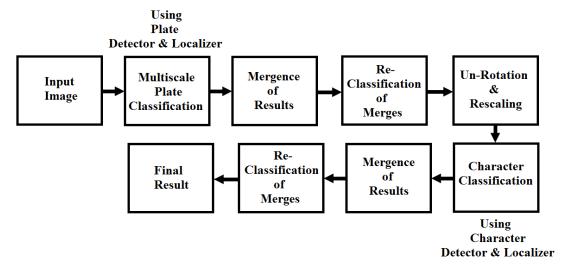

| 6.3  | Flow of neural network-based license plate recognition system developed for desktop and server environments                                                                                                                            | 78 |

| 6.4  | Simplified Flow of neural network-based license plate recognition system.                                                                                                                                                              | 79 |

| 6.5  | Images captured at night in different imaging conditions: (a) image captured with perspective distortion; (b) image captured with insufficient illumination; (c) image captured with over-exposure and reflections due to speed-light. | 80 |

| 6.6  | Rescaled input image                                                                                                                                                                                                                   | 81 |

| 6.7  | Overlapping classifications and selection of alpha-numeric characters for final result                                                                                                                                                 | 82 |

| 6.8  | Detected Characters in output image                                                                                                                                                                                                    | 83 |

# **List of Tables**

| 2.1  | Comparison of convolutional neural networks (ILSVRC challenges).                                                                           | 12 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Neural Architectures used for implementation and evaluation                                                                                | 37 |

| 4.2  | Size of parameters imported form Torch Computing framework                                                                                 | 38 |

| 4.3  | Comparison of different convolution layers under various computational loads on Jetson TX1 Board, best results are written in bold         | 39 |

| 4.4  | Execution time of rectifier linear unit under various computational loads on Jetson TX1 Board, best results are written in bold            | 41 |

| 4.5  | Execution time of both versions of pooling layers under various computational loads (Jetson TX1 Board), best results are written in bold.  | 42 |

| 4.6  | Classification time of deep models on Jetson TX1 board, best results are written in bold                                                   | 43 |

| 4.7  | Comparison of double- and single-precision ConvMM layers on Jetson TX1 board, best results are written in bold                             | 44 |

| 4.8  | Classification time of double- and single-precision deep models on Jetson TX1 Board, best results are written in bold                      | 45 |

| 4.9  | Comparison of different convolution layers under various computational loads on Nvidia Shield K1 tablet, best results are written in bold. | 46 |

| 4.10 | Execution time of rectifier linear unit under various computational loads on Nvidia Shield K1 tablet, best results are written in bold     | 47 |

xiv List of Tables

| 4.11 | putational loads (Nvidia Shield K1 tablet), best results are written in bold.                                                                                   | 48 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.12 | Classification time of deep models on Nvidia Shield K1 tablet, best results are written in bold.                                                                | 49 |

| 4.13 | Energy consumed by different deep classifier on Nvidia Shield K1 tablet (joule), best results are written in bold.                                              | 49 |

| 5.1  | Comparison of different versions of ConvMM layers under various computational loads on Jetson TX1 Board, best results are written in bold.                      | 62 |

| 5.2  | Performance comparison of different ConvMM layers based deep models (Jetson TX1 embedded board), best results are written in bold.                              | 64 |

| 5.3  | Performance comparison of ConvCAMM layers on the deep architectures (Jetson TX1 embedded board), best results are written in bold.                              | 64 |

| 5.4  | Performance Comparison of Unified ConvCAMM layer over deep classifier (Jetson TX1 Board), best results are written in bold                                      | 65 |

| 5.5  | Comparison of double-, single- and half-precision ConvMM layers on Jetson TX1 Board, best results are written in bold                                           | 65 |

| 5.6  | Classification time of double-, single- and half-precision deep models on Jetson TX1 Board, best results are written in bold                                    | 66 |

| 5.7  | Performance of ConvCAMM and Unified ConvCAMM layers on the deep models (Jetson TX1 Board), best results are written in bold.                                    | 67 |

| 5.8  | Performance Comparison of different versions of convolutional layer under various computational loads on Nvidia Shield tablet, best results are written in bold | 68 |

| 5.9  | Performance Comparison of different versions of accelerated and optimized ConvMM layers (Nvidia Shield tablet), best results are written in bold                | 69 |

| 5.10 | Classification time of optimized deep models on Nvidia Shield K1 tablet, best results are written in bold.                                                      | 69 |

List of Tables xv

| 5.11 | Performance gain achieved by proposed optimized scheme on Nvidia Shield K1 tablet, best results are written in bold | 70 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

| 5.12 | Power consumption of optimized scheme on Nvidia Shield K1 tablet (joule), best results are written in bold.         | 70 |

| 5.13 | Comparison of proposed scheme with torch computing framework on Jetson TX1 embedded board                           | 71 |

| 5.14 | Size of Model/Parameters                                                                                            | 72 |

| 6.1  | Performance analysis of original and simplified networks                                                            | 84 |

| 6.2  | Size of Parameters                                                                                                  | 85 |

| 6.3  | Classification accuracy of character detection and localization                                                     | 86 |

| 6.4  | Error correction based on position.                                                                                 | 86 |

# **Chapter 1**

## Introduction

Visual analysis is an ever-growing field with real-time applications reaching out into daily life. Convolutional neural networks (CNN) have recently enjoyed a great success in a range of visual applications. Deep convolutional neural networks exhibit unmatched recognition and classification accuracy in visual analysis applications [1–5]. This accuracy mainly comes from the deeper architecture [6, 7]. As the network grows deeper, the computational complexity of both training and testing stages of neural networks increase exponentially.

The requirements of both training and testing stages are slightly different. Training of a neural network is more intensive due to a huge number of input samples, parallel classifications and numerous iterations required for learning large datasets, it can only be performed offline on a powerful desktop workstation or using a cluster of computational accelerators. However, a trained network usually needs to classify only single images in its testing phase. This actual image classification may has to be performed online on an embedded device for the real-time visual analysis [8]. With the ongoing traction of embedded computing, deployment of deep classifiers on mobile devices is getting more and more attention. There are numerous practical real-time applications where the hand-held devices can be more useful due to their compact size and integrated resources (like Graphics Processing Unit (GPU), Camera, etc) [9, 10].

Due to the increasing demands of parallel computing in various fields, GPU has evolved from a graphics accelerator into a programmable computer. GPU is an efficient accelerator with the good price per performance ratio. There are

2 Introduction

different programming environments available (e.g. OpenCL and CUDA) to perform and assign the general purpose tasks to a GPU. The computational power of the embedded GPUs can be exploited to deploy complex general-purpose applications on the hand-held devices [11, 12].

### 1.1 Problem Statement

Many frameworks like Torch and Caffe are currently available for implementing the neural classifiers [13–16]. These frameworks exploit the computational power of modern GPUs for faster training and deployment of deep neural networks. However, most of such libraries are designed for desktop and server environments; therefore, do not consider the unique peculiarities of embedded platforms and cannot be directly used on a mobile device due to software/hardware constraints and dependences.

Some of these constraints are limited computational resources and battery life of the mobile devices. Furthermore, the embedded platforms have limited storage capacity; so the size of trained models, computing framework and required computational packages must also be considered as limiting factor for the realization of neural classifiers on the embedded devices. Due to these massive computational and storage requirements, the realization of deep architectures on the embedded platforms is still a challenging problem.

### 1.2 Contribution

The goal of the thesis is to design and develop an optimized framework that can be used to deploy the deep classifiers on the embedded platforms. The CUDA computing framework is used for the realization of identical neural architectures on embedded devices to exploit the already trained networks. The CUDA computing language is selected to design the proposed scheme because it is widely used by the deep learning community and more mature than the OpenCL language in terms of performance. The main contributions of our research activities are:

Development of a CUDA-based framework that supports nearly all layer types of deep neural architectures and suitable for deploying complex state-of-the-art deep classifiers. Intermediate frameworks and memory consuming computational packages are avoided using the proposed CUDA-only scheme to resolve the problem of software dependencies and reduce the storage requirements. The proposed framework can be easily integrated into an Android application for actual classification and provides compatibility for models trained with other desktop or server frameworks.

- Optimization of proposed framework to improve the inference performance, storage requirements and energy efficiency. Only CUDA-based functions and libraries are used to optimize the framework. An efficient memory transfer scheme is employed to optimize the flow of implemented functions. Additionally, the proposed framework is further accelerated and optimized using the hardware-dependent selection of GPU resources.

- Utilization of proposed optimized framework to realize the neural networkbased real-time classification problems on embedded GPUs. A comparative analysis of arithmetical complexity and inference performance is performed by simplifying the flow of trained deep architecture developed for computationally powerful desktop and server environments.

## 1.3 Organization of the thesis

A brief description of each chapter is presented here.

**Chapter 2** presents a short overview of the recent evolution of deep convolutional neural networks and their contributions to image classification.

**Chapter 3** gives a description of OpenCL and CUDA Programming Languages for GPU based computing. Different concepts like the arrangement of computational resources and memory model of CUDA language are explained.

Chapter 4 discusses the architecture of deep neural classifiers and our proposed scheme to realize them on embedded platforms. This is done by replicating all required functions to construct neural architecture in CUDA computing framework and exploiting the computational power of the embedded GPUs. This chapter also discusses the relevant literature concerning deep neural networks on mobile devices.

4 Introduction

**Chapter 5** describes the optimization techniques that we used to improve the performance of our proposed framework, making deep classifiers applicable to embedded applications.

**Chapter 6** presents a practical application of the proposed framework where a neural network-based automatic license plate recognition (ALPR) system is realized on a mobile platform.

This research work is finally concluded in **Chapter 7** along with a brief description of the future directions to further improve the performance of proposed framework.

### 1.4 Publications

This section provides a list of publications which are the result of our research activities carried out in the Ph.D. program.

Journals:

- Rizvi, S.T.H.; Cabodi, G.; Patti, D.; Francini, G. GPGPU Accelerated Deep Object Classification on a Heterogeneous Mobile Platform, *Electronics*, 2016, 5, 88.

- Rizvi, S.T.H.; Cabodi, G.; Francini, G. Optimized Deep Neural Networks for Real-Time Object Classification on Embedded GPUs, *Applied Sciences*, 2017, 7, 826.

- 3. Rizvi, S.T.H.; Patti, D.; Björklund, T.; Cabodi, G.; Francini, G. Deep Classifiers-Based License Plate Detection, Localization and Recognition on GPU-Powered Mobile Platform, *Future Internet*, 2017, 9, 66.

- 4. Rizvi, S.T.H.; Cabodi, G.; Patti, D.; Gulzar, M.M. A General-Purpose Graphics Processing Unit (GPGPU)-Accelerated Robotic Controller Using a Low Power Mobile Platform, *Journal of Low Power Electronics and Applications*, 2017, 7, 10.

1.4 Publications 5

### Conference proceedings:

1. Rizvi, S.T.H.; Cabodi, G.; Gusmao, P.; Francini, G. Gabor Filter based Image Representation for Object Classification, *Proc. of IEEE International Conference on Control, Decision and Information Technologies (CoDIT)*, 2016, pp. 628-632.

- 2. Rizvi, S.T.H.; Cabodi, G.; Patti D.; Gulzar, M.M. Comparison of GPGPU based robotic manipulator with other embedded controllers, *Proc. of IEEE International Conference on Development and Application Systems (DAS)*, 2016, pp. 10-15.

- 3. Rizvi, S.T.H.; Cabodi, G.; Arif, A.; Javed M.Y.; Gulzar, M.M. GPGPU based concurrent classification using trained model of handwritten digits, *Proc. of IEEE International Conference on Open Source Systems & Technologies (ICOSST)*, 2016, pp. 142-146.

- 4. Rizvi, S.T.H.; Cabodi, G.; Francini, G. GPU-only unified ConvMM layer for neural classifiers, *Proc. of IEEE International Conference on Control, Decision and Information Technologies (CoDIT)*, 2017, pp. 0539-0543.

## Chapter 2

# **Deep Learning for Image Classification**

Neural networks have the ability to perform analysis of different types of data such as text, image, audio and video [1, 17–20]. However, the field of image processing is heavily impacted by the neural networks.

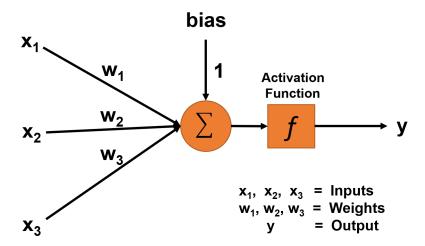

An Artificial Neural Network (ANN) is a computational model composed of interconnected units called Neurons. A neuron receives inputs from other neurons or sources and computes an output. Each Neuron has associated weights for its inputs and a threshold value (bias). The weighted sum of inputs, bias and activation function of neuron define the final output as shown in Figure 2.1.

Fig. 2.1 A single neuron of ANN.

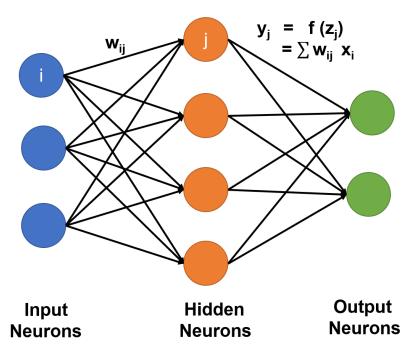

These neurons are arranged in layers and form a directed graph known as feedforward neural network. Neurons of these adjacent layers are normally fully interconnected and have weights associated with them as shown in Figure 2.2. A feedforward neural network is composed of input, hidden and output layers. Input and output layers of these feedforward neural networks are used to get the input data and provide the final output. There can be multiple hidden layers in a neural network to perform computations and transfer information from the input layer to the output layer.

Fig. 2.2 Feedforward neural network.

Deep models are composed of multiple hidden processing layers stacked together to extract the meaningful information from the input data [21]. These networks contain millions of trainable parameters (weights and biases). Deep classifiers learn from the input data using an iterative learning procedure by reducing the difference between the actual and the target values with help of an objective function. During training, the trainable parameters (weights and biases) of classifiers are adjusted repetitively to reduce the error or difference.

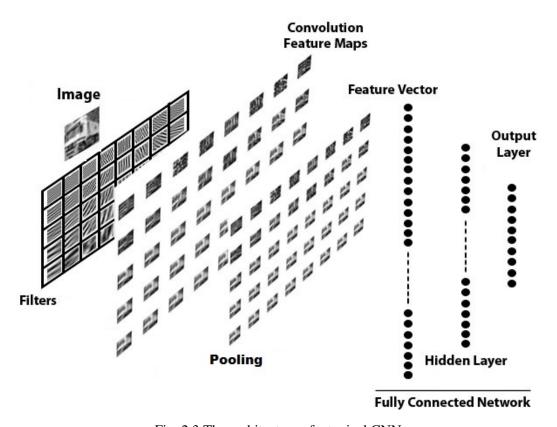

Convolutional neural networks (CNN) exhibit unmatched performance in classification tasks. Convolutional neural networks are also feedforward ANNs, but with a special structure having shared weights that help to capture the local properties of the input data or signal. A typical convolutional neural network (CNN) is composed

of two stages as shown in Figure 2.3. The first stage of CNN is for feature extraction while other is trained for feature classification. The first stage is mainly composed of convolutional and pooling layers. Convolution operation extracts the features by convolving a trainable filter (weights) with the input image. Convolutional layers preserve the spatial resolution of input data (image) and provide feature maps while pooling layers are responsible for reducing the resolution of feature maps for the manageable representation. Fully connected layers in the second stage classify the features and provide the final output. There are also some others layers for regularization and normalization in both of these stages that improve the performance of a neural network. The deep architectures and their basic components are further discussed in detail in **Chapter 4**.

Fig. 2.3 The architecture of a typical CNN.

### 2.1 Deep Architectures

The neural networks have largely remained neglected till last few years. From 2012, a yearly competition ILSVRC (ImageNet Large-Scale Visual Recognition Challenge) diverted the attention of researchers to neural classifiers through some ground-breaking results and competitive solutions. However, these recent deep architectures demand massive storage capacity and computational power for training and realization. With the evolution of processing units, the computationally and memory intensive neural classifiers can be easily trained and deployed using the powerful desktop workstations and GPU servers often in multi-GPU configuration. This section presents a short overview of the recent evolution of deep classifiers and their contributions to the image classification.

### 2.1.1 AlexNet

It all started with a very deep convolutional network that was proposed and won the ILSVRC competition in 2012 [1]. This deep classifier was comprised of five convolutional layers and three fully connected layers as shown in Figure 2.4. The network was trained using a dataset of about a million images to classify 1000 different categories.

Fig. 2.4 AlexNet.

Results proved the effectiveness of deep classifiers over other state-of-the-art techniques. This success was made possible by the efficient use of GPU, Rectifier Linear unit and a regularization technique 'dropout' [22]. This was the first time

when such a deep network is trained efficiently using the GPU and performed very well on a large and difficult dataset like ImageNet.

#### 2.1.2 OverFeat

In 2013, a multi-scale, sliding window based deep learning approach was proposed for object classification, localization and detection with a single network [23]. This network obtained some astonishing results that proved the effectiveness of CNN for localization and detection tasks. These points were not addressed in previous works.

#### **2.1.3 VGG** Net

This research work proposed and evaluated the importance of depth in visual representation [2]. In this work, very small (3x3) convolutional filters were used to steadily increase the depth of a network. Instead of using large receptive fields like previous networks, small filters were used to achieve very deep convolutional networks (having up to 19 layers). Figure 2.5 shows the architecture of a VGG-16 network having 16 convolutional layers. These networks were trained over ImageNet dataset and showed state-of-the-art performance in ILSVRC 2014 challenges. Achieved results reinforced the notion that the classification accuracy of a neural network can be improved significantly by increasing the depth of network.

Fig. 2.5 Architecture of VGG-16.

### 2.1.4 GoogLeNet

Google proposed a computationally efficient deep architecture named GoogLeNet having 22 convolutional layers [6]. A new module known as inception was introduced and used to increase the width and depth of this architecture by keeping the computational complexity constant. The structure of inception module can be visualized using Figure 2.6. Instead of stacking convolutional and pooling layers on each other in sequential manners, inception module concatenated layers in serial and parallel structure to improve the performance and computational efficiency. Using inception module, the GoogLeNet achieved state-of-the-art results for classification and detection in ILSVRC 2014.

Fig. 2.6 The inception module.

### **2.1.5** ResNet

A new deep architecture named Residual network (ResNet) was proposed by Microsoft Research Asia in late 2015 [7]. This network used the concept of shortcut connections to learn the difference of representation using residual block shown in Figure 2.7. The purpose of these shortcut connections in the residual network is to force the layers to refine the features [24].

Residual network set the new record in terms of number of layers in a deep architecture and also significantly reduced the number of trainable parameters compared to other networks like VGG Net. The 152-layer ResNet model won ILSVRC classifi-

cation competition in 2015. These residual networks are the current state-of-the-art on ImageNet dataset.

Fig. 2.7 Residual block.

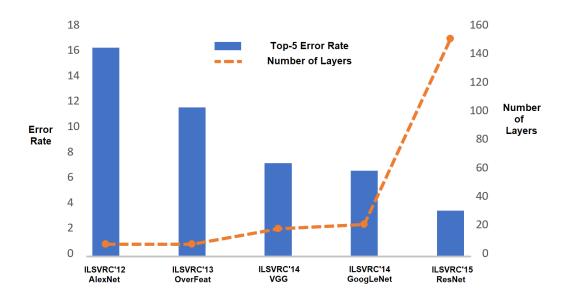

Table 2.1 and Figure 2.8 present a comparative analysis of depth, number of parameters and error rate of previously discussed neural architectures. Since 2012, the error rates of image classifiers have reduced significantly and at the same time, the number of convolutional layers has also increased with the reduction in trainable parameters. State-of-the-art deep neural architectures (Like GoogLeNet and ResNet) have human-level classification accuracy and, are less computationally and memory demanding due to the reduced number of parameters. These deep architectures can be realized on an embedded platform for the real-time image classification with the help of an optimized framework.

| Table 2.1 Comparison of | t convolutional neura | l networks (ILSVRC | challenges). |

|-------------------------|-----------------------|--------------------|--------------|

|-------------------------|-----------------------|--------------------|--------------|

| Model     | No. of Layers | <b>Top-5 Error Rate</b> | <b>Number of Parameters</b> |

|-----------|---------------|-------------------------|-----------------------------|

| AlexNet   | 8             | 16.4 %                  | 60 million                  |

| OverFeat  | 8             | 11.7 %                  | 145 million                 |

| VGG       | 19            | 7.3 %                   | 144 million                 |

| GoogLeNet | 22            | 6.7 %                   | 6.8 million                 |

| ResNet    | 152           | 3.57 %                  | 1.7 million                 |

Fig. 2.8 Evolution of deep convolutional neural networks.

# **Chapter 3**

## **Overview of GPGPU Programming**

With the rapidly evolving computing technology, the General-Purpose Graphics Processing Unit (GPGPU) has emerged as a competitive accelerator for computationally demanding applications like training of neural networks. The architecture of a GPGPU is highly parallel and can provide massive computational power than the CPUs. A GPGPU can be programmed using a high-level programming language to exploit its multi-core multi-thread structure for accelerating the general-purpose applications.

## 3.1 Programming Languages for GPU Computing

A GPGPU can be programmed using two different programming interfaces, Compute Unified Device Architecture (CUDA) and Open Computing Language (OpenCL) [25, 26]. OpenCL is an open standard that can be used to program various devices (GPUs, CPUs etc.) from different vendors, while CUDA is proprietary language that can only be used to program Nvidia GPUs.

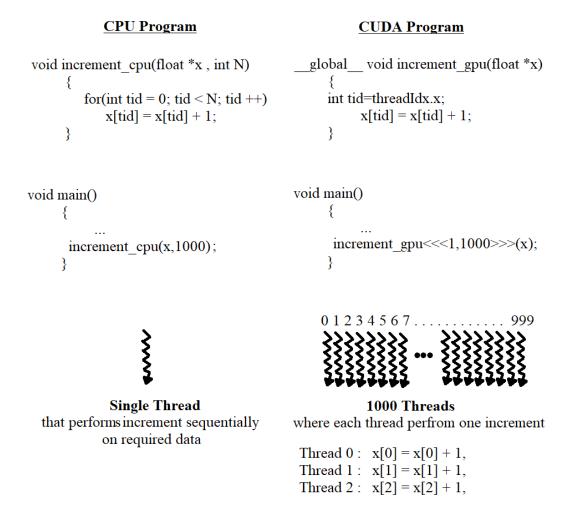

A GPU program is composed of the device (kernel) and the host codes. A kernel code is only executable on the device (GPU) and can only be called by host side, while the host code is executed by the CPU and manages the resources like initialization of device, allocation of memory, transfer of data and launch of kernel etc.

Both OpenCL and CUDA launch the kernel from host side (CPU) and execute it on the device (GPU). Porting the kernel code from one language to the other requires minimal modifications. However, the host code for both languages is substantially different and needs to be completely rewritten according to the syntax and libraries of the required programming environment. Both languages provide some similar host functions to set up the GPGPU for execution of the kernel code. Context initialization, data allocation and data transfer are few examples of these host functions.

Although OpenCL is a portable language and supports a variety of devices, but it is less efficient than the CUDA-based libraries and functions in terms of execution time due to its generality [27, 28]. OpenCL functions need to be optimized carefully for a specific hardware. Furthermore, OpenCL is not directly supported on Android Operating system from version 4.3 onwards. An intermediate library is required to access the mobile GPU and its resources. Such a library not only adds extra computational overhead, but also increases the storage requirements and complexity of source application. Therefore, it is not feasible to use the standalone OpenCL for the realization of deep classifiers on mobile devices. In addition, CUDA libraries are widely used by the deep learning community. In this work, CUDA computing language is used to realize the deep classifiers on embedded platforms. The next sections of this chapter briefly discuss the thread and memory hierarchy.

## 3.2 Arrangement of Computing Resources

As a device code is invoked, the GPU launches a number of threads to concurrently execute the instructions of the kernel function; while the same program written for CPU executes the instructions sequentially using a single thread. As shown in Figure 3.1, the required operation of increment is performed concurrently on a GPU using a block of threads. The concurrent execution of threads can significantly improve the performance of the data independent applications.

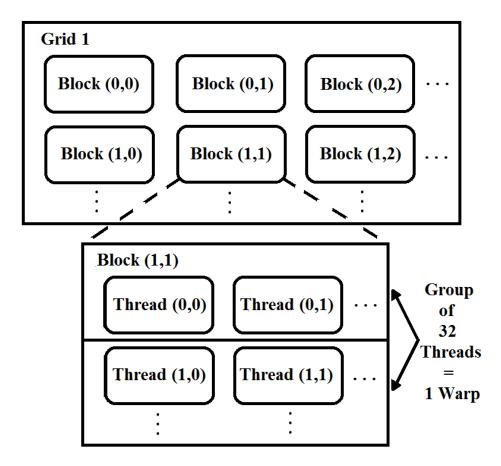

GPGPU is a multi-core, multi-thread system where these threads are organized into a multi-dimensional grid of independent blocks. Each block is comprised of concurrent threads that operate cooperatively within each block as shown in Figure 3.2. The Single instruction multiple threads (SIMT) programming model of GPU is an extension of single instruction multiple data (SIMD) approach. In SIMD programming model, the same operation is applied to all data items, while SIMT

execution model provides flexibility by combining the SIMD model with multithreading where a group of threads (called warp) perform the same operation. A group of 32 threads forms a warp.

Fig. 3.1 Structure of a CUDA program.

Depending on the architecture of GPGPU, there is a limit on the number of threads per block. There can be maximum 1024 threads in a block, so multiple blocks may be required to execute a single kernel. Total number of threads invoked during execution can be calculated using following formula:

$Total\ number\ of\ Threads = Threads/block \times Number\ of\ blocks \qquad (3.1)$

The number of blocks in a grid is defined with accordance to the size of data to be processed. These blocks execute independently across the different cores of a GPU.

Fig. 3.2 Arrangement of GPU resources.

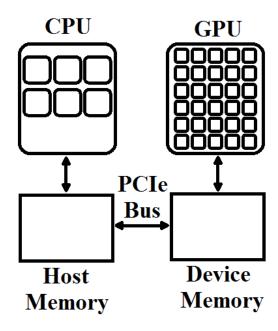

## 3.3 CUDA Memory Model and Hierarchy

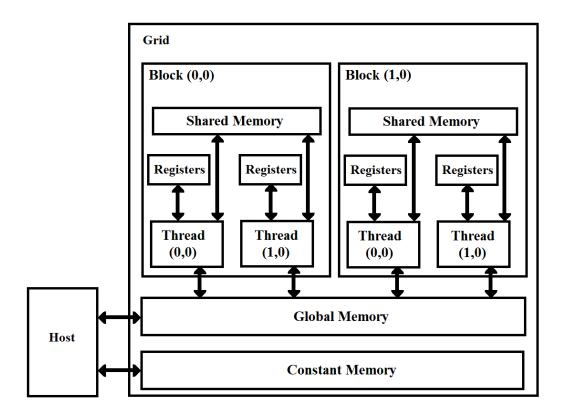

For GPU-based computations, the input data to be processed must be copied from the host (CPU) memory to the device (GPU) memory and the output data (final results) must be retrieved from the GPU memory to the CPU memory. CUDA devices have different types of memory spaces which offer various performance characteristics. Data from these different memory spaces may be accessed by threads during execution. Hierarchy of CUDA memory model can be visualized using Figure 3.3.

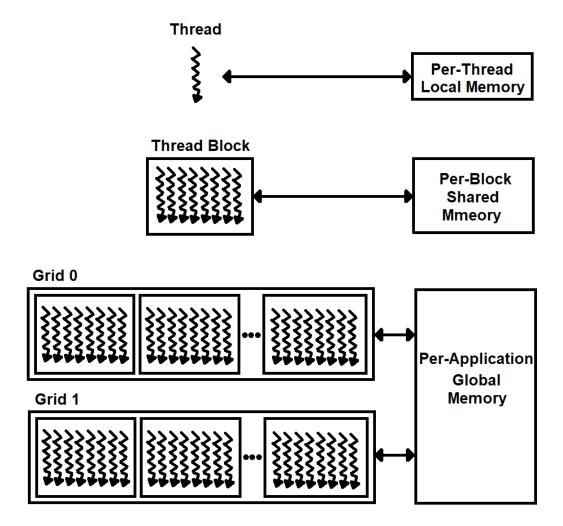

Every thread has registers or private local memory that is only available to one thread. Each block has its own shared memory that is available and visible to all threads within the same block. Data present in global memory can be accessed by all threads of an application. Figure 3.4 presents a visual representation of threads, blocks and grids with corresponding per-thread private, per-block shared and per-application global memory spaces.

Constant and texture memory spaces are two additional read-only memory portions in CUDA processors that are generally used to store the constants, kernel arguments and to support optimized 2D access pattern.

Fig. 3.3 CUDA memory types.

The global memory is the main and largest memory space in the graphics processing unit. The computational data is usually stored and transferred between the host (CPU) and the device (GPU) through global memory. The latency to access global memory is generally higher. However, its performance can be improved by coalescing the memory accesses. Shared memory is on-chip and faster than global

memory, but it is limited and its performance is subject to bank conflicts among threads.

Fig. 3.4 CUDA hierarchy of threads, blocks and grids with corresponding memory spaces.

Proper utilization of computing and memory resources can significantly improve the performance of CUDA-based general purpose applications. The next chapter presents the adopted methodology to realize the deep classifiers on embedded platforms using CUDA computing framework.

# **Chapter 4**

# Neural Architecture and CUDA-based Proposed Realization

This chapter describes the most common layers required by the neural networks to perform image classification and our proposed approach to realize the deep classifiers on the embedded platforms<sup>1</sup>. In this work, the CUDA computing language is used to replicate the neural architectures and exploit the computational power of the embedded GPUs. Namely, our proposed framework relies on a GPU-only scheme for performing convolutions in the transform domain. The performance of this GPU-only scheme is compared with the heterogeneous and sequential versions. Different neural architectures are considered to evaluate the performance of the proposed CUDA-based scheme.

### 4.1 Introduction

Image classification via convolutional neural networks (CNN) involves two stages. The first stage is an offline learning state to train the required neural architecture over a set of labeled input data (images) and the second stage is testing or inference phase where a proper image classification can be performed using the trained network. During training stage, the network parameters are iteratively updated to predict the

<sup>&</sup>lt;sup>1</sup>Part of the work described in this chapter has been previously published in **Electronics** Journal as "Rizvi, S.T.H., Cabodi, G., Patti, D. and Francini, G. "GPGPU Accelerated Deep Object Classification on a Heterogeneous Mobile Platform," Electronics 2016, 5, 88.

4.2 Related Work 21

output values corresponding to the input labels. A trained network can classify the new images using the learned set of parameters (weights and biases).

Deep convolutional neural networks demand high computational power and memory storage. These are the constraints that limit the possibility to realize the deep classifiers on the embedded devices. Due to the huge demand of resources, the training stage can only be performed offline on a dedicated GPU or server infrastructure. However, the actual image classification may has to be performed online on an embedded device for the real-time visual analysis [8]. There are numerous practical real-time applications where the hand-held devices can be more useful due to portability and on-board resources [29, 30].

Recent embedded devices employ the heterogeneous architectures and are well suited for challenging real-time applications [31–34]. As mentioned earlier, training and testing phases are computationally intensive problems, so heterogeneous (GPU-CPU) resources of an embedded platform can be exploited to accelerate the sequential and concurrent processes in such problems. GPUs can be exploited to accelerate the concurrent processes, whereas the CPUs can execute the sequential tasks efficiently due to their higher operational frequencies. Training and classification time of neural classifiers can be largely improved by proper scheduling of computational resources of the heterogeneous architectures [32, 33, 35–37].

### 4.2 Related Work

As mentioned earlier, many computing frameworks like Torch and Caffe are currently available for implementing the neural networks. These frameworks rely on a number of third-party libraries to leverage the computational resources of modern GPUs for faster training and deployment of deep neural classifiers. However, such libraries are designed for computationally powerful environments like desktop workstations and server platforms. Therefore, these libraries do not consider the unique peculiarities of embedded platforms and cannot be directly used on a mobile device. Realization of neural architectures on a low power embedded platform is still a challenging problem, and there have been very few studies conducted on this.

An OpenCL-based deep CNN framework is proposed for mobile devices in [38]. This scalable framework leverages a variety of optimization techniques like memory

vectorization and half floating-point processing to execute several CNN models in real-time, with no or marginal accuracy tradeoffs. However, this scheme relies on OpenCL language, which is less efficient than the CUDA-based same libraries and built-in functions in terms of execution time; therefore, demand much optimization [28]. Furthermore, OpenCL is not directly supported on Android Operating system from version 4.3 onwards.

An efficient mobile GPU-accelerated Deep Neural Network flow is presented in [39]. Different optimization techniques to increase the computing efficiency are discussed. This DNN flow shows significant speedup and higher energy efficiency over the CPU-based sequential version. However, the information that is presented is not enough to reproduce the results.

An open source GPU-based library "CNNdroid" is introduced in [40]. This library is designed to realize the trained neural classifiers on Android-based mobile devices. However, this library does not provide support for all CNN layers required to realize the state-of-the-art neural classifiers like ENet and Residual Network.

An efficient embedded framework named "Quantized CNN" is proposed in [41]. This framework simultaneously improves the computation time and reduces the storage/memory overhead and power consumption. This gain in performance is achieved by compressing the convolutional neural networks for realization on mobile devices. However, results also show that the quantization and compression of parameters jeopardize the precision of results [42–44]. Furthermore, state-of-the-art deep classifiers can be directly used on a mobile platform without any need of quantization, because these classifiers already have fewer parameters and provide state-of-the-art classification accuracy [45].

Above mentioned schemes focus on the efficient realization of testing/inference phase on the embedded platforms, however, a lot of research work is also going on the training of memory efficient neural architectures [46–48]. These works propose that more computationally and memory efficient deep neural architectures can be constructed by approximating, quantizing or compressing some of the parameters during the training phase.

Concluding, the contributions of our proposed framework and improvements over the above-mentioned schemes can be summarized as follows. First of all, the proposed scheme has the merit of supporting nearly all layer types of deep neural architectures and suitable for deploying complex state-of-the-art deep classifiers. All

required layers and functions are realized using CUDA computing framework. Intermediate frameworks and memory consuming computational packages are avoided using the proposed CUDA-only scheme to resolve the problem of software dependencies and reduce the storage requirements. In addition, the accuracy of our proposed scheme is similar to the existing desktop and server frameworks. Furthermore, the proposed framework can be easily integrated into an Android application for actual classification and provides compatibility for models trained with other desktop or server frameworks.

#### 4.3 Adopted Methodology

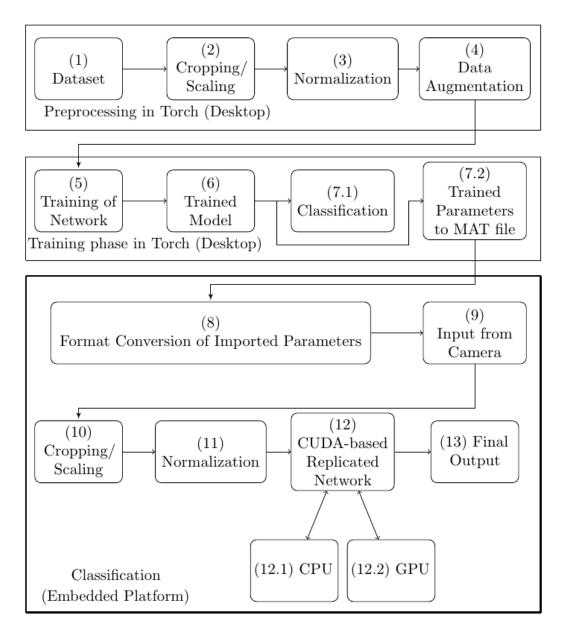

Figure 4.1 presents the proposed flow to realize a deep classifier on an embedded platform. First of all, Torch computing framework is used to train the state-of-the-art deep neural classifiers. These neural classifiers are trained using the powerful desktop workstation or GPU server depending on the required computational power. Some preprocessing techniques are performed to enhance the computational efficiency of training process and accuracy of results [49]. Neural networks are normally trained on a fixed size of training data, while the training data can be of various sizes and dimensions because of its collection from different sources. Therefore, the training images are required to be scaled or cropped to fit the defined architecture. Scaling and cropping can be performed using different approaches.

Normalization of input and target data is also an important preprocessing step for proper training of a neural network. Data normalization is generally useful to map the widely-spaced scale data to a uniform scale. It is performed here by normalizing the data to have zero mean and unity variance, also called mean-standard deviation normalization.

Since the deep networks need a large amount of training data to improve the performance and classification accuracy, data augmentation is used to artificially increase the amount of training data. This image augmentation is performed through different augmenting techniques like color jittering, random crops, horizontally flipping, etc. Finally, the neural architectures are trained and can be used for classification purposes in the field.

Fig. 4.1 Block diagram of the CUDA-based neural classifier for embedded platform.

Once a network is trained, its trained parameters can be imported for the actual classification. In this work, the CUDA programming framework is used to replicate the trained neural architectures on the embedded platforms. All required layers and activation functions are implemented in CUDA to realize the identical architectures. The computational power of GPGPU is exploited to accelerate these CUDA-based identical functions (Convolution, pooling, batch normalization, rectifier linear unit, etc.). Convolution is the most computationally intensive layer of neural classifiers.

Two versions of convolution operation are implemented to perform a comparative analysis and support the different neural architectures trained in torch framework. The trained parameters from Torch framework are formatted in different ways depending on the used convolution method. So it is important to perform the format conversion of imported parameters to achieve the same results on the embedded platforms. By importing the trained parameters and realizing the identical architecture, these CUDA-based deep classifiers are executed on the embedded platform. Furthermore, these classifiers are realized on a portable embedded device as a part of the Android application.

The onboard/integrated camera of the embedded platforms is used to acquire the input image as shown in Figure 4.1. Real-time image classification is performed on this captured image using the trained networks. Same preprocessing steps are required to be performed on the captured image as done at the time of training. As the trained classifiers are designed for a specific input dimension and the captured image can be of different aspect ratio depending on the camera of the embedded platform, so it is essential to crop or scale the image to the exact size required by a neural network. Similarly, it is necessary to normalize the input image to minimize the bias towards different features and map the input/output values to a specific range. After these steps, the captured image is fed and classified by the CUDA-based replicated networks on the embedded platform using imported trained parameters. Final classification results can be displayed on the screen of a portable embedded device or can be used by another application for the further developments.

#### 4.4 Architecture of the Convolutional Neural Networks

This section presents the architecture of deep classifiers and the entailed layers.

#### 4.4.1 Convolutional Layer

The convolutional layer is core building block of deep classifiers. It extracts the robust pattern or features from the input images. Mathematically, convolution can be expressed as the summation of point-wise multiplication of filter/mask coefficients with the input image/function. A filter is an integral component of the layered architecture. Convolution operation extracts the features by convolving a filter

with the input image. These features or output of convolution operation are called activation maps. Filters are trainable parameters that are adjusted during the training to predict the meaningful aspects of the input data.

State-of-the-art deep classifiers are composed of multiple convolutional layers [6, 7, 23]. By stacking a number of convolutional layers, accuracy of a neural classifier can be significantly improved [1, 6]. However, convolution is a computationally intensive operation and demands high computational power and memory storage. Therefore, these factors limit the realization of convolutional neural networks on the embedded platforms. By an effective and efficient realization of the convolution operation, the computational burden of these layers can be reduced and an embedded GPU can be exploited to accelerate the neural classifiers.

There are different methods to compute the convolution operation. In this work, two approaches to compute the multi-channel convolution operation are discussed, realized and compared for the adaptation of torch-based trained networks on the embedded platforms.

The first and traditional approach is full convolution. In this approach, convolution is computed by the sum of products of the filter and the input image. This operation is extended to perform the multi-dimensional convolutions as required by the neural classifiers.

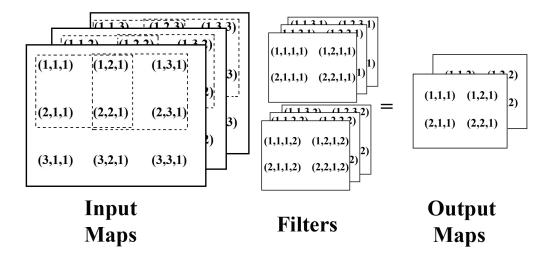

Both input and output images are three dimensional. If the input and output images have C and D channels respectively and sizes of the trained filter bank and the input image are X x Y and I x J respectively, then the output of a multi-channel fully-convolutional layer can be expressed by the following equation:

$$Output\_map_{i,j,d} = \sum_{c=1}^{C} \sum_{i1=1}^{X} \sum_{j1=1}^{Y} Input\_map_{c,i+i1,j+j1} Filters_{d,c,i1,j1}$$

(4.1)

Figure 4.2 illustrates the example of a fully convolutional layer where the pixels of input maps, output maps and filters are defined by their index positions. As both input and output maps have three dimensions, so their pixels are represented by (row, column and channel number) while the pixels of filter banks are represented as (row, column, input channel number and output channel number) because the filter bank is 4 dimensional. The index value (3,2,1) of input map represents the pixel present

on the first channel of the input image at the third row and second column. In this particular example, the input image is of size 3 x 3 and has 3 channels. There are 2 filter banks each having 3 channels. Size of each filter is 2 x 2. The number of channels in a filter bank depends on the channels of input maps while the number of filter banks defines the number of channels of output map. So for this particular example, output map would have 2 channels and size of output map would be defined by the size of the filter and few other parameters defined in Section 4.4.6. In this approach, filters and input maps have to convolve in a sliding manner that can be a slow process which cannot fully exploit the concurrent resources of a GPU [50].

Fig. 4.2 Multi-dimensional full convolution.

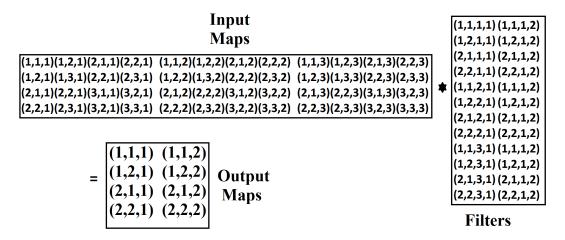

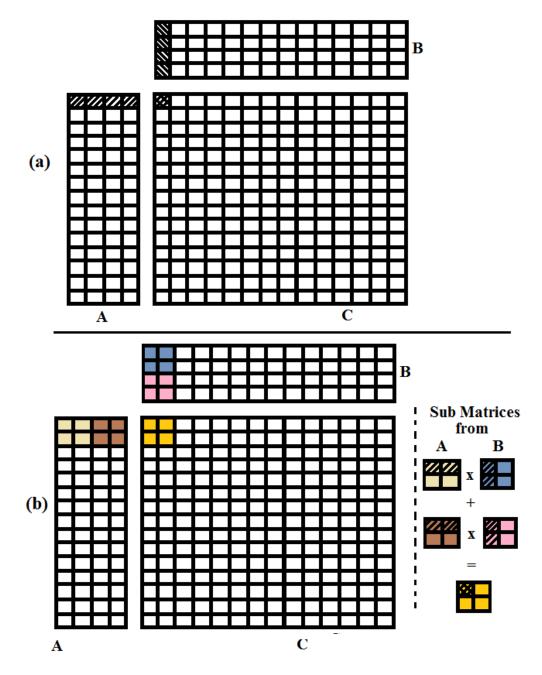

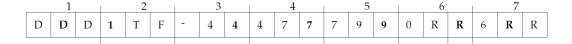

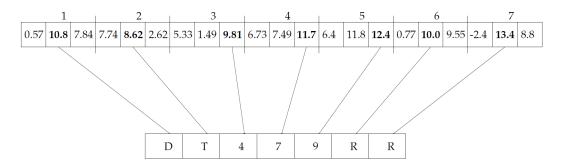

The second approach realized for the computation of convolution is based on Matrix Multiplication. In this Matrix Multiplication based Convolution (ConvMM) approach, first, the input maps and filter banks are transformed into two-dimensional matrices and then directly multiplied [51, 52]. Figure 4.3 illustrates the matrix multiplication based version of the convolutional layer where the input image and filters are arranged as the matrices in the transform domain.

Fig. 4.3 Matrix multiplication based convolution (ConvMM).

Figure 4.3 also explains the mapping of pixel values from the multi-dimensional input maps and filter bank to the two-dimensional matrices. Figure 4.3 represents the pixels shown in Figure 4.2 in two-dimensional transformed form. Resultant matrix (output map) can be calculated by multiplying these transformed input and filter matrices. Values of the resultant matrix can be arranged to achieve the output representation equivalent of the traditional convolutional layer.

Convolution can also be computed using other approaches like Winograd minimal filtering algorithm, fast Fourier transformation and lookup table-based approaches [42, 51–55]. Using fast Fourier transformation (FFT)-based approach, convolution can be computed as point-wise products in the Fourier domain [53]. This FFT-based convolution requires large memory space to store the transformed data that can be a problem for existing GPUs having a limited amount of on-chip memory. Furthermore, FFT-based approach is fast for large filters, while state-of-the-art deep classifiers use small filters [7]. For networks having small filters, minimal filtering algorithm pioneered by Winograd can be employed to compute the convolution over small tiles [42]. This algorithm is memory friendly and fast for small filter and batch sizes. The Winograd technique minimizes the complexity by performing element-wise multiplication instead of matrix multiplication and reduces the number of arithmetic operations. Some optimization techniques can also be used to improve the performance of these convolution approaches [56–58].

#### 4.4.2 Pooling Layer

In a traditional convolutional network, every convolutional layer is followed by a pooling layer. Convolutional layers preserve the spatial resolution of input data (image) while pooling layers are responsible for reducing the resolution of feature maps for the manageable representation. This down-sampling doesn't affect the depth (Channels) of feature maps. The most common pooling approaches are max- and average-pooling. These layers do not have any trainable parameter like convolution. There are also other pooling techniques and regularization methods that can be used to improve the training speed and classification accuracy of the convolutional neural networks [50, 59].

#### 4.4.3 Batch Normalization

Batch normalization is also an important part of state-of-the-art deep classifiers. It dramatically speedup the training of neural classifiers [60]. By adding some extra trainable parameters, batch normalization preserves the representation ability of the network. Furthermore, the resulting networks do not require any further regularization. This function can be expressed as follows:

$$BN(x) = \frac{x - mean}{\sqrt{Var}} * gamma + beta$$

(4.2)

In batch normalization layer, values of mean and variance are estimated from the training data; while beta and gamma are the trainable parameters. This layer first normalizes each scalar feature by making it have the zero mean and unit variance, and then gamma and beta are used to scale and shift the normalized output.

#### 4.4.4 Activation Functions (ReLu, Tanh and Threshold)

There are several activation functions for neural networks, like the rectifier linear unit, threshold unit and tangent hyperbolic unit. Activation function is one of the important components of a neural network. It is a non-linear decision-making function that determines the presence of a particular feature. It improves the training of a neural network and further eliminates the problems like vanishing gradient [61].

#### 4.4.5 Linear or Fully Connected Layers

As the name implies, this layer is fully connected to the output of the previous layer. These layers are typically used in the last stages of a classifier. Where convolutional layers extract the robust features, these fully connected layers (multilayer perceptron) perform the feature classification and provide the final output. These layers also have trainable parameters (weights and biases) like convolutional layers. Furthermore, most of the parameters of a network are in the fully connected layers.

#### 4.4.6 Sizing Convolutional Neural Networks

The size of the output map of a convolutional or pooling layer is dependent on the size of the filter, the striding size and the number of padding bits used in the input image.

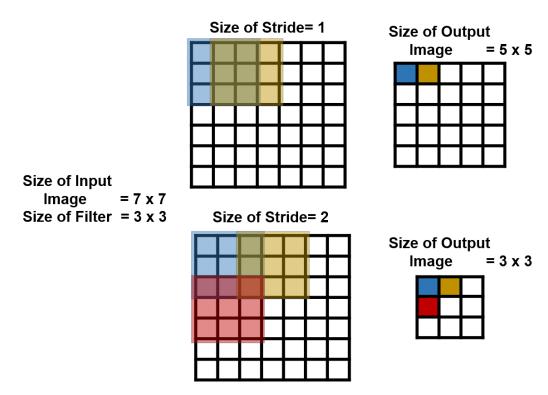

The stride size controls the movement of the filter around the input map in the convolution/pooling operation. It defines the amount by which the filter shifts and directly affects the size of the output map as shown in Figure 4.4.

Fig. 4.4 Effect of stride length on the size of output maps.

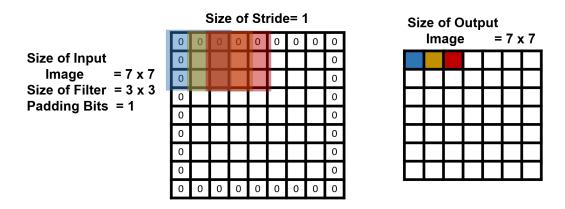

It can be visualized from the previous figure that the size of output map would always decrease after the convolution and pooling operations. In some cases, it is required to preserve and attain the size of maps. Zero padding is used to resolve this problem and achieve the desired size of output maps. As shown in Figure 4.5, the size of output map is same as the input map after required operation due to additionally padded zeros around the border of input maps.

Fig. 4.5 Effect of padding and stride length on the size of output maps.

#### 4.5 CUDA-based Proposed Framework

This section discusses the CUDA-based realization of the deep architecture for image classification on embedded devices.

#### 4.5.1 GPGPU-accelerated Fully Convolutional Layer

The CUDA computing language is used to implement the traditional fully convolutional layer. The computational power of GPGPU is exploited to accelerate this layer. A 3-dimensional grid of blocks and threads is used to offload the complete workload into the GPU and concurrently compute the convolution operation. To realize the Torch-based identical classifier, formatting of the acquired input image and trained parameters is one of the most important tasks. As mentioned earlier, trained parameters of the fully-convolutional layer and matrix multiplication based convolution have structurally different format. So format conversion of imported parameters is essential to acquire the same results as provided by the Torch-based

model. The row-major layout is used to store and access the multi-dimensional trained parameters, input image and results. This contiguous memory allocation speedup the access of array elements. Padding function is also implemented and accelerated using GPGPU. This CUDA-based padding function is realized to provide the identical functionality and architecture as provided by the convolutional layers of Torch framework.

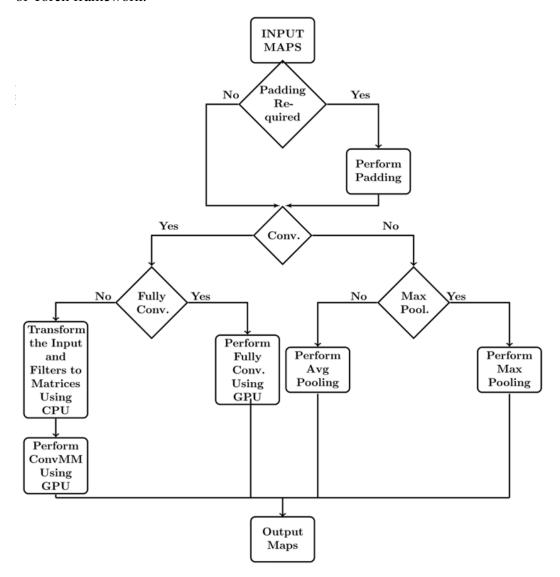

Fig. 4.6 Flow of GPGPU-based convolutional and pooling layers.

The realized convolutional and pooling layers have same flow because both are composed of two kernels. The first kernel performs the concurrent padding of input data and the second kernel executes the selected operation of pooling or convolution

on this padded input. All others layers like the batch normalization and threshold unit, where the padding function is not required are computed using a single kernel. The flow of both convolutional and pooling layers is depicted in Figure 4.6. First of all, upon execution, padding is performed on the input data. And if it is not required to perform padding, then directly the second kernel is called for execution. This second kernel can be either convolution or padding function depending on the defined flag. There are two further options in both convolution and pooling kernels. In case of convolution kernel, it is checked that either full convolution or matrix multiplication based convolution is required to be performed. Similarly, in case of pooling function, average or max function is invoked depending upon the defined flag.

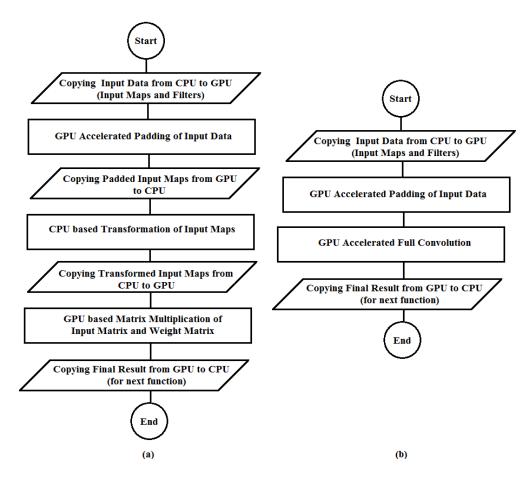

#### 4.5.2 Heterogeneously Accelerated ConvMM Layer

Matrix multiplication based convolutional layer is also realized using CUDA language. Heterogeneous resources of the embedded platform are fully utilized to compute the solution of the ConvMM layer. This layer is accelerated by offloading the appropriate computations between the CPU and the GPGPU of the embedded platform. The sequential tasks like the transformation of input maps and filters into two-dimensional matrices are assigned to the powerful CPU, and the concurrent matrix multiplication of this transformed data is performed using the GPU. In this transformation step, pixel values from the multi-dimensional input maps and filters are required to be placed on the distinct locations of matrices in a specific sequence. As CPUs are best suited for sequential computations, this sequence sensitive transformation can be performed efficiently using the CPU. An algorithm like this can benefits from the heterogeneous accelerators in terms of execution time [33, 62, 63].

Figure 4.7 illustrates the scheduling of workload between the GPU and the CPU for the full convolutional approach and heterogeneous ConvMM layer. As shown in Figure 4.7, fully convolution layer is executed homogeneously on the GPGPU, therefore, data is transferred two times between the device and the host memory, to copy the input data to the GPU and to provide the final result. GPU-accelerated padding followed by full convolution is performed on the input data to compute the desired solution. While in case of heterogeneous ConvMM layer data is transferred four times between the GPU and the CPU memories, first copied to the device memory to perform the concurrent padding, then transferred back to the CPU side to

perform the sequential transformation, then again to the device memory to perform the GPU-based matrix multiplication and finally to the CPU memory.

Fig. 4.7 (a) Flow of heterogeneous ConvMM layer; (b) Flow of full convolutional layer.

#### 4.5.3 GPU-only ConvMM Layer

Instead of just comparing the execution time of the same kernel on the CPU and the GPU, cost of moving data should also be considered. Extra memory transfers across the PCI-express bus can break the performance of an application. The Number of data transfers should be minimized, even if the GPU version get little or no speedup compared to the CPU version.

Figure 4.7 (a) also depicts that the data is transferred four times between the GPU and the CPU memories to realize the heterogeneous ConvMM layer. Out of four, two transfers are done to perform the CPU-based transformation. These

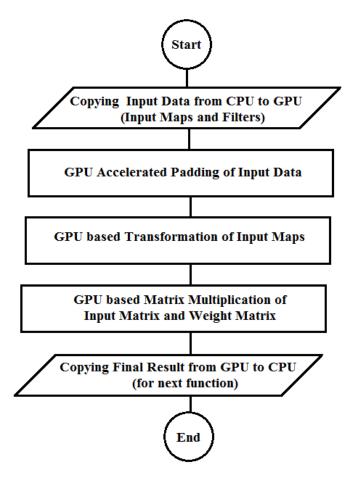

transfers can break the overall performance of the system in case of slower memory bandwidth. If this CPU-based transformation step of heterogeneous ConvMM layer is parallelized and performed using the GPU, so these extra memory transfers can be avoided [64]. Figure 4.8 shows the proposed flow of GPU-only ConvMM layer where both transformation and multiplication steps can be performed using the GPU.

Fig. 4.8 Flow of GPU-only ConvMM layer.

Following formula can be used to transform the multi-dimensional input map into two-dimensional input matrix concurrently.

$$Input\_matrix_{(row,col)} = \sum_{i=1}^{o\_Row} \sum_{j=1}^{o\_Col} \left( \sum_{k=1}^{i\_Dim} \sum_{h=1}^{k\_h} \sum_{w=1}^{k\_w} Input\_map_{(i+h,j+w,k)} \right)$$

(4.3)

```

where o\_Row = i\_Row - k\_h + 1; o\_Col = i\_Col - k\_w + 1; row = i \times (o\_Col) + j; col = (k \times k\_w \times k\_h + (h \times k\_w) + w);

```

In this formula, width and height of the filter are represented by k\_w and k\_h. i\_Row, i\_Col and i\_Dim are representing the number of rows, columns and dimensions (channel) of the input image. Rows and columns of the output matrix are represented by the o\_Row and o\_Col.

#### 4.5.4 GPU-Accelerated Max and Average Pooling Layers

Both max and average pooling layers are implemented to realize the different neural architectures on the embedded platform. The CUDA programming language is used to concurrently compute the solution of these sub-sampling approaches. The computational power of GPU is exploited to surpass the sequential version of pooling layers in terms of execution time. The CUDA-based padding function is also implemented and employed in these pooling layers to support the same options and architectures as provided by the Torch framework.

#### 4.5.5 GPU-Accelerated Batch Normalization and Other Layers

All remaining layers (Fully connected, tangent hyperbolic unit, Threshold and ReLu) are also implemented in CUDA and accelerated using the three-dimensional grid of parallel blocks and threads. The fully connected layer is computed by the GPU-based concurrent matrix multiplication followed by a bias offset [65]. Trained weights and biases are used to perform this operation. The batch normalization layer also has trainable parameters (beta, gamma. variance and mean). These parameters are also imported from Torch-based trained models to normalize the feature maps using the CUDA-based version of batch normalization layer.

#### 4.5.6 Neural Network Architectures implemented in CUDA