Doctoral Dissertation Doctoral Program in Computer and Systems Engineering (XXX cycle)

# Mixed-Criticality Systems on Commercial-Off-the-Shelf Multi-Processor Systems-on-Chip

By

**Stefano Esposito**

\*\*\*\*\*

#### Supervisor(s):

Prof. M. Violante

#### **Doctoral Examination Committee:**

- Prof. M. Di Natale, Referee, Istituto Superiore Sant'Anna of Pisa, Italy

- Prof. A. Bosio, Referee, University of Montpellier, France

- Prof. G. Pravadelli, University of Verona, Italy

- Prof. P. Bernardi, Politecnico di Torino, Italy

- Prof. M. Rebaudengo, Politecnico di Torino, Italy

Politecnico di Torino 2018

## Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Stefano Esposito 2018

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). To my father, for his pride support. To my mother, for her love.

## Acknowledgements

The work in this thesis was partially founded by the ARTEMIS/ECSEL JU project in the IPP "Computing platforms for embedded systems" (AIPP5), under grant agreement no. 621429 (EMC<sup>2</sup> project).

I would like to thank my advisor M. Violante for his support and insights.

I would also like to thank S. Avramenko, for his valuable insights, L. Bozzoli, for her acronym-finding capabilities, and all industrial partners of the EMC<sup>2</sup> project, especially M. Sozzi, M. Terrone, and M. Traversone, for their contributions.

### Abstract

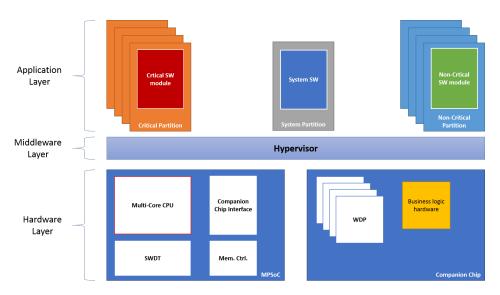

Avionics and space industries are struggling with the adoption of technologies like multi-processor system-on-chips (MPSoCs) due to strict safety requirements. This thesis propose a new reference architecture for MPSoC-based mixed-criticality systems (MCS) - i.e., systems integrating applications with different level of criticality - which are a common use case for aforementioned industries.

This thesis proposes a system architecture capable of granting partitioning which is, for short, the property of fault containment. It is based on the detection of spatial and temporal interference, and has been named the *online detection of interference* (ODIn) architecture.

Spatial partitioning requires that an application is not able to corrupt resources used by a different application. In the architecture proposed in this thesis, spatial partitioning is implemented using type-1 hypervisors, which allow definition of resource partitions. An application running in a partition can only access resources granted to that partition, therefore it cannot corrupt resources used by applications running in other partitions.

Temporal partitioning requires that an application is not able to unexpectedly change the execution time of other applications. In the proposed architecture, temporal partitioning has been solved using a bounded interference approach, composed of an offline analysis phase and an online safety net.

The offline phase is based on a statistical profiling of a metric sensitive to temporal interference's, performed in nominal conditions, which allows definition of a set of three thresholds:

- 1. the detection threshold  $T_D$ ;

- 2. the warning threshold  $T_W$ ;

3. the  $\alpha$  threshold.

Two rules of detection are defined using such thresholds:

Alarm rule When the value of the metric is above  $T_D$ .

Warning rule When the value of the metric is in the warning region  $[T_W; T_D]$  for more than  $\alpha$  consecutive times.

ODIn's online safety-net exploits performance counters, available in many MP-SoC architectures; such counters are configured at bootstrap to monitor the selected metric(s), and to raise an interrupt request (IRQ) in case the metric value goes above  $T_D$ , implementing the alarm rule. The warning rule is implemented in a software detection module, which reads the value of performance counters when the monitored task yields control to the scheduler and reset them if there is no detection.

ODIn also uses two additional detection mechanisms:

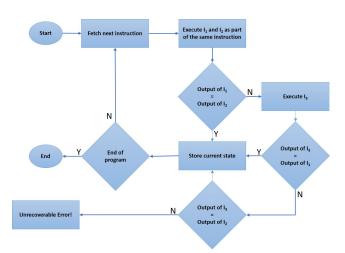

- 1. a control flow check technique, based on compile-time defined block signatures, is implemented through a set of watchdog processors, each monitoring one partition.

- 2. a timeout is implemented through a system watchdog timer (SWDT), which is able to send an external signal when the timeout is violated.

The recovery actions implemented in ODIn are:

- graceful degradation, to react to IRQs of WDPs monitoring non-critical applications or to warning rule violations; it temporarily stops non-critical applications to grant resources to the critical application;

- hard recovery, to react to the SWDT, to the WDP of the critical application, or to alarm rule violations; it causes a switch to a hot stand-by spare computer.

Experimental validation of ODIn was performed on two hardware platforms: the ZedBoard - dual-core - and the Inventami board - quad-core.

A space benchmark and an avionic benchmark were implemented on both platforms, composed by different modules as showed in Table 1 Each version of the final application was evaluated through fault injection (FI) campaigns, performed using a specifically designed FI system. There were three types of FI campaigns:

- 1. HW FI, to emulate single event effects;

- 2. SW FI, to emulate bugs in non-critical applications;

- 3. artificial bug FI, to emulate a bug in non-critical applications introducing unexpected interference on the critical application.

Experimental results show that ODIn is resilient to all considered types of fault.

| Benchmark | HW        | Modules        |              |                   |               |

|-----------|-----------|----------------|--------------|-------------------|---------------|

|           | Platform  | Control<br>law | Compression  | Edge<br>detection | Sensor<br>log |

| Avionic   | ZedBoard  | $\checkmark$   | $\checkmark$ | _                 | _             |

| Avionic   | Inventami | $\checkmark$   | $\checkmark$ | $\checkmark$      | $\checkmark$  |

| Smaaa     | ZedBoard  | $\checkmark$   | $\checkmark$ | _                 | _             |

| Space     | Inventami | $\checkmark$   | $\checkmark$ | _                 | $\checkmark$  |

Table 1 Benchmark composition.

# Contents

| Li | st of l            | Figures |                                                            | xii |

|----|--------------------|---------|------------------------------------------------------------|-----|

| Li | List of Tables xiv |         |                                                            | xiv |

| No | omeno              | clature |                                                            | XV  |

| 1  | Intr               | oductio | n                                                          | 1   |

|    | 1.1                | Proces  | ssor-based embedded systems                                | 1   |

|    |                    | 1.1.1   | The challenge of MPSoCs for avionic and space applications | 3   |

|    | 1.2                | Defini  | tions and Terminology                                      | 5   |

|    |                    | 1.2.1   | Basic definitions                                          | 6   |

|    |                    | 1.2.2   | Dependability and its attributes                           | 6   |

|    |                    | 1.2.3   | Threats to Dependability                                   | 7   |

|    |                    | 1.2.4   | Natural Threats to Dependability During Use-Phase of a     |     |

|    |                    |         | System                                                     | 8   |

|    | 1.3                | Fault I | Effects Analysis Techniques                                | 13  |

|    |                    | 1.3.1   | Fault Injection by Physical Means                          | 13  |

|    |                    | 1.3.2   | Fault Injection Simulation                                 | 14  |

|    |                    | 1.3.3   | Anatomy of a Fault Injection System                        | 17  |

|    |                    | 1.3.4   | Fault Injection Systems                                    | 19  |

|    | 1.4                | Safety  | Standards                                                  | 22  |

|   | 1.5 | Depen         | dable Embedded Systems Design for Safety-Critical Applica- |    |

|---|-----|---------------|------------------------------------------------------------|----|

|   |     | tions .       |                                                            | 27 |

|   |     | 1.5.1         | Fault Detection, Isolation, and Recovery                   | 28 |

| 2 | Mix | ed-Crit       | icality Systems                                            | 33 |

|   | 2.1 | Mixed         | -Criticality Systems Model                                 | 34 |

|   |     | 2.1.1         | Scheduling Concepts                                        | 35 |

|   |     | 2.1.2         | Mixed criticality Scheduling                               | 37 |

|   |     | 2.1.3         | Mixed Criticality Scheduling and Resource Sharing          | 39 |

|   | 2.2 | Comm          | ercial-Off-The-Shelf Components in Space Applications      | 43 |

| 3 | The | <b>ODIn</b> A | Architecture                                               | 48 |

|   | 3.1 | Safety        | Guidelines for Multi-Core Use in Avionic Applications      | 48 |

|   |     | 3.1.1         | Partitioning and Safety Objectives                         | 49 |

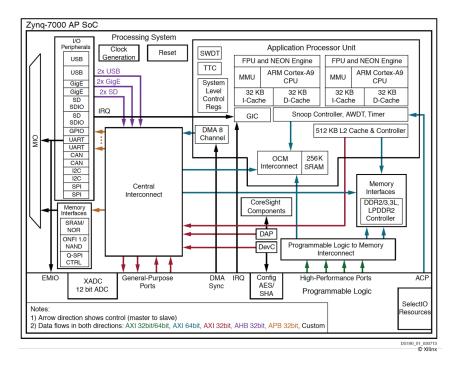

|   | 3.2 | Spatial       | Partitioning in ODIn                                       | 51 |

|   | 3.3 | Tempo         | oral Partitioning in ODIn                                  | 52 |

|   |     | 3.3.1         | Benchmark Application                                      | 54 |

|   |     | 3.3.2         | Metric Definition                                          | 55 |

|   |     | 3.3.3         | Metric Selection                                           | 56 |

|   |     | 3.3.4         | Metric Characterization                                    | 59 |

|   |     | 3.3.5         | Thresholds Determination                                   | 61 |

|   |     | 3.3.6         | Online Phase: Detection and Recovery                       | 65 |

|   | 3.4 | Hardw         | are Support for ODIn                                       | 67 |

|   |     | 3.4.1         | Watchdog Processor                                         | 67 |

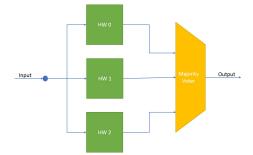

|   |     | 3.4.2         | Hardware Majority Voter                                    | 69 |

|   |     | 3.4.3         | System Watchdog Timer                                      | 69 |

|   |     | 3.4.4         | Metric Monitor                                             | 70 |

|   | 3.5 | ODIn          | Configurations: Avionics and Space                         | 71 |

|   |     | 3.5.1   | Avionic Platform                          | 72  |

|---|-----|---------|-------------------------------------------|-----|

|   |     | 3.5.2   | Space Platform                            | 73  |

|   | 3.6 | Chapte  | er Summary                                | 74  |

| 4 | Exp | eriment | tal Evaluation                            | 77  |

|   | 4.1 | Target  | Hardware                                  | 77  |

|   |     | 4.1.1   | ZedBoard                                  | 78  |

|   |     | 4.1.2   | Inventami Board                           | 80  |

|   | 4.2 | Bench   | mark Applications                         | 81  |

|   |     | 4.2.1   | The <i>RICE</i> compression algorithm     | 82  |

|   |     | 4.2.2   | The <i>Sobel</i> edge detection algorithm | 84  |

|   |     | 4.2.3   | The Avionic Benchmark Application         | 85  |

|   |     | 4.2.4   | The Space Benchmark Application           | 86  |

|   | 4.3 | Experi  | imental Setup                             | 87  |

|   |     | 4.3.1   | The Fault Injection System                | 88  |

|   |     | 4.3.2   | Description of a Fault Injection Campaign | 91  |

|   |     | 4.3.3   | The Type-1 Hypervisor                     | 93  |

|   | 4.4 | Evalua  | ating ODIn for an Avionic Application     | 93  |

|   |     | 4.4.1   | Dual-Core Platform                        | 93  |

|   |     | 4.4.2   | Quad-Core Platform                        | 96  |

|   |     | 4.4.3   | Experiments and Results                   | 98  |

|   | 4.5 | Evalua  | ating ODIn for a Space Application        | 101 |

|   |     | 4.5.1   | Dual-Core Platform                        | 101 |

|   |     | 4.5.2   | Quad-Core Platform                        | 105 |

|   |     | 4.5.3   | Experiments and Results                   | 108 |

|   | 4.6 | Overhe  | ead Evaluation                            | 109 |

|   |     | 4.6.1   | Area Overhead                             | 109 |

|   |     | 4.6.2    | Performance Overhead                           | 110 |

|---|-----|----------|------------------------------------------------|-----|

|   | 4.7 | Chapte   | er Summary                                     | 111 |

| 5 | Con | clusions | s and Future Developments                      | 112 |

|   | 5.1 | ODIn:    | summary of the architecture and its validation | 112 |

|   |     | 5.1.1    | ODIn architecture                              | 114 |

|   |     | 5.1.2    | Experimental validation                        | 117 |

|   |     | 5.1.3    | Conclusions                                    | 118 |

|   | 5.2 | Future   | Developments                                   | 119 |

|   |     | 5.2.1    | Automotive                                     | 119 |

|   |     | 5.2.2    | Next-Gen MPSoCs                                | 120 |

|   |     |          |                                                |     |

### References

122

# **List of Figures**

| 1.1 | Diagrams of an NMOS transistor and of a particle striking a NMOS                                                                                                                                                                                                                                                                                                        |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | transistor                                                                                                                                                                                                                                                                                                                                                              | 10 |

| 1.2 | Anatomy of a fault injection system.                                                                                                                                                                                                                                                                                                                                    | 17 |

| 1.3 | Xception architecture                                                                                                                                                                                                                                                                                                                                                   | 21 |

| 1.4 | Triple modular redundancy.                                                                                                                                                                                                                                                                                                                                              | 29 |

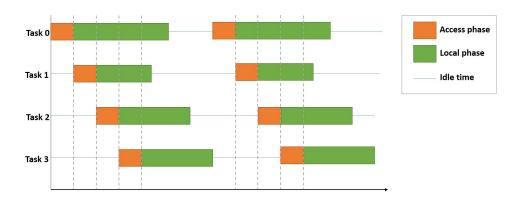

| 2.1 | Example of a four tasks system scheduled on a quad-core processor                                                                                                                                                                                                                                                                                                       |    |

|     | with time multiplexing approach.                                                                                                                                                                                                                                                                                                                                        | 41 |

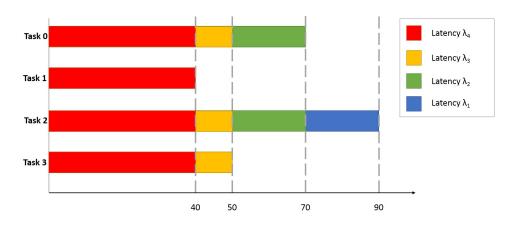

| 2.2 | Example of application of isWCET to four tasks on a quad-core system                                                                                                                                                                                                                                                                                                    | 42 |

| 2.3 | Temporal TMR as implemented by the Proton-100k pre-processor                                                                                                                                                                                                                                                                                                            | 45 |

| 2.4 | Architectural block diagram of the ESA HiRel Computer                                                                                                                                                                                                                                                                                                                   | 47 |

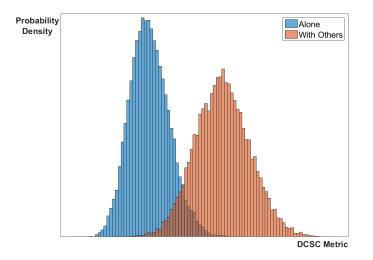

| 3.1 | Comparison of measurements performed with the monitoring task<br>running alone, or with other tasks in the system. Each dataset con-<br>sists of 15000 measures taken on as many executions. In the <i>alone</i><br>scenario, the monitored task was running alone in the system. In the<br><i>with others</i> scenario it was running with one bubblesort task on each |    |

|     | of the other cores in the system.                                                                                                                                                                                                                                                                                                                                       | 59 |

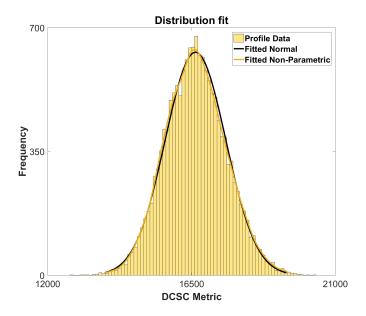

| 3.2 | Data was fitted to a normal distribution and to a non-parametric distribution using Matlab's statistical toolbox. Both distributions where test using an Anderson-Darling goodness-of-fit test. The confidence level in both tests was 0.001                                                                                                                            | 61 |

|     |                                                                                                                                                                                                                                                                                                                                                                         | 01 |

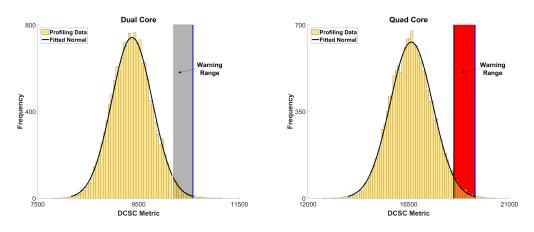

| 3.3 | Data gathered during the profiling phase, with fitter normal distribution, $T_W$ (warning) threshold, and $T_D$ (detection) threshold. The warning range is delimited by the $T_W$ threshold on the left and the                                                                      |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | $T_D$ threshold on the right.                                                                                                                                                                                                                                                         | 64  |

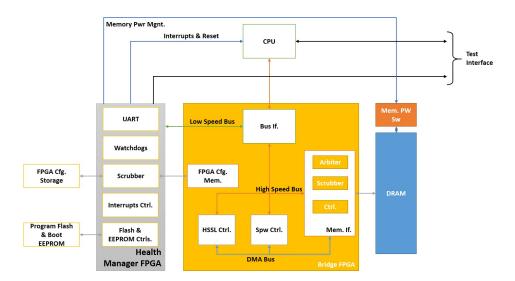

| 3.4 | Block diagram for the ODIn-A configuration.                                                                                                                                                                                                                                           | 72  |

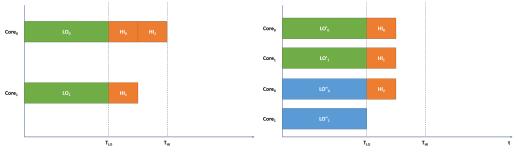

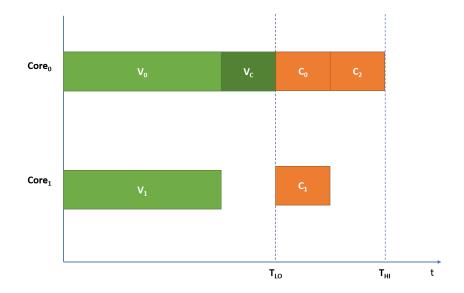

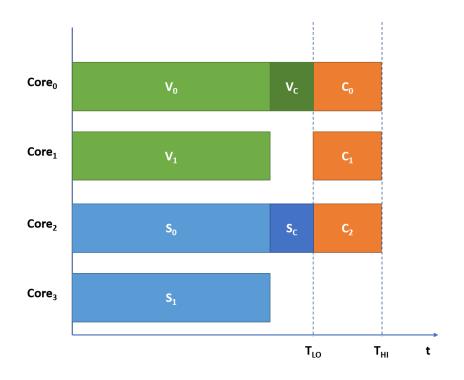

| 3.5 | Example of scheduling for space platforms on a dual-core and on a quad-core MPSoC. $T_{LO}$ is the period of the LO applications, $T_{HI}$ is the period of the HI application. On the dual-core, there are one LO application and one HI application. On the quad-core there are two |     |

|     | LO applications and one HI application.                                                                                                                                                                                                                                               | 73  |

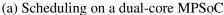

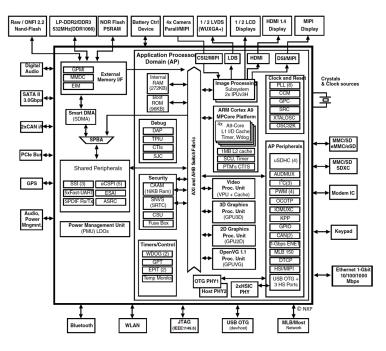

| 4.1 | Block diagram of the Xilinx Zynq-7000 APSoC.                                                                                                                                                                                                                                          | 79  |

| 4.2 | Simplified block diagram of the i.MX6Quad MPSoC                                                                                                                                                                                                                                       | 80  |

| 4.3 | Application of the Sobel edge detection on a standard image. On the left the original image, on the right results of the Sobel algorithm                                                                                                                                              | 84  |

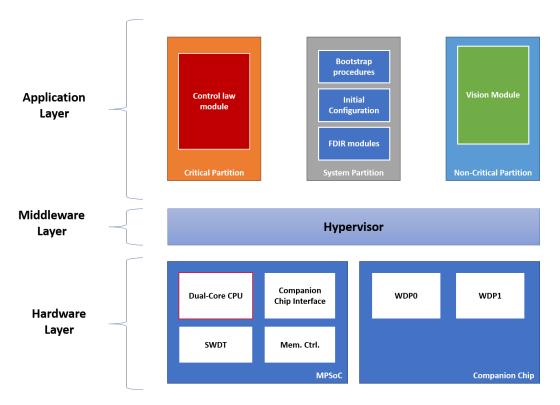

| 4.4 | System-level block diagram for avionic dual core implementation                                                                                                                                                                                                                       | 94  |

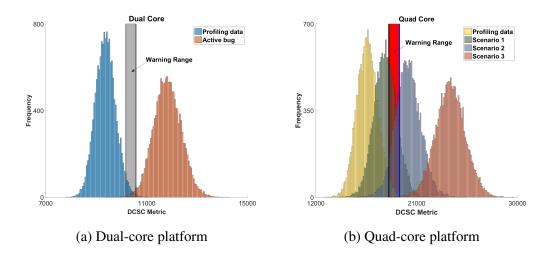

| 4.5 | Results of the application of the temporal partitioning on both the dual-core and the quad-core platforms                                                                                                                                                                             | 100 |

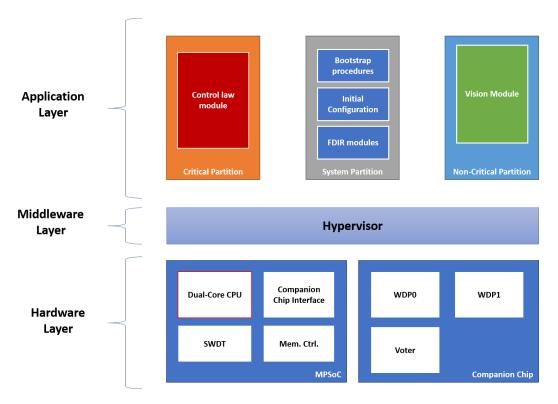

| 4.6 | System-level block diagram for space dual core implementation                                                                                                                                                                                                                         | 102 |

| 4.7 | Nominal system scheduling for the space application on the dual-<br>core platform.                                                                                                                                                                                                    | 103 |

| 4.8 | Nominal system scheduling for the space application on the quad-<br>core platform.                                                                                                                                                                                                    | 106 |

# **List of Tables**

| 1   | Benchmark composition                                                                                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 | ASIL evaluation table                                                                                                                                                          |

| 1.2 | DALs are defined based on the hazard analysis and are associated to<br>a maximum probability of occurrence per flight hour                                                     |

| 2.1 | Task system used as example of application for isWCET 43                                                                                                                       |

| 4.1 | Hardware fault injection results on the dual-core platform for the avionic use-case. For acronyms see Section 4.3.2                                                            |

| 4.2 | Software fault injection results on the dual-core platform for the avionic use-case. For acronyms see Section 4.3.2                                                            |

| 4.3 | Temporal partitioning detection rules activations. The <i>affected tasks</i> column refers to the number of non-critical tasks affected by the artificial bug at the same time |

| 4.4 | Hardware fault injection campaigns results on the quad-core platform for the space use-case                                                                                    |

| 4.5 | Module code size overhead                                                                                                                                                      |

| 4.6 | Total code size overhead                                                                                                                                                       |

# Nomenclature

## Other Symbols

| $ ho_i$     | Priority of task $\tau_i$                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------|

| $R_i$       | Response time of task $\tau_i$                                                                            |

| $T_i$       | Period of task $\tau_i$                                                                                   |

| L           | Criticality levels                                                                                        |

| μ           | Expected value of a random variable                                                                       |

| $\Phi(x)$   | CDF of the standard normal distribution (i.e., a normal distribution with null mean and unitary variance) |

| ψ           | Size of a sample in the RICE compression algorithm                                                        |

| σ           | Standard deviation of a random variable                                                                   |

| $\sigma^2$  | Variance of a random variable                                                                             |

| $	au_i$     | Task i                                                                                                    |

| $B_L$       | Length of a block in the RICE compression algorithm                                                       |

| $C_D$       | Confidence level in the computation of the detection threshold                                            |

| $C_W$       | Confidence level in the computation of the warning threshold                                              |

| $C_{i\ell}$ | Execution time of task $\tau_i$ as estimated for criticality level $\ell$                                 |

| $F_X(x)$    | CDF for the random variable <i>X</i>                                                                      |

| $f_X(x)$    | PDF for the random variable <i>X</i>                                                                      |

| k                | Divisor for the RICE code computation in the RICE compression algorithm          |

|------------------|----------------------------------------------------------------------------------|

| k <sub>opt</sub> | Optimal value of the divisor for a given block in the RICE compression algorithm |

| $L_i$            | Criticality level of task $\tau_i$                                               |

| $T_D$            | Detection threshold                                                              |

| $T_W$            | Warning threshold                                                                |

| Acronyms /       | Abbreviations                                                                    |

| ACP              | Advanced coherency port                                                          |

| API              | Application programming interface.                                               |

| APSoC            | All programmable system-on-chip (the Zynq)                                       |

| APU              | Application processor unit                                                       |

| ARINC            | Aeronautical radio incorporated.                                                 |

| ASIC             | Application-specific integrated circuit.                                         |

| ASIL             | Automotive safety integrity level                                                |

| AXI              | Advanced extensible interface                                                    |

| BE               | Best effort                                                                      |

| CAST             | Certification Authorities Software Team                                          |

| CDF              | Cumulative distribution function                                                 |

| CFC              | Control flow check.                                                              |

| CFE              | Control flow error.                                                              |

| CFG              | Control flow graph.                                                              |

| COTS             | Commercial-off-the-shelf.                                                        |

| CPU              | Central processing unit                                                          |

|                  |                                                                                  |

| DAL              | Design assurance level                              |

|------------------|-----------------------------------------------------|

| DMA              | Direct memory access                                |

| DP               | Dynamic priority scheduling algorithms              |

| EASA             | European aviation safety agency                     |

| ECC              | Error-correcting code.                              |

| EDF              | Earliest deadline first                             |

| ESA              | European space agency.                              |

| FAA              | Federal aviation administration                     |

| FD-SOI           | Full-depletion silicon-on-insulator.                |

| FET              | Field effect transistor                             |

| FF               | Flip-flop                                           |

| FJP              | Fixed job priority scheduling algorithms            |

| FPGA             | Field-programmable gate array.                      |

| FRT              | Firm real-time                                      |

| FTP              | Fixed task priority scheduling algorithms           |

| GAIA             | Global astrometric interferometer for astrophysics. |

| GPIO             | General purpose input/output                        |

| GPU              | Graphic processor unit                              |

| HDMI             | High-definition multimedia interface                |

| HRT              | Hard real-time                                      |

| I/O              | Input/output                                        |

| I <sup>2</sup> C | Inter-integrated circuit                            |

| IC               | integrated circuit.                                 |

| IEC    | International electrotechnical commission             |

|--------|-------------------------------------------------------|

| IMA    | Integrated modular avionics.                          |

| IoT    | Internet-of-Things                                    |

| ISO    | International Standards Organization                  |

| L1C    | Level-1 cache.                                        |

| L2C    | Level-2 cache.                                        |

| MCA    | Mixed-criticality application                         |

| MCS    | Mixed-Criticality System                              |

| MCS    | Mixed-criticality system                              |

| MMU    | Memory management unit.                               |

| MOSFET | Metal-oxide-silicon field effect transistor           |

| MPSoC  | Multi-processor system-on-chip                        |

| NMOS   | N-channel metal-oxide-silicon field effect transistor |

| OCM    | On-chip memory                                        |

| ODIn   | Online detection of interference.                     |

| OEM    | Original equipment manufacturer.                      |

| PCI-e  | Peripheral component interconnect express             |

| PDF    | Probability density function                          |

| PL     | Zynq Programmable Logic                               |

| PS     | Zynq Processing System                                |

| Q-SPI  | Quad SPI                                              |

| RAM    | Random-access memory.                                 |

| ROM    | Read-only memory.                                     |

### xviii

| RTCA   | Radio Technical Commission for Aeronautics  |

|--------|---------------------------------------------|

| RTOS   | Real-time operating system.                 |

| SATA   | Serial advanced technology attachment       |

| SD     | Secure digital                              |

| SDMA   | Smart direct memory access                  |

| SEE    | Single event effect                         |

| SEFI   | Single event functional interruption        |

| SEL    | Single event latch-up                       |

| SERDES | Serialized/deserializer                     |

| SET    | Single event transient                      |

| SEU    | Single event upset                          |

| SIL    | Safety integrity level                      |

| SoC    | System-on-chip                              |

| SOI    | Silicon-on-insulator                        |

| SPI    | Serial peripheral interface                 |

| SRAM   | Static RAM.                                 |

| SRT    | Soft real-time                              |

| STS    | Sporadic tasks system                       |

| SWaP   | Space, weight and power                     |

| TID    | Total ionizing dose                         |

| TTMR   | Temporal triple modular redundancy          |

| UART   | Universal asynchronous receiver transmitter |

| USB    | Universal serial bus                        |

|        |                                             |

| VLIW | Very long instruction word |

|------|----------------------------|

| WCET | Worst-case execution time  |

| WD   | Watchdog.                  |

| WDP  | Watchdog processor         |

# Chapter 1

# Introduction

### **1.1 Processor-based embedded systems**

Processor-based systems have been used in several applications since the start of the information era. Of all such applications a special mention should be made of the embedded systems.

Electronics systems tightly integrated with a physical device, implementing the control logic of the device, can be classified as embedded systems. A typical example of embedded systems are those integrated in household appliances. Such systems have been using small and simple computers for quite some time in order to implement the control logic. Think for instance of washing machines with multiple programs and chronological programming capabilities. Such systems use simple micro-controller-based computers in order to translate user commands into actuation commands to their physical parts, for instance to the electrical motors and valves of a washing machine.

The success of embedded systems is at the origin of the explosion of *smart appliances* and recently of the current *internet-of-things* (IoT) trend. Such applications have been enabled by the use of computers with increasing computational capabilities. In particular, industries like the home appliances and the consumer electronics in general - including the very flourishing industry of handhold devices such as the smart-phones - have been taking advantage of the peculiar capabilities of a rather new set of computers designed for embedded systems. The first step towards

this evolution was the integration of an entire system on a single chip, creating *system-on-chip* (SoC) devices.

The SoC concept is a very successful one, and has been since used in various instances to integrate on a single chip a set of devices which would have been integrated on a circuit board before the development of such concept, such as memory controllers, communication devices, actuator drivers, etc... The SoC concept actually enabled the home theater and the early smart-phone era.

However, increasing performance requirements in applications using SoC required a change in the paradigm of development of such devices. It was not possible to achieve better performance simply increasing the clock frequency as it had been done before, due to the phisical limits of the implementation technology. Therefore, chip manufacturers implemented multi-core system. Multi-core systems are characterized by the integration of more than one central processing unit (CPU) on the same chip. Software developers took advantage of such new platforms to implement new systems with an increasing number of functionalities, partially by using the parallel programming paradigm that had been developed in the years before in other contexts, such as high-performance computing. Since there are several CPUs, each able of running a separate program in cooperation with other cores, applications were segmented into parallel chunks of computation, enabling a great increase in computational throughput, i.e. of the number of computations a systems is able to perform in a unit of time.

Soon after the concept of multi-core processors was merged with that of the SoC to create the multi-processor SoC (MPSoC). An MPSoC is a SoC which integrates more than one CPU. All CPUs in a MPSoC have access to the same system interconnect and as a consequence to all the on-chip and off-chip resources. This development actually enabled the explosion of the contemporary smart-phones.

Although performance gains granted by MPSoCs are of interest for any industry, up until now their use has been greatly reduced in industry domains facing strict and long certification processes. Industries such as civil avionics, automotive, railways and signaling, are all characterized by a set of peculiar requirements that make using MPSoCs a very challenging design choice, mostly due to the added cost of certification that new applications in these domains must face.

### 1.1.1 The challenge of MPSoCs for avionic and space applications

Use of MPSoCs presents several challenges to designers of safety-critical embedded systems such as those found on air-crafts or spacecrafts. One of the main characteristics of such systems are the safety requirements. Such requirements impose a strict development process to achieve the maximum level of certification or qualification, as needed in some cases. In this context, MPSoCs are ill suited, since they are very complex systems, which greatly increase the complexity of the whole certification item. Moreover, MPSoCs are too complex to be developed *in house* by an avionic equipment developer, nor are MPSoCs manufacturers willing to add special provisions to their systems to meet requirements of a relatively small market, such as the avionics or the space applications.

The main issue for a system designer developing an avionic application using a MPSoC, is the partitioning problem. In this thesis, the definition of partitioning is as in [1], where it is defined as "appropriate hardware and software mechanisms to restore strong fault containment". A precise definition of *fault* is proposed in the remaining part of this chapter; however, to understand the definition of partitioning just proposed, one can think of a fault as of the root cause of any malfunctioning. To enforce partitioning as per the definition proposed above, that each application in a system should be self-contained, and any fault affecting any given application in a system should not affect any other application in the system. This property is strictly related to the safety requirements, since the issue for avionics and space applications is the added requirement of strict safety regulations. If the system designer is able to prove partitioning, he/she could also prove safety as required by certification authorities. The partitioning problem has also been identified by the certification authorities software team (CAST), which produced the position paper CAST-32 [2]. The main recommendation to avionic OEMs in [2] is essentially to not use multi-core systems, such as MPSoCs, unless detailed information can be gathered on several details of the architecture. Such details include very sensitive information on the internal bus architecture; such information is a crucial trade secret for MPSoCs manufacturers, one they are reluctant to share with avionics OEMs. As a consequence, the choice left for OEMs is to use MPSoCs as a single-core SoC; i.e., OEMs that use MPSoCs are forced to shutdown all computational cores but one in order to avoid additional challenges - i.e., costs - during the certification process. Similar recommendations are also contained in [3], which is a similar report produced in an European context. In [3], an additional recommendation for procurement of multi-core systems is added, that recommends selecting only systems for which some level of detail on the bus subsystem's behavior is provided by, or can be obtained from the manufacturer.

This thesis deals with the challenges arising from the use of multi-core systems, more precisely MPSoCs, in avionic and space applications. The main motive for use of MPSoCs in such industry domains is the consolidation of functionalities with different levels of criticality on a single hardware, therefore reducing space, weigh, and power (SWaP) consumption of the whole system. A system with such a characteristic is define a mixed-criticality system (MCS). An application featuring at least one MCS as subsystem is a mixed-criticality application (MCA). In an MCS, the main issue is the partitioning, as defined above. To deal with the partitioning problem, it is often divided in two sub-types:

- 1. *Spatial partitioning*: the property of containment with respect to faults affecting resources shared by more than one application in the system. The fault does not affect timing properties of the interaction between an application and the resource, but it affects the correctness of the result. For instance, a faulty application might change the configuration of a shared peripheral in an unpredictable way.

- 2. *Temporal partitioning*: the property of containment with respect to faults affecting the timing of an application. The fault affects some shared resource in a way that change the timing properties of the interaction between an application and the resource but it does not affect the correctness of the result. For instance, a faulty application might abuse a shared communication channel, causing a delay in other applications.

This thesis proposes a novel reference architecture which addresses the challenges of MCS deployed on MPSoCs. This thesis describes a set of mechanisms and support hardware that can be used by designers in order to develop certifiable equipment for both avionic and space applications. It presents the key features of the architecture and a realistic avionic use-case. Although the architecture proposed in this thesis was developed with mainly the avionic and space applications in mind, the MCS problem is of interest for many other industries. Suffice to cite the  $EMC^2$  project [4], which was promoted by a consortium of tens of companies, operating in the industries of automotive, avionic, and space. The project was focused on the identification and development of technologies for use of multi-core systems in the scope of mixed-criticality systems. This thesis work is partially in the scope of the  $EMC^2$  project.

This thesis is organized as follows: the remainder of the present chapter introduces key concepts used in the rest of the thesis; Chapter 2 contains a survey of the relevant literature on the topic of MCA for avionics and space applications; Chapter 3 describes the proposed solution in detail; Chapter 4 describes the experimental evaluation performed on the architecture; Chapter 5 presents the conclusion of the thesis and outlines possible extensions and new applications.

### **1.2 Definitions and Terminology**

This section provides the definition for some of the terms that are commonly used in the literature that constitutes the context of this thesis. The literature will be properly analyzed in the next chapter, however it is useful to have some terminology in order to better describe the problem tackled by the work presented in this thesis. The main focus of this thesis is on dependability and in particular safety of a set of applications defined as safety-critical. Some industry domains, characterized by strict safety requirements, have in time adopted a set of safety regulations. All such regulations share a common root in the IEC-61508 [5]. This standard introduces some core concepts which are referenced and extended in more specific standards for some domains such as RTCA DO-178C [6] for avionics and ISO 26262 [7] for automotive. In the rest of this section, the basic terms for understanding the dependability problem are defined, and then a very brief survey of the cited safety standard is provided, for the parts most relevant to the scope of the thesis. A more complete review of the standards, although it might result interesting, is out of the scope of this work.

### **1.2.1 Basic definitions**

For the following discussion, it is useful to define some terms that are widely used in safety standards as those cited in Section 1.2. In this thesis, definitions are as in [8] and [9], and are reported here to constitute a glossary for the remainder of the thesis.

In the scope of this thesis, a **system** is any entity carrying out a specific function while interacting with other systems, which constitute its environment. The behavior of a system is represented by how the system carries out its intended function. The way this behavior is perceived by an user is the service provided by the system. An user is another system, including in this definition an human being, interacting with the system through the system boundary. The portion of system boundary used to deliver the service is the service interface. The part of the system's state that can be observed at the service interface is its external state, whereas the rest is the internal state. The portion of the service interface with which the user interfaces is the use interface. A system provides correct service when it implements its function. A failure is the transition or deviation from the correct service to a non-correct service. The period during which the correct service is not delivered is the **service outage**. There is a **service restoration** when after a service outage the correct service is restored. A fault is the "adjudged or hypothesized cause of an error" [8]. A fault is dormant if it has not caused an error in the system, it is active otherwise. An error is any variation in the total state of the system with respect to the expected total state in that instant in time. An error can propagate within the system until it reaches the use interface of the system. When an error reaches the interface it becomes a failure or misbehavior.

### **1.2.2** Dependability and its attributes

The **dependability** of a system is its ability to "deliver service that can be justifiably trusted" [8]. The dependability of a system comprises several attributes, which have been defined over several contributions in the past. The definitions used in this thesis and reported below are the ones collected in [9]. Such attributes are:

• *availability*: readiness for service or the probability that service delivered by a system is correct at any given time;

- *reliability*: continuity of a correct service or the probability that the system delivers a service correctly at a time T given that it was delivering correct service at a time  $T_0 < T$ ;

- *integrity*: the capability of avoiding improper alterations, which can be further categorized into:

- system integrity: the ability of detecting a fault and to inform the user;

- *data integrity*: the ability of preventing and correcting errors in the system database, which may result as a consequence of an error.

- *safety*: the capability of avoiding catastrophic consequences for the environment or the user;

- maintainability: the capability of being repaired and evolved.

### **1.2.3** Threats to Dependability

Threats to dependability include all such phenomena that may affect the system reducing its dependability. A very comprehensive classification of such threats is reported in [8]. For the scope of this thesis, just a subset of such classification is needed and is here reported for a better fruition of the remainder of the thesis.

A threat to dependability acts by introducing a fault in the system. Threats to dependability can be classified based on the moment in the life cycle of the system in which they are introduced. The life cycle of the system can be subdivided in a *development* phase and in a *use* phase. In the rest of this paper, the terms use phase and *mission* of the system might be used interchangeably.

Threats introduced in the development phase consists mainly in design errors or *bugs*. Such errors can be *malicious* or *non-malicious*. The most relevant case in the scope of this thesis is the unintentional design error, which introduces an unexpected behavior of the system, which does not respect its classification in a given circumstance. Authors of [8] suggest a further classification in *deliberate* and *non-deliberate* which is of little consequence to the scope of this thesis, however it might be interesting to notice that the certification process is put in place with the main objective of avoiding deliberate or non-deliberate non-malicious development errors. Threats introduced in the use phase consists mainly of *natural* or *human-made* threats. Human-made use phase errors can be either *malicious* or *non-malicious*, and are differentiated mainly by the intention of the human causing the error. A malicious use phase human-made error is introduced with the purpose of causing a service failure, a non-malicious use phase human-made errors are not considered in the rest of this thesis, since it is supposed that human users of safety-critical systems are always highly trained in the use of the system and as such are unlikely to introduce non-malicious human-made errors during the use phase. Natural use-phase errors are those most relevant in the scope of this thesis and as such are treated in a dedicated section below.

# **1.2.4** Natural Threats to Dependability During Use-Phase of a System

Natural threats to dependability during the use-phase of a system are introduced by unexpected interactions between the system and its environment. In this kind of interactions, the system is subjected to random stimuli coming from the environment, which may introduce a fault in the system (see Section 1.2.3).

Faults are can be classified as follows, according to[10].

- *permanent faults*, which persist in the system for an indefinite time;

- transient faults, which disappear from the system after a finite amount of time.

- *intermittent faults*, which causes errors to happen in burst only under given circumstances.

- **Permanent Faults.** A permanent fault is originated by a defect in the system. In an electronics system, permanent faults can be either introduced during manufacturing, due to the intrinsic uncertainty of some processes in the realization of integrated circuits (ICs), or can arise due to aging. The main source of aging in semiconductors are microscopic effects of current in metal conductors embedded in the IC. Such effects as the electromigration or the hill effect, can cause the entire circuit or portion of the circuit to cease function. Since

these, as well as the manufacturing defects, are physical defects, they cannot be removed from the circuit and are, as a consequence, permanent faults.

Permanent faults are classified according to several models, the most widely used are the single stuck-at and the delay model.

- *single stuck-at*: this fault model refers to the situation in which the value of a logic element in the system is always providing either a logic high or a logic low voltage;

- *delay*: this fault model refers to the situation in which a defect in the system is causing a given circuit to provide its outputs later than expected. As a consequence, the results of such computations may not be correctly sampled by sequential elements in the system, thus causing an error.

- **Intermittent Faults.** Such faults can be modeled as permanent faults which only happen under given conditions. These faults can be difficult to distinguish from transient faults; however, some criteria are suggested in [10]:

- 1. intermittent faults occur repeatedly at the same location;

- 2. intermittent faults can be removed from the system by replacing the affected circuit, whereas transient faults are not removed by such an action;

- 3. intermittent faults cause bursts of errors when the fault is activated.

- **Transient Faults.** A transient fault is introduced in the system by an unexpected interaction with the environment and has the characteristic of disappearing spontaneously from the system. However, such faults can cause errors and failures in the affected system. The main source of transient faults, in the scope of this thesis, are radiation effects on electronic circuits in the system. Since transients are the most relevant faults in the scope of this thesis, they are described below in more detail, together with their models.

#### **Radiation-Induced Faults**

The most relevant natural threat to dependability, in the scope of this thesis, is the radioactive environment in which the system may be operating.

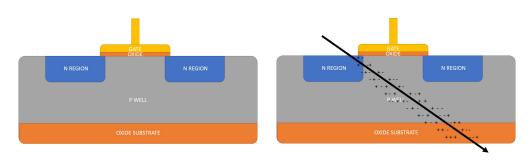

(a) A typical NMOS transistor

Fig. 1.1 Diagrams of an NMOS transistor and of a particle striking a NMOS transistor

The radioactive environment is here defined as the capability of the environment of exchange energy with the system in the form of radiation packets or particles. Such event is very frequent and relevant for space applications, however it is becoming more relevant in more traditional applications such as avionics, high performance computing and even automotive, due to the shrinking of the technology node used in such applications.

Radiations act as unexpected stimuli to the system according to several physical mechanisms. The specifics of the effects of radiation on electronic circuits are beyond the scope of this thesis. Suffice to say that as a consequence of the interaction between radiations and the system, some unexpected behavior is observed. As already stated above, in the scope of this thesis, the system is always an electronic system. The interactions between an electronic systems and radiations can be considered as the effects of a particle strike on the matter composing the integrated circuits of the system. This matter is mostly silicon, since most of the circuitry in an electronic circuit is realized with such material. In fig. 1.1a it is depicted a typical implementation of a silicon-on-insulator (SOI) N-channel metal-oxide-silicon field effect transistor (MOSFET or simply MOS). This is the basic implementation of most modern technologies, although in more recent developments, the gate has been modified to overcome problems due to the reduced size of the channel, that is the distance between the two N regions in fig. 1.1a. The most relevant of such developments is the so-called FIN-FET, used for technology nodes of 28 nm and below. For sake of simplicity, the full extent of this technology is not described in this thesis. For the scope of this thesis it should be sufficient to mention that in this

type of technology node, the channel is developed vertically above the surface of the silicon substrate and the gate envelopes the whole surface of this extrusion.

The main effect of a particle strike on a transistor as the one depicted in fig. 1.1a is the creation of a current, due to the displacement of electron-well pairs in the wake of the particle passing. When an high energy particle, like a proton or a heavy ion strikes the transistor, if it has enough energy, it can pass through the silicon lattice of the substrate, causing a parasitic current to flow through the transistor. Depending on the nature of the circuitry surrounding the transistor, this parasitic current can be seen as a fault appearing in the system. Due to the high number of variables that can change the effects of a particle strike, it is necessary to classify faults according to a set of models, which allows for an easier analysis of effects and outcomes.

Faults arising from radiation can be classified at first as effects of a single particle strike, which are the single event effects (SEE), and as effects of the total exposition to radiation, i.e. the total ionizing dose (TID). The TID effect is due to the damages introduced by several particle strikes in the system. When such damages are above a certain tolerable threshold, the system breaks down and is incapable of providing its service, unless the damaged parts are replaced by new ones. TID effects can be classified as permanent faults and are important when considering long space missions, although they are not considered in the scope of this thesis, since they are primarily of concern during components procurement.

In the scope of this thesis, SEE are much more interesting than TID. A SEE is the effect of a single particle strike, introducing a fault in the system. SEEs are further subdivided into:

- *single event upset (SEU)*: this fault model represents the effect of a single particle strike hitting a memory cell in the system and altering its content. The memory cells of an electronic system are susceptible to change in their contents due to parasitic currents induced by a particle strike.

- *single event transient (SET)*: this fault model represents the effect of a single particle strike hitting a logic gate within the system. The parasitic current resulting from the particle strike, temporarily alters the output of a logic cell. This wrong output can be sampled by multiple flip-flops (FFs) down the line, introducing multi-bit errors in the system memory.

- *single event functional interruption (SEFI)*: this fault model represents the effect of a single particle strike causing the system to enter a state from which it cannot recover without an external intervention. An example of SEFI, can be a particle striking the reset logic of a processor, causing it to enter in a permanent reset state; in this instance, the system can be recovered through a power cycle which can be initiated by a human user or by a companion system.

- *single event latch-up (SEL)*: this fault model represents the effect of a single particle strike resulting in a permanent error. In this case, the particle strike occurred in such a way to cause a high current to develop in a part of the system. Such a high current can cause a permanent damage in the system, in which case all or part of system functions are lost; if there is no permanent damage, the system can recover through a power cycle.

All SEEs can be classified as *soft errors*. As opposed to *hard errors* - which are permanent damages to the hardware of the system - soft errors are faults that can be removed from the system without replacing any parts of it. In the scope of this thesis, soft errors are most interesting than hard errors, since these are only recoverable through a recovery maintenance in which the faulty part of the system is replaced by a new fault-free one.

Although up until now only hardware faults have been considered, it is worth to mention and clarify that also software can be subject to faults. However, software faults can be introduced in the system only as design errors, meaning that they are deliberate or non-deliberate non-malicious design phase threats to dependability. However, a software fault, or bug, can be activated - excited - as a consequence of a SEE, which can put the system hardware in a state that was not foreseen during software development, and as such cause a software error. All software errors can be considered soft errors, since restoring the system to a known state usually involves also the resolution of the software error. Safety standards as those cited in Section 1.2 introduce several measures in the development process to ensure that in the system there is no software fault. Although, this kind of process is rather costly and as such is reserved only to highly critical parts of the system, i.e. those parts whose failure may result in loss of mission or in injury to humans or to the environment.

### **1.3 Fault Effects Analysis Techniques**

Several techniques have been proposed over the years to analyze effects of faults on electronics systems. Components that have to meet quality requirements as those in automotive standards of quality - e.g., the automotive electronic council quality standards [11] - are commonly subjected to environmental conditions designed to speed-up aging processes which would naturally occur at a much slower pace. One such technique is the burn-in technique, in which a batch of newly produced ICs is inserted in an oven which reaches high temperatures - usually above 200 °C. In such an environment, phenomena like electromigration or hill effects occur much more quickly that in normal conditions, and allow to discard components subjected to the so-called infant mortality during a subsequent test phase.

The main scope of this thesis is however on transient faults; therefore, this section focuses on techniques used to introduce such faults in a working system in order to analyze their effects and to evaluate detection mechanisms. The process of introducing faults in a system is commonly referred to as fault injection [12]. Fault injection can be performed in several different ways.

#### **1.3.1** Fault Injection by Physical Means

In this kind of fault injection, a physical mean is used to inject faults in the system. Such physical mean usually consists of a radiation beam or a laser source [13]. Experiments performed using radiation beams, or radiation experiments, are very widespread especially during qualification of components for space use. Each year, the Radiation Effects Data Workshop (REDW) provides an publication outlet for researchers around the world performing studies on radiation effects on electronics. A review of such results can provide an outline of the most used techniques.

Radiation experiments can be classified on the basis of the nature of the radiation beam. Radiation experiments are usually performed using heavy ions beams [14][15]. Results of such experiments can be used to estimate the response of the system to other types of radiations it might encounter in space[16]. Other commonly used radiation beams are protons [17][18], and neutron beams [19][20].

Data obtained through such experiments can be used to estimate dependability attributes of the system, as the figure of merit (FOM) method [16]. Another approach

uses data from radiation experiments and from fault injection simulation experiments to estimate the availability of a system [21].

### **1.3.2** Fault Injection Simulation

Fault injection is a deliberate introduction of faults in operational systems to observe the response [12]. There are several methods to achieve such a goal that can be categorized as

- 1. Simulation Based

- 2. Software Based

- 3. Hybrid techniques

For the purposes of this thesis, the target system is considered to be a processor based embedded system in which a set of faults F is injected during normal operations with activation trajectories A. The behavior of the system is read at readouts R and dependability measures M are obtained through the fault injection. These sets form the so called FARM model [9]. The FARM model can be extended adding a set Wcontaining workloads applied to the system during fault injection. The measures in M are obtained through a succession of fault injections, each called an *experiment*, forming a *campaign* [9]. Each experiment is characterized by a fault, an activation trajectory and a readout, i.e. by a triple < f, a, r > with  $f \in F$ ,  $a \in A$  and  $r \in R$ . Measures in M are computed from readouts obtained during the campaign compared to the workloads W.

The FARM model can be applied to different techniques, being a general model for a fault injection campaign. Each technique is characterized by a set of attributes [9]:

**Intrusiveness.** The intrusiveness is defined by the changes that are applied to the system in order to implement the fault injection techniques. Often the memory content changes because some code is added to the system to support fault injection. Moreover, the system can show a different temporal behavior because of the fault injection. A good fault injection method tries to minimize the intrusiveness.

- **Speed.** Duration of a fault injection campaign is given by the duration of a single experiment and the number of faults to inject, thus to reduce duration of a campaign two approaches can be applied:

- 1. Reduce duration of a single fault injection

- 2. Reduce size of the fault list, by applying some fault collapsing rule or by random sampling.

- **Cost.** The fault injection system must have a negligible cost with respect to the cost of the system. In the cost are included all the hardware, software and the time needed to setup the system and adapt it to the target system.

Now it is in order to describe what each set in the FARM model should contain and its desirable characteristics.

- Set F. This set contains the faults to be injected in a target system. To define this set a fault model must be selected, considering both the need of a fault model close to reality and feasibility of the fault injection campaign. Once the fault model has been selected, the fault list can be generated. The set F, which is practically the fault list, contains one entry for each fault, each entry containing [9]:

- **Fault injection time,** which is the time instant when the fault is injected in the system. It can be expressed in a proper time unit, in number of instructions or in clock cycles.

- **Fault location,** which is the part of the system affected by the fault. For example, if the selected fault model is SEU/SET, the location can be the register or the memory location to be affected by an SEU or the gate where an SET must be injected.

- **Fault mask,** which is the way the exact bit to be changed is selected from an n-bit wide register or memory location.

- **Set A.** This set contains the description of how the inputs should be applied to the system during the fault injection campaign. It can be very complex, especially in an embedded system featuring several inputs of different kind (digital/analog, high frequency/low frequency, ...) [9].

- Set R. This set is filled by information gathered during the fault injection campaign observing the target behavior [9].

- **Set M.** This set is filled at the end of the campaign and contains the results of the performed experiments. Faults effect are classified based on their effect on the system. Here is introduced the classification to which this thesis refers and that has been described in [9]:

- **Effect-less or silent fault.** The fault is never activated as an error and after injection stays in the system for a while as a passive fault before being removed. An example of this effect is the following: a fault is injected in a CPU register but the first operation performed on that register after the injection is a write operation, the fault is thus removed from the system and does not produce neither an error nor a misbehavior.

- **Failure.** The fault evolved as an error which was able to propagate to the system outputs.

- **Detected fault.** The fault evolved as an error, but the error was then detected by an implemented fault tolerance solution. Based on the way the fault was detected we can further classify detected faults as follows:

- **Software-detected fault.** The module that detected the fault was implemented in the system's software which in turn signaled the presence of the error either to the user or to a fault recovery mechanism.

- Hardware-detected fault. The module that detected the fault was implemented in the system's hardware. In a processor system, this can be either a special purpose peripheral or an exception mechanism implemented into the processor. An example of special purpose hardware could be a parity-checker used on some of the system's data: when a parity-violation is detected the parity checker raises an interrupt that implements the error-signaling. An example of a CPU-implemented exception is the illegal instruction trap triggered when the CPU fetches a malformed instruction from memory. This can be in turn the result of a fault affecting the instruction memory hierarchy.

- **Timeout-detected fault.** The fault was detected by a timing violation of the outputs, which can be still correct but were provided after a

fixed deadline. This kind of faults can be detected, for instance, by a watchdog timer that expires when the system violates its timing.

#### **1.3.3** Anatomy of a Fault Injection System

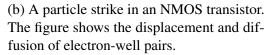

Many solutions for a fault injection system has been proposed with different approaches [22] [23] [24] [25] [26]. However, all fault injection systems share some concepts and components that are described in this section. Figure 1.2 shows how a fault injection system is organized and its components with respect to a target system.

Fig. 1.2 Anatomy of a fault injection system.

#### **Components of a Fault Injection System**

This section describes the typical components of a fault injection system in terms of functionalities implemented and relations with the target system and the other components of the fault injection system.

*Fault List Generator.* A fault list generator is responsible for the creation and trimming of a fault list. The fault list depends on the used fault model, but with SEU/SET it can be at first very large. Since a very large fault list means a very long time needed to inject all its faults, various strategies are used to reduce its size. In [26] a fault collapsing strategy is used. The strategy is a workload-dependent fault collapsing exploiting the concepts of equivalent faults and effect-less faults. Two faults are equivalent if they propagate at the same time. A fault is effect-less if the first operation after its injection is a write operation that removes the fault. By applying this two concepts, the fault list size can be greatly reduced.

- *Fault Injector.* The Fault injector is responsible for introducing the fault into the system. Depending on the used approach, the fault injector can be a piece of software running on a workstation computer, a piece of software running on the target system or a special purpose hardware. In simulation based solutions, the fault injector can be either a component specifically added to the model or it can be a script running inside the simulation tool in use. This component behavior is quite important since it could modify the behavior of the system, for instance by modifying its timing properties.

- *Workload Generator.* The workload generator is responsible for generating and applying input patterns to the target system. The fault injection happens while the target system is processing the inputs generated by this component.

- *System Monitor*. The system monitor is responsible for observing the system status and eventually triggering the data collector and analyzer component.

- *Data Collector and Analyzer*. The Data Collector and Analyzer, fetch data from the system when triggered by the system monitor, and depending on the obtained data it decides what is the outcome of the experiment. At this end the data collector and analyzer can collect various information including the outputs, the internal state and timing information on the execution.

- *Injection Manager.* The Injection Manager is the key point of a fault injection system. Its role is to supervise to the fault injection campaign by coordinating all other components. In particular the Injection Manager is in charge of

- 1. Extract one fault from the fault list

- 2. Instruct the Fault Injector with the information relevant to the extracted fault

- 3. Activate the System Monitor

- 4. Reset the Target System

- 5. Activate the Workload Generator

- 6. Categorize the experiment outcome based on the data collected by the Data Collector and Analyzer.

#### **1.3.4 Fault Injection Systems**

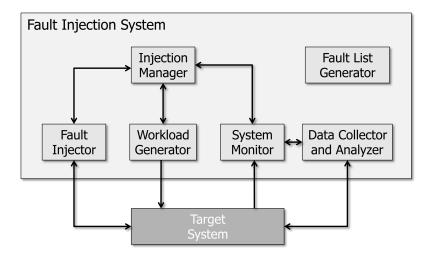

Many fault injection solutions have been developed and proposed over the years. The various fault injection systems can be categorized into three categories:

- **Simulation-based.** To this class belong the systems that use a simulator to run a model of the target system and injecting faults as needed.

- **Software Implemented.** This class includes systems that are implemented through software mechanisms running on the target system or on a host workstation connected to the target system.

- **Hardware-based.** This kind of solutions includes systems implemented with an external hardware in charge of managing the faults and the injection procedure.

- **Hybrid Solutions.** There exists solutions that can be described as hybrid between software and hardware-based systems, as the one that was used in this thesis and that will be described in following chapters.

#### Simulation-based Systems

This kind of systems rely on the description of the target system in some modeling language. Usually the system is described either in VHDL or Verilog and is simulated using fault-simulation tools [27]. Available logic-simulation or fault-simulation tools have usually a good built-in support for permanent fault models like stuck-at or delay, but lack a support for SEU/SET fault models, thus implementing a fault injection system requires one of the following approaches:

**Modify the tool.** The tool could be modified to implement SEU/SET fault models, when possible, or a different tool can be used with a built-in support for these fault models. However tools with such a built-in support are few and mostly come from universities.

- **Modify the model.** The system model can be modified to add some support to the fault injection model. This is a rather simple solution allowing test engineers to easily implement a fault injection system and is one of the most successful approaches in this field with various proposed tools [22] [23] [24] [25]. The popularity of the solution is also due to the fact that it avoids to have to change the simulation tool already in use.

- **Using simulator commands.** This approach exploits the scripting facilities commonly included in a simulation tool and the commands already implemented in the tool to force a value inside the model [28]. Using this approach is possible to support SEU/SET but also other fault models.

An example of the latest solution is AMATISTA [26]. The AMATISTA solution uses concepts already introduced in [28], that are

- **Golden Run.** It is a fault free simulation of the system used to store information on the expected state and outputs. The state is saved at some given checkpoints that will be later used during fault injection

- **Static Fault Analysis.** It is an analysis performed on the fault list to delete faults whose effect can be determined *a priori*. For instance, a fault that is injected just before a write operation on the target register. This fault can be deleted from the fault list, since it is granted to be effect-less.

- **Dynamic Fault Analysis.** During the fault injection experiments, the status of the system is periodically compared to the state saved from the golden run to detect errors and failures.